### **OVERVIEW**

The SM8578BV is a serial interface, real-time clock IC that uses a 32.768 kHz crystal oscillator for its reference timing. It comprises second-counter to year-counter clock and calendar circuits that feature automatic leap-year adjustment, alarm and timer interrupt functions, as well as oscillator stop, timer reloading, and other detection functions. Data is transferred to and from an external controller using a 3-wire serial interface. It is available in compact 8-pin VSOP packages, making it ideal for use in all types of portable, hand-held equipment.

#### **FEATURES**

- 1.6 to 5.5V wide operating voltage range

- 0.5 $\mu$ A (typ.) current consumption (V<sub>DD</sub> = 3.0V, CE = Low)

- 3-wire serial interface control

- Day, day-of-week, hour, and minute alarm interrupt function

- 1/4096 seconds to 255 minutes presettable interval timer interrupt function

- Time update detection function

- Abnormal oscillation detection function

- Automatic leap-year adjustment function (Western and Japanese calendars)

- Oscillator capacitor C<sub>D</sub> built-in

- Molybdenum-gate CMOS process

- Miniature 8-pin VSOP package

### ORDERING INFORMATION,

| Device   | Package    |

|----------|------------|

| SM8578BV | 8-pin VSOP |

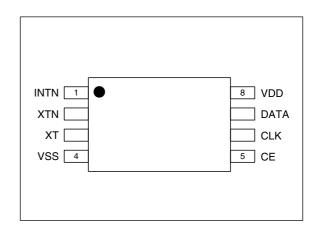

### **PINOUT**

(Top view)

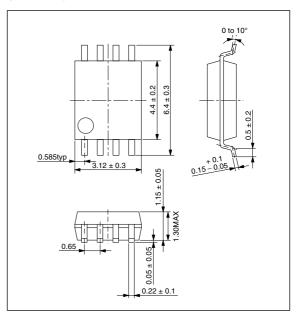

### **PACKAGE DIMENSIONS**

(Unit: mm)

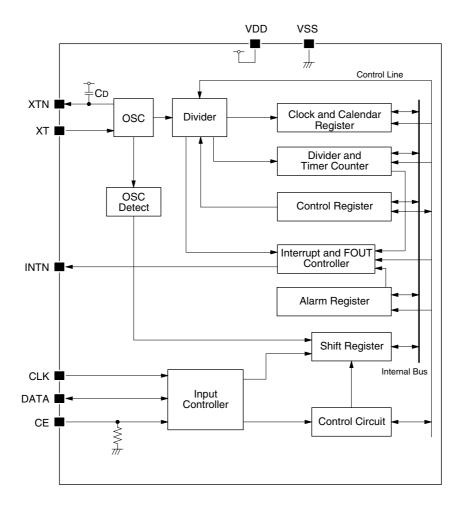

# **BLOCK DIAGRAM**

## **PIN DESCRIPTION**

| Number | Name | I/O | Function                                                                                                                                                                                 |

|--------|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | INTN | 0   | Timer interrupt/alarm interrupt output, determined by internal mode setting, or frequency output, with frequency value given in the frequency set register (N-channel open-drain output) |

| 2      | XTN  | 0   | Oscillator output. Oscillator capacitor C <sub>D</sub> built-in.                                                                                                                         |

| 3      | XT   | ı   | Oscillator input                                                                                                                                                                         |

| 4      | VSS  | -   | Negative supply voltage connection                                                                                                                                                       |

| 5      | CE   | ı   | Chip enable input with pull-down resistance built-in. Internal registers can be accessed when CE is HIGH.                                                                                |

| 6      | CLK  | I   | Serial data transfer clock input. In write mode, data is read in from DATA on the rising edge of CLK. In read mode, data is read out from DATA on the rising edge of CLK.                |

| 7      | DATA | I/O | Serial data transfer data input/output. When CE goes HIGH, the first four bits of write data determine the operating mode (read mode/write mode).                                        |

| 8      | VDD  | -   | Positive supply voltage connection. A 0.1µF bypass capacitor should be connected between VDD and VSS.                                                                                    |

### **SPECIFICATIONS**

# **Absolute Maximum Ratings**

$$V_{SS} = 0V$$

| Parameter                 | Symbol            | Condition  | Rating                                  | Unit |

|---------------------------|-------------------|------------|-----------------------------------------|------|

| Supply voltage range      | V <sub>DD</sub>   |            | -0.3 to +7.0                            | V    |

| Input voltage range       | V <sub>IN</sub>   | Input pins | $V_{SS} - 0.3 \text{ to } V_{DD} + 0.3$ | V    |

| Output voltage range 1    | V <sub>OUT1</sub> | INTN       | V <sub>SS</sub> – 0.3 to +8.0           | V    |

| Output voltage range 2    | V <sub>OUT2</sub> | DATA       | $V_{SS} - 0.3 \text{ to } V_{DD} + 0.3$ | V    |

| Power dissipation         | P <sub>D</sub>    |            | 150                                     | mW   |

| Storage temperature range | T <sub>STG</sub>  |            | -55 to +125                             | °C   |

# **Recommended Operating Conditions**

$$V_{SS} = 0V$$

| Parameter                   | Symbol           | Condition | Rating     | Unit |

|-----------------------------|------------------|-----------|------------|------|

| Supply voltage range        | V <sub>DD</sub>  |           | 1.6 to 5.5 | V    |

| Operating temperature range | T <sub>opr</sub> |           | -40 to +85 | °C   |

## **DC Characteristics**

$V_{SS}$  = 0V,  $V_{DD}$  = 1.6 to 5.5V,  $C_G$  = 10pF, Ta = -40 to +85°C unless otherwise noted.

| Parameter                | Symbol            |                                                                            | Condition -                      |                    | Rating |                        | Unit  |

|--------------------------|-------------------|----------------------------------------------------------------------------|----------------------------------|--------------------|--------|------------------------|-------|

| raiailicici              | Symbol            | ,                                                                          |                                  |                    | typ    | max                    | J.III |

| Current consumption 1    | I <sub>DD1</sub>  | V <sub>DD</sub> = 5V                                                       | CE = V <sub>SS</sub> , DATA,     | -                  | 1.0    | 2.0                    | μΑ    |

| Current consumption 2    | I <sub>DD2</sub>  | V <sub>DD</sub> = 3V                                                       | INTN = V <sub>DD</sub>           | -                  | 0.5    | 1.0                    | μΑ    |

| HIGH-level input voltage | V <sub>IH</sub>   | CE, CLK, D                                                                 | ATA nino                         | 0.8V <sub>DD</sub> | -      | V <sub>DD</sub>        | V     |

| LOW-level input voltage  | V <sub>IL</sub>   | OE, OLK, D                                                                 | AIA pilis                        | 0                  | -      | 0.2V <sub>DD</sub>     | V     |

| Input leakage current    | I <sub>LEAK</sub> | $V_{IN} = V_{DD}$ o                                                        | r V <sub>SS</sub> , CE, CLK pins | -0.5               | -      | 0.5                    | μΑ    |

| Input resistance 1       | R <sub>DWN1</sub> | V <sub>DD</sub> = 5V                                                       | $V_{DD} = 5V$ $V_{IN} = V_{DD}$  |                    | 150    | 300                    | kΩ    |

| Input resistance 2       | R <sub>DWN2</sub> | V <sub>DD</sub> = 3V                                                       | CE pin                           | 150                | 300    | 600                    | kΩ    |

|                          | V <sub>OH1</sub>  | V <sub>DD</sub> = 5V                                                       | I <sub>OH</sub> = -1mA,          | 4.5                | -      | 5.0                    | V     |

| Output valtage 1         | V <sub>OH2</sub>  | V <sub>DD</sub> = 3V                                                       | DATA pin                         | 2.0                | -      | 3.0                    | V     |

| Output voltage 1         | V <sub>OL1</sub>  | V <sub>DD</sub> = 5V                                                       | I <sub>OL</sub> = 1mA,           | -                  | -      | V <sub>SS</sub> + 0.5  | V     |

|                          | V <sub>OL2</sub>  | V <sub>DD</sub> = 3V                                                       | DATA pin                         | -                  | -      | V <sub>SS</sub> + 0.8  | V     |

| Output valtage 0         | V <sub>OL3</sub>  | V <sub>DD</sub> = 5V                                                       | I <sub>OL</sub> = 1mA,           | -                  | -      | V <sub>SS</sub> + 0.25 | V     |

| Output voltage 2         | V <sub>OL4</sub>  | V <sub>DD</sub> = 3V                                                       | INTN pin                         | -                  | -      | V <sub>SS</sub> + 0.4  | V     |

| Output leakage current   | l <sub>OZ</sub>   | V <sub>OUT</sub> = V <sub>DD</sub> or V <sub>SS</sub> ,<br>DATA, INTN pins |                                  | -0.5               | -      | 0.5                    | μА    |

## **Oscillator Characteristics**

$Ta = 25 ^{\circ}C, C_G = 10 pF, X'tal = NPC \ reference \ crystal \ (C_I = 30 k\Omega, C_L = 6 pF) \ unless \ otherwise \ noted.$

| Parameter                        | Symbol              | Condition                     |     | Unit |     |       |

|----------------------------------|---------------------|-------------------------------|-----|------|-----|-------|

| raiailietei                      | Symbol              | Condition                     | min | typ  | max | Oill  |

| Oscillator startup time          | T <sub>STA</sub>    | V <sub>DD</sub> = 1.6V        | -   | -    | 5.0 | S     |

| Oscillator stop voltage          | V <sub>STO</sub>    |                               | -   | -    | 1.5 | ٧     |

| Frequency voltage characteristic | f/V                 | V <sub>DD</sub> = 1.6 to 5.5V | -2  | -    | 2   | ppm/V |

| Frequency accuracy               | $\epsilon_{\sf IC}$ | V <sub>DD</sub> = 5.0V        | -10 | -    | 10  | ppm   |

| Output capacitance               | C <sub>D</sub>      | V <sub>DD</sub> = 5.0V        | -   | 15   | -   | pF    |

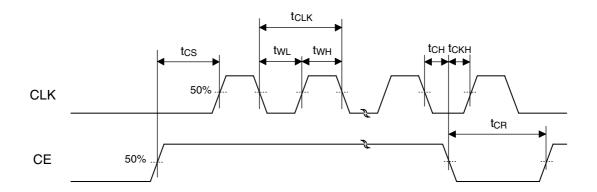

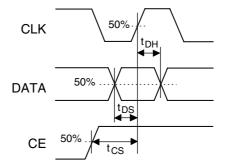

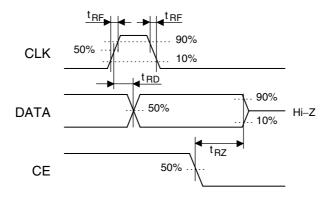

## **AC Characteristics**

$V_{SS} = 0V$ , Ta = -40 to +85°C unless otherwise noted.

| Parameter                           | Symbol           | Symbol Condition                  |     | <sub>D</sub> = 5.0V ± 1 | 0%  | V <sub>D</sub> | <sub>D</sub> = 3.0V ± 1 | 0%  | Unit |

|-------------------------------------|------------------|-----------------------------------|-----|-------------------------|-----|----------------|-------------------------|-----|------|

| Faranieter                          | Syllibol         | Condition                         | min | typ                     | max | min            | typ                     | max | UIII |

| CLK clock cycle                     | t <sub>CLK</sub> |                                   | 600 | -                       | -   | 1200           | -                       | -   | ns   |

| CLK HIGH-level pulsewidth           | t <sub>WH</sub>  |                                   | 300 | -                       | -   | 600            | -                       | -   | ns   |

| CLK LOW-level pulsewidth            | t <sub>WL</sub>  |                                   | 300 | -                       | -   | 600            | -                       | -   | ns   |

| CE setup time                       | t <sub>CS</sub>  |                                   | 150 | -                       | -   | 300            | -                       | -   | ns   |

| CE hold time                        | t <sub>CH</sub>  |                                   | 200 | -                       | -   | 400            | -                       | -   | ns   |

| CE recovery time                    | t <sub>CR</sub>  |                                   | 300 | -                       | -   | 600            | -                       | -   | ns   |

| CLK hold time                       | t <sub>CKH</sub> |                                   | 50  | -                       | -   | 100            | -                       | -   | ns   |

| Write data setup time               | t <sub>DS</sub>  |                                   | 50  | -                       | -   | 100            | -                       | -   | ns   |

| Write data hold time                | t <sub>DH</sub>  |                                   | 50  | -                       | -   | 100            | -                       | -   | ns   |

| Read data output delay time         | t <sub>RD</sub>  | C <sub>L</sub> = 50pF             | -   | -                       | 200 | -              | -                       | 400 | ns   |

| Output disable delay time           | t <sub>RZ</sub>  | $C_L = 50pF$<br>$R_L = 10k\Omega$ | -   | -                       | 100 | -              | -                       | 200 | ns   |

| Input rise and fall time            | t <sub>RF</sub>  |                                   | -   | -                       | 20  | -              | -                       | 40  | ns   |

| Abnormal oscillation detection time | tosc             |                                   | 10  | -                       | -   | 10             | -                       | -   | ms   |

# **Timing Diagrams**

## Data write

### Data read

## **FUNCTIONAL DESCRIPTION**

# **Register Table**

| Address | Function            | Bit7 | Bit6 | Bit5 | Bit4  | Bit3 | Bit2 | Bit1 | Bit0 | Read | Write       |

|---------|---------------------|------|------|------|-------|------|------|------|------|------|-------------|

| 0       | Second              | FOS  | 40   | 20   | 10    | 8    | 4    | 2    | 1    | Yes  | Yes         |

| 1       | Minute              | fr   | 40   | 20   | 10    | 8    | 4    | 2    | 1    | Yes  | Excl. bit 7 |

| 2       | Hour                | fr   | *    | 20   | 10    | 8    | 4    | 2    | 1    | Yes  | Excl. bit 7 |

| 3       | Day-of-week         | fr   | 6    | 5    | 4     | 3    | 2    | 1    | 0    | Yes  | Excl. bit 7 |

| 4       | Day                 | fr   | *    | 20   | 10    | 8    | 4    | 2    | 1    | Yes  | Excl. bit 7 |

| 5       | Month               | fr   | *    | *    | 10    | 8    | 4    | 2    | 1    | Yes  | Excl. bit 7 |

| 6       | Year                | 80   | 40   | 20   | 10    | 8    | 4    | 2    | 1    | Yes  | Yes         |

| 7       | Minute alarm        | AE   | 40   | 20   | 10    | 8    | 4    | 2    | 1    | Yes  | Yes         |

| 8       | Hour alarm          | AE   | *    | 20   | 10    | 8    | 4    | 2    | 1    | Yes  | Yes         |

| 9       | Day-of-week alarm   | AE   | 6    | 5    | 4     | 3    | 2    | 1    | 0    | Yes  | Yes         |

| Α       | Day alarm           | AE   | *    | 20   | 10    | 8    | 4    | 2    | 1    | Yes  | Yes         |

| В       | Frequency           | FE   | *    | FD4  | FD3   | *    | FD2  | FD1  | FD0  | Yes  | Yes         |

| С       | Fixed cycle         | TE   | *    | TD1  | TD0   | *    | *    | *    | *    | Yes  | Yes         |

| D       | Fixed-cycle counter | 128  | 64   | 32   | 16    | 8    | 4    | 2    | 1    | Yes  | Yes         |

| Е       | Control 1           | *    | *    | *    | TI/TP | AF   | TF   | AIE  | TIE  | Yes  | Yes*1       |

| F       | Control 2           | *    | TEST | *    | RESET | HOLD | *    | *    | *    | Yes  | Yes         |

<sup>\*1.</sup> The AF and TF bits have "0" only valid write data values.

Note 1. When power is applied, all register values are undefined, hence they must be initialized.

Note 2. When Register D is read, the previously preset data value written to the register is read.

### Clock and Calendar Registers (Registers 0 to 6)

- Data is in BCD format. For example, register 0 data "0101 1001" represents the value 59 seconds. Also, "\*"-entries in the register table represent read/write locations that can be used as RAM.

- Clock timing is in 24-hour mode.

- Year register and leap year:

The year register represents years as 2 digits, with 00 following year 99. Leap years are automatically identified for years up to 2099.

■ Day-of-week register:

The day-of-week register is a 7-bit register (bits 0 to 6) with valid values shown in the following table. Note that a register setting with a multiple number of "1" bits is invalid.

| Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | Day-of-week |

|------|------|------|------|------|------|------|-------------|

| 0    | 0    | 0    | 0    | 0    | 0    | 1    | Sunday      |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | Monday      |

| 0    | 0    | 0    | 0    | 1    | 0    | 0    | Tuesday     |

| 0    | 0    | 0    | 1    | 0    | 0    | 0    | Wednesday   |

| 0    | 0    | 1    | 0    | 0    | 0    | 0    | Thursday    |

| 0    | 1    | 0    | 0    | 0    | 0    | 0    | Friday      |

| 1    | 0    | 0    | 0    | 0    | 0    | 0    | Saturday    |

#### ■ FOS (Abnormal Oscillation Detection Bit)

This flag reports oscillation abnormalities during normal operation, such as may occur when the supply voltage falls too low, for example. It is set to "1" to indicate abnormal oscillation, and maintains this value until a "0" bit is written. It is not affected by the function of any other bits.

#### ■ fr (Read Flags)

When CE is HIGH, these flags are set to "1" when the 1s seconds digit is incremented. They are set to "0" when CE goes LOW. This makes it possible to determine whether the 1s seconds digit has been incremented during a clock register read-out operation (when CE is HIGH). If the fr bits are set to "1", all the clock timing registers should be read again.

The seconds and year registers do not have fr flags. Instead, bits 6 and 5 in the seconds register and bits 7 and 6 in the year register are logically-Ored with data "1" (example: year register  $00101001 \rightarrow 11101001$ ). When CE goes LOW, the register values are restored (example: year register  $11101001 \rightarrow 00101001$ ).

### Alarm Registers (Registers 7 to A)

- These registers contain the alarm interrupt time setting. When the alarm matches the clock registers, the INTN output goes LOW (if the alarm interrupt enable AIE bit is set to 1).

- The alarm can be set for day-of-week, day, hour and minute.

Bit 7 of each of the alarm registers is an enable alarm AE bit. These bits can be used to implement repetitive alarms, such as for every hour or every day.

- The day-of-week alarm can optionally be set for multiple alarms.

Correct alarm output may not occur if the only alarm setting is a day-of-week alarm.

- When the AE bit is set to 0, the alarm registers are compared with the corresponding clock registers. When set to "1", the data is ignored as don't care bits and is always deemed to match.

- When the AIE bit in register E is set to "0", output on pin INTN is disabled. The TIE and FE bits must be set to "1" and the AIE bit must be set to "0" to enable alarm interrupts.

- Day-of-week alarm bit relationship.

| Bit         | Bit6     | Bit5   | Bit4     | Bit3      | Bit2    | Bit1   | Bit0   |

|-------------|----------|--------|----------|-----------|---------|--------|--------|

| Day-of-week | Saturday | Friday | Thursday | Wednesday | Tuesday | Monday | Sunday |

### **Timer Registers (Registers C to E)**

- These registers control the 8-bit presettable down-counters used for timer interrupts. The counter source clock is assigned by register C, and the counter frequency divider is assigned by register D.

- When the timer count register counts down to zero, with source clock cycle timing, the INTN output goes LOW (if the timer interrupt enable TIE bit is set to "1").

- When the TI/TP bit is set to "1", the fixed-cycle counter register data is reloaded and the count down starts again. Accordingly, this bit can be used to implement an interval timer (periodic mode).

- When the TIE bit in register E is set to "0", output on INTN is disabled.

The TI/TP, FE, AIE, and TIE bits must be set for normal timer operation (with the FE and AIE bits set to "0").

- When data is written to register D, the presettable down counters are updated. The data written to register D is maintained until a subsequent data write is performed, hence this register can be used as RAM, similar to the "\*"- entries in the register table, when timer interrupt mode is not used (when TIE is "0").

- When the TE bit is set to "0", the counter loads the fixed-cycle counter contents and the count stops. When the TE bit is set to "1", the count starts.

- Note that when the TE bit is set to "0", fixed-cycle interrupts from output INTN are not generated even when the fixed-cycle counter (register D) is loaded with zero data.

| TD1 | TD0 | Source clock |

|-----|-----|--------------|

| 0   | 0   | 4096Hz       |

| 0   | 1   | 64Hz         |

| 1   | 0   | 1Hz          |

| 1   | 1   | 1/60Hz       |

### Frequency Setting Register (Register B)

- This register contains the arbitrary frequency setting for output on INTN.

The FD4 and FD3 bits set the frequency divider source clock, and the FD2 to FD0 bits set the frequency divider ratio of the source clock (output frequency = source clock frequency × frequency divider ratio).

The FE bit must be set to "1" to enable frequency output on INTN, with frequency given by the frequency set register (with the AIE and TIE bits set to "0").

- When the FE bit is set to "0", the output is disabled and is high impedance (Hi-Z).

| FD4 | FD3 | Source clock |

|-----|-----|--------------|

| 0   | 0   | 32768Hz      |

| 0   | 1   | 1024Hz       |

| 1   | 0   | 32Hz         |

| 1   | 1   | 1Hz          |

| FD2 | FD1 | FD0 | Frequency divider ratio |

|-----|-----|-----|-------------------------|

| 0   | 0   | 0   | 1/1                     |

| 0   | 0   | 1   | 1/2                     |

| 0   | 1   | 0   | 1/3                     |

| 0   | 1   | 1   | 1/6                     |

| 1   | 0   | 0   | 1/5                     |

| 1   | 0   | 1   | 1/10                    |

| 1   | 1   | 0   | 1/15                    |

| 1   | 1   | 1   | 1/30                    |

### **Control Register 1 (Register E)**

This register controls alarm interrupts and timer interrupts.

| Address | Bit7 | Bit6 | Bit5 | Bit4  | Bit3 | Bit2 | Bit1 | Bit0 |

|---------|------|------|------|-------|------|------|------|------|

| Е       | *    | *    | *    | TI/TP | AF   | TF   | AIE  | TIE  |

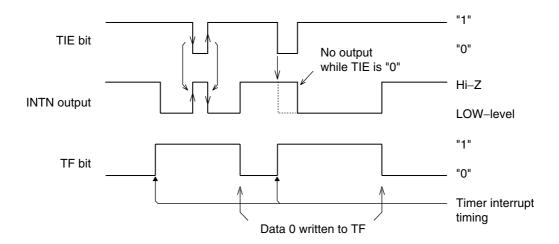

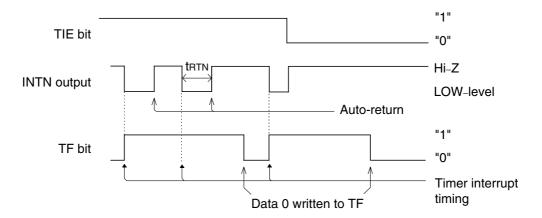

■ TI/TP bit: Interrupt Signal Output Mode Select. Interrupt/Periodic

This selects the timer interrupt signal output mode (with the FE and AIE bits set to "0").

| TI/TP | 0                                                                                                                                                               | 1                                                                                                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode  | <level interrupt="" mode=""> INTN goes LOW immediately when a timer interrupt occurs. INTN remains LOW until the TF bit is set to "0" (with TIE = "1").</level> | <periodic (interval="" interrupt="" interrupt)="" mode=""> INTN goes LOW immediately when a timer interrupt occurs (with TIE = "1"), the TF bit is set to "1", and then INTN becomes high impedance until "0" data is written to the TF bit.</periodic> |

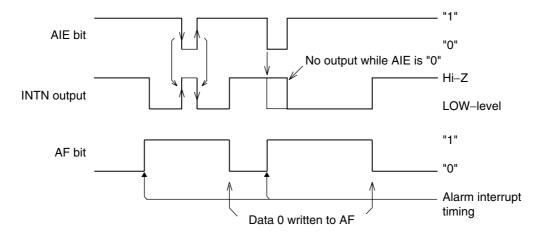

■ AF, TF bits: Alarm Flag, Timer Flag

The AF bit is set to "1" when an alarm occurs, and the TF bit is set to "1" when the timer is zero.

The data bits are maintained until "0" data is written to both bits.

Note that "1" data cannot be written to both bits.

■ AIE, TIE bits: Alarm, Timer Interrupt Enable

These bits determine the output on INTN when alarm or timer interrupt events occur.

AIE is the alarm interrupt enable flag, and TIE is the timer interrupt enable flag.

The alarm or timer interrupt is enabled when the corresponding enable bit is set to "1" (both interrupts are output if both bits are set to "1", so setting both bits to "1" should be avoided).

### **Control Register 2 (Register F)**

This register controls the clock timing frequency divider.

| Address | Bit7 | Bit6 | Bit5 | Bit4  | Bit3 | Bit2 | Bit1 | Bit0 |

|---------|------|------|------|-------|------|------|------|------|

| F       | *    | TEST | *    | RESET | HOLD | *    | *    | *    |

■ TEST bit: NPC Test Bit

This bit should be set to "0" when power is applied and when writing to register F.

■ RESET bit

When this bit is set to "1", the 2kHz to 1Hz frequency divider counters are reset and clock timing stops. After "1" data is written, test mode is cancelled by writing "0" data or by setting the CE input LOW. It is not affected by the state of any other bits.

■ HOLD bit

When this bit is set to "1", the seconds digit increment operation is disabled.

However, if an increment operation occurs when this bit is "1" and the bit is subsequently set to "0" within 1 second, the automatic correction function forces a 1-second correction.

Therefore, it is recommended that the HOLD bit should be used for less than 1 second.

■ Functional operation table

The function of the RESET and HOLD bits is shown in the following table.

| Bit   |      | Function     |                        |                        |                            |  |

|-------|------|--------------|------------------------|------------------------|----------------------------|--|

| RESET | HOLD | Clock timing | Timer interrupt output | Alarm interrupt output | Arbitrary frequency output |  |

| 0     | 0    | Operating    | Operating              | Operating              | Operating                  |  |

| 0     | 1    | *1           | *2                     | Stopped                | Operating                  |  |

| 1     | 0    | Stopped      | *3                     | Stopped                | *4                         |  |

| 1     | 1    | Stopped      | *3                     | Stopped                | *4                         |  |

<sup>\*1.</sup> The automatic correction function operates if the HOLD bit is set for less than 1 second.

<sup>\*2.</sup> Normal operation for source clocks other than 1/60Hz (1 minute).

<sup>\*3.</sup> Normal operation for 4096Hz source clock only.

<sup>\*4.</sup> Normal operation for 32768Hz source clock only.

#### INTERRUPT HANDLING

### **Alarm Interrupt**

- If AIE = 1 when the alarm occurs, output INTN goes LOW. If AIE = 0, INTN is in high impedance state.

- The alarm interrupt is output when the 10s seconds digit carries over to the minutes digit.

### **Timer Interrupt**

■ The TI/TP bit setting selects either level interrupt mode or periodic interrupt mode output (with the AIE and FE bits set to "0").

# (1) Level interrupt mode (TI/TP = "0")

■ If TIE = "1" when the interrupt occurs, output INTN goes LOW. If TIE = "0", INTN is in high impedance state.

# (2) Periodic mode (TI/TP = "1")

- If TIE = "1" when the interrupt occurs, output INTN goes LOW.

- If TIE = "0" when the interrupt occurs, output INTN stays high impedance and the TF bit is set to "1", and this condition is maintained.

\* Auto-return: The auto-return time  $(t_{\mbox{\scriptsize RTN}})$  is determined by the source clock set by register C.

| Source clock | Auto-return time (t <sub>RTN</sub> ) |  |  |

|--------------|--------------------------------------|--|--|

| 4096Hz       | 0.122ms                              |  |  |

| 64Hz         | 7.81ms                               |  |  |

| 1Hz          | 0.5s                                 |  |  |

| 1/60Hz       | 0.122ms                              |  |  |

#### **USAGE NOTES**

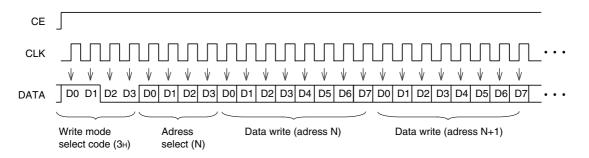

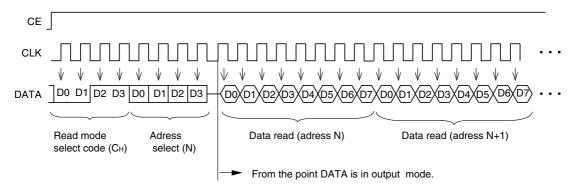

#### Data Read/Write

- For both writing and reading data, the first 4 bits after CE goes HIGH are mode select bits, the next 4 bits assign the address, and subsequent bits are read/write data in 8-bit units.

- When writing data, the data must be input in 8-bit units.

- If CE goes LOW before an 8-bit unit data word is input, the 8-bit data being written when CE goes LOW will not be written correctly.

- Write data and read data are in LSB-first format.

#### [Write mode]

- 1) If the first 4 bits after CE goes HIGH have value "3", write mode is selected. The next 4 bits determine the write address.

- 2) The next 8-bit data unit is written to the write address, and subsequent 8-bit data units are written to consecutive locations addressed using an automatic address increment function.

- 3) The address automatic increment function is cyclical, with address 0 following after address F.

#### [Read mode]

- 1) If the first 4 bits after CE goes HIGH have value "C", read mode is selected. The next 4 bits determine the read address.

- 2) The next 8-bit data unit is read from the read address, and subsequent 8-bit data units are read from consecutive locations addressed using an automatic address increment function.

- 3) The address automatic increment function is cyclical, with address 0 following after address F.

Note. If the mode set code is neither "C" nor "3", all subsequent data is ignored and the DATA pin input state is maintained.

### **Alarm Interrupt**

Alarms can be set for day, day-of-week, hour, and minute. Also, multiple day-of-week alarms can be set. It is recommended that the AF bit and AIE bit be initialized to "0" to avoid unexpected hardware interrupts during the alarm setting procedure. Subsequent alarm data can be set and then the AF flag can be reset to zero for reliable initialization. Then the AIE bit should be set to "1". If hardware interrupts are never used, the AIE should be set to "0" and the AF bit should be monitored using software as necessary.

#### **Example 1) Alarm output for 6pm tomorrow:**

- Write "0" to AIE bit, and "0" to AF bit.

- Write "1" to day alarm AE bit.

- Write register 3's current day-of-week data left-shifted by 1 bit into the day-of-week alarm register. If bit 6 in register 3 is "1", left shift into the fr bit is not allowed. Instead, write "01h" (Sunday).

- Write "18h" to the hour alarm register.

- Write "00h" to the minute alarm register.

- Reset the AF bit to zero.

- Write "1" to the AIE bit.

#### Example 2) Alarm output for 6am every day excluding Saturday and Sunday:

- Write "0" to AIE bit, and "0" to AF bit.

- Write "1" to day alarm AE bit.

- Write "3Eh" to the day-of-week alarm register.

- Write "06h" to the hour alarm register.

- Write "00h" to the minute alarm register.

- Reset the AF bit to zero.

- Write "1" to the AIE bit.

#### **Interrupt Output (INTN)**

- The INTN output mode can be selected, by internal mode setting, for timer interrupt output, alarm interrupt output, or arbitrary frequency output.

- The output mode setting is set by the TIE, AIE, and FE bits as shown in the following table. Note that multiple "1" bits are invalid.

| Mode                       | Bit |     |    |  |  |

|----------------------------|-----|-----|----|--|--|

| Wode                       | TIE | AIE | FE |  |  |

| Timer interrupt output     | 1   | 0   | 0  |  |  |

| Alarm interrupt output     | 0   | 1   | 0  |  |  |

| Arbitrary frequency output | 0   | 0   | 1  |  |  |

| Output disabled            | 0   | 0   | 0  |  |  |

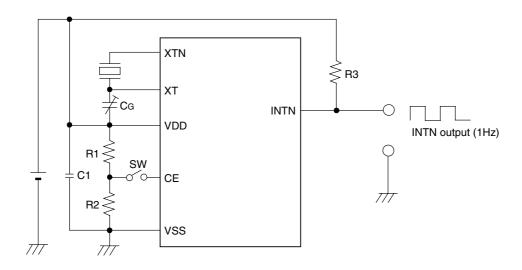

# **Monitoring Oscillator Frequency**

A 1Hz signal is output from INTN when input CE is biased to  $1/2V_{\mbox{\scriptsize DD}}$ .

By monitoring this output, the oscillator frequency can be adjusted by tuning an external capacitor (C<sub>G</sub>).

$\begin{aligned} &R1 = R2 \ (\approx 10 k\Omega) \\ &R3 \approx 10 k\Omega \\ &C1 \approx 0.1 \mu F \end{aligned}$

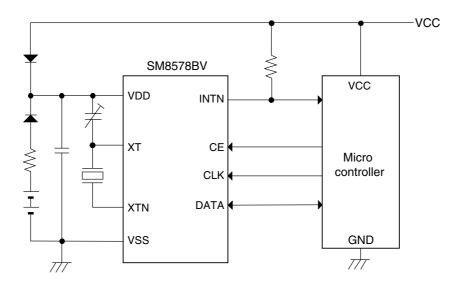

## **TYPICAL APPLICATION CIRCUIT**

Please pay your attention to the following points at time of using the products shown in this document.

The products shown in this document (hereinafter "Products") are not intended to be used for the apparatus that exerts harmful influence on human lives due to the defects, failure or malfunction of the Products. Customers are requested to obtain prior written agreement for such use from NIPPON PRECISION CIRCUITS INC. (hereinafter "NPC"). Customers shall be solely responsible for, and indemnify and hold NPC free and harmless from, any and all claims, damages, losses, expenses or lawsuits, due to such use without such agreement. NPC reserves the right to change the specifications of the Products in order to improve the characteristic or reliability thereof. NPC makes no claim or warranty that the contents described in this document dose not infringe any intellectual property right or other similar right owned by third parties. Therefore, NPC shall not be responsible for such problems, even if the use is in accordance with the descriptions provided in this document. Any descriptions including applications, circuits, and the parameters of the Products in this document are for reference to use the Products, and shall not be guaranteed free from defect, inapplicability to the design for the mass-production products without further testing or modification. Customers are requested not to export or re-export, directly or indirectly, the Products to any country or any entity not in compliance with or in violation of the national export administration laws, treaties, orders and regulations. Customers are requested appropriately take steps to obtain required permissions or approvals from appropriate government agencies.

#### NIPPON PRECISION CIRCUITS INC.

4-3, Fukuzumi 2-chome, Koto-ku, Tokyo 135-8430, Japan Telephone: +81-3-3642-6661 Facsimile: +81-3-3642-6698 http://www.npc.co.jp/ Email: sales@npc.co.jp

NC9619DE 2004.10