# Bluetooth<sup>™</sup> Radio

# **Key features**

- A small cost effective class 2 Bluetooth radio

- Forms a complete radio with only an antenna and a reference frequency

- Very high out-band blocking in all GSM bands

- Excellent high signal level performance in-band

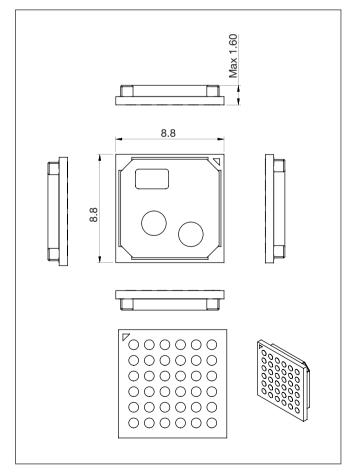

- Small LGA package (8.8×8.8×1.6 mm)

- Prequalified for Bluetooth specification 1.1

- Requires no external shielding

## Description

The Bluetooth Radio PBA 313 05 from Ericsson Microelectronics is a short-range microwave frequency radio transceiver for Bluetooth communication links. Provided in a compact LGA package. No external shield is required.

The Bluetooth Radio offers a combination of compact size, low power consumption, and cost effective assembly. The PBA 313 05 forms a complete radio with only the addition of an antenna, a 13 MHz reference frequency crystal, and a digital control functionality. As a result, designers can benefit from a pre-tested and ready-to-use device, providing a robust Bluetooth Radio function in the final OEM application.

PBA 313 05 is built around an RFCMOS ASIC. Antenna filter, RX and TX baluns are all integrated into the circuit. The antenna filter is specially designed for application in GSM environment such as inside a mobile phone. The Radio PBA 313 05 also has a very high threshold for high signal levels in-band, which makes it very suitable to be in an IEEE 802.11b environment. Operating from a 2.6 V supply, the module has a typical supply current consumption of only 50 mA (receive mode) or 60 mA (transmit mode), thus helping to extend battery life for portable equipment. Standby mode provides further power savings.

#### Suggested applications

- Mobile phones

- PDA

- Modems

- Laptop computers

- Handheld equipment

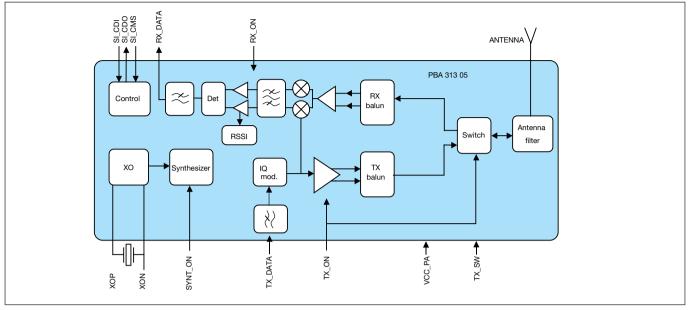

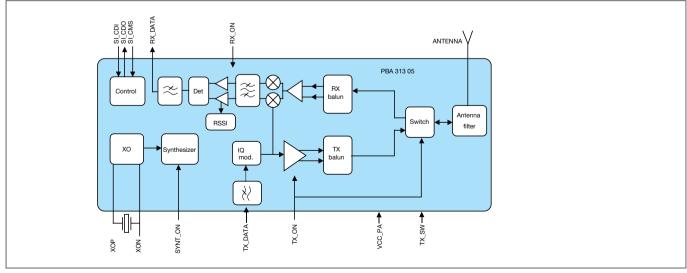

# **Block diagram**

Figure 1. Block diagram.

# Absolute maximum ratings

| Parameter                  |               | Symbol | Min  | Тур | Max  | Unit |

|----------------------------|---------------|--------|------|-----|------|------|

| Temperature                |               |        |      |     |      |      |

| Storage temperature        |               |        | -40  |     | +100 | °C   |

| Operating temperature      |               |        | -20  |     | +75  | °C   |

| Power Supply               |               |        |      |     |      |      |

| Supply voltage             |               |        | 2.5  |     | 2.75 | V    |

| Applied voltage of non-sup | ply pins      |        | -0.2 |     | 3.3  | V    |

| Applied voltage of XO_P    |               |        | -0.2 |     | 2.75 | V    |

| Applied voltage of XO_N    |               |        | -0.2 |     | 2.75 | V    |

| Input RF power             | - In-band     |        |      |     | 15   | dBn  |

|                            | - Out of band |        |      |     | 15   | dBn  |

## **Electrical characteristics**

Unless otherwise noted, the specification applies for  $T_{amb} = 25^{\circ}C$ ,  $V_{DD} = 2.6$  V,  $f_{ref} = 13$  MHz  $\pm 10$  ppm,  $V_{ppref} = 0.8$ , VSWR  $\leq 2:1$

#### **Operating Conditions**

| Parameter                                         |           |                       | Min                 | Тур      | Max                 | Unit     |

|---------------------------------------------------|-----------|-----------------------|---------------------|----------|---------------------|----------|

| Frequency range                                   |           |                       | 2.400               |          | 2.480               | GHz      |

| Reference clock frequency (f <sub>EXT_CLK</sub> ) |           |                       | 12.99974            | 13.00000 | 13.00026            | MHz      |

| Reference clock amplitude                         |           |                       | 0.200               |          | 2.0                 | $V_{PP}$ |

| Reference clock phase noise                       | ∆f=2.5kHz |                       |                     |          | -100                | dBc/     |

| Hz                                                |           | $\Delta f \ge 15 kHz$ |                     |          |                     | -110     |

| dBc/Hz                                            |           |                       |                     |          |                     |          |

| Supply voltage (V <sub>DD</sub> )                 |           |                       | 2.5                 |          | 2.75                | V        |

| Applied voltage of non-supply pins                |           |                       | 0.2                 |          | 3.3                 | V        |

| Output matching of ANT pin (VSWR)                 |           |                       |                     |          | 2:1                 |          |

| Logical high input                                |           |                       | 0.7*V <sub>DD</sub> |          | 3.3                 | V        |

| Logical low input                                 |           |                       | -0.2                |          | 0.3*V <sub>DD</sub> | V        |

| Rise/fall time of all digital inputs              |           |                       |                     |          | 4                   | ns       |

| Clock frequency of SI_CLK                         |           |                       |                     |          | 4                   | MHz      |

| Positive period of SI_CLK                         |           |                       | 76                  |          |                     | ns       |

| Ambient temperature (T <sub>Amb</sub> )           |           |                       | -20                 | +25      | +75                 | °C       |

# **DC** specifications

| Parameter                          |                            | Min    | Тур             | Max    | Unit |

|------------------------------------|----------------------------|--------|-----------------|--------|------|

| Power Supply                       |                            |        |                 |        |      |

| Supply Current                     | - Sleep mode <sup>1)</sup> |        | 70              | TBD    | μΑ   |

|                                    | - Synt mode                |        | 35              | TBD    | mA   |

|                                    | - Transmit mode            |        | 60              | TBD    | mA   |

|                                    | - Receive mode             |        | 50              | TBD    | mA   |

| Capacitance of digital inputs      |                            |        | 10              |        | pF   |

| XO_N input capacitance             |                            |        | 3               |        | pF   |

| XO_P input capacitance             |                            |        | 3               |        | pF   |

| Input leakage current              |                            |        | 5               |        | μΑ   |

| Rise/fall time of all digital outp | uts <sup>2)</sup>          |        | 40              |        | ns   |

| Logical high output                |                            |        | V <sub>DD</sub> |        | V    |

| Logical low output                 |                            |        | 0               |        | V    |

| SYS_CLK frequency                  |                            |        | 13              |        | MHz  |

| TX_CLK frequency                   |                            |        | 1               |        | MHz  |

| LPO_CLK frequency                  |                            | 3.1992 | 3.2             | 3.2008 | kHz  |

Average current the first second after shut down.

Driving a 10 pF load.

#### **RF** specifications

All parameters are guaranteed when measured according to the Bluetooth test specification.

| Parameter                               |                              | Min | Тур | Max | Unit |

|-----------------------------------------|------------------------------|-----|-----|-----|------|

| Receiver performance, BER =             | 0.1 %,                       |     |     |     |      |

| Sensitivity level                       |                              |     | -80 | -75 | dBm  |

| Max input level                         |                              | 5   | 15  |     | dBm  |

| RSSI value                              | P <sub>in</sub> ≥ -40 dBm    | 39  | 43  | 47  |      |

|                                         | P <sub>in</sub> ≤ -60 dBm    | 16  | 20  | 24  |      |

| Co-Channel interference, C/Ico-c        |                              |     | 11  | dB  |      |

| Adjacent (1 MHz) interference, 0        |                              |     | 0   | dB  |      |

| Adjacent (2 MHz) interference, (        |                              |     | -30 | dB  |      |

| Adjacent (3 MHz) interference, (        |                              |     | -40 | dB  |      |

| Image frequency (-4 MHz) interf         |                              |     | -9  | dB  |      |

| Adjacent (1 MHz) interference to        |                              |     | -20 | dB  |      |

| frequency, C/I <sub>image±1MHz</sub>    |                              |     |     |     |      |

| Out-of-band blocking                    | 30-880 MHz <sup>4)</sup>     | 4   | TBD |     | dBm  |

|                                         | 880-1785 MHz <sup>4)</sup>   | 5   |     |     | dBm  |

|                                         | 1785-1910 MHz <sup>4)</sup>  | 4   |     |     | dBm  |

|                                         | 1910-1980 MHz <sup>4)</sup>  | 3   |     |     | dBm  |

|                                         | 1980-2000 MHz <sup>4)</sup>  | -10 |     |     | dBm  |

|                                         | 2000-2004 MHz <sup>4)</sup>  | -27 |     |     |      |

|                                         | 2497-3000 MHz 4)             | -27 |     |     |      |

|                                         | 3000-12750 MHz <sup>4)</sup> | -10 |     |     | dBm  |

| Intermodulation rejection <sup>5)</sup> |                              | -32 | TBD |     | dBm  |

| Spurious Emissions                      | 30 MHz – 1 GHz               |     |     | -57 | dBm  |

|                                         | 1 GHz – 12.75 GHz            |     |     | -47 | dBm  |

# PBA 313 05

#### RF specifications continued.

| Parameter                         |                    | Min | Тур | Max  | Unit     |

|-----------------------------------|--------------------|-----|-----|------|----------|

| Transmitter Performance           |                    |     |     |      |          |

| Output power                      |                    | -2  |     | 4    | dBm      |

| Frequency deviation <sup>6)</sup> |                    | 140 | 159 | 175  | kHz      |

| Initial frequency error           |                    | -48 | 0   | 48   | kHz      |

| TX carrier drift                  | 1 slot             | -25 |     | 25   | kHz      |

|                                   | 3 slots            | -40 |     | 40   | kHz      |

|                                   | 5 slots            | -40 |     | 40   | kHz      |

|                                   | idle               | -40 |     | 40   | kHz      |

| Drift rate                        |                    | -20 |     | 20   | kHz/50μs |

| 20 dB-bandwidth with peak det     | ector              |     |     | 1000 | kHz      |

| Adjacent channel power            | ±2 MHz             |     |     | -20  | dBm      |

|                                   | ±3 MHz             |     |     | -40  | dBm      |

|                                   | ±4 MHz             |     |     | -40  | dBm      |

|                                   | ±13 MHz            |     |     | -40  | dBm      |

| Spurious emission                 | 30 MHz – 1 GHz     |     |     | -36  | dBm      |

|                                   | 1 GHz – 12.75 GHz  |     |     | -30  | dBm      |

|                                   | 1.8 GHz – 1.9 GHz  |     |     | -47  | dBm      |

|                                   | 5.15 GHz – 5.3 GHz |     |     | -47  | dBm      |

<sup>3)</sup> Carrier signal level of -60 dBm, interferer Bluetooth modulated.

<sup>4)</sup> Carrier signal at 2460 MHz with a level of -67 dBm , Continuous Wave (CW) interferer.

<sup>5)</sup> Carrier: -64 dBm @ 2441 MHz, 1<sup>st</sup> interferer: CW @ 2446 MHz, 2<sup>nd</sup> interferer: BT mod. @ 2451 MHz.

<sup>6)</sup> Measured differentially.

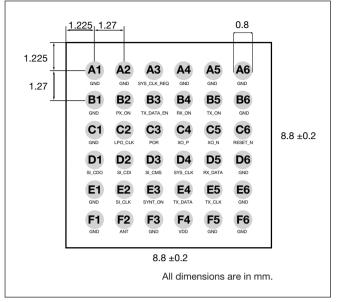

| Pin | x      | У     | Pin | X      | У      | Pin | x      | У      |

|-----|--------|-------|-----|--------|--------|-----|--------|--------|

| A1  | -3.175 | 3.175 | C1  | -3.175 | 0.635  | E1  | -3.175 | -1.905 |

| A2  | -1.905 | 3.175 | C2  | -1.905 | 0.635  | E2  | -1.905 | -1.905 |

| A3  | -0.635 | 3.175 | C3  | -0.635 | 0.635  | E3  | -0.635 | -1.905 |

| A4  | 0.635  | 3.175 | C4  | 0.635  | 0.635  | E4  | 0.635  | -1.905 |

| A5  | 1.905  | 3.175 | C5  | 1.905  | 0.635  | E5  | 1.905  | -1.905 |

| A6  | 3.175  | 3.175 | C6  | 3.175  | 0.635  | E6  | 3.175  | -1.905 |

| B1  | -3.175 | 1.905 | D1  | -3.175 | -0.635 | F1  | -3.175 | -3.175 |

| B2  | -1.905 | 1.905 | D2  | -1.905 | -0.635 | F2  | -1.905 | -3.175 |

| B3  | -0.635 | 1.905 | D3  | -0.635 | -0.635 | F3  | -0.635 | -3.175 |

| B4  | 0.635  | 1.905 | D4  | 0.635  | -0.635 | F4  | 0.635  | -3.175 |

| B5  | 1.905  | 1.905 | D5  | 1.905  | -0.635 | F5  | 1.905  | -3.175 |

| B6  | 3.175  | 1.905 | D6  | 3.175  | -0.635 | F6  | 3.175  | -3.175 |

Table 1.Pad Recommended pad co-ordinates for module PBA 313 05.

Figure 2. Pin numbering LGA.

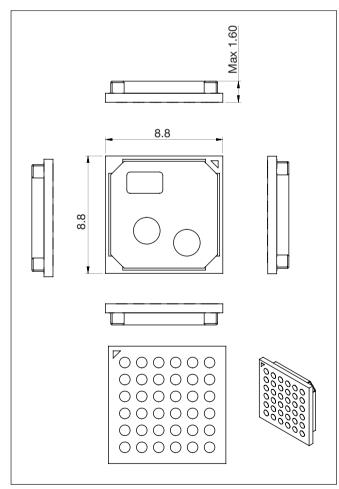

Figure 3. Mechanical dimensions and footprint.

# **Pin description**

| Pin No. | Pin name    | Туре   | Description                                       |

|---------|-------------|--------|---------------------------------------------------|

| A1      | GND         | Ground | Common ground                                     |

| A2      | GND         | Ground | Common ground                                     |

| A3      | SYS_CLK_REQ | D in   | System clock request                              |

| A4      | GND         | Ground | Common ground                                     |

| A5      | GND         | Ground | Common ground                                     |

| A6      | GND         | Ground | Common ground                                     |

| B1      | GND         | Ground | Common ground                                     |

| B2      | PX_ON       | D in   | Packet on                                         |

| B3      | TX_DATA_EN  | D in   | Transmit data enable                              |

| B4      | RX_ON       | D in   | Receiver power on                                 |

| B5      | TX_ON       | D in   | Transmit power on                                 |

| B6      | GND         | Ground | Common ground                                     |

| C1      | GND         | Ground | Common ground                                     |

| C2      | LPO_CLK     | D out  | 3.2 kHz clock                                     |

| C3      | POR         | D out  | Power on reset output                             |

| C4      | XO_P        | A in   | Crystal positive input                            |

| C5      | XO_N        | A in   | Crystal negative input<br>or external clock input |

| C6      | RESET_N     | D in   | External power on reset input                     |

| D1      | SI_CDO      | D out  | Serial data output                                |

| D2      | SI_CDI      | D in   | Serial data input                                 |

| D3      | SI_CMS      | D in   | Serial interface control                          |

| D4      | SYS_CLK     | D out  | System clock 13 MHz                               |

| D5      | RX_DATA     | D out  | Received data output                              |

| D6      | GND         | Ground | Common ground                                     |

| E1      | GND         | Ground | Common ground                                     |

| E2      | SI_CLK      | D in   | Serial interface clock                            |

| E3      | SYNT_ON     | D in   | Synthesizer power on                              |

| E4      | TX_DATA     | D in   | Transmit data                                     |

| E5      | TX_CLK      | D out  | 1 MHz clock                                       |

| E6      | GND         | Ground | Common ground                                     |

| F1      | GND         | Ground | Common ground                                     |

| F2      | ANT         | 50 Ω   | Antenna input/output                              |

| F3      | GND         | Ground | Common ground                                     |

| F4      | VDD         | Power  | Common power supply                               |

| F5      | GND         | Ground | Common ground                                     |

| F6      | GND         | Ground | Common ground                                     |

Table 2. Short description of the PBA 313 05 pin-out. In the Type-column "A" denotes Analog bipolar and "D" Digital CMOS.

# **Functional description**

#### Overview of radio functionality

PBA 313 05 is a radio module requiring minimal external components. The receiver has a heterodyne architecture with low IF. The transmitter utilises an IQ modulation architecture. The block diagram of PBA 313 05 is shown in figure 4.

# Radio ASIC

The receiver consists of a LNA followed by I and Q mixers. The I and Q IF signals of these mixers are fed to an image rejecting selectivity filter. The filter is followed by two limiters (I and Q) fixing the amplitude of the received signal to the required level for the demodulator. The limiters generate an RSSI signal, which is converted to a digital word and is available through the serial interface. The demodulator is an IQ quadrature demodulator. A post detection filter and a slicer, which will output the received data to the baseband processor, follow the demodulator.

The local oscillator is an integrated VCO. The VCO frequency is controlled by means of a phase locked loop. The same VCO is used when receiving and transmitting.

The transmitter utilises IQ modulation. The bit stream from the base band radio is digitally processed to generate gaussian shaped I & Q output. A DAC and reconstruction filter is used to generate the IF input to the mixer. The RF input to the mixer comes from the phase locked VCO via phase shifters and buffering. The mixer output is fed to the PA-driver, which will deliver a nominal 0 dBm output power at the antenna.

There are a number of other circuit blocks such as the crystal oscillator, low power oscillator, power on reset circuit, control logic and the serial interface.

## Loop filter

Generates the tuning voltage for the VCO.

#### RX balun

Transformation from unbalanced (single-ended) to balanced (differential) transmission. The balun is integrated in the substrate.

#### TX balun

Transformation from balanced to unbalanced transmission. The balun is integrated in the substrate.

#### Antenna switch

Directs the power either from the antenna filter to the receive ports or from the external PA output ports to the antenna filter.

#### Antenna filter

Front end bandpass filter fully integrated in the ceramic substrate.

# **I/O Signal Description**

#### **Power supply**

There is one supply connection, VDD. It's important that this supply is properly decoupled and free from noise and other disturbances.

# Oscillator or external clock input (No external load capacitors are required)

XO\_N and XO\_P connect to the crystal's inputs. The load capacitance to the crystal can be trimmed using the XO-Trim register. If an external clock is used, it should be AC coupled into the XO\_N input and the XO\_P input shall be left unconnected.

#### Ground

Ground should be distributed with very low impedance as a ground plane. Connect all GND connections to the ground plane. It is good to have a ground plane underneath the Bluetooth radio in order to shield the module from

Figure 4. PBA 313 05 block diagram

any electrical noise. The purpose of the ground vias is to connect the local ground plane to the main ground layer. The Bluetooth radio will be self shielding and no additional shields should be necessary for normal operating conditions.

#### Antenna

The ANT pin should be connected to a 50  $\Omega$  antenna interface, thereby supporting the best signal strength performance. Ericsson Microelectronics partners can support application specific antennas.

#### Input control

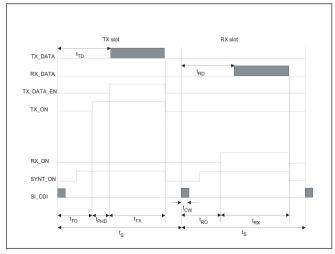

There are five digital inputs available for the radio controlling features of the PBA 313 05. The Bluetooth timing requirements for these are described in table 3 and figure 5. In addition, there is a digital input signal for hardware reset of the radio, and a digital input signal for waking up the clock circuitry after a sleep mode period.

| Symbol | Parameter          | Min | Typical | Max  | Unit |

|--------|--------------------|-----|---------|------|------|

| tS     | One Slot time      |     |         | 625  | μs   |

| tS     | Two Slot times     |     |         | 1875 | μs   |

| tS     | Three Slot times   |     |         | 3125 | μs   |

| tто    | Transmitter On     |     |         |      |      |

|        | delay              |     | 102     |      | μs   |

| tTD    | Delay before       | 203 | 213     |      |      |

|        | transmitting       |     | 104     |      |      |

|        | data               |     |         | 223  | μs   |

| tEN    | Transmit data      |     |         |      |      |

|        | enable delay       |     |         |      |      |

|        | after tTO          |     |         |      | μs   |

| tD     | Data sending       |     |         |      |      |

|        | period, one slot   |     |         | 366  | μs   |

| tD     | Data sending       |     |         | 1598 |      |

|        | period, two slots  | 5   |         |      | μs   |

| tD     | Data sending       |     |         | 2862 |      |

|        | period, three slot | ts  |         |      | μs   |

| tRO    | Receiver On dela   | ay  | 175     | 213  | μs   |

| tRD    | Delay before       |     |         |      |      |

|        | receiving data     |     | 213     |      | μs   |

Table 3. Timing requirements for data transmission.

Figure 5. Timing sequence for data transmission.

#### PX\_ON

Packet switch on control is active 'high'. Activate this signal during reception of a Bluetooth payload.

PX\_ON is used to control the Slicer of the receiver. Since the General Inquiry Access Code (GIAC), information in a Bluetooth packet header contains an equal number of one's (+ $F_{MOD}$ ) and zero's (- $F_{MOD}$ ), the average frequency will always be centred on the carrier frequency. This provides the Slicer the reference for the fast tuning. If the fast mode is not used during the header then the first bits could be interpreted incorrectly.

The slow mode gives a more accurate FSK compensation of the thresholds for a one and a zero compared to the fast mode; therefore, the BER is less. The fast mode (time constant <  $2\mu$ s) is used when PX\_ON is deactivated and the slow mode (time constant < 50 µs) when it is activated.

#### SYNT\_ON

Synthesiser on control is active 'high'. Activate this signal to power up of the VCO section of the radio. SYNT\_ON is used in both transmit and receive mode. This activates the PLL as well as the VCO.

#### RX\_ON

Receive-on control is active 'high'. Activate this signal to enable reception of Bluetooth data on the RX\_DATA pin. The transmit-on control (TX\_ON) must be deactivated and the synthesiser (SYNT\_ON) activated if data is to be received.

#### TX\_ON

Transmit-on control is active 'high'. Activate this signal to enable radio signal output on the ANT pin. The actual transfer of data that exists on the TX\_DATA input occurs when TX\_DATA\_EN goes 'high'. The receive-on control, RX\_ON, must also be 'low' and the transmit-switch, TX\_SW, be held "high" if data is to be transmitted.

#### TX\_DATA\_EN

Enables the modulator thus allowing the input data on TX\_DATA to modulate the carrier in transmit mode. TX\_DATA\_EN is activated after the initialisation of the SYNT\_ON signal and the TX\_ON signal.

#### RESET\_N

External power on reset is active 'high'. An external poweron-reset digital input signal that will reset the radio controller and its registers. A reset will occur on the positive edge of RESET\_N signal. The signal should remain high during operation.

## SYS\_CLK\_REQ

System clock request control is active 'high'. Once the crystal oscillator bit ( $XO_{CTR}$ , control register, bit #2) has been set, use this control to switch off (sleep mode) and wake up (idle and operating modes) the reference clock circuitry and corresponding 13 MHz and 1 MHz clock output ports of the module.

#### **Output control**

There are four digital output control signals available for controlling external baseband circuitry.

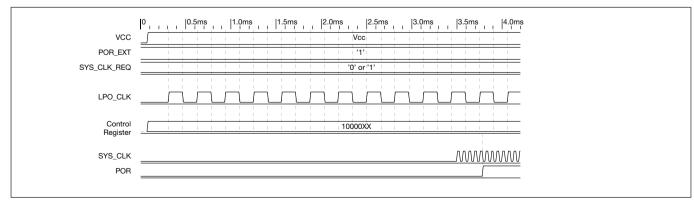

#### POR

Power-on-reset digital output is activated after the power has been applied to the Bluetooth radio or on a positive edge of the POR\_EXT digital input. POR has a transition from 'low' to 'high' after four clock cycles have been delivered to the baseband chip, see figure 6.

#### SYS\_CLK

13 MHz system clock digital output available for the baseband circuitry when the POR\_EXT and SYS\_CLK\_REQ are both 'high'. SYS\_CLK will also be available during start-up, independent on the value of SYS\_CLK\_REQ.

#### TX\_CLK

1 MHz transmit clock digital output available for the baseband circuitry when the POR\_EXT and SYS\_CLK\_REQ (see above) are both 'high'. TX\_CLK changes value on rising edges of SYS\_CLK.

#### LPO\_CLK

3.2 kHz low power oscillator clock digital output. The clock output is available as soon as the power supply is applied and POR\_EXT is 'high'. The LPO is necessary for wake-up timing in the baseband circuitry, if the Ericsson baseband is used.

#### Data interface

Two digital signals are used for data flow over the air interface.

## TX\_DATA

Transmit data digital control is active 'high'. The radio module samples Bluetooth data (1 Mbit/s) after a positive edge on TX\_CLK, feeds it through a digital filter and on to the radio frequency modulator when TX\_DATA\_EN is activated. The total delay from the TX\_DATA pin to the ANT pin is typically 0.5  $\mu$ s.

#### RX\_DATA

Receive data digital output is active 'high'. The radio module

latches out Bluetooth data (1 Mbit/s) on the RX\_DATA pin on falling edges of SYS\_CLK when RX\_ON is activated. The total delay from the ANT pin to the RX\_DATA pin is typically 2.5  $\mu s.$

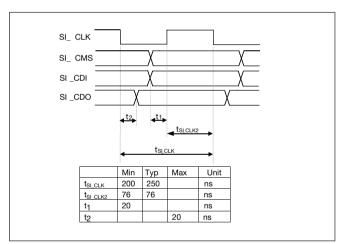

#### Serial interface

The serial control interface is a JTAG Boundary-Scan Architecture (IEEE Std 1149.1). Interconnection between the serial interface and the external controller (baseband circuit) consists of four 1-bit digital signals; control data input (SI\_CDI), control mode select (SI\_CMS), control clock (SI\_CLK) and control data output (SI\_CDO). The timing of these signals is defined in figure 7.

#### Overview

PBA 313 05 is controlled by programming registers via a 4 pin serial interface and a number of dedicated pins to control the receive and transmit sequences.

The serial interface is accessed using pins SI\_CLK, SI\_CMS, SI\_CDO and SI\_CDI. Pins associated with receive and transmit are SYNTH\_ON, TX\_ON, RX\_ON, TX\_DATA\_EN and PX\_ON.

Data to be transmitted is applied to TX\_DATA, received data will be available at RX\_DATA. The radio relies on an accurate 13 MHz reference signal. This signal can be generated by using a 13 MHz crystal on pins XO\_P and XO\_N and

Figure 7. Timing diagram of the serial interface.

Figure 6. Powering up the module.

trimming to the required frequency via the serial interface. Alternatively an externally generated 13 MHz reference can be applied to the XO\_N input, (in this case the oscillator amplifier can be powered down via the serial interface to save power).

A number of clocks are derived from the 13 MHz reference. The LPO output provides a 3.2 kHz reference, which is always available, (this relies either on the use of a crystal or the constant availability of an external 13 MHZ reference). A buffered version of the 13 MHz clock, SYS\_CLK and a 1 MHz derived clock, TX\_CLK are available when the input pin SYS\_CLK\_REQ is asserted.

The radio will generate a power on reset signal when powered up. This will reset all on radio registers to a defined state. The signal will also be present on the POR pin so that it can be used as a system reset signal for the base band processor. The radio can be reset to the default state by applying a '0' at the RESET\_N pin.

#### **Serial interface**

PBA 313 05 contains registers for setting the frequency, storing the value of the signal power etc. The base band processor circuit will read from and write to these registers in PBA 313 05.

The registers are reset to their default values either when EXT\_RESET is low or when the supply is first applied (generating a power on reset signal internally). The serial interface is implemented as described in the BlueRF specification.

Additional information for engineers interfacing PBA 313 05 to a baseband can be found in the Programmers Reference and Base Band Interface Guide PBA 313 05/1.

## Assembly guidelines

#### Solder paste

The PBA 313 05 module is made for surface mounting with land grid array (LGA) solder joints. To assemble the module, solder paste (eutectic Tin/Lead) must be printed at the target surface. Preferred solder paste height is 100-127 $\mu$ m (4-5 mil).

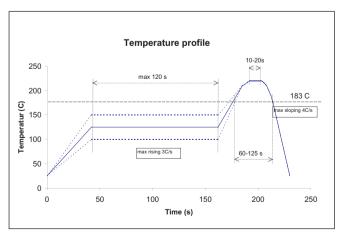

Figure 8. Eutectic SnPb-solder profile.

#### **Soldering profile**

It must be noted that the module should not be allowed to be hanging upside down in the reflow operation. This means that the module has to be assembled on the side of the PCB that is soldered last. The reflow process should be a regular surface mount soldering profile (full convection strongly preferred), the ramp-up should not be higher than 3°C/s and with a peak temperature of 210-225°C during 10-20 seconds. Max sloping rate should not be higher than 4°C/s (see example of reflow profile in figure 8).

#### Placement

The recommended pickup coordinates for the PBA 313 05 shield is based on a nozzle with inner diameter 1.9 mm. From the origin of coordinates, (0,0) for (x,y), the pickup coordinates are (4.4mm, 4.4mm) for (x,y).

#### **Control interface**

Operation together with a Bluetooth Baseband using the Ericsson Bluetooth Core is recommended.

#### Antenna interface

50  $\Omega$  Bluetooth ISM band antenna (2.4 – 2.5 GHz).

Figure 9. Mechanical dimensions and footprint

Information given in this data sheet is believed to be accurate and reliable. No responsibility is assumed for the consequences of its use nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Ericsson Microelectronics. These products are sold only according to Ericsson Microelectronics' general conditions of sale, unless otherwise confirmed in writing. Specifications subject to change without notice.

Ericsson Microelectronics SE-164 81 Kista, Sweden +46 8 757 50 00 www.ericsson.com/microelectronics

For local sales contacts, please refer to our website or call: Int +46 8 757 47 00, Fax: +46 8 757 47 76

#### Preliminary Data Sheet

EN/LZT 146 131 R1B © Ericsson Microelectronics AB, June 2002