Version 1.00

980910EBA1-981021TS

- TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

- The information contained herein is presented only as a guide for the product operation, its functions, and applications. We request that the operation of any application system incorporating this product is fully tested by system vendor.

## Contents

|    | Description                                                |      |

|----|------------------------------------------------------------|------|

| 2. | Feature                                                    |      |

|    | 2.1 Line Interface                                         | 4    |

|    | 2.2 Voice Interface                                        |      |

|    | 2.3 Touch Screen Interface                                 |      |

|    | 2.4 Others                                                 | 4    |

| 3. | System Block Diagram                                       | 5    |

|    | 3.1 Internal System                                        | 6    |

| 4. | Pin Function                                               | 8    |

|    | 4.1 Pin Layout                                             | 8    |

|    | 4.2 Pin Function                                           | 9    |

| 5. | Function                                                   | . 12 |

|    | 5.1 Hardware Interface                                     | . 12 |

|    | 5.2 Hardware Reset                                         | . 13 |

|    | 5.3 Power-down Control                                     | . 14 |

|    | 5.4 Serial Interface                                       | . 16 |

|    | 5.4.1 Pin Function                                         | . 16 |

|    | 5.4.2 Interface Timing                                     | . 17 |

|    | 5.4.3 SIB Data Format                                      | . 18 |

|    | 5.4.4 Handshaking Procedure for the Control Register Field | . 19 |

|    | 5.5 Line and Voice Interface Sample Data Handshake         | . 20 |

|    | 5.5.1 Voice and Telecom Input Data Transfer Timings        | . 22 |

|    | 5.5.2 Voice and Telecom Output Data Transfer Timings       | . 24 |

|    | 5.6 Control Register                                       | . 25 |

|    | 5.6.1 Write Register Map                                   | . 28 |

|    | 5.6.2 Read Register Map                                    | 30   |

|    | 5.7 General I/O Ports                                      | . 32 |

|    | 5.8 Interrupt                                              | . 33 |

|    | 5.9 Telecom Interface                                      | . 37 |

|    | 5.9.1 Functional Description of Analog Echo Canceler       | . 41 |

|    | 5.9.2 Functional Description of Analog Echo Canceler       | . 42 |

|    | 5.9.3 Receive Band-pass Filter Characteristics             | . 43 |

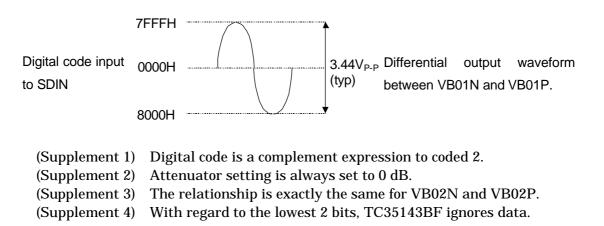

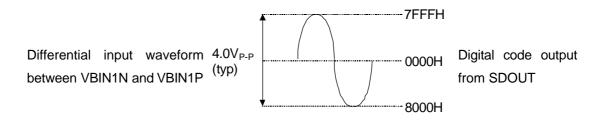

|    | 5.9.4 Relationship Between Analog Signal and Digital Code  | . 45 |

|    | 5.10 Voice Interface                                       |      |

|    | 5.10.1 Configuration of External Microphone Circuit        | 48   |

|    | 5.10.2 Configuration of External Speaker Circuit           |      |

|    | 5.10.3 Voice Interface Receive Filter Characteristics      |      |

|    | 5.10.4 Relationship Between Analog Signal and Digital Code | 56   |

|    | 5.11 Control Register                                      | . 57 |

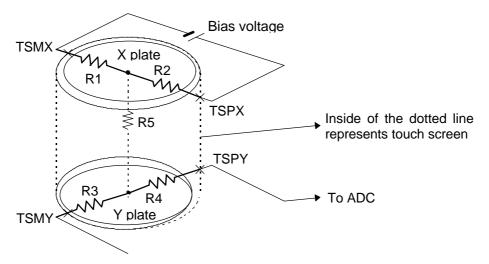

|    | 5.11.1 Principle of Position Measurement                   | 57   |

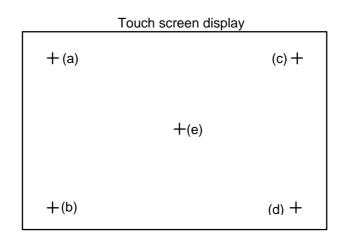

|    | 5.11.2 Principle of Position Calibration                   |      |

|    | 5.11.3 Principle of Contact Detection                      |      |

|    | 5.11.4 Operation Modes and Block Configuration             |      |

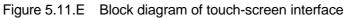

|    | 5.11.5 Control Procedure for Contact Detection             |      |

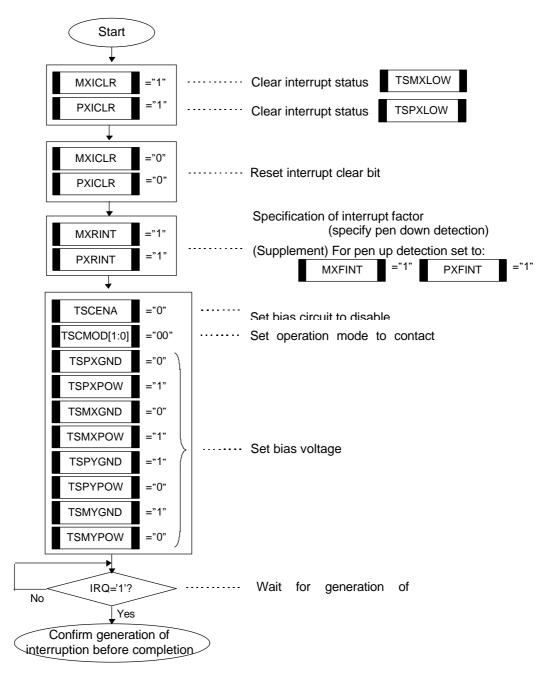

|    | 5.11.6 Control Procedure for Position Measurement          | 68   |

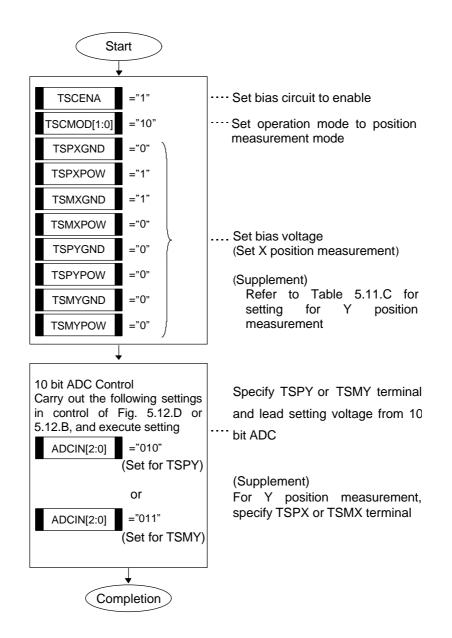

| 5.12 10-bit AD Converter                                   |    |

|------------------------------------------------------------|----|

| 5.12.1 Block Configuration                                 |    |

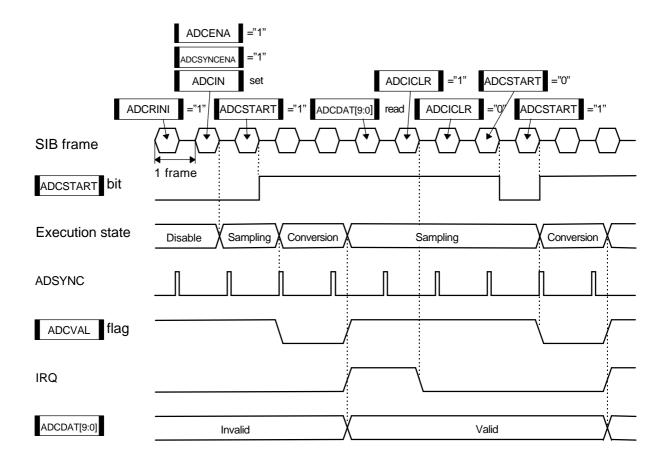

| 5.12.2 ADC Operation Timing                                |    |

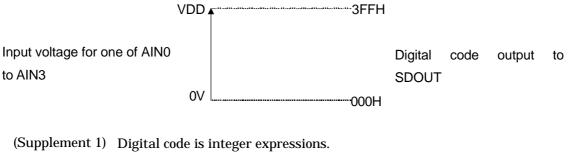

| 5.12.3 Relationship Between Analog Signal and Digital Code |    |

| 5.13 DATE Register                                         |    |

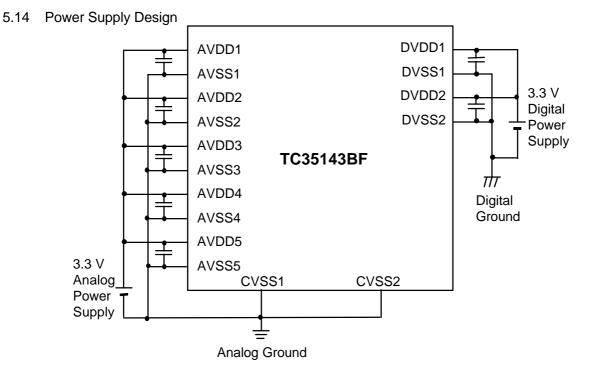

| 5.14 Power Supply Design                                   |    |

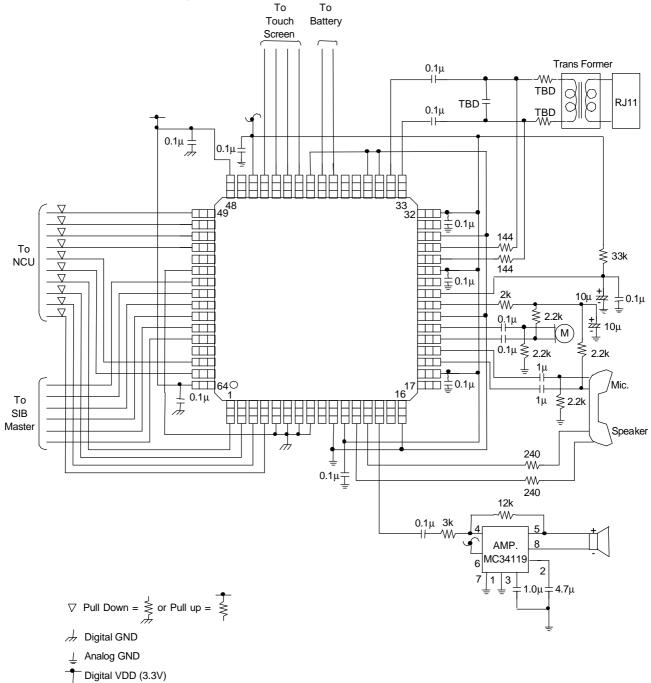

| 5.15 Example Circuit Drawing                               | 80 |

| 6. Electrical Characteristics                              |    |

| 6.1 Absolute Maximum Ratings                               |    |

| 6.2 Recommended Operating Conditions                       |    |

| 6.3 DC Characteristics                                     |    |

| 6.4 AC Characteristics                                     |    |

| 6.4.1 Serial Interface Timing                              |    |

| 6.4.2 Reset Pulse Timing                                   |    |

| 6.4.3 Telecom Interface                                    |    |

| 6.4.4 Voice Interface                                      |    |

| 6.4.5 Touch Screen Interface                               |    |

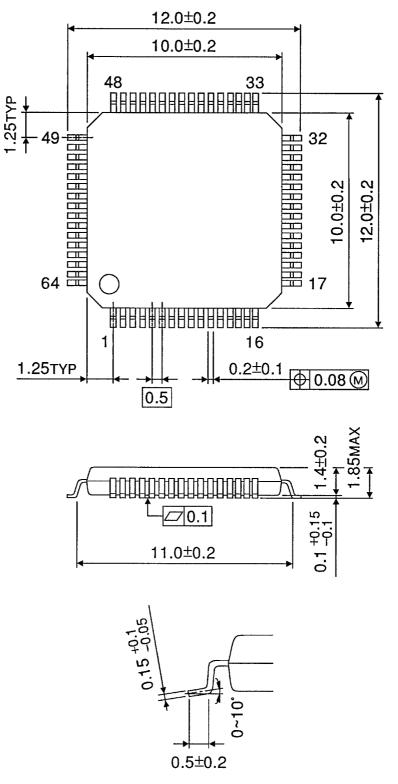

| 7. Outline Drawing                                         | 89 |

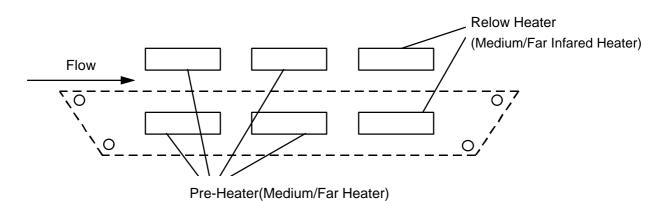

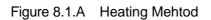

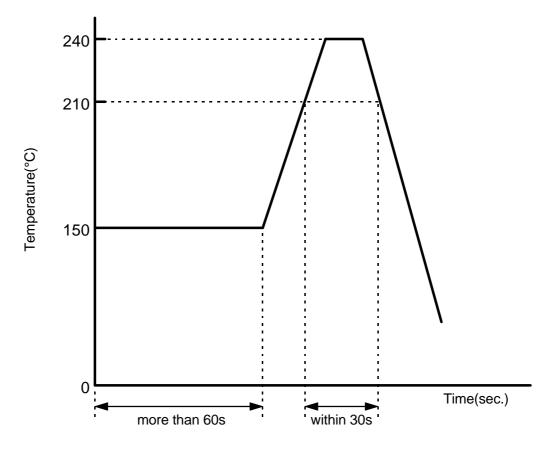

| 8. Reflow                                                  |    |

| 8.1 Method of Solder Reflow                                |    |

| 8.2 Dry Package                                            |    |

|                                                            |    |

### 1. Description

TC35143BF is a suitable analog front end LSI for handy communicator such as an HPC(Handheld PC). This LSI includes a line interface for V.34,V.90 a voice interface which is suitable for hands free/hand set system and a touch screen interface. TC35143BF communicates with a host processor through a serial interface called SIB. A host processor supplies the synchronization clock and shift clock to TC35143BF. Since all clocks of TC35143BF are generated from the shift clock, crystal for TC35143BF is not necessary. ADC/DAC sampling data of each interface, the control data to TC35143BF and the status data from TC35143BF are all transferred through this SIB interface.

LQFP64-P-1010-0.50A

- 2. Feature

- 2.1 Line Interface

- □ 16bit ADC/DAC

- □ Programmable input gain amplifier(2 levels/6dB step)

- $\Box$  ADC clip detector

- □ Differential line driver and receiver

- $\Box$  Analog echo canceler

- □ Programmable sampling frequency (three frequencies : 7.2 kHz, 8 kHz, and 9.6 kHz)

- 2.2 Voice Interface

- □ 14bit ADC/DAC

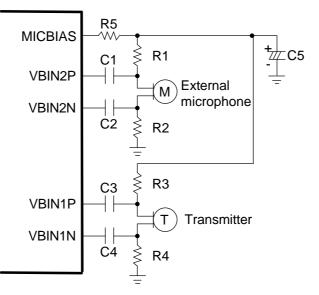

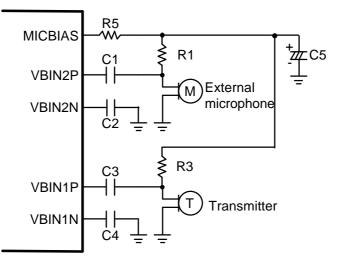

□ 2 channel differential microphone inputs and 2 channel differential speaker outputs (useful for hands-free / handset system)

- □ Enabling/disabling for each block

- □ Mute switches in microphone input pass and speaker output pass

- □ Programmable microphone gain amplifier (15 levels/1.5dB step and 4 levels/6 dB step)

- □ Programmable speaker output attenuator (8 levels/3 dB step)

- □ Programmable sampling frequency

- (four frequencies : 8 kHz / approximately 11.08 kHz / 16 kHz / approximately 22.15 kHz)

- 2.3 Touch Screen Interface

- □ 10bit ADC for voltage measurement

- D Pen touch detection(Available during stand-by mode)

- □ Plate bias voltage generator

- □ Auxiliary analog input ports(4 ports)

- 2.4 Others

- □ 10 channels I/O ports

- □ Multi-chip connectivity via SIB(SIB input frequency is 9.216MHz)

- □ Interrupt output port

- $\Box$  +3.3V single power supply

- □ 64 pin plastic package

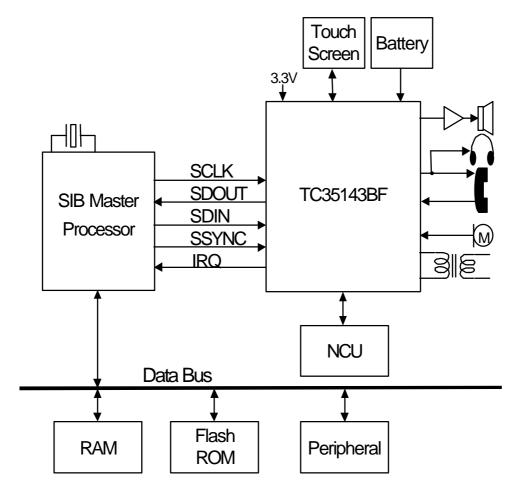

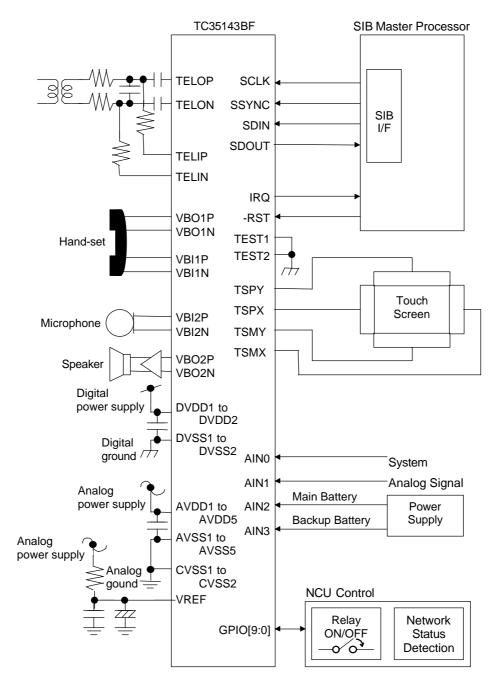

## 3. System Block Diagram

Below figure shows system block diagram using TC35143BF.

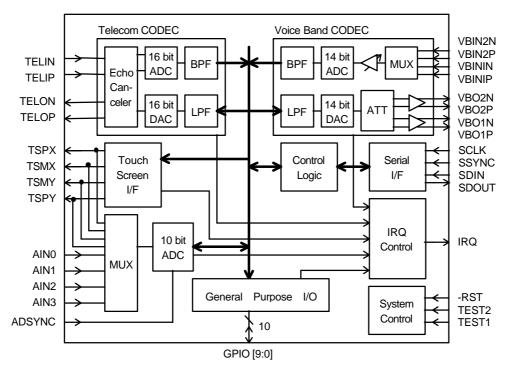

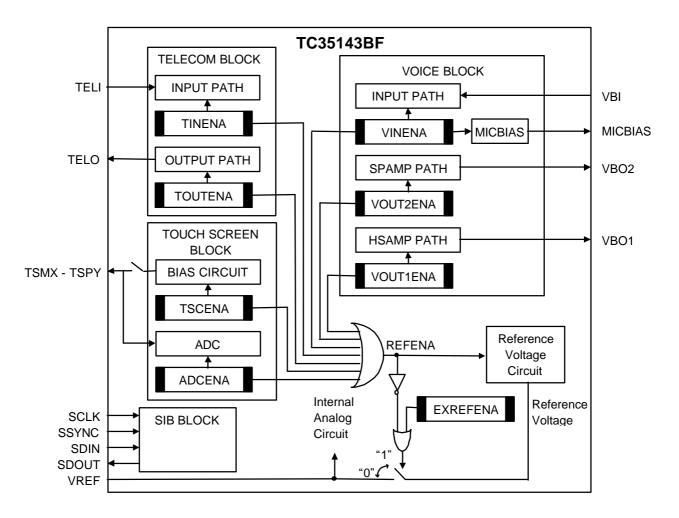

### 3.1 Internal System

The internal system block diagram is shown in the following figure.

Figure 3.1.A TC35143BF block diagram

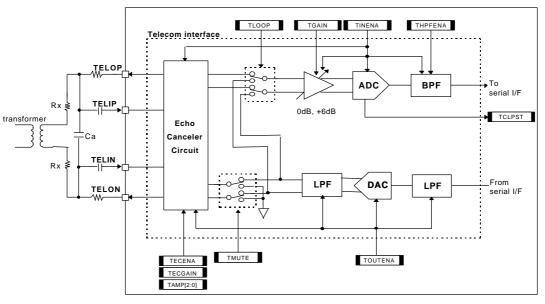

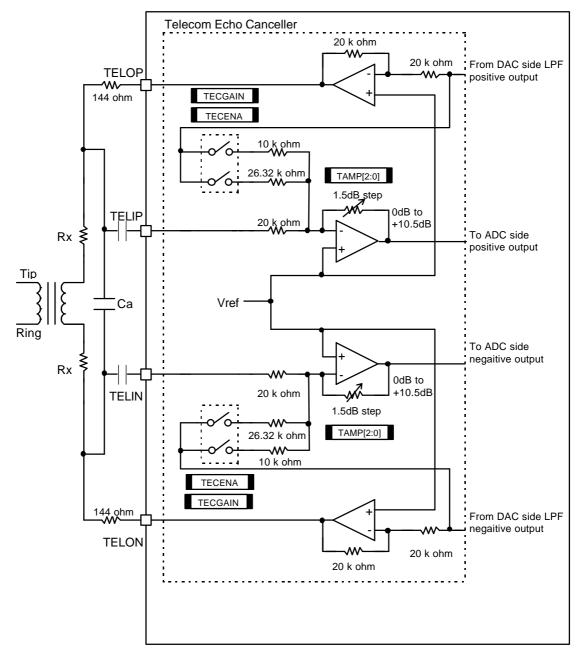

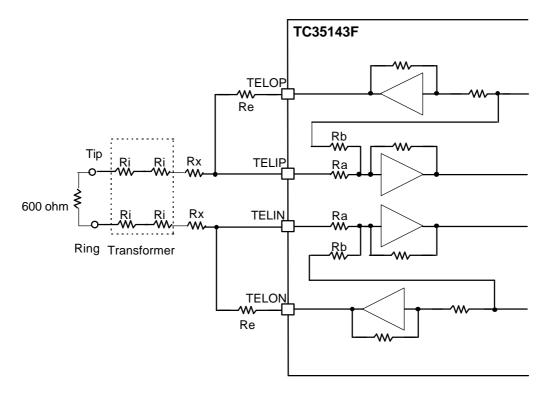

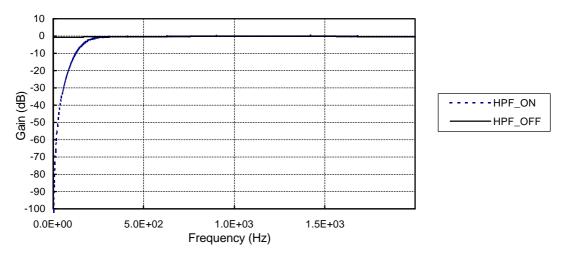

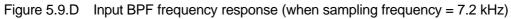

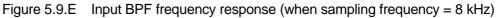

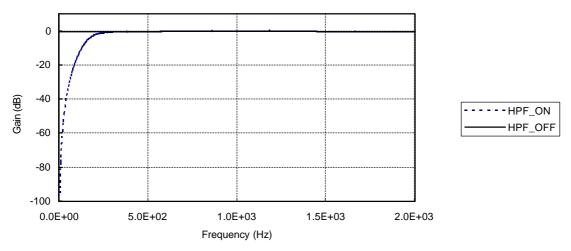

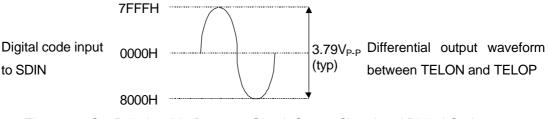

The line interface consists of a 16 bit ADC, a 16 bit DAC, an analog echo canceler for suppression of the telecom output signal and a voice band filter, which consist of an digital band pass filter. The ADC and the DAC have a performance for V.34,V.90 modem communications. Enabling and disabling of high pass filtering of the received band pass filter is useful for detecting several call progress tones. The differential interface extends dynamic range of reception signal. Individual enabling and disabling for the input and the output block save power consumption.

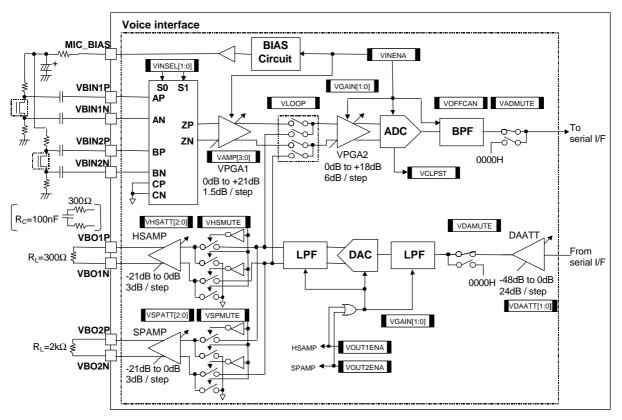

The voice interface is composed of a 14-bit ADC, 14-bit DAC, a digital filter for limiting the bandwidth, and an attenuator for adjusting the input/output levels. The 14-bit ADC and DAC allow you to configure a system featuring superior sound quality. Two channels of input and output pins each are provided for hands-free and handset use. An internal analog switch allows you to choose two channels of microphone input. Two channels of speaker outputs each are provided with an attenuator, so that sound volume on each speaker output can be adjusted independently. The input and output blocks can be powered off individually, making it possible to save power consumption.

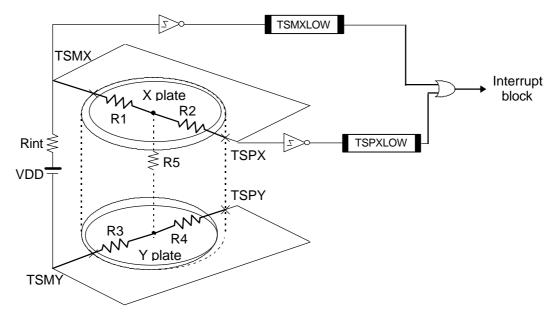

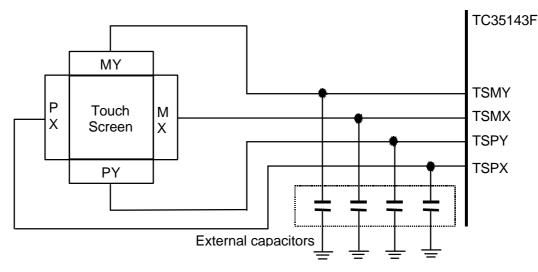

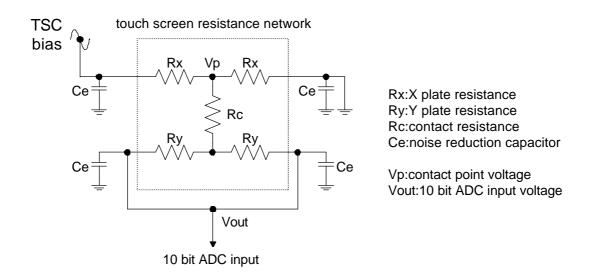

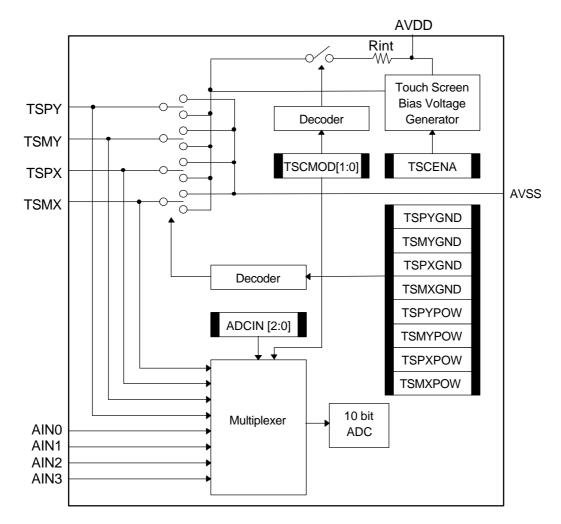

The touch-screen interface controls the bias voltage applied to the touch-screen resistor network and switches over the circuits to measure the voltage of the resistor network. Four pins, TSPX, TSMX, TSMY, and TSPY, are used to apply a bias voltage to the resistor network and read out its measured voltage. The voltage is measured using a 10-bit ADC. An internal switch allows selection of either the touch-screen voltage input or general-purpose voltage input. The four channels of general-purpose voltage inputs can be used to monitor the battery voltage or for other purposes.

Ten general-purpose I/O ports are included as an additional function. These I/O ports can be used to control the NCU, etc.

Control of each block and transfer of sample data all are performed via a serial interface. in description.

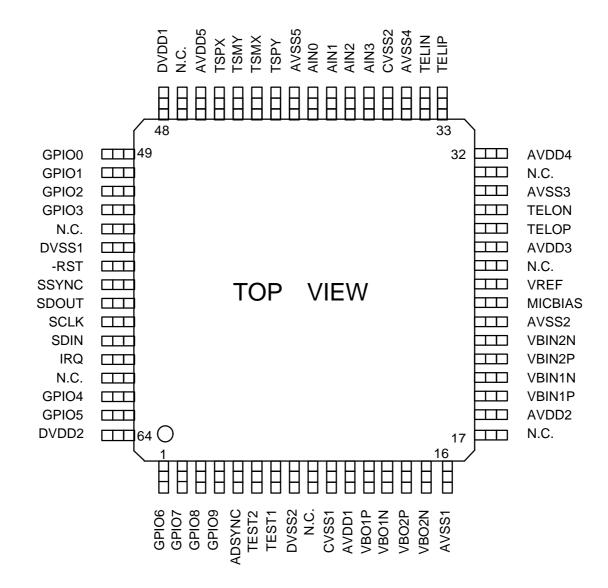

## 4. Pin Function

4.1 Pin Layout

Figure 4.1.A TC35143BF pin layout

### 4.2 Pin Function

| Pin name | Pin No. | A/D/P | I/O | DEF        | Group | Function                                                                                                                                                                                               |

|----------|---------|-------|-----|------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCLK     | 58      | D     |     | -          | HOST  | The bit clock of the host interface. This clock is<br>user as the internal master clock. It should be<br>9.216MHz clock with duty 50%. Connect this pin<br>to the clock output of the SIB master chip. |

| SSYNC    | 56      | D     | I   | -          | HOST  | The synchronization clock of host interface. This clock should be 72kHz. 128 bits of serial data constitutes one frame. Connect this pin to the sync signal output of the SIB master chip.             |

| SDIN     | 59      | D     | I   | -          | HOST  | The host data input. The data is latched at the falling edge of SCLK. Connect this pin to the data output of the SIB master chip.                                                                      |

| SDOUT    | 57      | D     | 0   | HZ         | HOST  | The host data output. The data is output at the rising edge of SCLK. Connect this pin to the data input of the SIB master chip.                                                                        |

| IRQ      | 60      | D     | 0   | L          | HOST  | The interrupt request output. High active. Use the control register to set the interrupt sources.                                                                                                      |

| -RST     | 55      | D     | I   | -          | HOST  | The system reset input. Low active.                                                                                                                                                                    |

| TSPX     | 45      | A     | I/O | HZ<br>(IN) | TSC   | The touch screen interface terminal for X plate.<br>When not using this pin, leave it open.                                                                                                            |

| TSMX     | 43      | A     | I/O | HZ<br>(IN) | TSC   | The touch screen interface terminal for X plate.<br>When not using this pin, leave it open.                                                                                                            |

| TSPY     | 42      | A     | I/O | HZ<br>(IN) | TSC   | The touch screen interface terminal for Y plate.<br>When not using this pin, leave it open.                                                                                                            |

| TSMY     | 44      | A     | I/O | HZ<br>(IN) | TSC   | The touch screen interface terminal for Y plate.<br>When not using this pin, leave it open.                                                                                                            |

| AIN0     | 40      | A     | I   | -          | ADC   | The ADC input terminal. When not using this pin, leave it open.                                                                                                                                        |

| AIN1     | 39      | A     | Ι   | -          | ADC   | The ADC input terminal. When not using this pin, leave it open.                                                                                                                                        |

| AIN2     | 38      | A     | I   | -          | ADC   | The ADC input terminal. When not using this pin, leave it open.                                                                                                                                        |

| AIN3     | 37      | A     | I   | -          | ADC   | The ADC input terminal. When not using this pin, leave it open.                                                                                                                                        |

| ADSYNC   | 5       | A     | I   | -          | ADC   | The external synchronization clock input for ADC According to edge, the ADC starts conversion in ADC sync mode. When not using this pin, pull it to GND.                                               |

Table 4.2.A The pin function of TC35143BF(1/3)

A/D/P: A - Analog part, D - Digital part, P - Power supply

I/O : I - Input, O - Output, I/O - BI-direction

DEF : This means default status of the pin.

H - Hi level, L - Low level, Hz - high impedance, IN - input mode

Group : This means the functional group of the pin.

HOST - Host interface, TSC - Touch screen interface,

TEL - Telecom CODEC, VB - Voice band CODEC, ETC - The other,

POW - power supply

| Pin name | Pin No. | A/D/P    | I/O  | DEF        | Group | Function                                                                                              |

|----------|---------|----------|------|------------|-------|-------------------------------------------------------------------------------------------------------|

| TELOP    | 28      | Α        | 0    | HZ         | TEL   | The telecom positive output. When not using this                                                      |

|          |         |          |      |            |       | pin, leave it open.                                                                                   |

| TELON    | 29      | А        | 0    | HZ         | TEL   | The telecom negative output. When not using this                                                      |

|          |         |          |      |            |       | pin, leave it open.                                                                                   |

| TELIP    | 33      | A        | I    | -          | TEL   | The telecom positive input. When not using this                                                       |

| TELINI   | 0.4     | •        |      |            | TEL   | pin, leave it open.                                                                                   |

| TELIN    | 34      | A        | I    | -          | TEL   | The telecom negative input. When not using this                                                       |

| VBO1P    | 12      | Α        | 0    | HZ         | VB    | pin, leave it open.<br>The voice band CODEC positive output 1. This                                   |

| VBOTE    | 12      | ~        | 0    | 112        | ٧D    | pin is used for a handset receiver.                                                                   |

| VBO1N    | 13      | Α        | 0    | ΗZ         | VB    | The voice band CODEC negative output 1. This                                                          |

| 120111   | 10      |          | Ŭ    |            |       | pin is used for a handset receiver.                                                                   |

| VBO2P    | 14      | Α        | 0    | HZ         | VB    | The voice band CODEC positive output 2. This                                                          |

|          |         |          |      |            |       | pin is used for an external speaker.                                                                  |

| VBO2N    | 15      | Α        | 0    | HZ         | VB    | The voice band CODEC negative output 2. This                                                          |

|          |         |          |      |            |       | pin is used for an external speaker.                                                                  |

| VBIN1P   | 19      | A        | I    | -          | VB    | The voice band CODEC positive input 1. This pin                                                       |

|          |         |          |      |            |       | is used for a handset microphone. When not                                                            |

| VBIN1N   | 20      | ^        |      |            |       | using this pin, leave it open.                                                                        |

| VBINTIN  | 20      | A        | I    | -          | VB    | The voice band CODEC negative input 1. This<br>pin is used for a handset microphone. When not         |

|          |         |          |      |            |       | using this pin, leave it open.                                                                        |

| VBIN2P   | 21      | Α        | 1    | -          | VB    | The voice band CODEC positive input 2. This pin                                                       |

|          |         |          | -    |            |       | is used for an external microphone. When not                                                          |

|          |         |          |      |            |       | using this pin, leave it open.                                                                        |

| VBIN2N   | 22      | А        | I.   | -          | VB    | The voice band CODEC negative input 2. This                                                           |

|          |         |          |      |            |       | pin is used for an external microphone. When                                                          |

|          |         |          |      |            |       | not using this pin, leave it open.                                                                    |

| MICBIAS  | 24      | A        | 0    | HZ         | VB    | The voltage source for electret microphone.<br>Insert an electrolytic capacitor of 10 $\mu$ F or more |

|          |         |          |      |            |       | cascadely between this pin and analog GND and                                                         |

|          |         |          |      |            |       | a $2k\Omega$ resistor.                                                                                |

| GPIO0    | 49      | D        | I/O  | HZ         | GPIO  |                                                                                                       |

|          |         |          |      | (IN)       |       |                                                                                                       |

| GPIO1    | 50      | D        | I/O  | HZ         | GPIO  |                                                                                                       |

|          |         |          |      | (IN)       |       | These pins are general purpose I/O. Use the                                                           |

| GPIO2    | 51      | D        | I/O  | HZ         | GPIO  | control register to set each port for input/output                                                    |

|          | 50      |          | 1/0  | (IN)       | 0.010 | and the output level. These ports are set for<br>input by default after a reset. When not using       |

| GPIO3    | 52      | D        | I/O  | HZ         | GPIO  | these pins, pull them to GND.                                                                         |

| GPIO4    | 62      | D        | I/O  | (IN)<br>HZ | GPIO  |                                                                                                       |

| 05104    | 02      |          | 1/0  | ⊓∠<br>(IN) | GFIU  |                                                                                                       |

| GPIO5    | 63      | D        | I/O  | HZ         | GPIO  |                                                                                                       |

|          |         |          | ., C | (IN)       |       |                                                                                                       |

| GPIO6    | 1       | D        | I/O  | HZ         | GPIO  |                                                                                                       |

|          |         |          |      | (IN)       |       |                                                                                                       |

| GPIO7    | 2       | D        | I/O  | HZ         | GPIO  |                                                                                                       |

|          |         |          |      | (IN)       |       |                                                                                                       |

| GPIO8    | 3       | D        | I/O  | HZ         | GPIO  |                                                                                                       |

|          | 4       | <u> </u> | 1/0  | (IN)       |       |                                                                                                       |

| GPIO9    | 4       | D        | I/O  | HZ         | GPIO  |                                                                                                       |

|          |         |          |      | (IN)       |       |                                                                                                       |

Table 4.2.B The pin function of TC35143BF(2/3)

| Pin name | Pin No.                            | A/D/P | I/O | DEF         | Group | Function                                                                                                                                                                                                                                           |  |

|----------|------------------------------------|-------|-----|-------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TEST1    | 7                                  | D     | Ι   | -           | ETC   | The test terminal 1. This pin should be grounded.                                                                                                                                                                                                  |  |

| TEST2    | 6                                  |       |     |             |       | The test terminal 2. This pin should be grounded.                                                                                                                                                                                                  |  |

| VREF     | 25                                 | A     | I/O | HZ<br>(OUT) | ETC   | The internal analog reference voltage. Insert a 10 $\mu$ F electrolytic capacitor between the analog GND and this pin and also a 33 k $\Omega$ resistor between the analog Vdd and this pin. The pin direction is determined by register settings. |  |

| DVDD1    | 48                                 | Р     | -   | -           | POW   | The digital power supply input. Fix these pins to                                                                                                                                                                                                  |  |

| DVDD2    | 64                                 | Ρ     | -   | -           | POW   | +3.3V. Insert a 0.1 $\mu$ F laminated ceramic capacitor between each of these pins and the digital VSS of the same number. Make sure the capacitor is inserted as close to the pin as possible.                                                    |  |

| AVDD1    | 11                                 | Р     | -   | -           | POW   | The analog power supply input. Fix these pins to                                                                                                                                                                                                   |  |

| AVDD2    | 18                                 | Р     | -   | -           | POW   | +3.3V. Insert a 0.1 $\mu$ F laminated ceramic                                                                                                                                                                                                      |  |

| AVDD3    | 27                                 | Р     | -   | -           | POW   | capacitor between each of these pins and the<br>analog VSS of the same number. Make sure the                                                                                                                                                       |  |

| AVDD4    | 32                                 | Р     | -   | -           | POW   | capacitor is inserted as close to the pin as                                                                                                                                                                                                       |  |

| AVDD5    | 46                                 | Р     | -   | -           | POW   | possible.                                                                                                                                                                                                                                          |  |

| DVSS1    | 54                                 | Р     | -   | -           | POW   | The digital ground. Use a pattern design so that                                                                                                                                                                                                   |  |

| DVSS2    | 8                                  | Р     | -   | -           | POW   | this pin is separated from the analog GND.                                                                                                                                                                                                         |  |

| AVSS1    | 16                                 | Р     | -   | -           | POW   | The analog ground. Use a pattern design so that                                                                                                                                                                                                    |  |

| AVSS2    | 23                                 | Р     | -   | -           | POW   | this pin is separated from the digital GND.                                                                                                                                                                                                        |  |

| AVSS3    | 30                                 | Р     | -   | -           | POW   |                                                                                                                                                                                                                                                    |  |

| AVSS4    | 35                                 | Р     | -   | -           | POW   |                                                                                                                                                                                                                                                    |  |

| AVSS5    | 41                                 | Р     | -   | -           | POW   |                                                                                                                                                                                                                                                    |  |

| CVSS1    | 10                                 | Р     | -   | -           | POW   | The common ground. Connect this pin to the                                                                                                                                                                                                         |  |

| CVSS2    | 36                                 | Р     | -   | -           | POW   | analog GND.                                                                                                                                                                                                                                        |  |

| NC       | 9, 17,<br>26, 31,<br>47, 53,<br>61 | -     | -   | -           | -     | Non connection pins. Leave it open.                                                                                                                                                                                                                |  |

Table 4.2.C The pin function of TC35143BF(3/3)

### 5. Function

5.1 Hardware Interface

The system example using TC35143BF is shown in the following figure.

Figure 5.1.A System construction

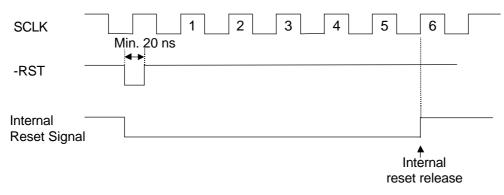

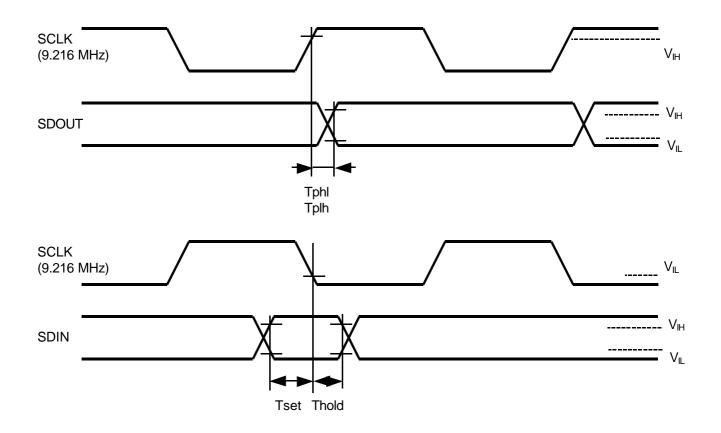

### 5.2 Hardware Reset

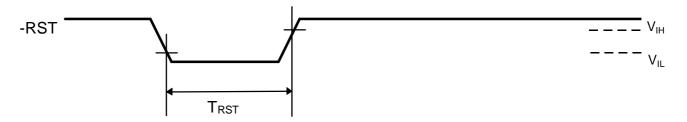

TC35143BF should be reset, after power on. To reset TC35143BF, -RST terminal should be kept low level for at least 20 ns. The reset execution is performed asynchronously. After 6 periods of SCLK from -RST release, the internal reset is released. Figure 5.2.A shows the timing at which the hardware reset is released.

Figure 5.2.A Hardware reset timing

After reset, all the internal registers are set default value and all the terminal are set the default status. The default value of registers is show in the resister map. The default status of the terminals are shown in the pin description table.

Set TC35143BF register after at least one frame has passed since the release of the reset. See 5.4.2 Interface Timing for frame timing.

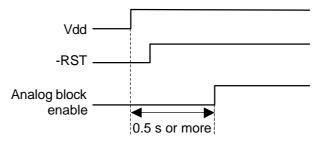

### 5.3 Power-down Control

Figure 5.3.A shows the power-down system of the TC35143BF. Since the analog circuits in the Telecom, Voice, and Touch Screen blocks can be enabled or disabled for each input/output path, sophisticated power-down control is possible. All these settings are made by controlling the internal registers. For details, refer to the explanation of registers in each block. If all analog blocks are disabled, the reference voltage circuit also stops supplying the reference voltage to those blocks.

The reference voltage can be selected between the internal and external sources. The EXREFENA [W:A:5] bit is used for this selection. If you want to use the internal reference voltage, set EXREFENA to 0. In this case, insert a 10  $\mu$ F capacitor between the analog GND and the VREF pin and also a 33 k $\Omega$  resistor between the analog Vdd and the VREF pin. Furthermore, when using the internal reference voltage, allow a period of at least 0.5 seconds before the analog block can be enabled immediately after power-on, as shown in Figure 5.3.A. As long as the power is supplied after this time on, there is no need to insert such a wait state. This wait state only needs to be inserted immediately after power-on. When using an external reference voltage, set EXREFENA to 1. In this case, the wait state of 0.5 seconds or more that is required when using the internal reference voltage is unnecessary. Note also that when an external reference power supply is connected directly to the VREF pin, an input leakage current of about 75  $\mu$ A (max) flows in it. For applications such as HPC and portable information terminals which require the current consumption to be suppressed to a minimum, make sure the external reference voltage is not applied to the device during power-down state (all functions stopped) by, for example, inserting a switch external to the chip.

Power-down control of the digital unit is accomplished by turning SCLK , SSYNC and SDIN off. These clocks can be turned off only when all function blocks of the TC35143BF are disabled. Do not turn off those clocks if one block is enabled at least.

In addition, TC35143BF has feedback-type analog circuits. These circuits require at least 1 ms of idling from startup to when their operations stabilize. TC35143BF invalidates request flags to receive data until internal operations stabilize. Data can therefore not be received for a minimum of 1 ms from enable setting by the enable bit. For this 1 ms interval connect SCLK before carrying out input.

Figure 5.3.A Timing at Which the Analog Block is Enabled Immediately After Power-on

Figure 5.3.B Power-down system

### 5.4 Serial Interface

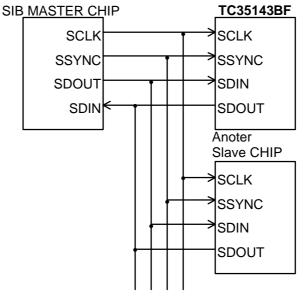

The TC35143BF's serial interface is mostly based on SIB interface standards, so it can be connected directly to the SIB master chip. Use of the SIB allows the master chip to communicate with multiple slave devices. Figure 5.4.A shows an example of a device connection.

To other SIB slave CHIP

Figure 5.4.A Example of connection for some SIB devices

### 5.4.1 Pin Function

The following explains the TC35143BF's pin functions related to the SIB interface.

| SDIN : This pin is used to receive the serial data sent from the SIB master | chip. |

|-----------------------------------------------------------------------------|-------|

|-----------------------------------------------------------------------------|-------|

- SDOUT : This pin outputs the serial data that is sent to the SIB master chip.

- SCLK: This pin is used to receive the serial clock supplied from the SIB master chip.Input a 9.216 MHz clock to this pin.The permissible deviation of the clockfrequency is 100 ppm and of the duty rate is 45 % to 55 %.

- SSYNC : This is a 72 kHz frame synchronizing signal supplied from the SIB master chip. This signal is driven high (= 1) for one SCLK cycle prior to each frame.

- IRQ : This pin outputs the interrupt request signal that is sent to the SIB master chip.

#### 5.4.2 Interface Timing

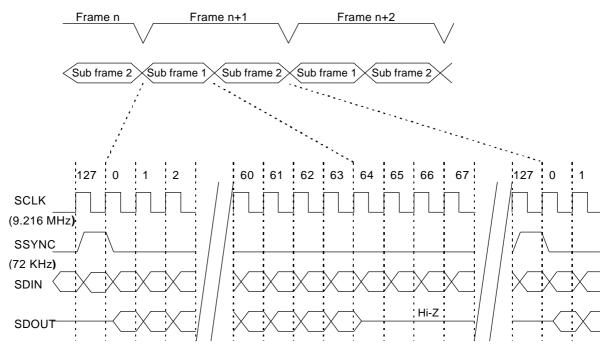

The SIB transfer method is synchronous, with data transferred in units of frames. Operations between the SIB master chip and SIB slave chips are synchronized using a frame sync signal. Figure 5.4.B shows a timing chart.

Figure 5.4.B Serial Interface Timing

One frame of data consists of 128 bits. A frame is divided into two subframes, each consisting of 64 bits. The TC35143BF uses subframe 1 to communicate with the master device. The TC35143BF latches the SDIN data into its internal circuit synchronously with falling edges of SCLK. It outputs the SDOUT data synchronously with rising edges of SCLK. SSYNC is a frame synchronizing signal which is driven high (= 1) for a duration of the last bit of each frame. The TC35143BF uses SSYNC and a SCLK counter to synchronize the frames being transferred. For details about the AC timing specifications of SCLK, SDIN, and SDOUT, refer to Section 6.4, "A.C. Characteristics."

In a multi-chip configuration, use subframe 2 for other slave devices to communicate with the master device. The TC35143BF uses subframe 1 to communicate with the master device as described above. To prevent the SDOUT outputs of multiple chips from conflict, make sure that when other slave device is communicating, TC35143BF has its SDOUT placed in the high-impedance state. Furthermore, in cases where only one TC35143BF is connected to the master device, make sure the SDOUT output level is fixed low for a duration of subframe 2 to prevent it from being left open. Use a control register to set the status of the SDOUT pin during a subframe 2 period. For details, refer to the description of the SIFZERO [W:1:15] bit of general-purpose I/O port in Section 5.6.

For any one of the function blocks to be operated, SCLK and SSYNC must be input. Note that interrupt output signals are generated regardless of whether SCLK is input.

### 5.4.3 SIB Data Format

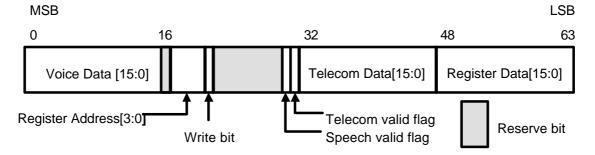

Figure 5.4.C shows the data format of SIB subframe 1 in the TC35143BF. The SDIN frame represents the frames input to the TC35143BF. The SDOUT frame represents the frames output by the TC35143BF.

| Frame<br>Bit                                            | SDIN Field Definition                    | SDOUT Field Definition                   |  |  |  |  |  |

|---------------------------------------------------------|------------------------------------------|------------------------------------------|--|--|--|--|--|

| [0:15]                                                  | Voice DAC Data (16 bits) ; Bit[0]=MSB    | Voice ADC Data (16 bits) ; Bit[0]=MSB    |  |  |  |  |  |

| [17:20]                                                 | Register Address (4 bits) ; Bit[17]=MSB  | Register Address (4 bits) ; Bit[17]=MSB  |  |  |  |  |  |

| [21]                                                    | Write Bit (Write=1)                      | Must write to 0                          |  |  |  |  |  |

| [30]                                                    | Voice Valid DAC Sample Flag              | Voice Valid ADC Flag                     |  |  |  |  |  |

| [31]                                                    | Telecom Valid DAC Sample Flag            | Telecom Valid ADC Flag                   |  |  |  |  |  |

| [32:47]                                                 | Telecom DAC Data (16 bits) ; Bit[32]=MSB | Telecom ADC Data (16 bits) ; Bit[32]=MSB |  |  |  |  |  |

| [48:63]                                                 | Register Data (16 bits) ; Bit[48]=MSB    | Register Data (16 bits) ; Bit[48]=MSB    |  |  |  |  |  |

| Supplement 1) The reserved bits are handled as follows: |                                          |                                          |  |  |  |  |  |

SDIN frame : All bits must be filled with 0s.

SDOUT frame : The TC35143BF always outputs a logic 0 to the reserved bits.

Supplement 2) Since the ADC/DAC's conversion accuracy is 14 bits, the 2 least significant bits of the Speed Data field are handled as follows:

| SDIN frame  | : | The TC35143BF ignores the 2 least significant bits.          |

|-------------|---|--------------------------------------------------------------|

| SDOUT frame | : | The TC35143BF outputs an indeterminate state for the 2 least |

|             |   | significant bits.                                            |

Figure 5.4.C Sub frame format

The SIB subframe is comprised of three data fields and handshaking flags. The DAC data in the Voice and Telecom units is transferred from the SIB master processor to the TC35143BF using the SDIN frame. Similarly, the ADC data in the Voice and Telecom units is transferred from the TC35143BF to the SIB master processor using the SDOUT frame. The valid flags are used to transfer sample data. For details about the transfer procedure and timing, refer to Section 5.5.

The 16 bits wide control register field, not just the control and status bits, includes the data bits used to transfer the sample data of the internal 10-bit ADC. For details about the 10-bit ADC's data transfer procedure, refer to Section 5.11. There are 16 control registers for the SDIN and the SDOUT frames each. The SDIN frame's address field is used to choose the register type. For details about the register types and functions, refer to Sections 5.5 and 5.6. The SDIN frame's Write bit is used for handshaking of the control registers. For details about the handshaking procedure and timing, refer to Section 5.4.4.

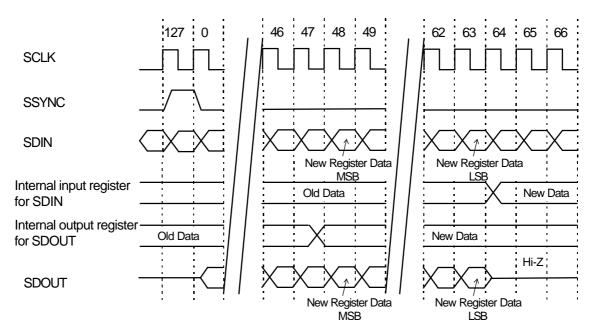

### 5.4.4 Handshaking Procedure for the Control Register Field

The SDIN frame's Write bit is used for the handshaking of control registers. Figure 5.4.D shows the update timing of the internal register. For reading from the register, a master processor sets the desired address and at the same time sets the Write bit to "0". TC35143BF sets a register data corresponds to a address into output buffer at the SCLK falling edge of bit 47 after recognizing write bit = "0". The buffer data is output from the SDOUT pin into the SDOUT stream from bit 48. Simultaneously in the frame whose Write bit = "0", the control data field of the SDIN stream is ignored, so an internal input register is not updated.

For writing to the register, set the Write bit to "1". At this time, a master processor sets the address and a control data simultaneously. TC35143BF internal control register are updated at the SCLK rising edge of bit 64 after recognizing write bit = "1". This means that the control data field of SDOUT stream in subframe 1 whose Write bit = "1" is the data immediately before being updated.

The address of SDIN stream is output from SDOUT stream directly.

Figure 5.4.D Control register up-date timing during subframe 1

### 5.5 Line and Voice Interface Sample Data Handshake

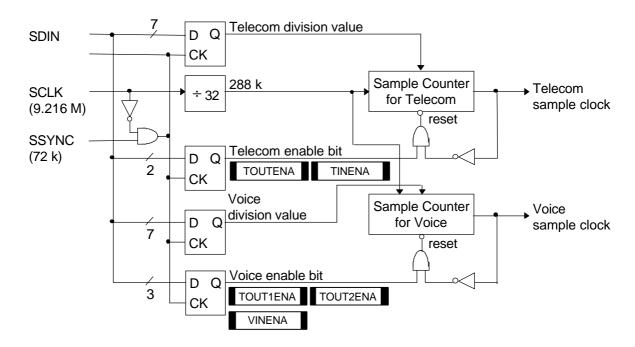

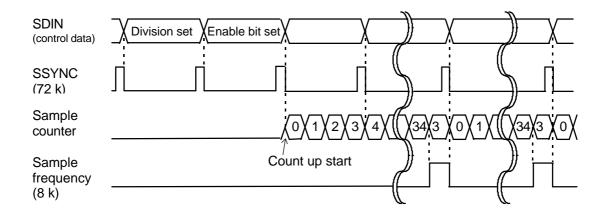

Figure 5.5.A shows the ADC and DAC sampling clock generating circuits in the Voice and Telecom blocks. Figure 5.5.B shows sampling clock timing diagrams. The sampling clocks can be set independently for the Telecom and Voice blocks. Use TDIV [W:5:6-0] and VDIV [W:7:6-0] for this setting. For details on how to set, refer to the chapters where the Telecom and Voice blocks are described. The host processor first sets the desired sampling frequencies to TDIV and VDIV. Then it enables the required circuit blocks. The sample counter starts counting after the circuit blocks are enabled. The sample counter counts up the 288 kHz clock derived from SCLK until the values set by TDIV and VDIV are reached. If the settings of TDIV or VDIV are changed in the middle of counting, the clock generation gets out of synchronization, resulting in an underwrite or underread of data. Therefore, be sure to disable the circuit blocks before changing the settings of sampling frequencies. Then, after setting the sampling frequencies, renewable the circuit blocks.

When the sample counter has completed one count up, the sampling pulse is toggled twice. It is synchronized to the sampling pulse, and the data request flag (valid flag) for receiving data becomes invalid.

The Telecom and Voice data are communicated with an SIB master processor using a flag called the "valid flag." If an SIB master processor has the same sample counter of TC35143BF, the data communication is possible by only using valid flag.

Figure 5.5.A Sampling clock generator

### 5.5.1 Voice and Telecom Input Data Transfer Timings

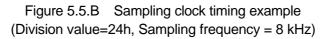

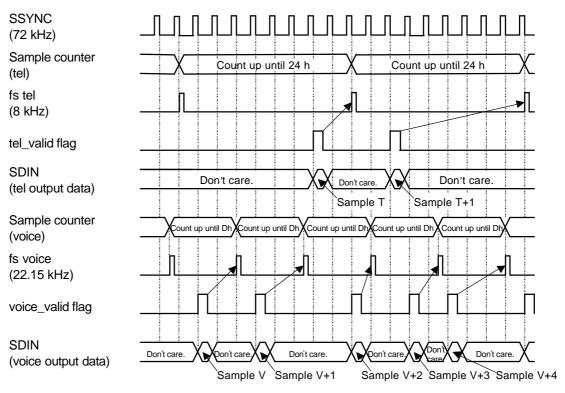

Figure 5.5.C shows ADC data handshaking timing for the Voice and Telecom input signals. Shown in this diagram are examples where the sampling frequency in the Telecom unit is set to 8 kHz (TDIV = 24h) and that in the Voice unit is set to 22.15 kHz (VDIV = Dh).

The ADC data handshaking basically is accomplished by using the valid flag. The valid flag is provided individually for the Telecom and Voice units. These valid flags are fixed to 0 when the corresponding input path is disabled. For example, if the Telecom input path is disabled (using the TINENA bit), tel\_valid flag does not turn on. Also, even when the input path is enabled, these flags indicate a 0 until the first converted data is prepared.Specifically, after enable setting, the valid flag becomes valid after the 65SSYNC interval (approximately 1 ms) has passed.

The valid flag has two operation modes. The DFLGENA [W:D:12] is used to set the modes. If DFLGENA is 0, the valid flag is always 1 in a subframe in which the ADC data is output from the SDOUT stream. The Telecom and Voice valid flags both behave in the same way. If DFLGENA is 1, the Telecom and Voice valid flags behave a little differently. The Telecom valid flag is set to 1 in only the subframe immediately after the Telecom data field in SDOUT stream is updated to new data. Although the data in the SDOUT stream itself remains valid until the data is updated to the next sample data, the valid flag indicates a 0. The Voice valid flag is set to 1 in only the subframe immediately before the Voice data field in SDOUT stream is updated to new data. Although the state a 0 before it is set to 1 after the data is updated to new data, the valid flag indicates a 0 before it is set to 1 after the data is updated to new data, the data in the SDOUT stream itself remains valid until the data. Although the valid flag indicates a 0 before it is set to 1 after the data is updated to new data, the valid flag indicates a 0 before it is valid.

Figure 5.5.C ADC data transfer timing

The host processor normally sets DFLGENA to 1 and receives the ADC data synchronously with the valid flag = 1. If a master processor uses a timer or a counter synchronizes with SCLK as handshake trigger, the data handshaking can be accomplished without monitoring the valid flags. Table 5.5.A shows the registers that contain the DFLGENA bit.

| BIT                                                 | R/W                                                 | SYMBOL    | BIT MEANING                                                                                                                                                                                                                                                                                                     | DEF. |  |  |  |  |  |

|-----------------------------------------------------|-----------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|--|--|

| 15 to 14                                            | W                                                   | RESERVED  | These are spare bits. Set them to 00b.                                                                                                                                                                                                                                                                          | 0    |  |  |  |  |  |

|                                                     | R RESERVED These are spare bits. They indicate a 0. |           |                                                                                                                                                                                                                                                                                                                 |      |  |  |  |  |  |

| 13                                                  | W                                                   | VOFFCAN   | This bit enables or disables the offset canceler of the Speech input unit.<br>0: Disabled.<br>1: Enabled.                                                                                                                                                                                                       |      |  |  |  |  |  |

|                                                     | R                                                   | VOFFCAN   | This bit indicates status of whether the offset canceler of the Speech input unit is enabled or disabled.<br>0: Disabled.<br>1: Enabled.                                                                                                                                                                        | 0    |  |  |  |  |  |

| 12                                                  | W                                                   | DFLGENA   | <ul><li>This bit sets the display mode of the valid flag in the SDOUT frame.</li><li>0: Static mode.</li><li>1: Dynamic mode.</li></ul>                                                                                                                                                                         | 0    |  |  |  |  |  |

|                                                     | R                                                   | DFLGENA   | This bit indicates the setup display mode of the valid flag in the SDOUT frame.<br>0: Static mode.<br>1: Dynamic mode.                                                                                                                                                                                          | 0    |  |  |  |  |  |

| 11                                                  | W                                                   | RESERVED  | This is a spare bit. Set it to 0.                                                                                                                                                                                                                                                                               | 0    |  |  |  |  |  |

|                                                     | R                                                   | RESERVED  | This is a spare bit. This indicates a 0.                                                                                                                                                                                                                                                                        | 0    |  |  |  |  |  |

| 10 to 8                                             | W                                                   | VCOF[2:0] | These bits select the frequency response of the Voice interface's digital filter. Choose the filter characteristic according to the sampling frequency. For the setup contents, see the table below.         For details about filter characteristics, refer to 5.10.3.         Voice interface       VCOF[2:0] | 1    |  |  |  |  |  |

|                                                     |                                                     |           | Voice interface     VCOF[2:0]       sampling frequency     8 kHz       8 kHz     001b       11.08 kHz     001b       16 kHz     100b       22.15 kHz     100b       (Note)     Do not set any other code.                                                                                                       |      |  |  |  |  |  |

|                                                     | R                                                   | VCOF[2:0] | These bits show the selected frequency response settings of the Voice interface's digital filter.<br>For the contents of setup code, refer to the explanation of the write register above.                                                                                                                      | 1    |  |  |  |  |  |

| 7 to 0                                              | W                                                   | RESERVED  | These are spare bits. Set them to 0.                                                                                                                                                                                                                                                                            | 0    |  |  |  |  |  |

| R RESERVED These are spare bits. They indicate a 0. |                                                     |           |                                                                                                                                                                                                                                                                                                                 | 0    |  |  |  |  |  |

Table 5.5.A Mode Register (Address D)

### 5.5.2 Voice and Telecom Output Data Transfer Timings

Figure 5.5.D shows DAC data handshaking timings for the Voice and Telecom output signals. Shown in this diagram are examples where the sampling frequency in the Telecom unit is set to 8 kHz (TDIV = 24h) and that in the Voice unit is set to 22.15 kHz (VDIV = Dh).

The DAC data handshaking is accomplished by using the valid flag. The valid flag is provided individually for the Telecom and Voice units. Unlike for the ADC data, the Telecom and Voice valid flags behave in the same way. Also, a register bit to set the operation modes (a bit equivalent to DFLGENA) is not provided.

If the output block is disabled, the TC35143BF does not output the corresponding analog signal even when the valid flag is 1. When the output block is enabled, the data in the frame whose valid flag = 1 is taken in and is output from the analog pins after being converted by the DAC. The data in the frames whose valid flag = 0 are not taken in.However, after enable setting, the valid flag is invalid for the 65SSYNC interval (approximately 1 ms) until operation of the analog circuit stabilizes, so please wait.

The host processor prepares an SCLK-synchronized timer or counter to synchronize its operation with the TC35143BF's sampling timing. The host processor sets the valid flag to 1 and at the same time writes the sample data into the data field of the SDIN stream before the next sampling timing as shown below. Since the TC35143BF does not take in data from the frames whose valid flag = 0, there will be no problem even when some data is written into those frames by the host processor.

Figure 5.5.D Example of DAC data transfer timing

### 5.6 Control Register

The TC35143BF has a 16 bits wide register field that is controlled via the SIB interface. The register field for the data (SDIN) that is input from the SIB master chip to the TC35143BF is called the "write" register. The register field for the data (SDOUT) that is output from the TC35143BF to the SIB master chip is called the "read" register. There are 16 register addresses for read and write each. Most bits at the same positions in the write and the read registers have the same effect, but some bits have different effects.

The SIB master chip controls the TC35143BF by writing and reading to and from the write and read registers. Since write and read to and from these registers are performed on one address at a time, note that even when rewriting one bit, data is written to all other bits at the same address also. The bit positions are described as follows:

| FORMAT:[W/R : ADDRESS : BIT] | W/R     | W (Write) or R (Read) |

|------------------------------|---------|-----------------------|

|                              | ADDRESS | 0 to F (Hex-Decimal)  |

|                              | BIT     | 0 (LSB) to 15 (MSB)   |

Example: The Telecom interface's loop test control bit is located at bit 7 of write register 5. Therefore, this bit is described as follows (see Tables 5.6.B to E for register maps):

TLOOP [W : 5 : 7]

The control registers described above are outlined in Table 5.6.A.

| ADDRESS | R/W | Symbol | Description                                                    |

|---------|-----|--------|----------------------------------------------------------------|

| 0H      | W   | IODAT  | I/O port data :                                                |

|         |     |        | Control register for I/O port output level                     |

|         | R   | IODAT  | I/O port data : I                                              |

|         |     |        | Status register for I/O port level                             |

| 1H      | W   | IODIR  | I/O port direction:                                            |

|         |     |        | Control register for I/O port input/output direction           |

|         | R   | IODIR  | I/O port direction :                                           |

|         |     |        | Status register for I/O port input/output direction            |

| 2H      | W   | RISINT | Rising edge interrupt:                                         |

|         |     |        | Setting register for rising edge trigger of interrupt factors  |

|         | R   | RISINT | Rising edge interrupt:                                         |

|         |     |        | Status register for rising edge trigger of interrupt factors   |

| 3H      | W   | FALINT | Falling edge interrupt:                                        |

|         |     |        | Setting register for falling edge trigger of interrupt factors |

|         | R   | FALINT | Falling edge interrupt:                                        |

|         |     |        | Setting register for falling edge trigger of interrupt factors |

| 4H      | W   | INTCLR | Interrupt clear:                                               |

|         |     |        | Setting register for interrupt clear                           |

|         | R   | INTCLR | Interrupt status:                                              |

|         |     |        | Status register for interrupt factors                          |

| 5H      | W   | TELA   | Telecom control A:                                             |

|         |     |        | Setting register for sampling frequency of telecom part        |

|         | R   | TELA   | Telecom control A:                                             |

|         | 147 |        | Status register for sampling frequency of telecom part         |

| 6H      | W   | TELB   | Telecom control B:                                             |

|         |     |        | Control register for telecom part                              |

|         | R   | TELB   | Telecom control B:                                             |

| 7H      | W   | VOICEA | Status register for telecom part control Voice control A:      |

| / []    | vv  | VOICEA | Setting register for sampling frequency of voice part          |

|         | R   | VOICEA | Voice control A:                                               |

|         |     | VOICEA | Status register for sampling frequency of voice part           |

| 8H      | W   | VOICEB | Voice control B:                                               |

| 011     | vv  | VOICED | Control register for voice part                                |

|         | R   | VOICEB | Voice control B:                                               |

|         |     | VOICED | Status register for voice part control                         |

| 9H      | W   | TSC    | Touch screen:                                                  |

|         |     |        | Control register for touch screen                              |

|         | R   | TSC    | Touch screen:                                                  |

|         |     |        | Status register for touch screen control                       |

| AH      | W   | ADC    | ADC control:                                                   |

|         |     |        | Control register for 10 bit ADC                                |

|         | R   | ADC    | ADC control:                                                   |

|         |     |        | Status register for 10 bit ADC control                         |

Table 5.6.A TC35143BF Control Register

| BH | W | RSV    | Reserved                                     |

|----|---|--------|----------------------------------------------|

|    | R | ADCDAT | ADC data:                                    |

|    |   |        | Data register of 10 bit ADC                  |

| СН | W | RSV    | Reserved                                     |

|    | R | DATE   | DATE:                                        |

|    |   |        | Indicates development date                   |

| DH | W | MODE   | Mode:                                        |

|    |   |        | Sets the operation mode.                     |

|    | R | MODE   | Mode:                                        |

|    |   |        | Indicates the setup state of operation mode. |

| EH | W | RSV    | Reserved                                     |

|    | R | RSV    | Reserved                                     |

| FH | W | RSV    | Reserved                                     |

|    | R | RSV    | Reserved                                     |

### 5.6.1 Write Register Map

Table 5.6.B and Table 5.6.C show the Write Register maps. Bit width is 16. Table 5.6.B shows the upper 8bits and Table 5.6.C shows lower 8bits. Description of each bit is described in after section 5.7.

| ADD- |          | BIT CONTENTS |          |         |         |         |         |         |        |  |  |  |

|------|----------|--------------|----------|---------|---------|---------|---------|---------|--------|--|--|--|

| RESS | BIT 15   | BIT 14       | BIT 13   | BIT 12  | BIT 11  | BIT 10  | BIT 9   | BIT 8   |        |  |  |  |

| 0 H  | IRQACT   | -            | -        | -       | -       | -       | IODAT9  | IODAT8  | IODAT  |  |  |  |

|      | 0        |              |          | 0       | 0       | 0       |         |         |        |  |  |  |

| 1 H  | SIFZERO  | -            | -        | -       | -       | -       | IODIR9  | IODIR8  | IODIR  |  |  |  |

|      | 0        | 0            | 0        | 0       | 0       | 0       | 0       | 0       |        |  |  |  |

| 2 H  | ACRINT   | TCRINT       | MXRINT   | PXRINT  | ADCRINT | -       | IORINT9 | IORINT8 | RISINT |  |  |  |

|      | 0        | 0            | 0        | 0       | 0       | 0       | 0       | 0       |        |  |  |  |

| 3 H  | ACFINT   | TCFINT       | MXFINT   | PXFINT  | ADCFINT | -       | IOFINT9 | IOFINT8 | FALINT |  |  |  |

|      | 0        | 0            | 0        | 0       | 0       | 0       | 0       | 0       |        |  |  |  |

| 4 H  | ACICLR   | TCICLR       | MXICLR   | PXICLR  | ADCICLR | -       | IOICLR9 | IOICLR8 | INTCLR |  |  |  |

|      | 0        | 0            | 0        | 0       | 0       | 0       | 0       | 0       |        |  |  |  |

| 5 H  | TCOF2    | TCOF1        | TCOF0    | -       | -       | -       | -       | -       | TELA   |  |  |  |

|      | 0        | 0            | 1        | 0       | 0       | 0       | 0       | 0       |        |  |  |  |

| 6 H  | TOUTENA  | TINENA       | TMUTE    | TECGAIN | TECENA  | -       | -       | TGAIN   | TELB   |  |  |  |

|      | 0        | 0            | 0        | 0       | 0       | 0       | 0       | 0       |        |  |  |  |

| 7 H  | VINSEL1  | VINSEL0      | VOUT2ENA | VGAIN1  | VGAIN0  | VAMP3   | VAMP2   | VAMP1   | VOICEA |  |  |  |

|      | 0        | 0            | 0        | 0       | 0       | 0       | 0       | 0       |        |  |  |  |

| 8 H  | VOUT1ENA | VINENA       | VADMUTE  | VHSMUTE | VHSATT2 | VHSATT1 | VHSATT0 | VLOOP   | VOICEB |  |  |  |

|      | 0        | 0            | 0        | 1       | 0       | 0       | 0       | 0       |        |  |  |  |

| 9 H  | -        | -            | -        | -       | TSCENA  | -       | TSCMOD1 | TSCMOD0 | TSC    |  |  |  |

|      | 0        | 0            | 0        | 0       | 0       | 0       | 0       | 0       |        |  |  |  |

| ΑH   | ADCENA   | -            | -        | -       | -       | -       | -       | -       | ADC    |  |  |  |

|      | 0        | 0            | 1        | 0       | 0       | 1       | 0       | 1       |        |  |  |  |

| ΒH   | -        | -            | -        | -       | -       | -       | -       | -       | RSV    |  |  |  |

|      | 0        | 0            | 0        | 0       | 0       | 0       | 0       | 0       |        |  |  |  |

| СН   | -        | -            | -        | -       | -       | -       | -       | -       | RSV    |  |  |  |

|      | 0        | 0            | 0        | 0       | 0       | 0       | 0       | 0       |        |  |  |  |

| DH   | -        | -            | VOFFCAN  | DFLGENA | -       | VCOF2   | VCOF1   | VCOF0   | MODE   |  |  |  |

|      | 0        | 0            | 0        | 0       | 0       | 0       | 0       | 1       |        |  |  |  |

| ΕH   | -        | -            | -        | -       | -       | -       | -       | -       | RSV    |  |  |  |

|      | 0        | 0            | 0        | 0       | 0       | 0       | 0       | 0       |        |  |  |  |

| FH   | -        | -            | -        | -       | -       | -       | -       | -       | RSV    |  |  |  |

|      | 0        | 0            | 0        | 0       | 0       | 0       | 0       | 0       |        |  |  |  |

Table 5.6.B TC35143BF Write Register Map (Higher Bits)

(Note) Upper : BIT Mnemonic, Lower : default value, - : reserved

| ADD- |          |         |                               | BIT CO  | NTENTS  |         |         |           | MNEMONIC |  |

|------|----------|---------|-------------------------------|---------|---------|---------|---------|-----------|----------|--|

| RESS | BIT 7    | BIT 6   | BIT 5                         | BIT 4   | BIT 3   | BIT 2   | BIT 1   | BIT 0     |          |  |

| 0 H  | IODAT7   | IODAT6  | IODAT5                        | IODAT4  | IODAT3  | IODAT2  | IODAT1  | IODAT0    | IODAT    |  |

|      | 0        | 0       | 0                             | 0       | 0       | 0       | 0       | 0         |          |  |

| 1 H  | IODIR7   | IODIR6  | IODIR5                        | IODIR4  | IODIR3  | IODIR2  | IODIR1  | IODIR0    | IODIR    |  |

|      | 0        | 0       | 0                             | 0       | 0       | 0       | 0       | 0         |          |  |

| 2 H  | IORINT7  | IORINT6 | IORINT5                       | IORINT4 | IORINT3 | IORINT2 | IORINT1 | IORINT0   | RISINT   |  |

|      | 0        | 0       | 0                             | 0       | 0       | 0       | 0       | 0         |          |  |

| 3 H  | IOFINT7  | IOFINT6 | IOFINT5                       | IOFINT4 | IOFINT3 | IOFINT2 | IOFINT1 | IOFINT0   | FALINT   |  |

|      | 0        | 0       | 0                             | 0       | 0       | 0       | 0       | 0         |          |  |

| 4 H  | IOICLR7  | IOICLR6 | IOICLR5                       | IOICLR4 | IOICLR3 | IOICLR2 | IOICLR1 | IOICLR0   | INTCLR   |  |

|      | 0        | 0       | 0                             | 0       | 0       | 0       | 0       | 0         |          |  |

| 5 H  | TLOOP    | TDIV6   | TDIV6 TDIV5 TDIV4 TDIV3 TDIV2 |         | TDIV1   | TDIV0   | TELA    |           |          |  |

|      | 0        | 0       | 1                             | 0       | 0       | 1       | 0       | 0         |          |  |

| 6 H  | TAMP2    | TAMP1   | TAMP0                         | TCLPCLR | THPFENA | -       | -       | -         | TELB     |  |

|      | 0        | 0       | 0                             | 0       | 0       | 0       | 0       | 0         |          |  |

| 7 H  | VAMP0    | VDIV6   | VDIV5                         | VDIV4   | VDIV3   | VDIV2   | VDIV1   | VDIV0     | VOICEA   |  |

|      | 0        | 0       | 1                             | 0       | 0       | 1       | 0       | 0         |          |  |

| 8 H  | VDAMUTE  | VCLPCLR | VSPMUTE                       | VDAATT1 | VDAATT0 | VSPATT2 | VSPATT1 | VSPATT0   | VOICEB   |  |

|      | 0        | 0       | 1                             | 0       | 0       | 0       | 0       | 0         |          |  |

| 9 H  | TSPYGND  | TSMYGND | TSPXGND                       | TSMXGND | TSPYPOW | TSMYPOW | TSPXPOW | TSMXPOW   | TSC      |  |

|      | 0        | 0       | 0                             | 0       | 0       | 0       | 0       | 0         |          |  |

| ΑH   | ADCSTART | -       | EXREFENA                      | ADCIN2  | ADCIN1  | ADCIN0  | -       | ADSYNCENA | ADC      |  |

|      | 0        | 0       | 0                             | 0       | 0       | 0       | 0       | 0         |          |  |

| ΒH   | -        | -       | -                             | -       | -       | -       | -       | -         | RSV      |  |

|      | 0        | 0       | 0                             | 0       | 0       | 0       | 0       | 0         |          |  |

| СН   | -        | -       | -                             | -       | -       | -       | -       | -         | RSV      |  |

|      | 0        | 0       | 0                             | 0       | 0       | 0       | 0       | 0         |          |  |

| DH   | -        | -       | -                             | -       | -       | -       | -       | -         | MODE     |  |

|      | 0        | 0       | 0                             | 0       | 0       | 0       | 0       | 0         |          |  |

| ΕH   | -        | -       | -                             | -       | -       | -       | -       | -         | RSV      |  |

|      | 0        | 0       | 0                             | 0       | 0       | 0       | 0       | 0         |          |  |

| FΗ   | -        | -       | -                             | -       | -       | -       | -       | -         | RSV      |  |

|      | 0        | 0       | 0                             | 0       | 0       | 0       | 0       | 0         |          |  |

Table 5.6.C TC35143BF Write Register Map (Lower Bits)

(Note) Upper : BIT Mnemonic, Lower : default value, - : reserved

### 5.6.2 Read Register Map

Table 5.6.D and Table 5.6.E show the Read Register maps. The bit width is 16. Table 5.6.D shows upper 8bit and Table 5.6.E shows lower 8bit. Description of each bit is described in after section 5.7.

| ADD- | BIT CONTENTS |         |                         |         |          |         |          |               | MNEMONIC |  |

|------|--------------|---------|-------------------------|---------|----------|---------|----------|---------------|----------|--|

| RESS | BIT 15       | BIT 14  | BIT 13                  | BIT 12  | BIT 11   | BIT 10  | BIT 9    | BIT 8         |          |  |

| 0 H  | IRQACT       | -       | -                       | -       | -        | -       | IODAT9   | IODAT8        | IODAT    |  |

|      | 0            | 0       | 0                       | 0       | 0        | 0       | *        | *             |          |  |

| 1 H  | SIFZERO      | -       | -                       | -       | -        | -       | IODIR9   | IODIR8        | IODIR    |  |

|      | 0            | 0       | 0                       | 0       | 0        | 0       | 0        | 0             |          |  |

| 2 H  | ACRINT       | TCRINT  | MXRINT                  | PXRINT  | ADCRINT  | -       | IORINT9  | IORINT8       | RISINT   |  |

|      | 0            | 0       | 0                       | 0       | 0        | 0       | 0        | 0             |          |  |

| 3 H  | ACFINT       | TCFINT  | MXFINT                  | PXFINT  | ADCFINT  | -       | IOFINT9  | IOFINT8       | FALINT   |  |

|      | 0            | 0       | 0                       | 0       | 0        | 0       | 0        | 0             |          |  |

| 4 H  | ACINTST      | TCINTST | MXINTST                 | PXINTST | ADCINTST | -       | IOINTST9 | IOINTST8      | INTSTAT  |  |

|      | 0            | 0       | 0                       | 0       | 0        | 0       | 0        | 0             |          |  |

| 5 H  | TCOF2        | TCOF1   | TCOF0                   | -       | -        | -       | -        | -             | TELA     |  |

|      | 0            | 0       | 1                       | 0       | 0        | 0       | 0        | 0             |          |  |

| 6 H  | TOUTENA      | TINENA  | TMUTE                   | TECGAIN | TECENA   | -       | -        | <b>TGAIN0</b> | TELB     |  |

|      | 0            | 0       | 0                       | 0       | 0        | 0       | 0        | 0             | ]        |  |

| 7 H  | VINSEL1      | VINSEL0 | VOUT2ENA                | VGAIN1  | VGAIN0   | VAMP3   | VAMP2    | VAMP1         | VOICEA   |  |

|      | 0            | 0       | 0                       | 0       | 0        | 0       | 0        | 0             |          |  |

| 8 H  | VOUT1ENA     | VINENA  | VADMUTE                 | VHSMUTE | VHSATT2  | VHSATT1 | VHSATT0  | VLOOP         | VOICEB   |  |

|      | 0            | 0       | 0                       | 1       | 0        | 0       | 0        | 0             |          |  |

| 9 H  | -            | -       | TSMXLOW                 | TSPXLOW | TSCENA   | -       | TSCMOD1  | TSCMOD0       | TSC      |  |

|      | 0            | 0       | 0                       | 0       | 0        | 0       | 0        | 0             |          |  |

| ΑH   | ADCENA       | -       | -                       | -       | -        | -       | -        | -             | ADC      |  |

|      | 0            | 0       | 1                       | 0       | 0        | 1       | 0        | 1             |          |  |

| BН   | ADCVAL       | ADCDAT9 | ADCDAT8                 | ADCDAT7 | ADCDAT6  | ADCDAT5 | ADCDAT4  | ADCDAT3       | ADCDAT   |  |

|      | 1            | *       | *                       | *       | *        | *       | *        | *             |          |  |

| СН   | DATE15       | DATE14  | DATE13                  | DATE12  | DATE11   | DATE10  | DATE9    | DATE8         | DATE     |  |

|      | 1            | 0       | 0                       | 1       | 0        | 1       | 1        | 1             |          |  |

| DH   | -            | -       | VOFFCAN DFLGENA - VCOF2 |         | VCOF1    | VCOF0   | MODE     |               |          |  |

|      | 0            | 0       | 0                       | 0       | 0        | 0       | 0        | 1             |          |  |

| ΕH   | -            | -       | -                       | -       | -        | -       | -        | -             | RSV      |  |

|      | 0            | 0       | 0                       | 0       | 0        | 0       | 0        | 0             |          |  |

| FH   | -            | -       | -                       | -       | -        | -       | -        | -             | RSV      |  |

|      | 1            | 1       | 1                       | 1       | 1        | 1       | 1        | 1             |          |  |

Table 5.6.D TC35143BF Read Register Map (Higher Bits)

(Note) Upper : BIT Mnemonic, Lower : default value, -: reserved, \*: undefined

| ADD- |          |          |          | BIT CO   | MNEMONIC |          |          |           |         |

|------|----------|----------|----------|----------|----------|----------|----------|-----------|---------|

| RESS | BIT 7    | BIT 6    | BIT 5    | BIT 4    | BIT 3    | BIT 2    | BIT 1    | BIT 0     |         |

| 0 H  | IODAT7   | IODAT6   | IODAT5   | IODAT4   | IODAT3   | IODAT2   | IODAT1   | IODAT0    | IODAT   |

|      | *        | *        | *        | *        | *        | *        | *        | *         |         |

| 1 H  | IODIR7   | IODIR6   | IODIR5   | IODIR4   | IODIR3   | IODIR2   | IODIR1   | IODIR0    | IODIR   |

|      | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0         |         |

| 2 H  | IORINT7  | IORINT6  | IORINT5  | IORINT4  | IORINT3  | IORINT2  | IORINT1  | IORINT0   | RISINT  |

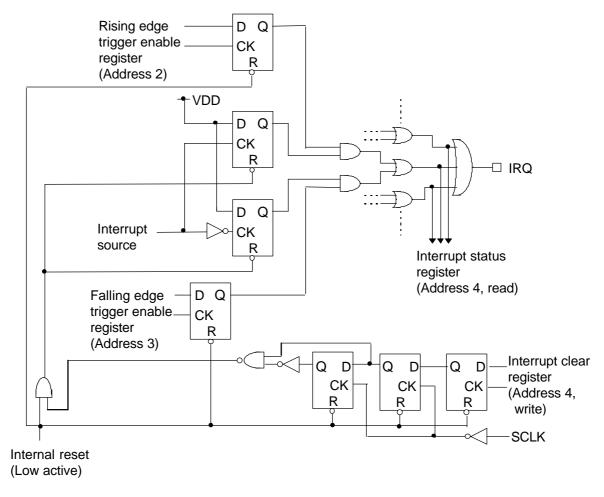

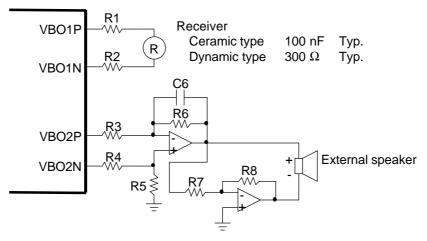

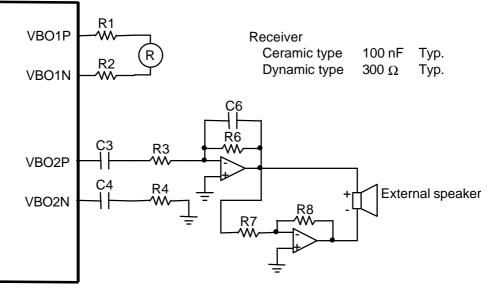

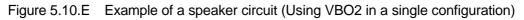

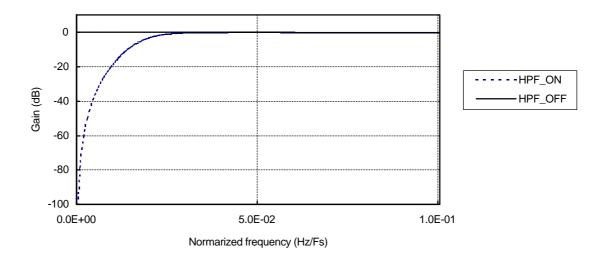

|      | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0         |         |