## ST14C04C

## CMOS SERIAL ACCESS 4K (2 blocks of 256 x 8) EEPROM

**BRIEF DATA**

- 1,000,000 ERASE/WRITE CYCLES MINIMUM

- OVER 10 YEARS DATA RETENTION

- SINGLE 3V to 5.5V POWER SUPPLY

- TWO WIRE SERIAL INTERFACE, FULLY I<sup>2</sup>C BUS COMPATIBLE

- BYTE and MULTIBYTE WRITE (UP TO 4 BYTES)

- PAGE WRITE (UP TO 8 BYTES)

- BYTE, RANDOM and SEQUENTIAL READ MODES

- SELF TIMED PROGRAMMING CYCLE

- AUTOMATIC ADDRESS INCREMENTING

- GUARANTEED 4KV ESD PROTECTION, USING HUMAN BODY MODEL

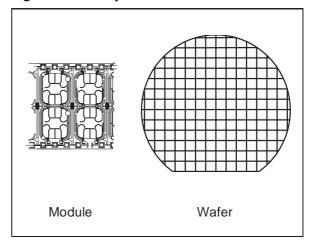

Figure 1 Delivery forms

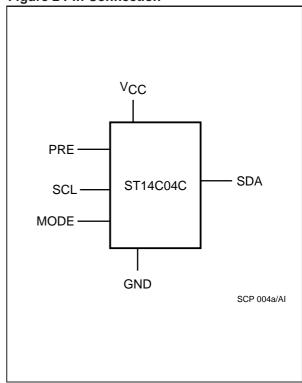

**Figure 2 Pin Connection**

**Table 1 Signal Names**

| PRE             | Write Protect Enable             |

|-----------------|----------------------------------|

| SDA             | Serial Data Address Input Output |

| SCL             | Serial Clock                     |

| MODE            | Write Mode                       |

| V <sub>CC</sub> | Supply Voltage                   |

| GND             | Ground                           |

BD.C04C/9609V1 1/2

**ST14C04C** BD.C04C/9609V1

## **DESCRIPTION**

The ST14C04C is a 4K bit electrically erasable programmable memory (EEPROM), organized as 2 blocks of 256 x 8 bits. It is manufactured in SGS-THOMSON's Hi-Endurance Advanced CMOS technology which confirms an endurance of more than 1,000,000 erase/write cycles with a data retention of over 10 years. This memory operates with a supply voltage value as low as 3V.

The memory is compatible with the I<sup>2</sup>C standard, two wire, serial interface which uses a bi-directional data bus and serial clock.

It carries a built-in 7 bit, unique device identification code (1010000) corresponding to the  $I^2C$  bus definition. Only one memory can be attached to the  $I^2C$  bus. This memory behaves as a slave de-

vice in the I<sup>2</sup>C protocol with all memory operations synchronized by the serial clock. Read and write operations are initiated by a START condition generated by the bus master. The START condition is followed by a stream of 7 bits (identification code 1010000), plus one read/write bit and terminated by an acknowledge bit.

When writing data to the memory it responds to the 8 bits received by asserting an acknowledge bit during the 9th bit time. When data is read by the bus master, it acknowledges the receipt of the data bytes in the same way. Data transfers are terminated with a STOP condition.

Both wafers (sawn or unsawn) and micromodules (on film) are available.

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without the express written approval of SGS-THOMSON Microelectronics.

© 1997 SGS-THOMSON Microelectronics - Printed in France - All Rights Reserved

Purchase of I<sup>2</sup>C Components by SGS-THOMSON Microelectronics conveys a licence under the Philips I<sup>2</sup>C Patent. Right to use these components in an I<sup>2</sup>C system is granted provided that the system conforms to the I<sup>2</sup>C Standard Specifications as defined by Philips.

SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco - The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.