## ASSP Communication Control

**CMOS**

# **SCSI-II Protocol Controller**

(with single-ended driver/receiver)

# MB86604L

#### ■ DESCRIPTION

The Fujitsu MB86604L is a single-ended transmission type SCSI-II Protocol Controller (SPC) with a single-ended driver/receiver. The MB86604L facilitates interface control between small/medium host computer and peripheral devices (such as a hard disk and printer). The specifications conform to the SCSI-II Standard.

The MB86604L supports high-speed synchronous transfer, the MPU/DMA independent system data bus, and user programmable command set to enable configuration of high-performance systems.

It can also have the phase-to-phase sequence control function to reduce the program overhead of the host MPU.

The MB86604L incorporate with a single-ended type SCSI driver/receiver which can drive 48 mA of large-current, and so, the device can be directly connected with the SCSI bus.

The device can operate with +5 V single-power supply and in up to 40 MHz clock frequency. As for package, a 100-pin plastic small quad flat package is available.

#### **■ FEATURES**

#### **SCSI Bus Interface:**

- Conforming to the SCSI-II standard

- · Operatable as Initiator and target

(Continued)

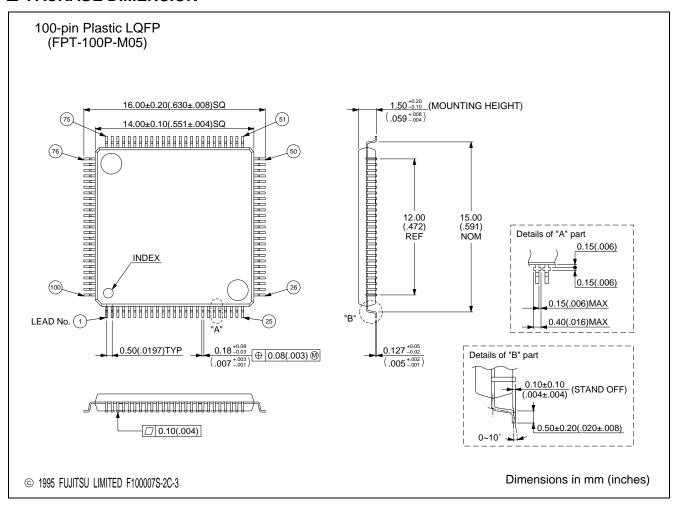

#### ■ PACKAGE

#### (Continued)

- Two types of high-speed data transfer:

- Synchronous data transfer (Max. 10 Mbytes/s, max. 32 offsets, 32-step transfer rate)

- Asynchronous data transfer (Max. 5 Mbyte/s)

- Transfer parameters (transfer mode, transfer rate, transfer offset) can be set for up to 7 connected devices.

- Single-ended transmission type (Maximum cable length: 6 m):

- On-chip single-ended driver/receiver which can drive 48 mA of "L" level output current

- Directly connectable with the SCSI bus

- On-chip three-state bidirectional I/O buffers for SCSI REQ and ACK pins (DB7-DB0, DBP, ATN, MSG, C/D, I/O pins can be selected from either three-state or open-drain buffer by controlling the TEST pins input.)

#### **Transfer Operation:**

- Automatic response to selection/reselection (Preset receiving operation can perform at the selection/reselection.):

- Initiator: Automatically operates until message received without command issue.

- Target: Automatically operates until command received without command issue.

- · Automatic receiving:

- Initiator: Automatically receives information for new phase to which target transited without command issue.

- Target: Automatically receives message from initiator when initiator generates attention condition.

- On-chip 32-byte data register (FIFO) for data phase

- On-chip two (send-only and receive-only) 32-byte data buffers for message, command, and status phases

- On-chip 16-bit transfer block register and 24-bit transfer byte register enabling 1 Tbytes transfer (1 Tbytes: 16 Mbytes × 64 k blocks)

- On-chip independent data transfer bus enabling the MPU operation during the data transfer

- · Parity through/generate can be specified.

#### **System Bus Interface:**

- 8-bit or 16-bit separate MPU and DMA buses

- Directly connectable with a 80 series or 68 series MPU

- Two types of transfer operation:

- Program transfer

- DMA transfer (Burst/Handshake)

#### **Command Set:**

- Supports sequential commands and programmable commands in addition to ordinary commands

- Command queuing (Command can be continuously issued by putting tags to commands in command phase.)

- On-chip 256-byte memory for command programming memory and command queuing buffer

#### **Others**

- Process: CMOS process

- Supply Voltage: Single +5 V

- Input System Clock: 20 MHz/30 MHz/40 MHz

- Package: 100-pin plastic LQFP

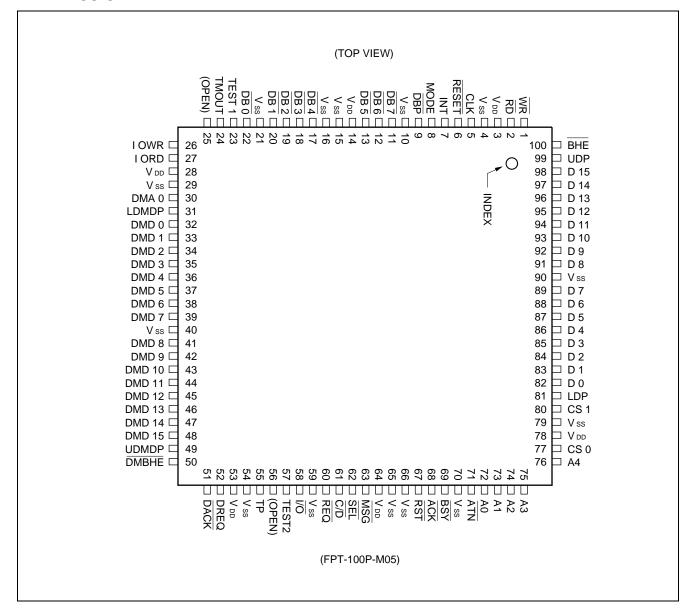

#### **■ PIN ASSIGNMENT**

## **■ PIN DESCRIPTION**

## 1. SCSI Interface

| Pin<br>number                        | Symbol           | Pin name                       | 1/0 | Function                                                                                                                                                                                                                                                                                                          |  |  |  |

|--------------------------------------|------------------|--------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 60                                   | REQ              | Request                        | I/O | Transfer request signal in the information transfer phases from target to initiator. The input signal to this pin is used for the timing control of data transfer sequence. This is a three-state I/O pin and an active low pin.                                                                                  |  |  |  |

| 68                                   | ACK              | Acknowledge                    | I/O | This pin is for the acknowledge signal from initiator to target for the REQ signal in the information transfer phases. The input signal to this pin is used for the timing control of data transfer sequence. This is a three-state I/O pin and an active low pin.                                                |  |  |  |

| 71                                   | ĀTN              | Attention                      | I/O | This pin is for the attention signal that initiator requests target for the message transfer phase. This is an active-low pin.                                                                                                                                                                                    |  |  |  |

| 63                                   | MSG*             | Message                        | I/O | This pin is for the message signal that specifies type of information transferred on the data bus. This is an active-low p and becomes "L" when message phase is specified.                                                                                                                                       |  |  |  |

| 61                                   | C/D*             | Control/data                   | I/O | This pin is for the control/data signal that specifies type of information transferred on the data bus. This an active-low pin and becomes "L" level when command, status, or message phase is specified.                                                                                                         |  |  |  |

| 58                                   | Ī/Ō*             | Input/output                   | I/O | This pin is for the input/output signal that specifies direction of information transferred on the data bus. This is an active-low pin. When this pin is "L" level, the information is transferred from target to initiator. When this pin is "H" level, the information is transferred from initiator to target. |  |  |  |

| 69                                   | BSY              | Busy                           | I/O | This pin is for the SCSI bus busy signal. In the arbitration phase, this is for the request signal for the use of bus acquisition. This is an active-low pin.                                                                                                                                                     |  |  |  |

| 62                                   | SEL              | Select                         | I/O | This pin is for the select signal used by initiator to select target during the selection phase and by target to reselect initiator during the reselection phase. This is an active-low pin.                                                                                                                      |  |  |  |

| 67                                   | RST              | Reset                          | I/O | This pin is for the reset signal used by any device on the bus. When the device is an input operation, the reset signal is input to this pin. When output operation, the reset signal is output from this pin. This is an active-low pin.                                                                         |  |  |  |

| 11, 12, 13,<br>17, 18, 19,<br>20, 22 | DB7<br>to<br>DB0 | Data bus 7<br>to<br>data bus 0 | I/O | These pins are for the bidirectional 8-bit SCSI data bus and 1-bit odd parity line.                                                                                                                                                                                                                               |  |  |  |

| 9                                    | DBP              | Data bus parity                |     |                                                                                                                                                                                                                                                                                                                   |  |  |  |

<sup>\* :</sup> Regarding the status of information transfer which is indicated by  $\overline{MSG}$ ,  $\overline{C/D}$ , and  $\overline{I/O}$  pins, See Table Phase Status.

| Phase name        | MSG   | C/D | Ī/O | Transfer direction |        |  |

|-------------------|-------|-----|-----|--------------------|--------|--|

| Filase fiame      | IVISG | C/D | 1/0 | Initiator          | Target |  |

| Data-out phase    | Н     | Н   | Н   | $\rightarrow$      |        |  |

| Data-in phase     | Н     | Н   | L   | <b>←</b>           |        |  |

| Command phase     | Н     | L   | Н   | $\rightarrow$      |        |  |

| Status phase      | Н     | L   | L   | <b>←</b>           |        |  |

| Message-out phase | L     | L   | Н   | $\rightarrow$      |        |  |

| Message-in phase  | L     | L   | L   | <b>←</b>           |        |  |

Note: The SCSI interface input/output pins can be connected to a single-end type SCSI bus.

## 2. MPU Interface

| Pin<br>number                        | Symbol*         | Pin name                        | I/O | Function                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------|-----------------|---------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 77                                   | CS0             | Chip select 0                   | I   | This is a chip select 0 pin used by MPU to select the SPC as an I/O device. This is an active-low pin.                                                                                                                                                                                                                                                               |

| 80                                   | CS1             | Chip select 1                   | I   | This is a chip select 1 pin to select when MPU inputs/outputs the data on DMA bus through SPC. This is an active-low pin.                                                                                                                                                                                                                                            |

| 98, 97, 96,<br>95, 94, 93,<br>92, 91 | D15<br>to<br>D8 | Data 15<br>to<br>data 8         | I/O | These pins are for the upper byte and parity bit of MPU data bus. When the CS0 input is valid, these pins serve as I/O ports for the SPC internal registers. When the CS1 input is valid, these pins                                                                                                                                                                 |

| 99                                   | UDP             | Upper data parity               |     | serve as I/O ports for the DMA bus data.                                                                                                                                                                                                                                                                                                                             |

| 89, 88, 87,<br>86, 85, 84,<br>83, 82 | D7<br>to<br>D0  | Data 7<br>to<br>data 0          | I/O | These pins are for the lower byte and parity bit of the MPU data bus. When the CS0 input is valid, these pins serve as I/O ports for the SPC internal registers. When the CS1 input is valid, these                                                                                                                                                                  |

| 81                                   | LDP             | Lower data parity               |     | pins serve as I/O ports for the DMA bus data.                                                                                                                                                                                                                                                                                                                        |

| 76, 75, 74,<br>73, 72                | A4<br>to<br>A0  | Address 4<br>to<br>address 0    | I   | These are address input pins to select the SPC internal registers.                                                                                                                                                                                                                                                                                                   |

| 2                                    | RD<br>(R/W)     | Read<br>(read/write)            | I   | In the 80-series mode, this is a read signal input pin (IORD or RD) that MPU reads the SPC. This read signal pin is an active-low. In the 68-series mode, this pin functions as the control signal input (R/W) to control the read/write operation to the SPC. In the read operation, this pin is an active-high. In the write operation, this pin is an active-low. |

| 1                                    | WR<br>(LDS)     | Write<br>(lower data<br>strobe) | I   | In the 80-series mode, this pin is a write signal input pin (IOWR or WR) that MPU writes to the SPC. This write signal input pin is active-low. In the 68-series mode, this pin function as the lower data strobe signal input (LDS) that MPU outputs when the lower byte of data bus is valid. The LDS pin is an active-low.                                        |

(Continued)

## (Continued)

| Pin<br>number | Symbol*      | Pin name                       | I/O | Function                                                                                                                                                                                                                                                                                                                                                                             |

|---------------|--------------|--------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 100           | BHE<br>(UDS) | Bus high<br>enable<br>(strobe) | I   | In the 80-series mode, this pin is used for input of the bus high enable signal (BHE) output from the MPU when the upper byte of the data bus is valid. The BHE pin is an active-low. In the 68-series mode, this pin functions as the upper data strobe signal input pin (UDS) output from the MPU when the upper byte of the data bus is valid. The UDS pin is also an active-low. |

| 7             | INT<br>(INT) | Interrupt<br>request           | 0   | The INT and INT pins are the interrupt request signal output. The INT pins is used for the 80-series mode (an active-high pin), and the INT signal is used for the 68-series mode (an active-low pin).                                                                                                                                                                               |

| 8             | MODE         | Mode                           | I   | This input pin is used to select the type of the MPU and DMA buses. In the 80-series mode, a high level is input. In the 68-series mode, a low level is input.                                                                                                                                                                                                                       |

$<sup>\</sup>mbox{\ensuremath{^{\star}}}$  : The pin symbols in parenthesis are the ones when the MODE input is "L".

## 3. DMA Interface

| Pin<br>number                        | Symbol*             | Pin name                                | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------|---------------------|-----------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 52                                   | DREQ                | DMA request                             | 0   | This is an output pin of DMA transfer request signal to the DMA controller. The data transfer between the SPC and memory via the DMA bus is requested. This pin is an active-high.                                                                                                                                                                                                                                                                                                                                |

| 51                                   | DACK                | DMA<br>acknowledge                      | I   | This is a DMA acknowledge signal input pin output from the DMA controller that enables the DMA transfer. This pin is an active-low. When this pin is an active state, the DMA cycle (read/write) is valid.                                                                                                                                                                                                                                                                                                        |

| 48, 47, 46,<br>45, 44, 43,<br>42, 41 | DMD15<br>to<br>DMD8 | DMA data 15<br>to<br>DMA data 8         | I/O | These pins are the input/output pins of the upper byte <u>and parity</u> bit of the DMA data bus. When the signal input to the <u>CS1</u> pin (pin 80) is valid, these pins are connected directly to the MPU                                                                                                                                                                                                                                                                                                     |

| 49                                   | UDMDP               | Upper DMA data parity                   |     | data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 39, 38, 37,<br>36, 35, 34,<br>33, 32 | DMD7<br>to<br>DMD0  | DMA data 7<br>to<br>DMA data 0          | I/O | These pins are the input/output pins of the lower byte and parity bit of the DMA data bus. When the CS1 (pin 80) input is valid, these pins are connected directly to the MPU data bus.                                                                                                                                                                                                                                                                                                                           |

| 31                                   | LDMDP               | Lower DMA data parity                   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 27                                   | IORD<br>(DMR/W)     | I/O read<br>(DMA read/<br>write)        | I   | In the 80-series mode, this pin ( $\overline{\text{IORD}}$ or $\overline{\text{RD}}$ ) is used for the input pin to output the data from the SPC to the DMA bus. This is an active-low pin. In the 68-series mode, this pin functions as a control signal input pin (DMR/ $\overline{\text{W}}$ ) to input/output the data to the SPC by the DMA controller. In the output operation, this pin is on the high-state (active-high state). In the input operation, this pin is on the low-state (active-low state). |

| 26                                   | IOWR<br>(DMLDS)     | I/O write<br>(DMA lower<br>data strobe) | I   | In the 80-series mode, this ( $\overline{\text{IOWR}}$ or $\overline{\text{WR}}$ ) is used for the input pin to input the DMA bus data to the SPC. In the 68-series mode, this pin functions as a DMA lower data strobe input ( $\overline{\text{DMLDS}}$ ) that DMA controller outputs when the lower byte of the DMA bus data is valid. Both $\overline{\text{IOWR}}$ and $\overline{\text{DMLDS}}$ pins are an active-low.                                                                                     |

(Continued)

## (Continued)

| Pin<br>number | Symbol*          | Pin name                                             | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------|------------------|------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 50            | DMBHE<br>(DMUDS) | DMA bus<br>high enable<br>(DMA upper<br>data strobe) | I   | In the 80-series mode, this pin is for the DMA bus high enable signal input pin (DMBHE) output from the DMA controller when the upper byte of the DMA data bus is valid. This is an active-low pin. In the 68-series mode, this pin functions as the DMA upper data strobe signal input pin (DMUDS) output from the DMA controller when the upper byte of data bus is valid. The DMUDS pin is also an active-low. |

| 30            | DMA0             | DMA<br>address 0                                     | I   | In the 80-series mode, this pin is used for the DMA address 0 input pin output from the DMA controller. In the 68-series mode, a high level should be input to this pin.                                                                                                                                                                                                                                          |

| 55            | TP               | Transfer permission                                  | I   | This is a DMA transfer permission signal input pin. When this pin is in active-state, the SPC does the DMA transfer. In case that this pin becomes inactive during the DMA transfer, the DMA transfer is paused on the block boundary. This pin is an active high.                                                                                                                                                |

<sup>\*:</sup> The pin symbols in parenthesis are the ones when the MODE input is "L".

#### 4. Others

| Pin<br>number                                                 | Symbol*         | Pin name     | I/O | Function                                                                                                                                                                                                                                                                                       |  |  |  |  |

|---------------------------------------------------------------|-----------------|--------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 6                                                             | RESET           | Reset        | I   | System reset input pin. The input reset active pulse width must have 4 times of the clock cycle at least. This is an active-low pin.                                                                                                                                                           |  |  |  |  |

| 5                                                             | CLK             | Clock        | Ι   | Clock signal input pin. 20 MHz, 30 MHz, or 40 MHz can be applied as the input clock frequency.                                                                                                                                                                                                 |  |  |  |  |

| 3, 14, 28<br>53, 64, 78                                       | V <sub>DD</sub> | Power supply | 1   | +5 V power supply pins.                                                                                                                                                                                                                                                                        |  |  |  |  |

| 4, 10, 15<br>16, 21, 29<br>40, 54, 59<br>65, 66, 70<br>79, 90 | Vss             | Ground       | _   | Ground pins.                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 23                                                            | TEST1           | TEST         | I   | This pin is used to select the type of I/O buffer on SCSI data bus pins. In case that DBP, DB7 – DB0 pins are used as an opendrain I/O, connect this pin to Vss. In case of three-state I/O, connect to VDD.                                                                                   |  |  |  |  |

| 57                                                            | TEST2           | TEST         | I   | This pin is used to select the type of I/O buffer on SCSI pins. In case that $\overline{\text{MSG}}$ , $\overline{\text{C/D}}$ , $\overline{\text{I/O}}$ , and $\overline{\text{ATN}}$ pins are used as an opendrain I/O, connect this pin to Vss. In case of three-state I/O, connect to VdD. |  |  |  |  |

| 24                                                            | TMOUT           | TIMEOUT      | 0   | This is a SCSI Timeout pin that indicates the SPC has been busy longer than the specified time. A high level is output on this pin if the SPC busy time exceeds the specified time. This pin can be used for the timeout counter.                                                              |  |  |  |  |

| 25, 26                                                        | (OPEN)          | (Open)       | _   | These are open pins. Those pins are not connected with the device internally. Those pins must be left open.                                                                                                                                                                                    |  |  |  |  |

<sup>\*:</sup> The pin symbols in parenthesis are the symbols when the MODE input is "L".

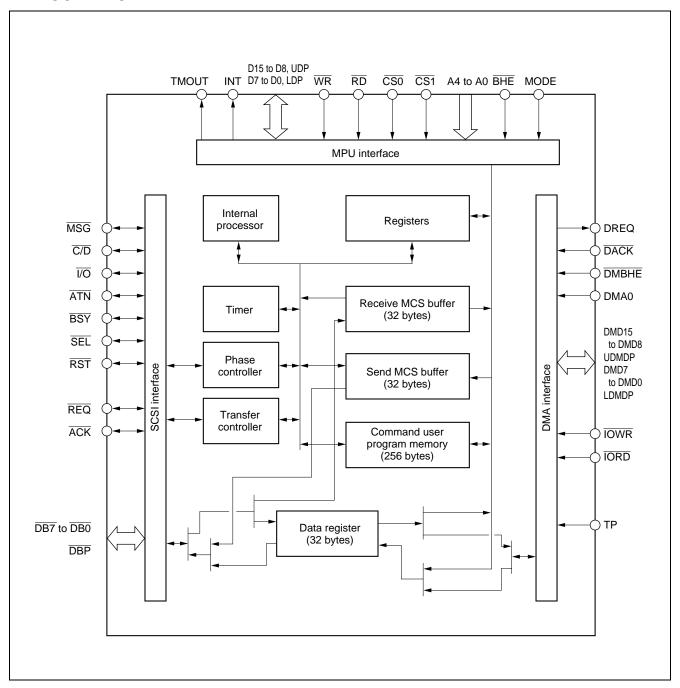

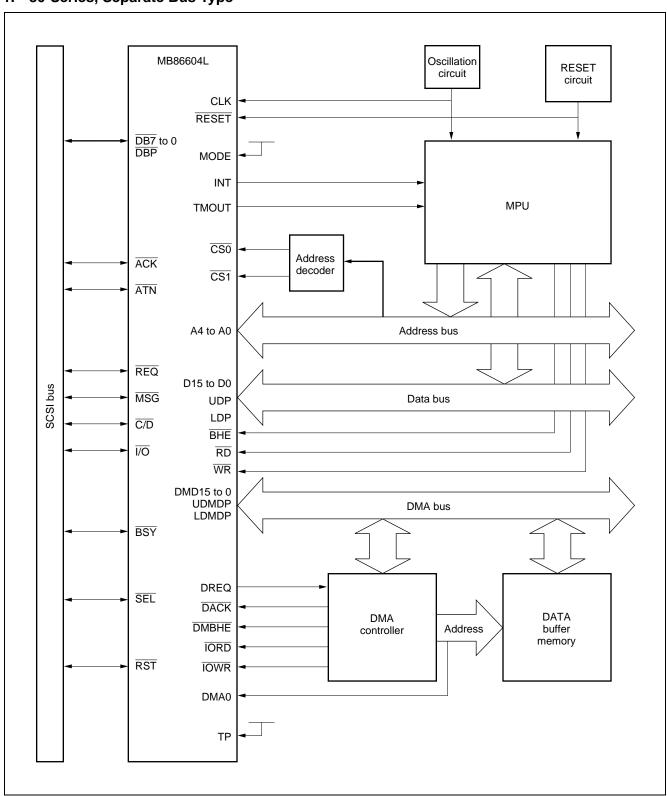

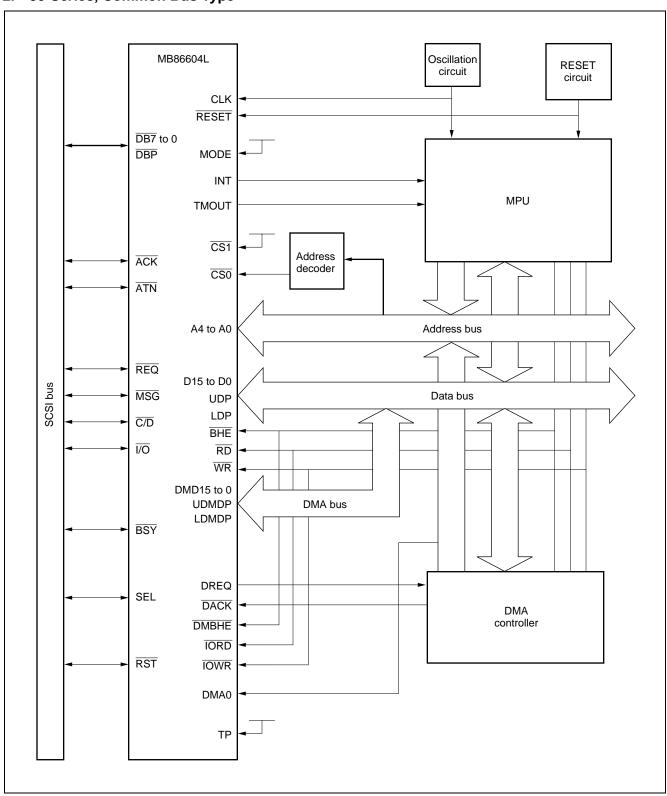

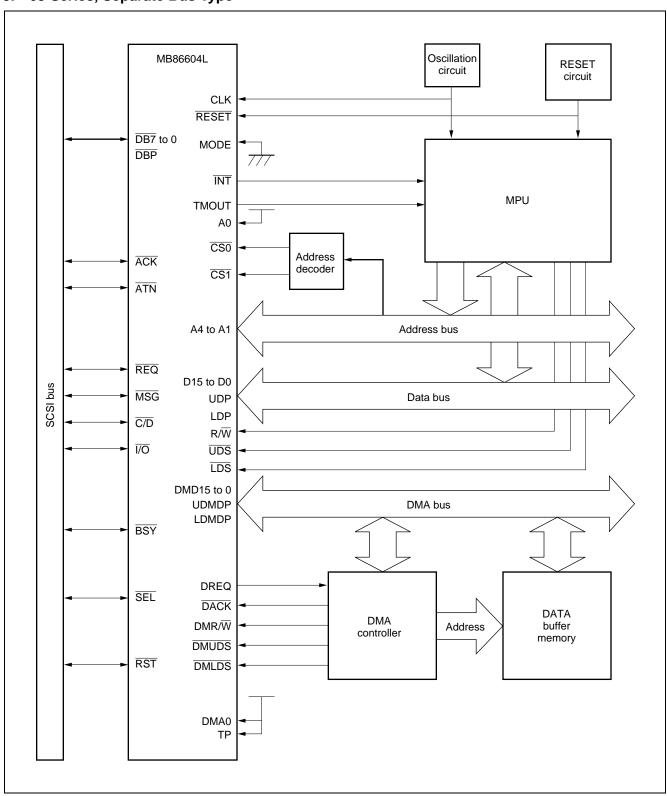

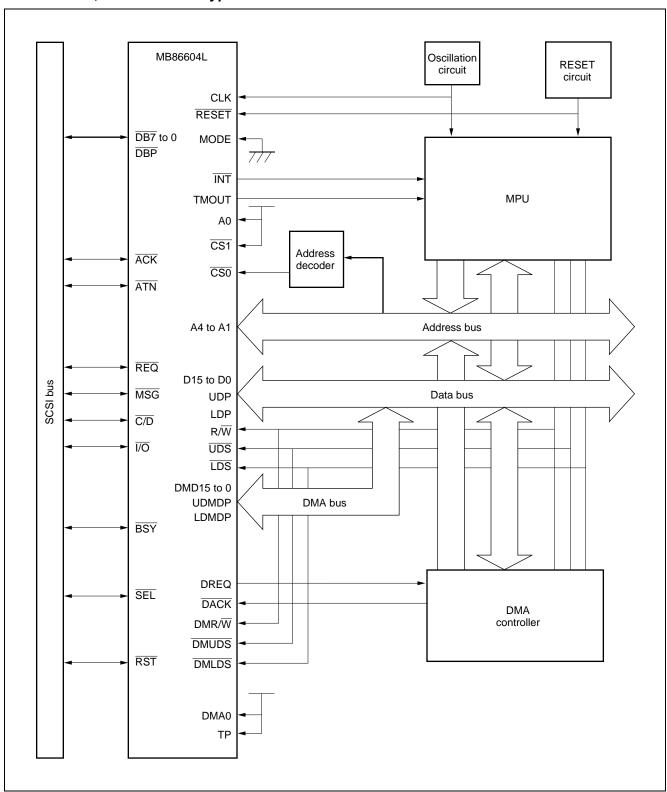

#### **■ BLOCK DIAGRAM**

#### **■ BLOCK DESCRIPTION**

#### 1. International Processor (Sequencer)

Performs sequence control between the SCSI bus phases.

#### 2. Timer

Manages the SCSI time standards.

Also, conducts the following time managements.

- Time until the REQ or ACK signal is asserted for asychronous transfer data

- · Time until selection or reselection is retried

- REQ and ACK timeout time during transfers:

Asychronous transfer case

Target: After the  $\overline{\text{REQ}}$  is asserted, the time until the initiator asserts the  $\overline{\text{ACK}}$

Initiator: After the ACK is asserted, the time until the target negates the REQ

Synchronous transfer case

Target: After the REQ is sent, the time until an ACK signal which makes the offset 0 is received from the initiator

SPC Timeout

Manages the SPC timeout indicating the SPC busy time longer than the specified time.

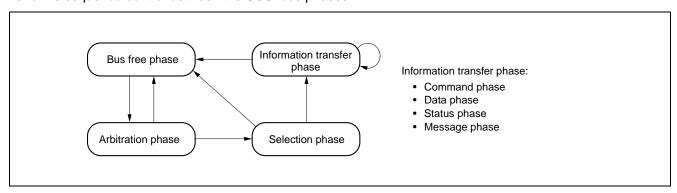

#### 3. Phase Controller

Controls the various phases executed by SCSI such as arbitration, selection/reselection, data in/out, command, status, and message in/out.

#### 4. Transfer Controller

Controls the information (data, command, status, message) transfer phases executed by SCSI.

The following two types of transfer phases are used.

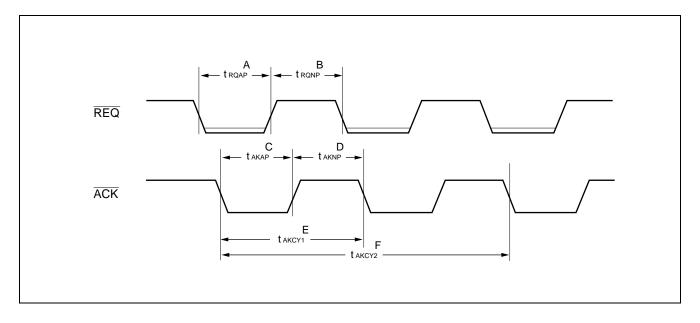

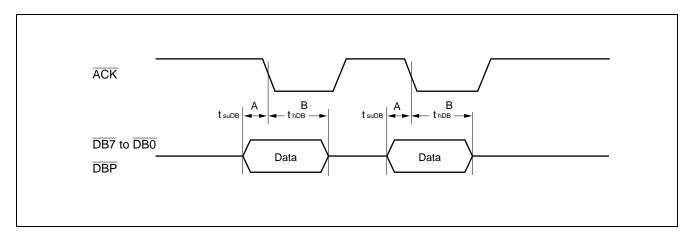

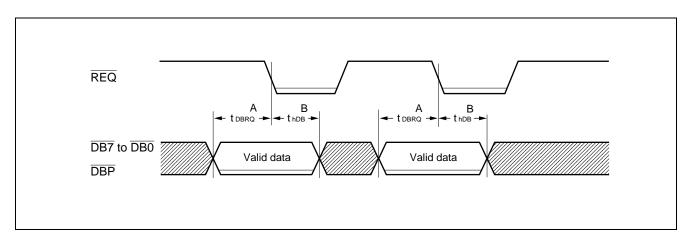

Asychronous transfer: Controls interlock (response confirmation format) between the  $\overline{\text{REQ}}$  and  $\overline{\text{ACK}}$  signals.

Synchronous transfer: Controls a maximum 32-byte offset value for the data in or data out phase.

The following two modes exist for the data phase.

Program transfer: Uses data register (address 00/01) via the MPU interface

DMA transfer: Uses DREQ and DACK signals via the DMA interface.

The transfer parameter setting values for synchronous transfer (Transfer mode, transfer rate, transfer offset) can be strobe for individual ID device and are automatically established when the data phase is initiated.

The number of transfer bytes is defined as block length × number of blocks.

#### 5. Register

The main registers are listed.

• Command register

Command is specified by an 8-bit code.

Specifies the program head address assigned to the user program memory for user program applications.

· Chip status register

Shows the chip's operating state, nexus counterpart ID, and data register state.

· SCSI bus status register

Shows the SCSI control signal state.

• Interrupt status register

Shows 8-bit code.

• Command step register

Shows 8-bit code indicating the command execution state.

Error analysis can be performed by referring to the information in this register and the interrupt status register.

• Group 6/7 command length setting register

Sets the group 6/7 command length which is undefined by the SCSI standard.

By setting the command length in this register, the SPC can determine the command length.

#### 6. Receive-MCS Buffer

A receive only, 32-byte data buffer which stores information received via SCSI (message, command, status)

M: Message, C: Command, S: Status

#### 7. Send-MCS Buffer

A send only, 32-byte data buffer which stores information sent via SCSI (message, command, status)

#### 8. Command User Program Memory

Program memory used for establishing programmable commands (256 bytes).

#### 9. Data Register

FIFO-type data register which stores data in SCSI data phase (32 bytes).

## ■ ABSOLUTE MAXIMUM RATINGS (See WARNING)

| Parameter                     | Symbol          | Rat       | Unit                  |      |  |

|-------------------------------|-----------------|-----------|-----------------------|------|--|

| Parameter                     | Symbol          | Min.      | Max.                  | Oill |  |

| Power supply voltage*         | V <sub>DD</sub> | Vss - 0.5 | 6.0                   | V    |  |

| Input voltage*                | Vı              | Vss - 0.5 | V <sub>DD</sub> + 0.5 | V    |  |

| Output voltage*               | Vo              | Vss - 0.5 | V <sub>DD</sub> + 0.5 | V    |  |

| Operating ambient temperature | Тор             | -25       | +85                   | °C   |  |

| Storage temperature           | Tstg            | -40       | +125                  | °C   |  |

<sup>\* :</sup> Vss = 0 V

WARNING: Permanent device damage may occur if the above Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### ■ RECOMMENDED OPERATING CONDITIONS

| Parameter                      |                  |                | Symbol          |      | Unit  |      |    |

|--------------------------------|------------------|----------------|-----------------|------|-------|------|----|

|                                | Symbol           | Min.           | Тур.            | Max. | Offic |      |    |

| Power supply volta             | age *1           |                | V <sub>DD</sub> | 4.75 | 5.0   | 5.25 | V  |

|                                | CLK              |                |                 | 3.5  | _     | _    | V  |

| "H" level<br>input voltage *1  | Except SCS       | I and CLK pins | Vıн             | 2.2  | _     | _    | V  |

| input voitage                  | SCSI pins        |                |                 | 2.0  | _     | _    | V  |

| "L" level                      | CLK              |                | VIL             | _    | _     | 1.5  | V  |

| input voltage *1               | Except CLK       | ( pin          | VIL             | _    | _     | 0.8  | V  |

|                                | Except SCSI pins |                |                 | _    | _     | -2.0 | mA |

| "H" level<br>output current *2 | SCSI pins        | Three-state    | Іон             | _    | _     | -8.0 | mA |

|                                | SCSI PILIS       | Open-drain     |                 | _    | _     | _    | mA |

| "L" level                      | Except SCSI pins |                |                 | _    | _     | +3.2 | mA |

| output current *2              | SCSI pins        |                | lol             | _    | _     | +48  | mA |

| Operating ambien               | t temperature    | e              | Та              | 0    | _     | +70  | °C |

<sup>\*1:</sup> Vss = 0 V

Note: The recommended operating conditions are the values recommended to ensure correct logic operation of the LSI. The standard values of the electrical characteristics (DC and AC characteristics) are guaranteed within the range of the recommended operating conditions.

<sup>\*2:</sup> SCSI pins are DB7 to DB0, DBP, BSY, SEL, RST, ATN, REQ, ACK, MSG, C/D, I/O

#### **■ ELECTRICAL CHARACTERISTICS**

#### 1. DC Characteristics

$(V_{DD} = +5 V \pm 5\%, V_{SS} = 0 V, Ta = 0^{\circ}C \text{ to } +70^{\circ}C)$

| Porc                           | ameter         |                | Cumbal          |                            | Condition                                          | Va                                                         | lue                                                                                                                                                                                                               | Unit |

|--------------------------------|----------------|----------------|-----------------|----------------------------|----------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Para                           | ameter         |                | Symbol          |                            | Condition                                          | Min.                                                       | Max.                                                                                                                                                                                                              | Unit |

|                                | CLK            |                |                 |                            |                                                    | 3.5                                                        | _                                                                                                                                                                                                                 | V    |

| "H" level input voltage        | Excep<br>CLK p | t SCSI and ins | Vıн             |                            | _                                                  | Min.                                                       | _                                                                                                                                                                                                                 | V    |

|                                | SCSI           | pins           |                 |                            |                                                    | 2.0                                                        | Min.     Max.       3.5     —       2.2     —       2.0     —       —     1.5       —     0.8       0.3     —       4.2     VDD       2.0     —       —     —       Vss     0.4       —     0.5       -10     +10 | V    |

| "L" level                      | CLK            |                | \/              | Vih                        | _                                                  | 1.5                                                        | V                                                                                                                                                                                                                 |      |

| input voltage                  | Excep          | t CLK pin      | VIL             |                            | _                                                  | 0.8                                                        | V                                                                                                                                                                                                                 |      |

| Input hysteresis o             | f SCSI         | pins *1        | V <sub>HW</sub> |                            | _                                                  | 0.3                                                        | _                                                                                                                                                                                                                 | V    |

|                                | Excep          | t SCSI pins    |                 | Iон = −2.0 r               | mA                                                 | 4.2                                                        | V <sub>DD</sub>                                                                                                                                                                                                   | V    |

| "H" level<br>output voltage *1 | SCSI           | Three-state    | Vон             | $I_{OH} = -8.0 \text{ mA}$ |                                                    |                                                            | _                                                                                                                                                                                                                 | V    |

|                                | pins           | Open-drain     |                 |                            | _                                                  | - 0.8  0.3 - 4.2 Vdd  2.0 Vss 0.4  - 0.5  -10 +10   45   r | V                                                                                                                                                                                                                 |      |

| "L" level                      | Excep          | t SCSI pins    | Vo              | loL = +3.2 mA              |                                                    | Vss                                                        | 0.4                                                                                                                                                                                                               | V    |

| output voltage *1              | SCSI           | pins           | VOL             | IoL = +48.0                | mA                                                 | _                                                          | Min. Max.  3.5 —  2.2 —  2.0 —  1.5 —  0.8  0.3 —  4.2 VDD  2.0 —  Vss 0.4  — 0.5  —10 +10  —10 +10  45  48  55  —65  60                                                                                          | V    |

| Input leakage curi             | rent           |                | Iы              | $V_{SS} \le V_I \le V_I$   | / <sub>DD</sub>                                    |                                                            |                                                                                                                                                                                                                   | μΑ   |

| Input/output leaka             | ige curi       | ent            | lloz            | $V_{SS} \leq V_I \leq V$   | /dd, See Note below                                | -10                                                        | +10                                                                                                                                                                                                               | μΑ   |

|                                |                |                |                 |                            |                                                    |                                                            | 45                                                                                                                                                                                                                | mA   |

|                                |                |                |                 |                            |                                                    |                                                            | 48                                                                                                                                                                                                                | mA   |

| Power supply our               | ont            |                | laa             |                            |                                                    |                                                            | 55                                                                                                                                                                                                                | mA   |

| Power supply current           |                | IDD            |                 |                            |                                                    | 65                                                         | mA                                                                                                                                                                                                                |      |

|                                |                |                |                 |                            |                                                    |                                                            | 60                                                                                                                                                                                                                | mA   |

|                                |                |                |                 |                            | CLK input = 40 MHz<br>SPC operating clock = 20 MHz |                                                            | Min. Max.  3.5 —  2.2 —  2.0 —  1.5 —  0.8  0.3 —  4.2 VDD  2.0 —  Vss 0.4  — 0.5  —10 +10  —10 +10  45  48  55  —65  60                                                                                          | mA   |

<sup>\*1:</sup> SCSI pins are DB7 to DB0, DBP, BSY, SEL, RST, ATN, REQ, ACK, MSG, C/D, I/O

Note: Leakage current in the above spec indicates the following currents.

- (1) Leakage current at the high-Z state on the three-state output pins.

- (2) Leakage current at the output high-Z state (input state) on the bidirectional bus pins.

## 2. I/O Pin Capacitance

| Param                          | otor             | Symbol | Va   | lue  | Unit  |

|--------------------------------|------------------|--------|------|------|-------|

| Faiaiii                        | etei             | Symbol | Min. | Max. | Offic |

| Input pin capacitance          |                  | Cin    | _    | 6    | pF    |

| Output pin capacitance         |                  | Соит   | _    | 6    | pF    |

| I/O nin conscitance            | Except SCSI pins | Core   | _    | 6    | pF    |

| I/O pin capacitance  SCSI pins |                  | C1/0   | _    | 25   | pF    |

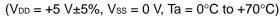

### 3. Load Conditions for AC Characteristics

#### 4. AC Characteristics

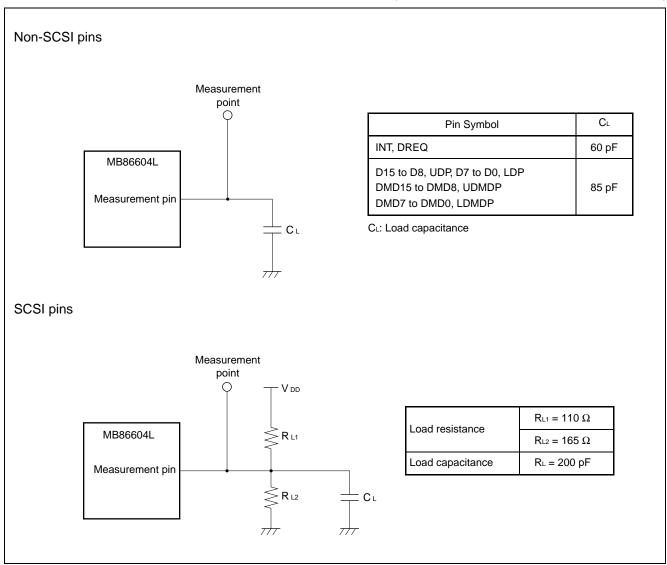

#### (1) System clock

| Doromotor              | Symbol        |           | Va   | lue  | l lmi4 |  |

|------------------------|---------------|-----------|------|------|--------|--|

| Parameter              | Symbol        | Position* | Min. | Max. | Unit   |  |

| Clock cycle time (CLK) | <b>t</b> clk  | А         | 25.0 | 50.0 | ns     |  |

| Clock "H" pulse width  | <b>t</b> wckH | В         | 10.0 | _    | ns     |  |

| Clock "L" pulse width  | twckl         | С         | 10.0 | _    | ns     |  |

| Clock rise time        | <b>t</b> CR   | D         | _    | 10.0 | ns     |  |

| Clock fall time        | <b>t</b> CF   | E         | _    | 10.0 | ns     |  |

<sup>\*:</sup> The position number indicates the position in the waveform.

Note: In case that the internal clock frequency and the input clock frequency are the same (i.e. when using the divided-by-one mode), the clock pulse width (for "H" and "L") must have at least 20 ns or longer.

### (2) System reset

| Parameter                   |        | Va     | Unit |       |

|-----------------------------|--------|--------|------|-------|

| Parameter                   | Symbol | Min.   | Max. | Offic |

| RESET "L" level pulse width | twRSL  | 4 tclk | _    | ns    |

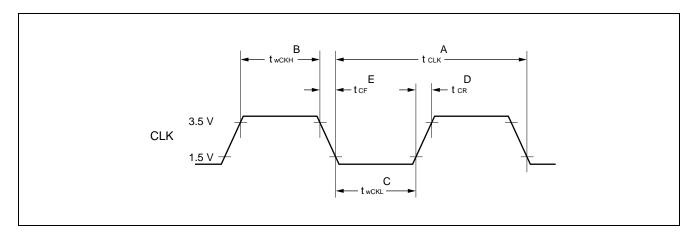

## (3) MPU interface (80 series)

## • Register write timing

| Parameter                           |             | Symbol        |           | Value |      | Unit  |

|-------------------------------------|-------------|---------------|-----------|-------|------|-------|

| Faranietei                          | Base signal | Syllibol      | Position* | Min.  | Max. | Oilit |

| Address (A4 to A0), BHE set up time | WR "L"      | <b>t</b> suA  | Α         | 40    | _    | ns    |

| Address (A4 to A0), hold time       | WR "H"      | <b>t</b> hA   | В         | 20    | _    | ns    |

| CS0 set up time                     | WR "L"      | tsuCS0        | С         | 20    | _    | ns    |

| CS0 hold time                       | WR "H"      | thcs0         | D         | 10    | _    | ns    |

| WR "L" level pulse width            | _           | <b>t</b> wWRL | E         | 70    | _    | ns    |

| Data set up time                    | WR "H"      | <b>t</b> suD  | F         | 40    | _    | ns    |

| Data hold time                      | WR "H"      | <b>t</b> hD   | G         | 10    | _    | ns    |

<sup>\*:</sup> The position number indicates the position in the waveform.

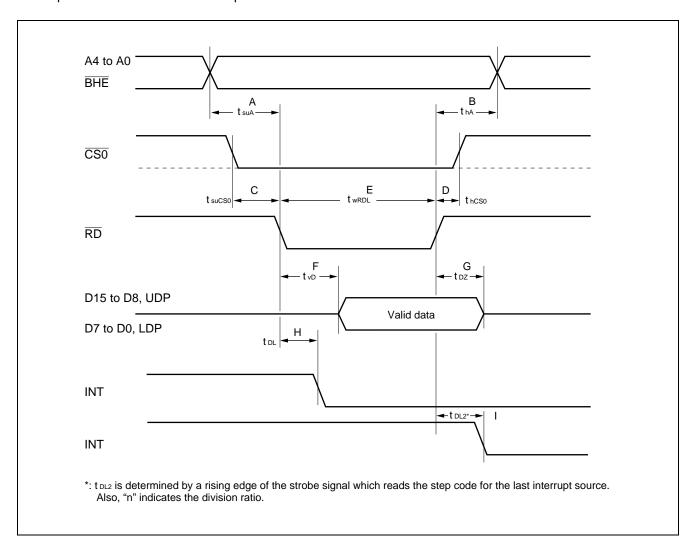

## • Register read timing

|              | Parameter                 |             | Symbol           | Value     |      | lue         | Unit  |

|--------------|---------------------------|-------------|------------------|-----------|------|-------------|-------|

|              | Parameter                 | Base signal | Symbol           | Position* | Min. | Max.        | Offic |

| Address (A   | 4 to A0), BHE set up time | RD "L"      | <b>t</b> suA     | Α         | 40   | _           | ns    |

| Address (A   | 4 to A0), Hold time       | RD "H"      | <b>t</b> hA      | В         | 20   | _           | ns    |

| CS0 set up   | time                      | RD "L"      | tsuCS0           | С         | 20   | _           | ns    |

| CS0 hold tir | me                        | RD "H"      | thcs0            | D         | 10   | _           | ns    |

| RD "L" level | pulse width               | _           | twrdl            | Е         | 70   | _           | ns    |

| Data output  | defined time              | RD "L"      | tvD              | F         | _    | 70          | ns    |

| Data output  | disable time              | RD "H"      | <b>t</b> dz      | G         | 10   | _           | ns    |

| INT signal   | for INT non-hold mode     | RD "L"      | <b>t</b> DL      | Н         | _    | 50          | ns    |

| clear time   | for INT hold mode         | RD "H"      | t <sub>DL2</sub> | I         | _    | n tclк + 50 | ns    |

<sup>\*:</sup> The position number indicates the position in the waveform.

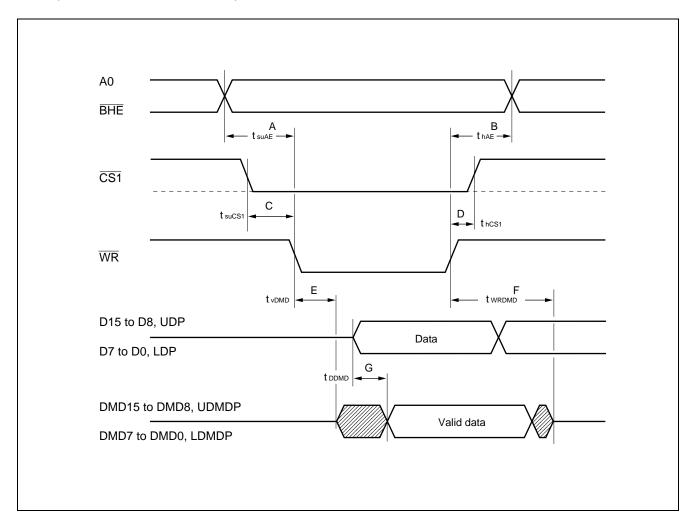

## • Register write timing (for external access)

| Parameter                                            |             | Symbol        |           | Value |      | Unit |

|------------------------------------------------------|-------------|---------------|-----------|-------|------|------|

| Farameter                                            | Base signal | Symbol        | Position* | Min.  | Max. | Unit |

| Address (A0), BHE set up time                        | WR "L"      | <b>t</b> suAE | Α         | 40    | _    | ns   |

| Address (A0), BHE hold time                          | WR "H"      | <b>t</b> hAE  | В         | 20    | _    | ns   |

| CS1 set up time                                      | WR "L"      | tsuCS1        | С         | 20    | _    | ns   |

| CS1 hold time                                        | WR "H"      | thcs1         | D         | 10    | _    | ns   |

| DMA data bus output delay time                       | WR "L"      | <b>t</b> vDMD | Е         | _     | 70   | ns   |

| DMA data bus output undefined time                   | WR "H"      | twrdmd        | F         | 10    | _    | ns   |

| MPU data $ ightarrow$ DMA data bus output delay time | _           | <b>t</b> DDMD | G         | _     | 40   | ns   |

$<sup>\</sup>ensuremath{^{\star}}$  : The position number indicates the position in the waveform.

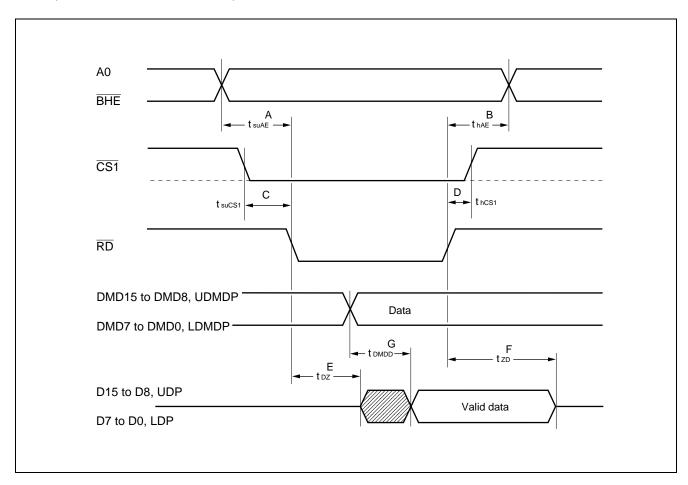

### • Register read timing (for external access)

| Parameter                                            |             | Symbol        |           | Value |      | Unit |

|------------------------------------------------------|-------------|---------------|-----------|-------|------|------|

| Farameter                                            | Base signal | Symbol        | Position* | Min.  | Max. | Unit |

| Address (A0), BHE set up time                        | RD "L"      | <b>t</b> suAE | А         | 40    | _    | ns   |

| Address (A0), BHE hold time                          | RD "H"      | <b>t</b> hAE  | В         | 20    | _    | ns   |

| CS1 set up time                                      | RD "L"      | tsuCS1        | С         | 20    | _    | ns   |

| CS1 hold time                                        | RD "H"      | thcs1         | D         | 10    | _    | ns   |

| MPU data bus output enable time                      | RD "L"      | <b>t</b> zd   | Е         | _     | 70   | ns   |

| MPU data bus output disable time                     | RD "H"      | <b>t</b> dz   | F         | 10    | _    | ns   |

| DMA data $ ightarrow$ MPU data bus output delay time | _           | <b>t</b> DMDD | G         | _     | 40   | ns   |

<sup>\*:</sup> The position number indicates the position in the waveform.

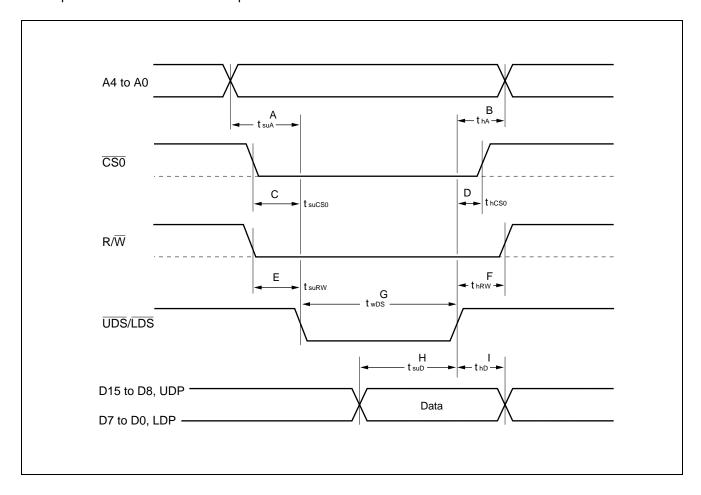

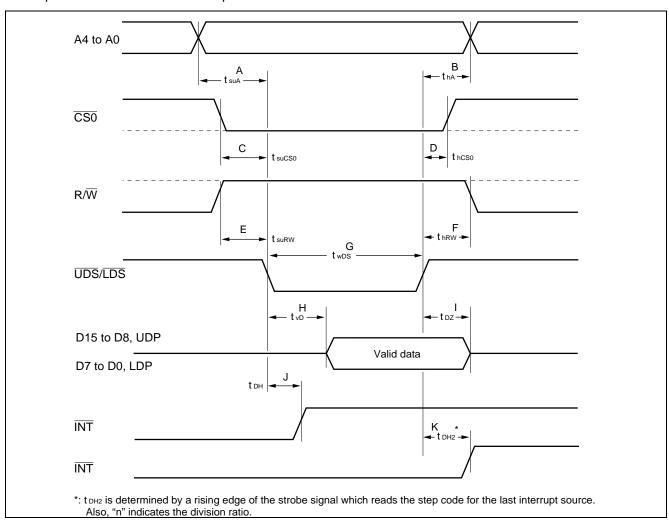

## (4) MPU interface (68 series)

## • Register write timing

| Parameter                      |             | Symbol        |           | Value |      | Unit |

|--------------------------------|-------------|---------------|-----------|-------|------|------|

| Farameter                      | Base signal | Symbol        | Position* | Min.  | Max. | Unit |

| Address (A4 to A0) set up time | UDS/LDS "L" | <b>t</b> suA  | Α         | 40    | _    | ns   |

| Address (A4 to A0) hold time   | UDS/LDS "H" | <b>t</b> hA   | В         | 20    | _    | ns   |

| CS0 set up time                | UDS/LDS "L" | tsuCS0        | С         | 20    | _    | ns   |

| CS0 hold time                  | UDS/LDS "H" | thcs0         | D         | 10    | _    | ns   |

| R/W set up time                | UDS/LDS "L" | <b>t</b> suRW | E         | 20    | _    | ns   |

| R/W hold time                  | UDS/LDS "H" | thRW          | F         | 20    | _    | ns   |

| UDS/LDS "L" level pulse width  | _           | twDS          | G         | 70    | _    | ns   |

| Data set up time               | UDS/LDS "H" | <b>t</b> suD  | Н         | 40    | _    | ns   |

| Data hold time                 | UDS/LDS "H" | <b>t</b> hD   | I         | 10    | _    | ns   |

<sup>\*:</sup> The position number indicates the position in the waveform.

### • Register read timing

|              | Parameter             |             | Symbol        |           | Value |             | l lni4 |

|--------------|-----------------------|-------------|---------------|-----------|-------|-------------|--------|

|              | Parameter             | Base signal | Symbol        | Position* | Min.  | Max.        | Unit   |

| Address (A4  | 4 to A0) set up time  | UDS/LDS "L" | <b>t</b> suA  | А         | 40    | _           | ns     |

| Address (A   | 4 to A0) hold time    | UDS/LDS "H" | <b>t</b> hA   | В         | 20    | _           | ns     |

| CS0 set up   | time                  | UDS/LDS "L" | tsuCS0        | С         | 20    | _           | ns     |

| CS0 hold tir | me                    | UDS/LDS "H" | thcs0         | D         | 10    | _           | ns     |

| R/W set up   | time                  | UDS/LDS "L" | <b>t</b> suRW | Е         | 20    | _           | ns     |

| R/W hold tir | me                    | UDS/LDS "H" | thRW          | F         | 20    | _           | ns     |

| UDS/LDS "I   | _" level pulse time   | _           | twDS          | G         | 70    | _           | ns     |

| Data output  | confirmation time     | UDS/LDS "L" | tvD           | Н         | _     | 70          | ns     |

| Data output  | disable time          | UDS/LDS "H" | <b>t</b> dz   | I         | 10    | _           | ns     |

| INT signal   | for INT non-hold mode | UDS/LDS "L" | <b>t</b> DH   | J         | _     | 50          | ns     |

| clear time   | for INT hold mode     | UDS/LDS "H" | <b>t</b> DH2  | К         | _     | n tclk + 50 | ns     |

<sup>\*:</sup> The position number indicates the position in the waveform.

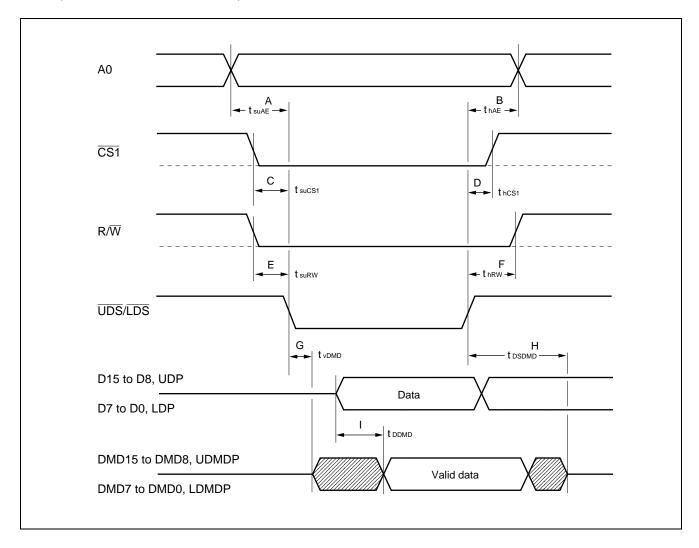

### • Register write timing (for external access)

| Parameter                                            |             | Symbol        |           | Value |      | Unit |

|------------------------------------------------------|-------------|---------------|-----------|-------|------|------|

| Farameter                                            | Base signal | Symbol        | Position* | Min.  | Max. | Unit |

| Address (A0) set up time                             | UDS/LDS "L" | <b>t</b> suAE | Α         | 40    | _    | ns   |

| Address (A0) hold time                               | UDS/LDS "H" | <b>t</b> hAE  | В         | 20    | _    | ns   |

| CS1 set up time                                      | UDS/LDS "L" | tsuCS1        | С         | 20    | _    | ns   |

| CS1 hold time                                        | UDS/LDS "H" | thcs1         | D         | 10    | _    | ns   |

| R/W set up time                                      | UDS/LDS "L" | <b>t</b> suRW | Е         | 20    | _    | ns   |

| R/W hold time                                        | UDS/LDS "H" | <b>t</b> hRW  | F         | 20    | _    | ns   |

| DMA data bus output delay time                       | UDS/LDS "L" | t√DMD         | G         |       | 70   | ns   |

| DMA data bus output undefined time                   | UDS/LDS "H" | tosomo        | Н         | 10    | _    | ns   |

| MPU data $ ightarrow$ DMA data bus output delay time | _           | <b>t</b> DDMD | I         | _     | 40   | ns   |

<sup>\*:</sup> The position number indicates the position in the waveform.

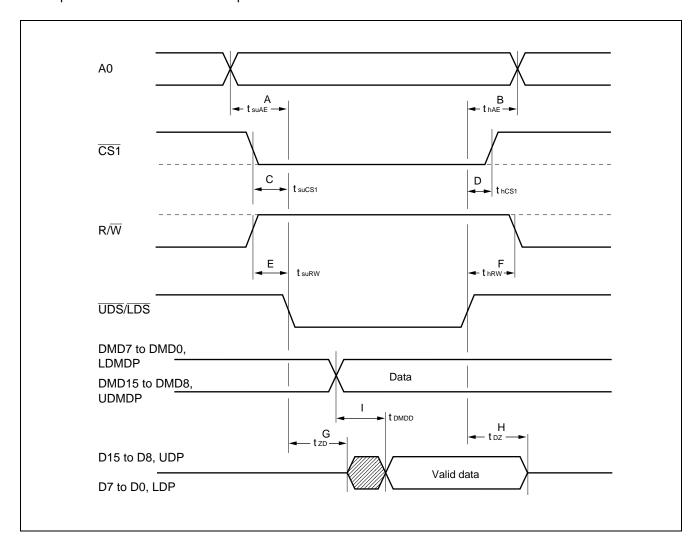

### • Register read timing (for external access)

| Parameter                                            |             | Symbol        |           | Value |      | Unit |

|------------------------------------------------------|-------------|---------------|-----------|-------|------|------|

| Farameter                                            | Base signal | Syllibol      | Position* | Min.  | Max. | Unit |

| Address (A0) set up time                             | UDS/LDS "L" | <b>t</b> suAE | А         | 40    | _    | ns   |

| Address (A0) hold time                               | UDS/LDS "H" | <b>t</b> hAE  | В         | 20    | _    | ns   |

| CS1 set up time                                      | UDS/LDS "L" | tsuCS1        | С         | 20    | _    | ns   |

| CS1 hold time                                        | UDS/LDS "H" | <b>t</b> hCS1 | D         | 10    | _    | ns   |

| R/W set up time                                      | UDS/LDS "L" | tsuRW         | Е         | 20    | _    | ns   |

| R/W hold time                                        | UDS/LDS "H" | <b>t</b> hRW  | F         | 20    | _    | ns   |

| Data output enable time                              | UDS/LDS "L" | <b>t</b> zd   | G         | _     | 70   | ns   |

| Data output disable time                             | UDS/LDS "H" | <b>t</b> dz   | Н         | 10    | _    | ns   |

| DMA data $ ightarrow$ MPU data bus output delay time | _           | <b>t</b> dmdd | I         | _     | 40   | ns   |

<sup>\*:</sup> The position number indicates the position in the waveform.

#### (5) DMA interface

The DMA access timing described in this section is not applicable in the following cases.

During SCSI input, when the data buffer is EMPTY or when one byte is stored During SCSI output, when the data buffer is FULL or when 31 bytes are stored

When a parity error is detected (target)

When an error which pauses the transfer occurs at the SCSI interface

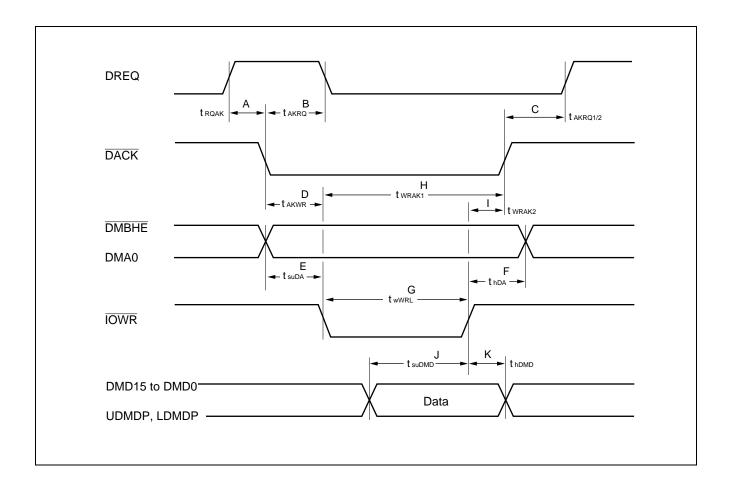

#### • 80 series handshake mode

#### (a) Write timing

| Parameter                     |             | Symbol         |           | Value          |             | l lni4 |

|-------------------------------|-------------|----------------|-----------|----------------|-------------|--------|

| Parameter                     | Base signal | Symbol         | Position* | Min.           | Max.        | Unit   |

| DACK "L" assert time          | DREQ "H"    | <b>t</b> rqak  | Α         | 0              | _           | ns     |

| DREQ "L" negate time          | DACK "L"    | <b>t</b> akrq  | В         | _              | 40          | ns     |

| DREQ "H" assert time (8 bit)  | DACK "H"    | <b>t</b> akrq1 | С         | _              | 50          | ns     |

| DREQ "H" assert time (16 bit) | DACK "H"    | <b>t</b> akrq2 | С         | _              | 2 tclk + 40 | ns     |

| IOWR "L" assert time          | DACK "L"    | <b>t</b> akwr  | D         | 0              | _           | ns     |

| DMBHE, DMA0 set up time       | ĪOWR "L"    | <b>t</b> suDA  | Е         | 20             | _           | ns     |

| DMBHE, DMA0 hold time         | ĪOWR "H"    | <b>t</b> hDA   | F         | 20             | _           | ns     |

| IOWR "L" level pulse width    | _           | twwrl          | G         | 40             | _           | ns     |

| DACK "Ll" pageta timo         | ĪOWR "L"    | <b>t</b> wrak1 | Н         | <b>1 t</b> ськ | _           | ns     |

| DACK "H" negate time          | IOWR "H"    | twrak2         | I         | 0              | _           | ns     |

| Input data set up time        | ĪOWR "H"    | <b>t</b> suDMD | J         | 30             | _           | ns     |

| Input data hold time          | IOWR "H"    | <b>t</b> hDMD  | К         | 5              | _           | ns     |

<sup>\*:</sup> The position number indicates the position in the waveform.

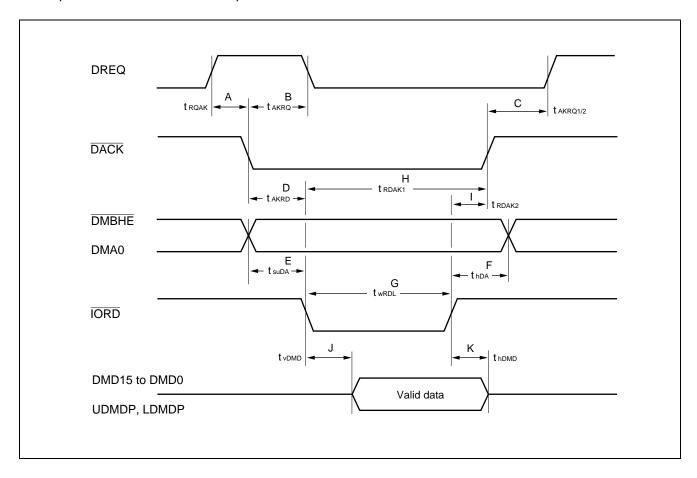

## (b) Read timing

| Parameter                     |             | Symbol         |           | Value          |             | Unit |

|-------------------------------|-------------|----------------|-----------|----------------|-------------|------|

| Farameter                     | Base signal | Symbol         | Position* | Min.           | Max.        | Unit |

| DACK "L" assert time          | DREQ "H"    | <b>t</b> rqak  | А         | 0              | _           | ns   |

| DREQ "L" negate time          | DACK "L"    | <b>t</b> akrq  | В         | _              | 40          | ns   |

| DREQ "H" assert time (8 bit)  | DACK "H"    | <b>t</b> akrq1 | С         | _              | 50          | ns   |

| DREQ "H" assert time (16 bit) | DACK "H"    | <b>t</b> akrq2 | С         | _              | 2 tclk + 40 | ns   |

| IORD "L" assert time          | DACK "L"    | <b>t</b> akrd  | D         | 0              | _           | ns   |

| DMBHE, DMA0 set up time       | ĪORD "L"    | <b>t</b> suDA  | Е         | 20             | _           | ns   |

| DMBHE, DMA0 hold time         | IORD "H"    | <b>t</b> hDA   | F         | 20             | _           | ns   |

| IORD "L" level pulse width    | _           | twrdl          | G         | 40             | _           | ns   |

| DACK "Ll" pagets time         | IORD "L"    | trdak1         | Н         | <b>1 t</b> ськ | _           | ns   |

| DACK "H" negate time          | IORD "H"    | trdak2         | I         | 0              | _           | ns   |

| Data output defined time      | ĪORD "L"    | t√DMD          | J         | _              | 40          | ns   |

| Data output hold time         | IORD "H"    | <b>t</b> hDMD  | К         | 10             | _           | ns   |

<sup>\*:</sup> The position number indicates the position in the waveform.

#### • 68 series handshake mode

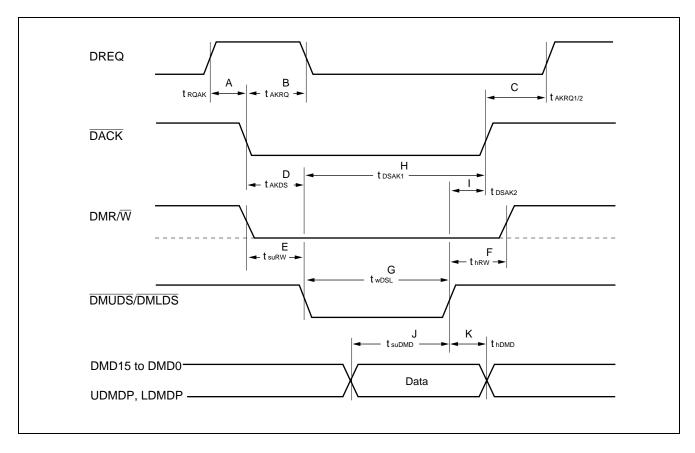

## (a) Write timing

| Parameter                         |                 | Cumbal         |           | Va             | lue         | l lmi4 |

|-----------------------------------|-----------------|----------------|-----------|----------------|-------------|--------|

| Parameter                         | Base signal     | Symbol         | Position* | Min.           | Max.        | Unit   |

| DACK "L" assert time              | DREQ "H"        | <b>t</b> rqak  | Α         | 0              | _           | ns     |

| DREQ "L" negate time              | DACK "L"        | <b>t</b> akrq  | В         | _              | 40          | ns     |

| DREQ "H" assert time (8 bit)      | DACK "H"        | takrq1         | С         | _              | 50          | ns     |

| DREQ "H" assert time (16 bit)     | DACK "H"        | <b>t</b> akrq2 | С         | _              | 2 tclk + 40 | ns     |

| DMUDS/DMLDS "L" assert time       | DACK "L"        | <b>t</b> AKDS  | D         | 0              | _           | ns     |

| DMR/W set up time                 | DMUDS/DMLDS "L" | <b>t</b> suRW  | Е         | 20             | _           | ns     |

| DMR/W hold time                   | DMUDS/DMLDS "H" | <b>t</b> hRW   | F         | 20             | _           | ns     |

| DMUDS/DMLDS "L" level pulse width | _               | twdsl          | G         | 40             | _           | ns     |

| DACK "H" negate time              | DMUDS/DMLDS "L" | tdsak1         | Н         | 1 <b>t</b> clk | _           | ns     |

| DACK in negate time               | DMUDS/DMLDS "H" | tdsak2         | I         | 0              | _           | ns     |

| Input data set up time            | DMUDS/DMLDS "H" | <b>t</b> suDMD | J         | 30             | _           | ns     |

| Input data hold time              | DMUDS/DMLDS "H" | <b>t</b> hDMD  | К         | 5              | _           | ns     |

<sup>\*:</sup> The position number indicates the position in the waveform.

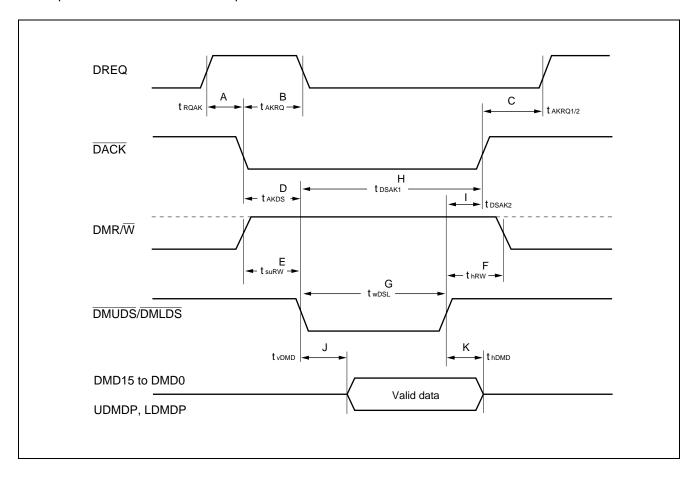

## (b) Read timing

| Parameter                         |                 | Symbol             |           | Va             | lue         | l lmi4 |

|-----------------------------------|-----------------|--------------------|-----------|----------------|-------------|--------|

| Parameter                         | Base signal     | Symbol             | Position* | Min.           | Max.        | Unit   |

| DACK "L" assert time              | DREQ "H"        | <b>t</b> rqak      | А         | 0              | _           | ns     |

| DREQ "L" negate time              | DACK "L"        | <b>t</b> akrq      | В         | _              | 40          | ns     |

| DREQ "H" assert time (8 bit)      | DACK "H"        | <b>t</b> AKRQ1     | С         | _              | 50          | ns     |

| DREQ "H" assert time (16 bit)     | DACK "H"        | <b>t</b> akrq2     | С         | _              | 2 tclk + 40 | ns     |

| DMUDS/DMLDS "L" assert time       | DACK "L"        | <b>t</b> AKDS      | D         | 0              | _           | ns     |

| DMR/W set up time                 | DMUDS/DMLDS "L" | <b>t</b> suRW      | Е         | 20             | _           | ns     |

| DMR/W hold time                   | DMUDS/DMLDS "H" | thRW               | F         | 20             | _           | ns     |

| DMUDS/DMLDS "L" level pulse width | _               | twDSL              | G         | 40             | _           | ns     |

| DACK "Ll" nageta tima             | DMUDS/DMLDS "L" | <b>t</b> DSAK1     | Н         | 1 <b>t</b> clк | _           | ns     |

| DACK "H" negate time              | DMUDS/DMLDS "H" | t <sub>DSAK2</sub> | I         | 0              | _           | ns     |

| Data output defined time          | DMUDS/DMLDS "L" | t√DMD              | J         | _              | 40          | ns     |

| Data output hold time             | DMUDS/DMLDS "H" | <b>t</b> hDMD      | К         | 10             | _           | ns     |

<sup>\*:</sup> The position number indicates the position in the waveform.

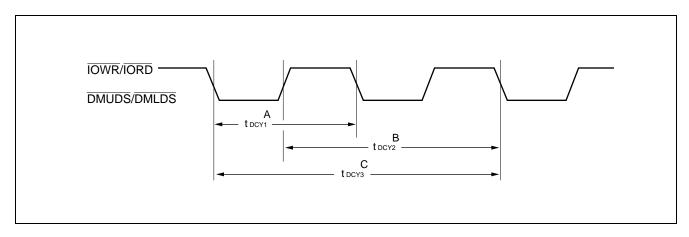

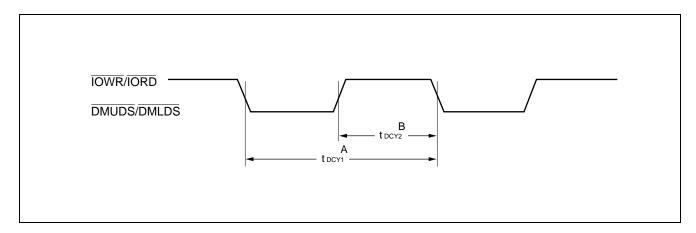

### • Burst mode (80 series/68 series common)

## (a) Data register access cycle time (8 bit)

| Parameter E                       |             | Symbol            |           | Value          |      | Unit |

|-----------------------------------|-------------|-------------------|-----------|----------------|------|------|

|                                   | Base signal | Symbol            | Position* | Min.           | Max. | Oill |

| Data register access cycle time 1 | _           | tDCY1             | Α         | <b>t</b> clk   | _    | ns   |

| Data register access cycle time 2 | _           | tDCY2             | В         | 3 tclk         | _    | ns   |

| Data register access cycle time 3 | _           | t <sub>DCY3</sub> | С         | <b>4 t</b> ськ | _    | ns   |

<sup>\*:</sup> The position number indicates the position in the waveform.

## (b) Data register access cycle time (16 bit)

| Parameter                         |             | Symbol |           | Value          |      | Unit  |

|-----------------------------------|-------------|--------|-----------|----------------|------|-------|

| Farameter                         | Base signal | Symbol | Position* | Min.           | Max. | Oilit |

| Data register access cycle time 1 | _           | tDCY1  | Α         | <b>4 t</b> ськ | _    | ns    |

| Data register access cycle time 2 | _           | tDCY2  | В         | 3 tськ         | _    | ns    |

<sup>\*:</sup> The position number indicates the position in the waveform.

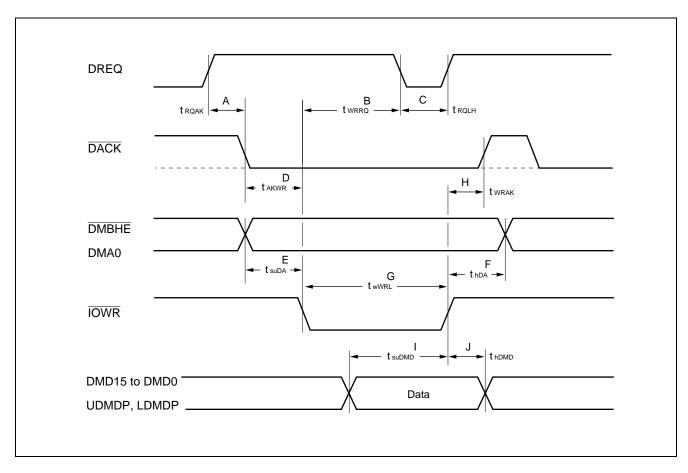

#### • 80 series burst mode

## (a) Write timing

| Parameter                       |             | Symbol         |           | Value |      | Unit |

|---------------------------------|-------------|----------------|-----------|-------|------|------|

| Farameter                       | Base signal | Symbol         | Position* | Min.  | Max. | Unit |

| DACK "L" assert time            | DREQ "H"    | <b>t</b> rqak  | Α         | 0     | _    | ns   |

| DREQ "L" negate time            | ĪOWR "L"    | twrrq          | В         | _     | 55   | ns   |

| DREQ "L" → DREQ "H" return time | _           | <b>t</b> RQLH  | С         | 0     | _    | ns   |

| IOWR "L" assert time            | DACK "L"    | <b>t</b> akwr  | D         | 0     | _    | ns   |

| DMBHE, DMA0 set up time         | ĪOWR "L"    | <b>t</b> suDA  | E         | 20    | _    | ns   |

| DMBHE, DMA0 hold time           | IOWR "H"    | <b>t</b> hDA   | F         | 20    | _    | ns   |

| IOWR "L" level pulse width      | _           | twwrl          | G         | 40    | _    | ns   |

| DACK "H" negate time            | ĪOWR "H"    | twrak          | Н         | 0     | _    | ns   |

| Input data set up time          | ĪOWR "H"    | <b>t</b> suDMD | I         | 30    | _    | ns   |

| Input data hold time            | ĪOWR "H"    | <b>t</b> hDMD  | J         | 5     | _    | ns   |

<sup>\*:</sup> The position number indicates the position in the waveform.

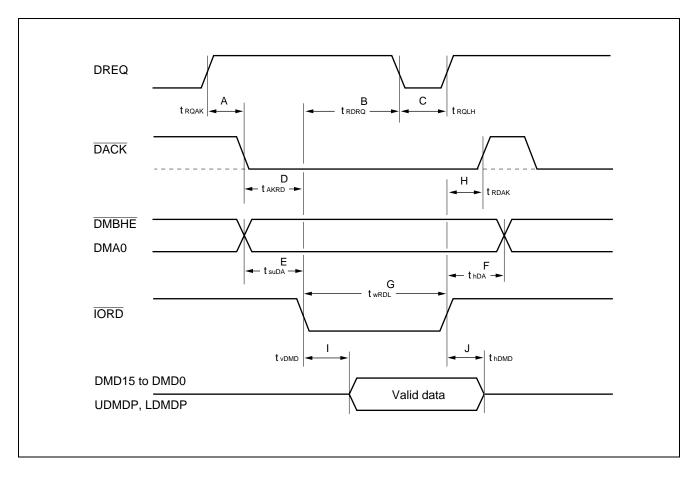

## (b) Read timing

| Parameter                       |             | Symbol        |           | Va   | lue  | Unit |

|---------------------------------|-------------|---------------|-----------|------|------|------|

| Farameter                       | Base signal | Cymbol        | Position* | Min. | Max. | Onit |

| DACK "L" assert time            | DREQ "H"    | <b>t</b> rqak | Α         | 0    | _    | ns   |

| DREQ "L" negate time            | IORD "L"    | <b>t</b> rdrq | В         | _    | 55   | ns   |

| DREQ "L" → DREQ "H" return time | _           | <b>t</b> RQLH | С         | 0    | _    | ns   |

| IORD "L" assert time            | DACK "L"    | <b>t</b> akrd | D         | 0    | _    | ns   |

| DMBHE, DMA0 set up time         | IORD "L"    | <b>t</b> suDA | E         | 20   | _    | ns   |

| DMBHE, DMA0 hold time           | IORD "H"    | <b>t</b> hDA  | F         | 20   | _    | ns   |

| IORD "L" level pulse width      | _           | twRDL         | G         | 40   | _    | ns   |

| DACK "H" negate time            | IORD "H"    | <b>t</b> rdak | Н         | 0    | _    | ns   |

| Data output defined time        | ĪORD "L"    | t√DMD         | I         | _    | 40   | ns   |

| Data output hold time           | IORD "H"    | <b>t</b> hDMD | J         | 10   | _    | ns   |

<sup>\*:</sup> The position number indicates the position in the waveform.

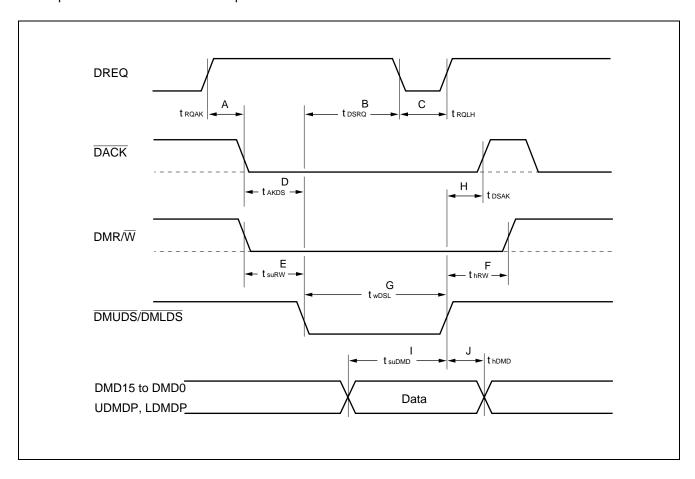

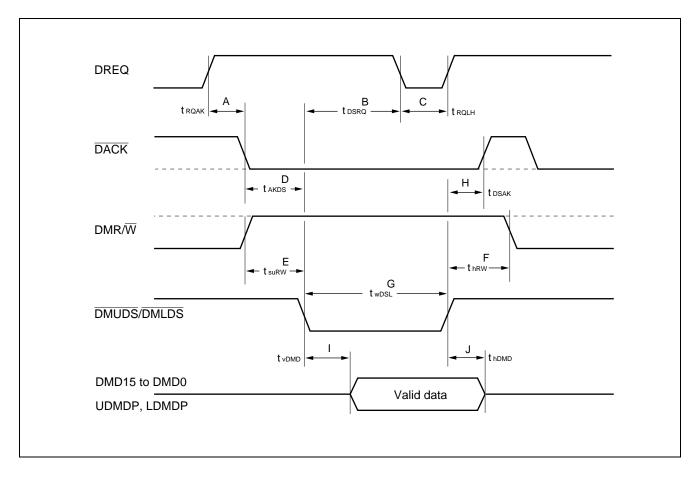

#### • 68 series burst mode

## (a) Write timing

| Doromotor                         |                 | Symbol         |           | Va   | lue  | Unit |  |

|-----------------------------------|-----------------|----------------|-----------|------|------|------|--|

| Parameter                         | Base signal     | Symbol         | Position* | Min. | Max. | Jill |  |

| DACK "L" assert time              | DREQ "H"        | <b>t</b> rqak  | Α         | 0    | _    | ns   |  |

| DREQ "L" negate time              | DMUDS/DMLDS "L" | <b>t</b> DSRQ  | В         | _    | 55   | ns   |  |

| DREQ "L" → DREQ "H" return time   | _               | <b>t</b> RQLH  | С         | 0    | _    | ns   |  |

| DMUDS/DMLDS "L" assert time       | DACK "L"        | <b>t</b> AKDS  | D         | 0    | _    | ns   |  |

| DMR/W set up time                 | DMUDS/DMLDS "L" | <b>t</b> suRW  | Е         | 20   | _    | ns   |  |

| DMR/W hold time                   | DMUDS/DMLDS "H" | <b>t</b> hRW   | F         | 20   | _    | ns   |  |

| DMUDS/DMLDS "L" level pulse width | _               | twDSL          | G         | 40   | _    | ns   |  |

| DACK "H" negate time              | DMUDS/DMLDS "H" | <b>t</b> dsak  | Н         | 0    | _    | ns   |  |

| Input data set up time            | DMUDS/DMLDS "H" | <b>t</b> suDMD | I         | 30   | _    | ns   |  |

| Input data hold time              | DMUDS/DMLDS "H" | <b>t</b> hDMD  | J         | 5    | _    | ns   |  |

<sup>\*:</sup> The position number indicates the position in the waveform.

## (b) Read timing

| Dorometer                         |                 | Symbol        |           | Va   | lue  | l lmi4 |

|-----------------------------------|-----------------|---------------|-----------|------|------|--------|

| Parameter                         | Base signal     | Symbol        | Position* | Min. | Max. | Unit   |

| DACK "L" assert time              | DREQ "H"        | <b>t</b> rqak | Α         | 0    | _    | ns     |

| DREQ "L" negate time              | DMUDS/DMLDS "L" | <b>t</b> DSRQ | В         | _    | 55   | ns     |

| DREQ "L" → DREQ "H" return time   | _               | <b>t</b> RQLH | С         | 0    | _    | ns     |

| DMUDS/DMLDS "L" assert time       | DACK "L"        | <b>t</b> AKDS | D         | 0    | _    | ns     |

| DMR/W set up time                 | DMUDS/DMLDS "L" | <b>t</b> suRW | Е         | 20   | _    | ns     |

| DMR/W hold time                   | DMUDS/DMLDS "H" | <b>t</b> hRW  | F         | 20   | _    | ns     |

| DMUDS/DMLDS "L" level pulse width | _               | twdsl         | G         | 40   | _    | ns     |

| DACK "H" negate time              | DMUDS/DMLDS "H" | <b>t</b> dsak | Н         | 0    | _    | ns     |

| Data output defined time          | DMUDS/DMLDS "L" | t√DMD         | I         | _    | 40   | ns     |

| Data output hold time             | DMUDS/DMLDS "H" | <b>t</b> hDMD | J         | 10   | _    | ns     |

<sup>\*:</sup> The position number indicates the position in the waveform.

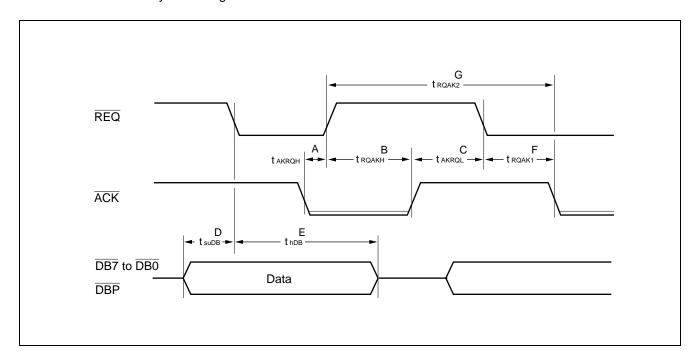

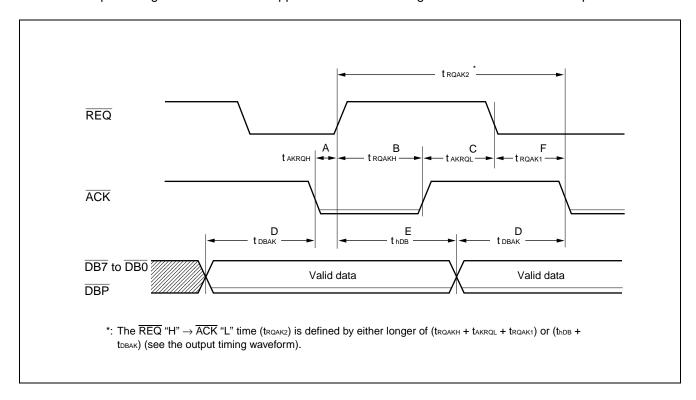

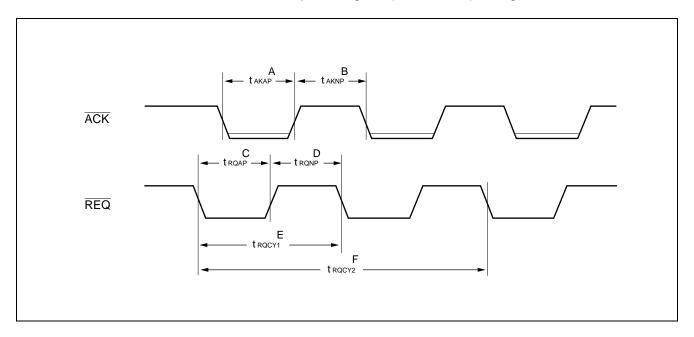

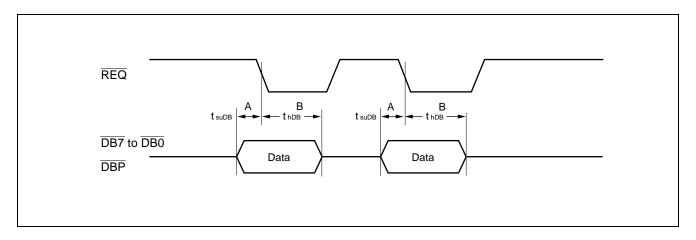

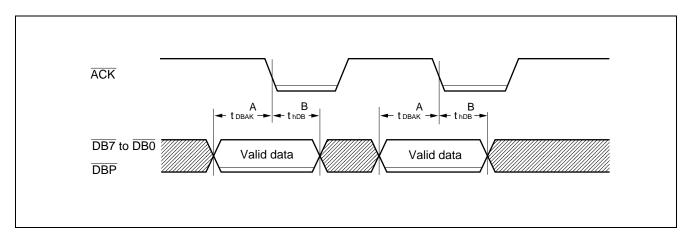

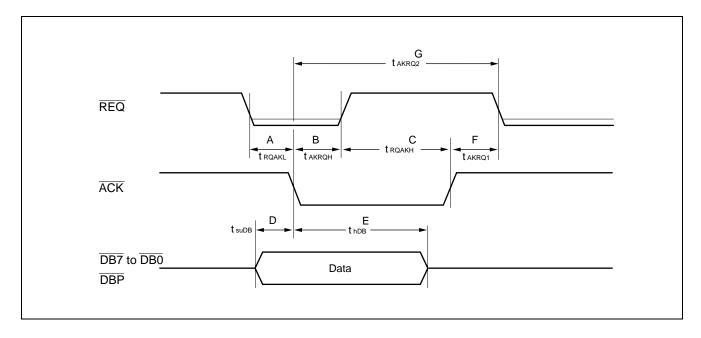

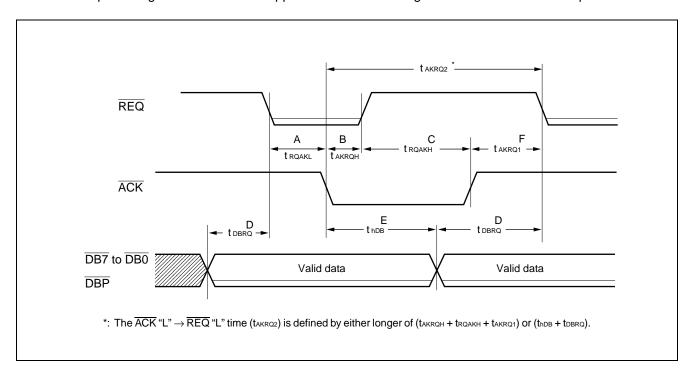

- (6) SCSI interface (as initiator)

- · Asynchronous transfer mode

- (a) Input timing (target  $\rightarrow$  initiator)

| Parameter                |             | Symbol         | Symbol     |      | Value       |      |

|--------------------------|-------------|----------------|------------|------|-------------|------|

| Farameter                | Base signal | Symbol         | Position*1 | Min. | Max.        | Unit |

| REQ "H" negate time      | ACK "L"     | <b>t</b> akrqh | А          | 0    | _           | ns   |