## 82434LX/82434NX PCI, CACHE AND MEMORY CONTROLLER (PCMC)

- Supports the Pentium<sup>™</sup> Processor at iCOMP<sup>™</sup> Index 510\60 MHz and iCOMP Index 567\66 MHz

- Supports the Pentium Processor at iCOMP Index 735\90 MHz, iCOMP Index 815\100 MHz, and iCOMP Index 610\75 MHz

- Supports Pipelined Addressing Capability of the Pentium Processor

- The 82430NX Drives 3.3V Signal Levels on the CPU and Cache Interfaces

- High Performance CPU/PCI/Memory Interfaces via Posted Write and Read Prefetch Buffers

- Fully Synchronous PCI Interface with Full Bus Master Capability

- Supports the Pentium Processor Internal Cache in Either Write-Through or Write-Back Mode

- Programmable Attribute Map of DOS and BIOS Regions for System Flexibility

- Integrated Low Skew Clock Driver for Distributing Host Clock

- Integrated Second Level Cache Controller

- Integrated Cache Tag RAM

- Write-Through and Write-Back Cache Modes for the 82434LX

- Write-Back for the 82434NX

- 82434NX Supports Low-Power Cache Standby

- Direct Mapped Organization

- Supports Standard and Burst SRAMs

- 256-KByte and 512-KByte Sizes

- Cache Hit Cycle of 3-1-1-1 on Reads and Writes Using Burst SRAMs

- Cache Hit Cycle of 3-2-2-2 on Reads and 4-2-2-2 on Writes Using Standard SRAMs

- Integrated DRAM Controller

- Supports 2 MBytes to 192 MBytes of Cacheable Main Memory for the 82434LX

- Supports 2 MBytes to 512 MBytes of Cacheable Main Memory for the 82434NX

- Supports DRAM Access Times of 70 ns and 60 ns

- CPU Writes Posted to DRAM 4-1-1-1

- Refresh Cycles Decoupled from ISA Refresh to Reduce the DRAM Access Latency

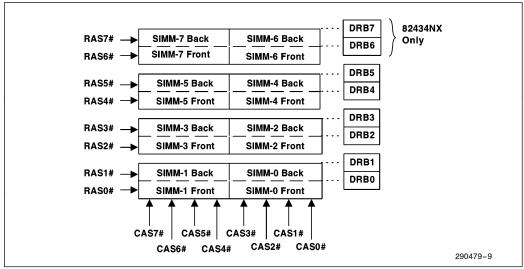

- Six RAS# Lines (82434LX)

- Eight RAS# Lines (82434NX)

- Refresh by RAS#-Only, or CAS-Before-RAS#, in Single or Burst of Four

- Host/PCI Bridge

- Translates CPU Cycles into PCI Bus Cycles

- Translates Back-to-Back Sequential CPU Memory Writes into PCI Burst Cycles

- Burst Mode Writes to PCI in Zero PCI Wait-States (i.e. Data Transfer Every Cycle)

- Full Concurrency Between CPU-to-Main Memory and PCI-to-PCI Transactions

- Full Concurrency Between CPU-to-Second Level Cache and PCI-to-Main Memory Transactions

- Same Cache and Memory System Logic Design for ISA and EISA Systems

- Cache Snoop Filter Ensures Data

Consistency for PCI-to-Main Memory

Transactions

- 208-Pin QFP Package

<sup>\*</sup>Other brands and names are the property of their respective owners.

#### 82434LX/82434NX

This document describes both the 82434LX and 82434NX. Unshaded areas describe the 82434LX. Shaded areas, like this one, describe 82434NX operations that differ from the 82434LX.

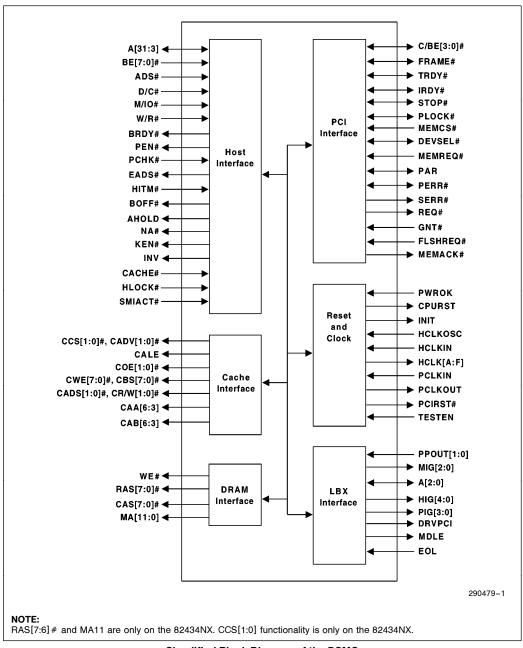

The 82434LX/82434NX PCI, Cache, Memory Controllers (PCMC) integrate the cache and main memory DRAM control functions and provide bus control for transfers between the CPU, cache, main memory, and the PCI Local Bus. The cache controller supports write-back (or write-through for 82434LX) cache policy and cache sizes of 256-KBytes and 512-KBytes. The cache memory can be implemented with either standard or burst SRAMs. The PCMC cache controller integrates a high-performance Tag RAM to reduce system cost.

Simplified Block Diagram of the PCMC

# 82434LX/82434NX PCI, CACHE AND MEMORY CONTROLLER (PCMC)

| CONTENTS                                      | PAGE |

|-----------------------------------------------|------|

| 1.0 ARCHITECTURAL OVERVIEW                    | 10   |

| 1.1 System Overview                           |      |

| 1.1.1 BUS HIERARCHY—CONCURRENT OPERATIONS     | 10   |

| 1.1.2 BUS BRIDGES                             | 13   |

| 1.2 PCMC Overview                             | 13   |

| 1.2.1 CACHE OPERATIONS                        | 14   |

| 1.2.1.1 Cache Consistency                     |      |

| 1.2.2 ADDRESS/DATA PATHS                      |      |

| 1.2.2.1 Read/Write Buffers                    |      |

| 1.2.3 HOST/PCI BRIDGE OPERATIONS              | 15   |

| 1.2.4 DRAM MEMORY OPERATIONS                  | 16   |

| 1.2.5 3.3V SIGNALS                            | 16   |

| 2.0 SIGNAL DESCRIPTIONS                       | 16   |

| 2.1 Host Interface                            | 17   |

| 2.2 DRAM Interface                            | 22   |

| 2.3 Cache Interface                           | 23   |

| 2.4 PCI Interface                             | 24   |

| 2.5 LBX Interface                             | 28   |

| 2.6 Reset And Clock                           | 28   |

| 3.0 REGISTER DESCRIPTION                      | 30   |

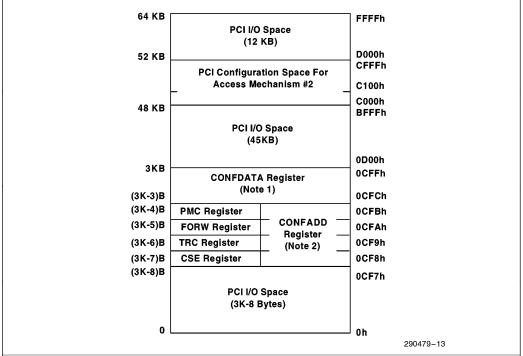

| 3.1 I/O Mapped Registers                      | 31   |

| 3.1.1 CONFADD—CONFIGURATION ADDRESS REGISTER  |      |

| 3.1.2 CSE—CONFIGURATION SPACE ENABLE REGISTER | 32   |

| 3.1.3 TRC—TURBO-RESET CONTROL REGISTER        | 33   |

| 3.1.4 FORW—FORWARD REGISTER                   | 34   |

| 3.1.5 PMC—PCI MECHANISM CONTROL REGISTER      |      |

| 3.1.6 CONFDATA—CONFIGURATION DATA REGISTER    |      |

| 3.2 PCI Configuration Space Mapped Registers  | 35   |

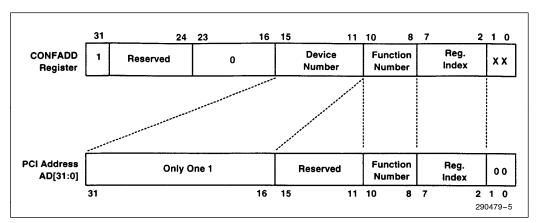

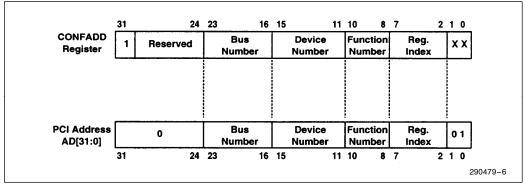

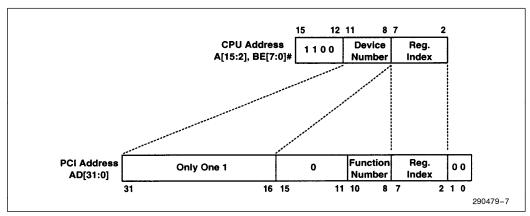

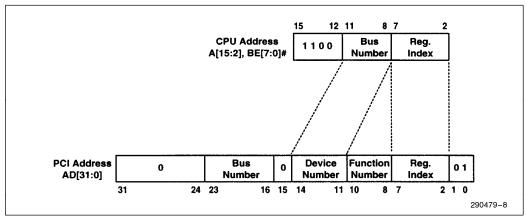

| 3.2.1 CONFIGURATION SPACE ACCESS MECHANISM    | 36   |

| 3.2.1.1 Access Mechanism #1:                  | 36   |

| 3.2.1.2 Access Mechanism #2                   | 37   |

| 3.2.2 VID—VENDOR IDENTIFICATION REGISTER      | 40   |

| 3.2.3 DID—DEVICE IDENTIFICATION REGISTER      | 40   |

| CONTENTS                                                   | PAGE |

|------------------------------------------------------------|------|

| 3.2.4 PCICMD—PCI COMMAND REGISTER                          | 41   |

| 3.2.5 PCISTS—PCI STATUS REGISTER                           | 42   |

| 3.2.6 RID—REVISION IDENTIFICATION REGISTER                 | 43   |

| 3.2.7 RLPI—REGISTER-LEVEL PROGRAMMING INTERFACE REGISTER . | 43   |

| 3.2.8 SUBC—SUB-CLASS CODE REGISTER                         | 43   |

| 3.2.9 BASEC—BASE CLASS CODE REGISTER                       |      |

| 3.2.10 MLT—MASTER LATENCY TIMER REGISTER                   | 44   |

| 3.2.11 BIST—BIST REGISTER                                  |      |

| 3.2.12 HCS—HOST CPU SELECTION REGISTER                     | 45   |

| 3.2.13 DFC—DETURBO FREQUENCY CONTROL REGISTER              | 46   |

| 3.2.14 SCC—SECONDARY CACHE CONTROL REGISTER                | 46   |

| 3.2.15 HBC—HOST READ/WRITE BUFFER CONTROL                  | 48   |

| 3.2.16 PBC—PCI READ/WRITE BUFFER CONTROL REGISTER          |      |

| 3.2.17 DRAMC—DRAM CONTROL REGISTER                         | 50   |

| 3.2.18 DRAMT—DRAM TIMING REGISTER                          | 51   |

| 3.2.19 PAM—PROGRAMMABLE ATTRIBUTE MAP REGISTERS (PAM[6:0]) | 51   |

| 3.2.20 DRB—DRAM ROW BOUNDARY REGISTERS                     |      |

| 3.2.20.1 82434LX Description                               |      |

| 3.2.20.2 82434NX Description                               | 56   |

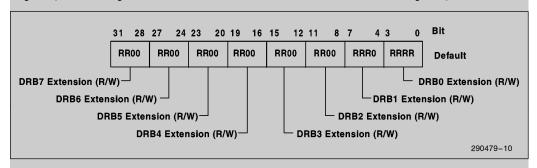

| 3.2.21 DRBE—DRAM ROW BOUNDARY EXTENSION REGISTER           | 58   |

| 3.2.22 ERRCMD—ERROR COMMAND REGISTER                       | 58   |

| 3.2.23 ERRSTS—ERROR STATUS REGISTER                        | 60   |

| 3.2.24 SMRS—SMRAM SPACE REGISTER                           |      |

| 3.2.25 MSG—MEMORY SPACE GAP REGISTER                       | 61   |

| 3.2.26 FBR—FRAME BUFFER RANGE REGISTER                     | 62   |

| 4.0 PCMC ADDRESS MAP                                       | 64   |

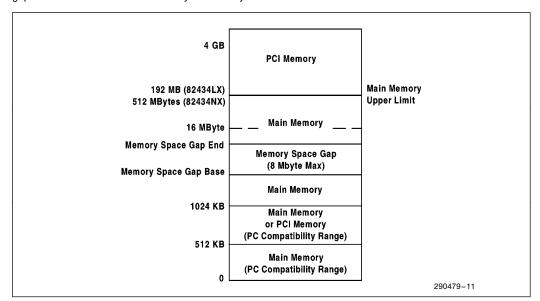

| 4.1 CPU Memory Address Map                                 | 64   |

| 4.2 System Management RAM—SMRAM                            | 64   |

| 4.3 PC Compatibility Range                                 | 65   |

| 4.4.I/O Address Man                                        | 66   |

| CONTENTS                                                      | PAGE |

|---------------------------------------------------------------|------|

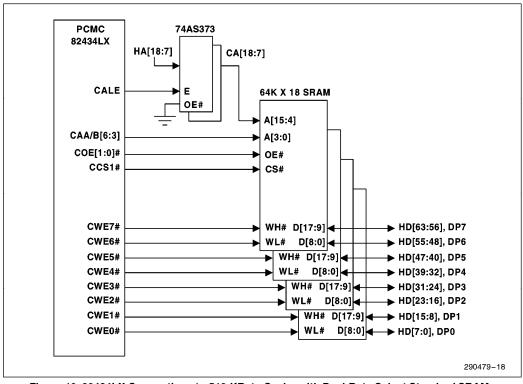

| 5.0 SECOND LEVEL CACHE INTERFACE                              | 67   |

| 5.1 82434LX Cache                                             | 67   |

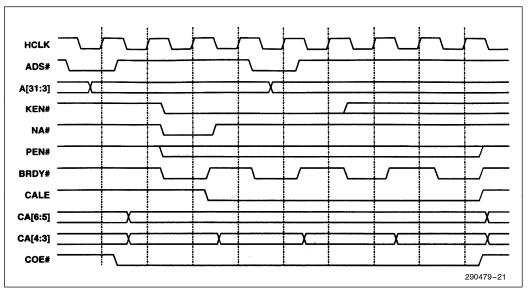

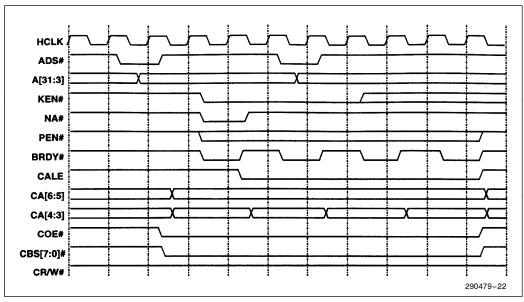

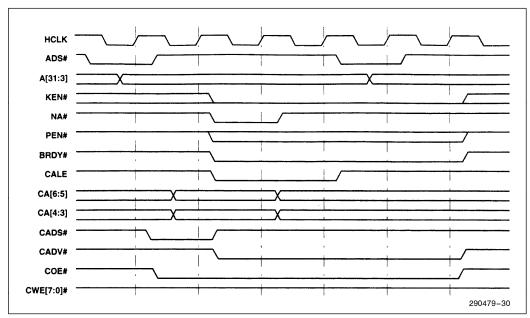

| 5.1.1 CLOCK LATENCIES (82434LX)                               | 75   |

| 5.1.2 STANDARD SRAM CACHE CYCLES (82434LX)                    | 76   |

| 5.1.2.1 Burst Read (82434LX)                                  | 76   |

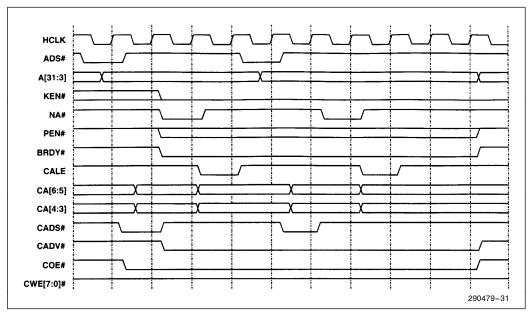

| 5.1.2.2 Burst Write (82434LX)                                 | 78   |

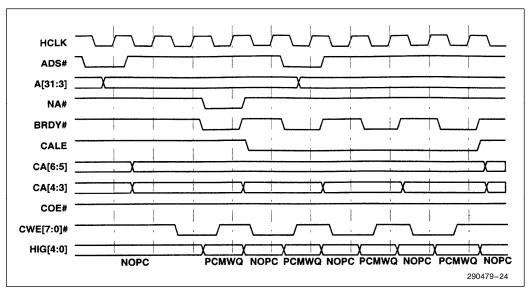

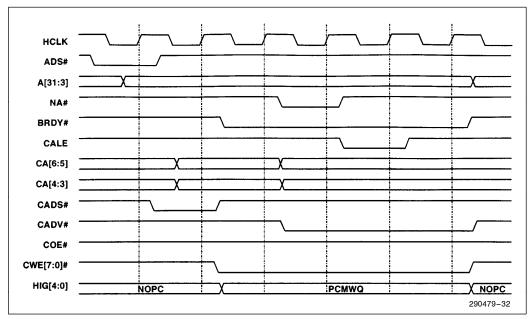

| 5.1.2.3 Cache Line Fill (82434LX)                             | 80   |

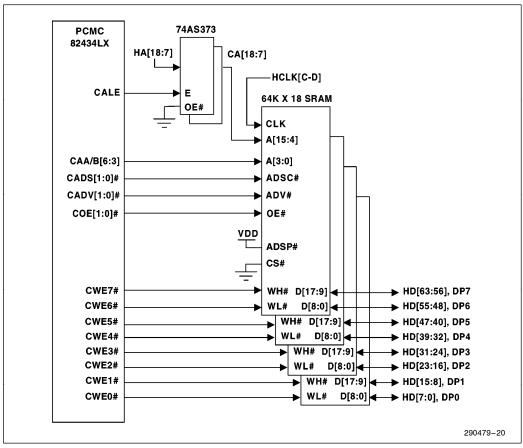

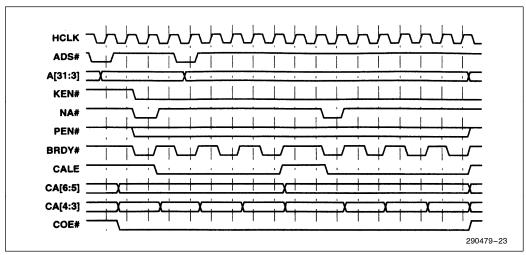

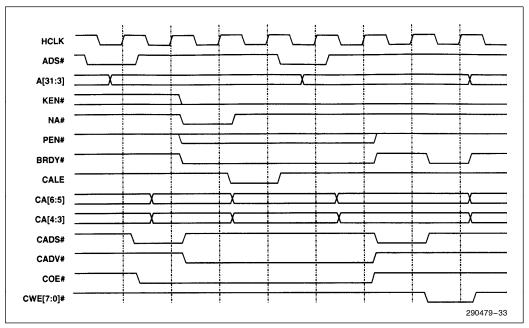

| 5.1.3 BURST SRAM CACHE CYCLES (82434LX)                       | 84   |

| 5.1.3.1 Burst Read (82434LX)                                  | 84   |

| 5.1.3.2 Burst Write (82434LX)                                 | 86   |

| 5.1.3.3 Cache Line Fill (82434LX)                             | 88   |

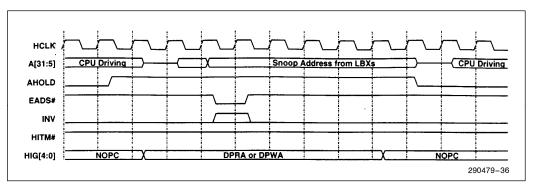

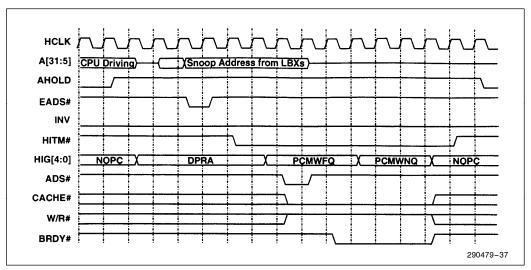

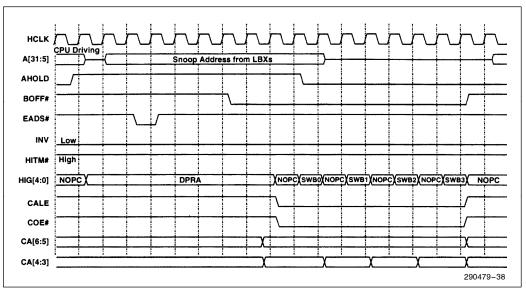

| 5.1.4 SNOOP CYCLES                                            |      |

| 5.1.5 FLUSH, FLUSH ACKNOWLEDGE AND WRITE-BACK SPECIAL CYCLES  | 98   |

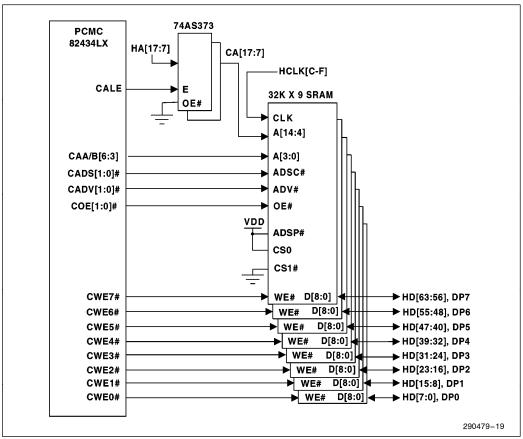

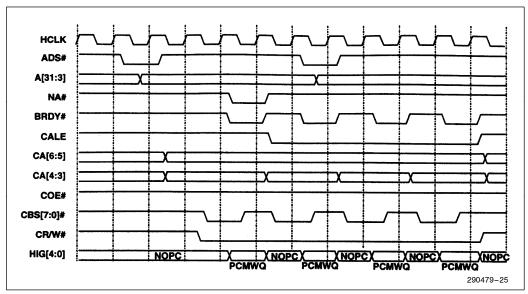

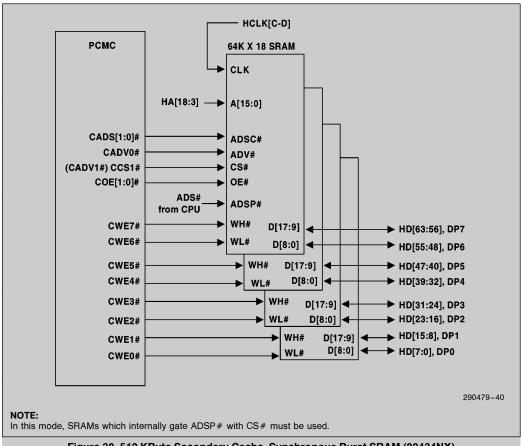

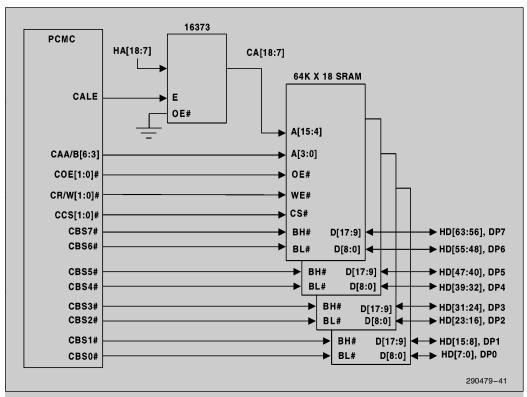

| 5.2 82434NX Cache                                             |      |

| 5.2.1 CYCLE LATENCY SUMMARY (82434NX)                         |      |

| 5.2.2 STANDARD SRAM CACHE CYCLES (82434NX)                    |      |

| 5.2.3 SECOND LEVEL CACHE STANDBY                              |      |

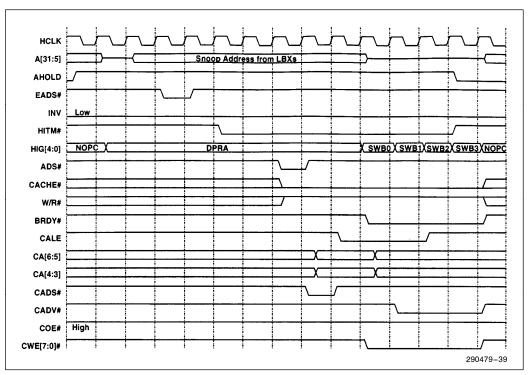

| 5.2.4 SNOOP CYCLES                                            |      |

| 5.2.5 FLUSH, FLUSH ACKNOWLEDGE, AND WRITE-BACK SPECIAL CYCLES | 103  |

| 6.0 DRAM INTERFACE                                            | 104  |

| 6.1 82434LX DRAM Interface                                    | 104  |

| 6.1.1 DRAM CONFIGURATIONS                                     |      |

| 6.1.2 DRAM ADDRESS TRANSLATION                                | 105  |

| 6.1.3 CYCLE TIMING SUMMARY                                    | 108  |

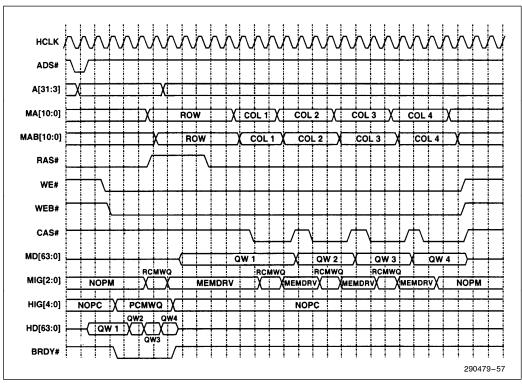

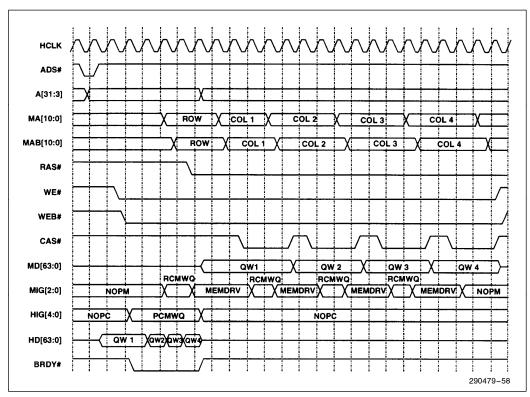

| 6.1.4 CPU TO DRAM BUS CYCLES                                  |      |

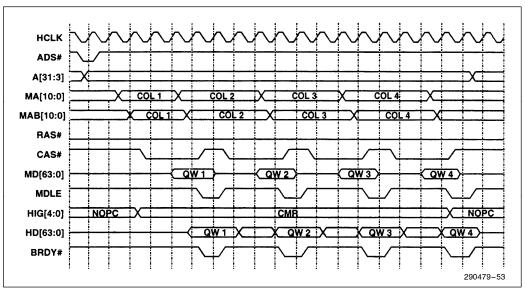

| 6.1.4.1 Read Page Hit                                         | 108  |

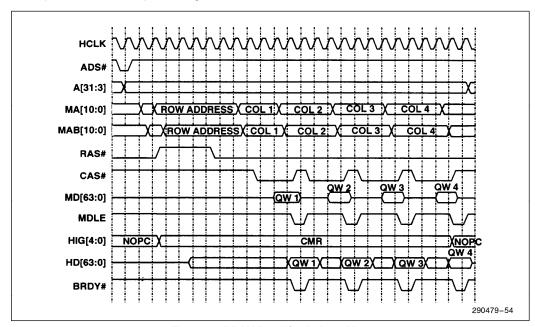

| 6.1.4.2 Read Page Miss                                        |      |

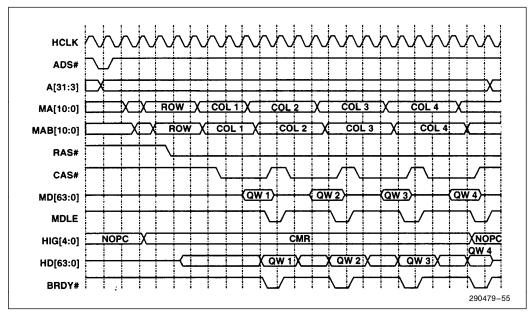

| 6.1.4.3 Read Row Miss                                         |      |

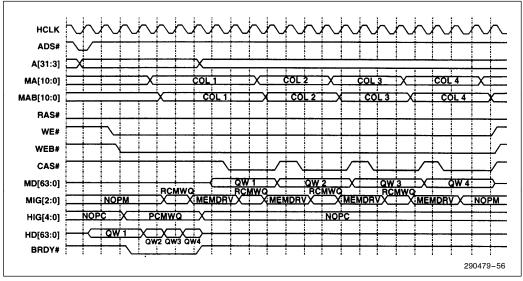

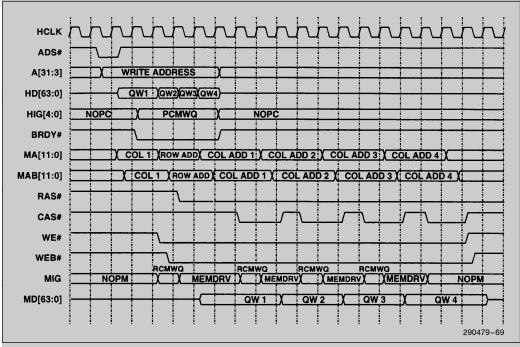

| 6.1.4.4 Write Page Hit                                        |      |

| 6.1.4.5 Write Page Miss                                       |      |

| 6.1.4.6 Write Row Miss                                        |      |

| 6.1.4.7 Read Cycle, 0-Active RAS# Mode                        |      |

| 6.1.4.8 Write Cycle, 0-Active RAS# Mode                       | 116  |

| CONTENTS                                              | PAGE |

|-------------------------------------------------------|------|

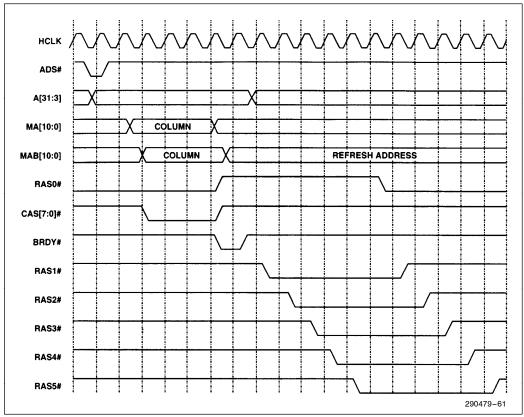

| 6.1.5 REFRESH                                         | 117  |

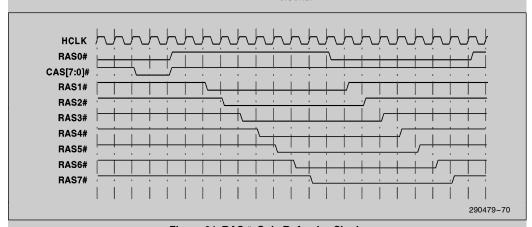

| 6.1.5.1 RAS#-Only Refresh-Single                      |      |

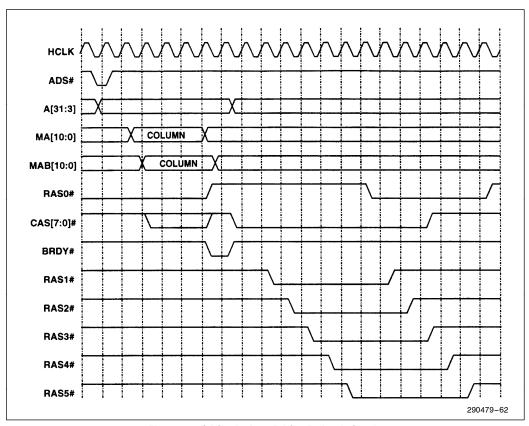

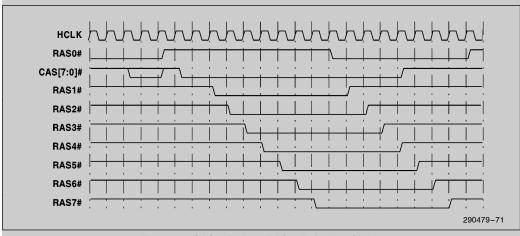

| 6.1.5.2 CAS#-Before-RAS# Refresh-Single               | 119  |

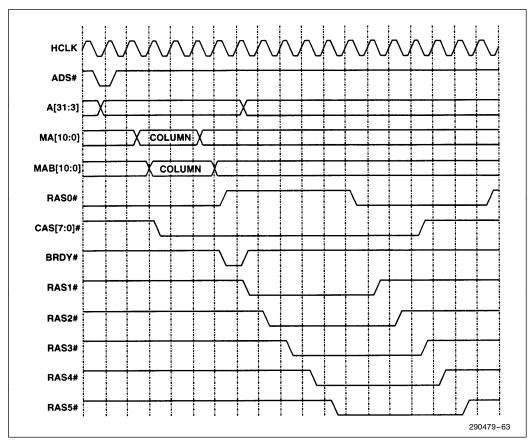

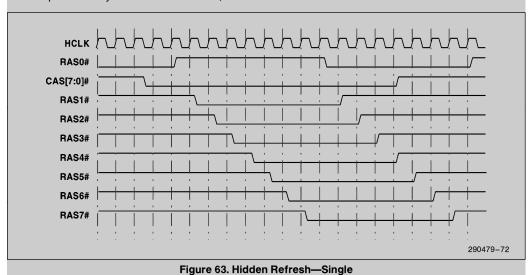

| 6.1.5.3 Hidden Refresh-Single                         | 120  |

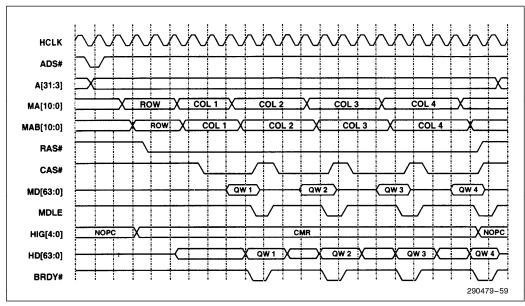

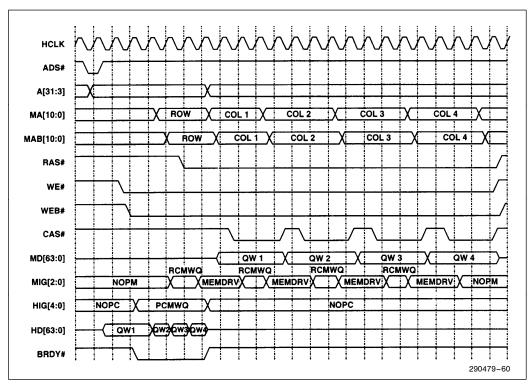

| 6.2 82434NX DRAM Interface                            | 121  |

| 6.2.1 DRAM ADDRESS TRANSLATION                        | 121  |

| 6.2.2 CYCLE TIMING SUMMARY                            | 122  |

| 6.2.3 CPU TO DRAM BUS CYCLES                          | 122  |

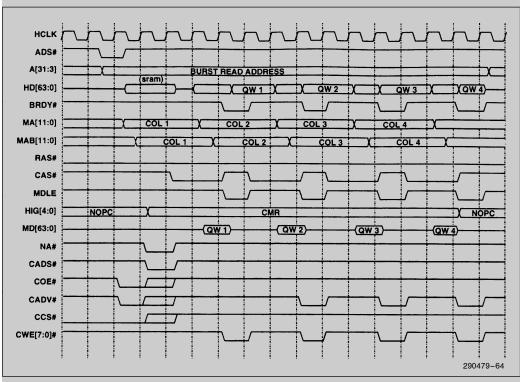

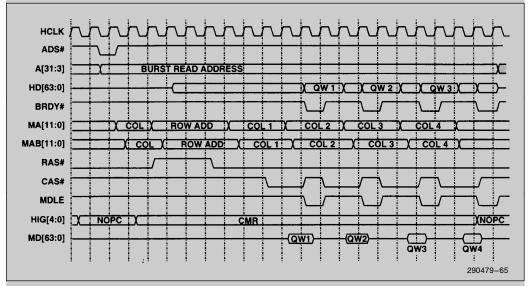

| 6.2.3.1 Burst DRAM Read Page Hit                      |      |

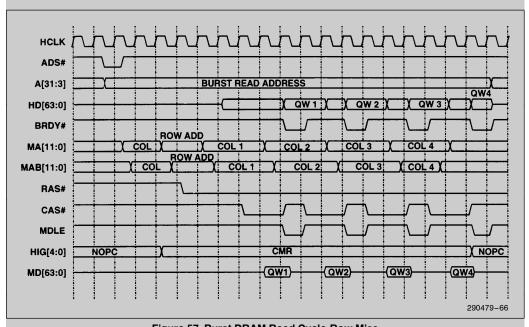

| 6.2.3.2 Burst DRAM Read Page Miss                     | 124  |

| 6.2.3.3 Burst DRAM Read Row Miss                      |      |

| 6.2.3.4 Burst DRAM Write Page Hit                     | 126  |

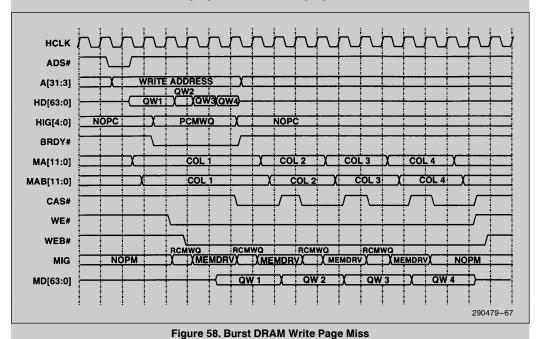

| 6.2.3.5 Burst DRAM Write Page Miss                    |      |

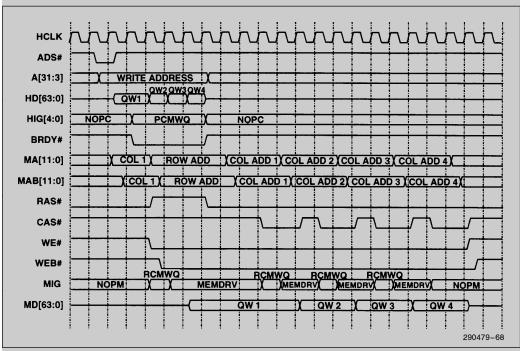

| 6.2.3.6 Burst DRAM Write Row Miss                     | 128  |

| 6.2.4 REFRESH                                         | 129  |

| 6.2.4.1 RAS#-Only Refresh—Single                      | 129  |

| 6.2.4.2 CAS#-before-RAS# Refresh—Single               |      |

| 6.2.4.3 Hidden Refresh-Single                         | 131  |

| 7.0 PCI INTERFACE                                     | 132  |

| 7.1 PCI Interface Overview                            |      |

| 7.2 CPU-to-PCI Cycles                                 |      |

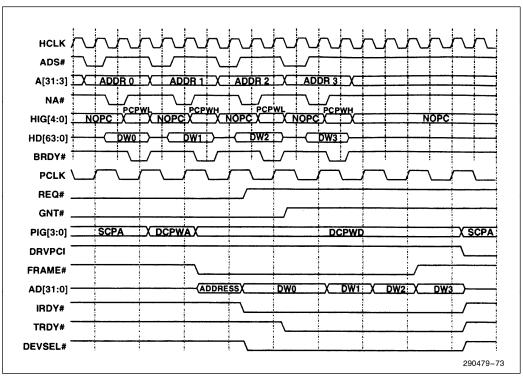

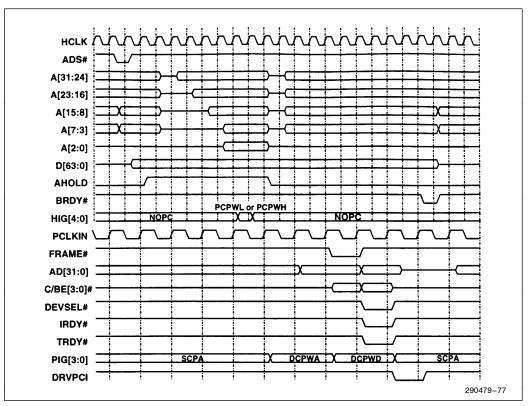

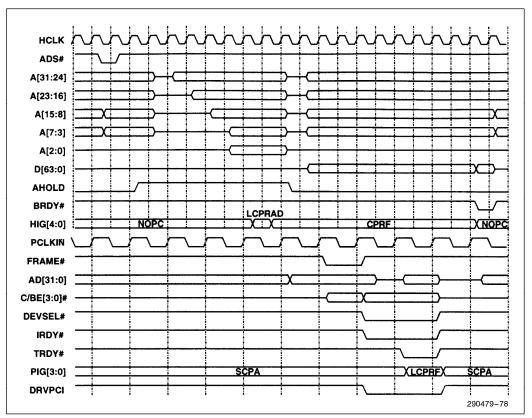

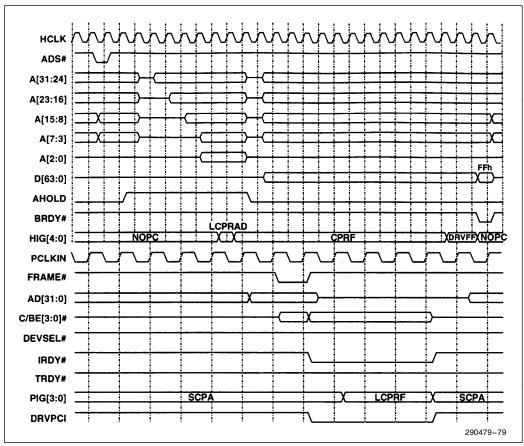

| 7.2.1 CPU WRITE TO PCI                                | 132  |

| 7.3 Register Access Cycles                            |      |

| 7.3.1 CPU WRITE CYCLE TO PCMC INTERNAL REGISTER       |      |

| 7.3.2 CPU READ FROM PCMC INTERNAL REGISTER            |      |

| 7.3.3 CPU WRITE TO PCI DEVICE CONFIGURATION REGISTER  |      |

| 7.3.4 CPU READ FROM PCI DEVICE CONFIGURATION REGISTER |      |

| 7.4 PCI-to-Main Memory Cycles                         | 141  |

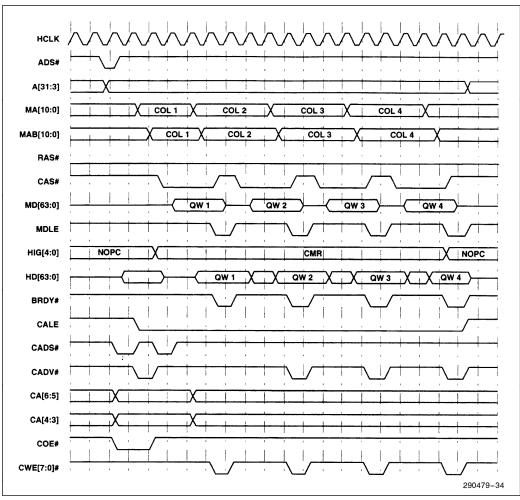

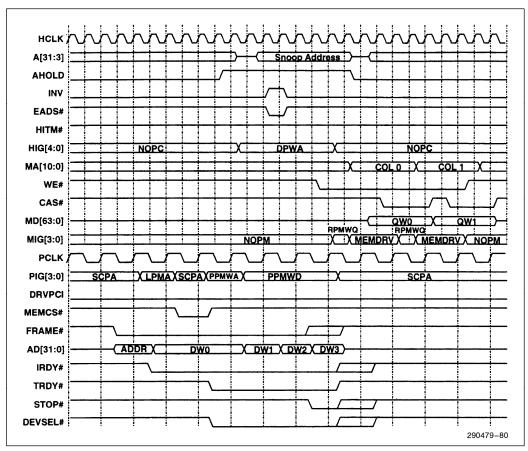

| 7.4.1 PCI MASTER WRITE TO MAIN MEMORY                 | 141  |

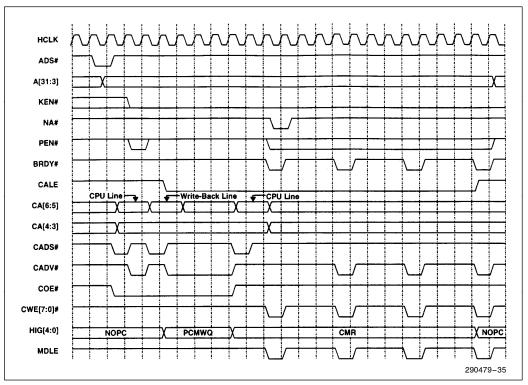

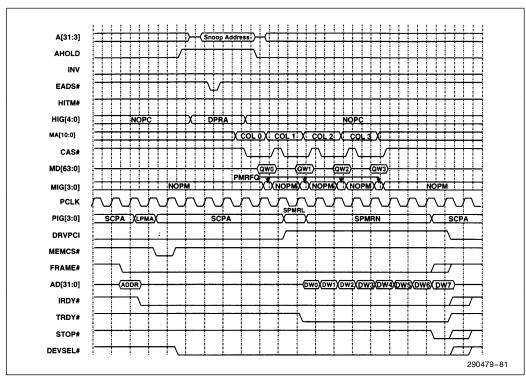

| 7.4.2 PCLMASTER READ FROM MAIN MEMORY                 | 143  |

| CONTENTS                                                          | PAGE |

|-------------------------------------------------------------------|------|

| 8.0 SYSTEM CLOCKING AND RESET                                     | 144  |

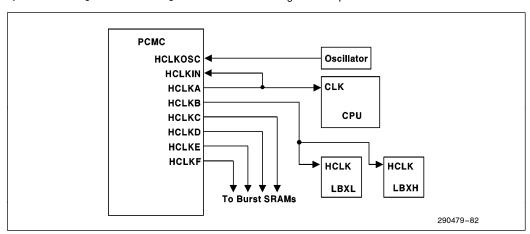

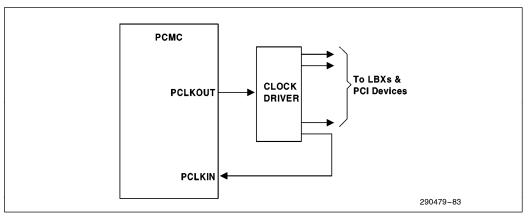

| 8.1 Clock Domains                                                 | 144  |

| 8.2 Clock Generation and Distribution                             | 144  |

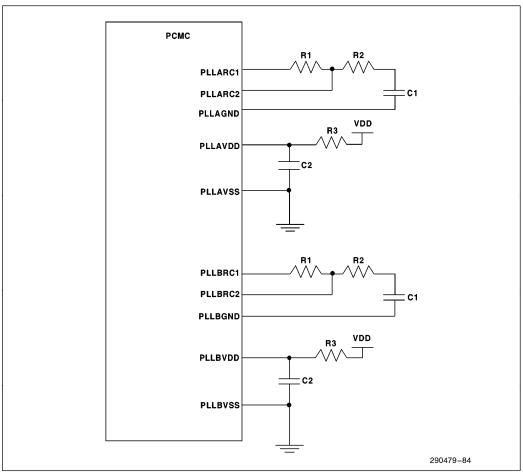

| 8.3 Phase Locked Loop Circuitry                                   | 145  |

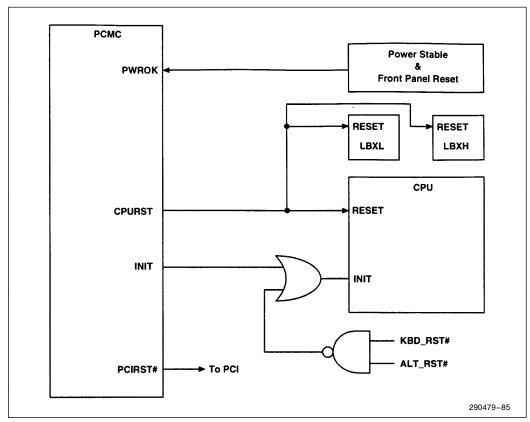

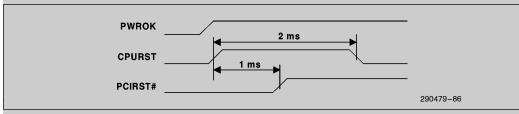

| 8.4 System Reset                                                  | 147  |

| 8.5 82434NX Reset Sequencing                                      | 149  |

| 9.0 ELECTRICAL CHARACTERISTICS                                    | 150  |

| 9.1 Absolute Maximum Ratings                                      | 150  |

| 9.2 Thermal Characteristics                                       | 150  |

| 9.3 82434LX DC Characteristics                                    | 150  |

| 9.4 82434NX DC Characteristics                                    | 152  |

| 9.5 82434LX AC Characteristics                                    | 154  |

| 9.5.1 HOST CLOCK TIMING, 66 MHz (82434LX)                         | 154  |

| 9.5.2 CPU INTERFACE TIMING, 66 MHz (82434LX)                      | 155  |

| 9.5.3 SECOND LEVEL CACHE STANDARD SRAM TIMING, 66 MHz (82434LX) . | 157  |

| 9.5.4 SECOND LEVEL CACHE BURST SRAM TIMING, 66 MHz (82434LX)      | 158  |

| 9.5.5 DRAM INTERFACE TIMING, 66 MHz (82434LX)                     |      |

| 9.5.6 PCI CLOCK TIMING, 66 MHz (82434LX)                          | 158  |

| 9.5.7 PCI INTERFACE TIMING, 66 MHz (82434LX)                      | 159  |

| 9.5.8 LBX INTERFACE TIMING, 66 MHz (82434LX)                      | 160  |

| 9.5.9 HOST CLOCK TIMING, 60 MHz (82434LX)                         | 160  |

| 9.5.10 CPU INTERFACE TIMING, 60 MHz (82434LX)                     | 161  |

| 9.5.11 SECOND LEVEL CACHE STANDARD SRAM TIMING, 60 MHz (82434LX)  | 163  |

| 9.5.12 SECOND LEVEL CACHE BURST SRAM TIMING, 60 MHz (82434LX)     | 164  |

| 9.5.13 DRAM INTERFACE TIMING, 60 MHz (82434LX)                    | 164  |

| 9.5.14 PCI CLOCK TIMING, 60 MHz (82434LX)                         | 165  |

| 9.5.15 PCI INTERFACE TIMING, 60 MHz (82434LX)                     | 165  |

| 9.5.16.LBX INTERFACE TIMING, 60 MHz (82434LX)                     | 166  |

| CONTENTS                                                                     | PAGE |

|------------------------------------------------------------------------------|------|

| 9.6 82434NX AC Characteristics                                               | 167  |

| 9.6.1 HOST CLOCK TIMING, 66 MHz (82434NX), PRELIMINARY                       | 167  |

| 9.6.2 CPU INTERFACE TIMING, 66 MHz (82434NX), PRELIMINARY                    | 168  |

| 9.6.3 SECOND LEVEL CACHE STANDARD SRAM TIMING, 66 MHz (82434NX), PRELIMINARY | 170  |

| 9.6.4 SECOND LEVEL CACHE BURST SRAM TIMING, 66 MHz (82434NX), PRELIMINARY    | 171  |

| 9.6.5 DRAM INTERFACE TIMING, 66 MHz (82434NX), PRELIMINARY                   | 171  |

| 9.6.6 PCI CLOCK TIMING, 66 MHz (82434NX), PRELIMINARY                        | 172  |

| 9.6.7 PCI INTERFACE TIMING, 66 MHz (82434NX), PRELIMINARY                    | 172  |

| 9.6.8 LBX INTERFACE TIMING, 66 MHz (82434NX), PRELIMINARY                    | 173  |

| 9.6.9 HOST CLOCK TIMING, 50 and 60 MHz (82434NX)                             | 173  |

| 9.6.10 CPU INTERFACE TIMING, 50 AND 60 MHz (82434NX)                         | 174  |

| 9.6.11 SECOND LEVEL CACHE STANDARD SRAM TIMING, 50 AND 60 MHz (82434NX)      | 176  |

| 9.6.12 SECOND LEVEL CACHE BURST SRAM TIMING, 50 AND 60 MHz (82434NX)         | 177  |

| 9.6.13 DRAM INTERFACE TIMING, 50 AND 60 MHz (82434NX)                        | 177  |

| 9.6.14 PCI CLOCK TIMING, 50 AND 60 MHz (82434NX)                             | 178  |

| 9.6.15 PCI INTERFACE TIMING, 50 AND 60 MHz (82434NX)                         | 178  |

| 9.6.16 LBX INTERFACE TIMING, 50 AND 60 MHz (82434NX)                         | 179  |

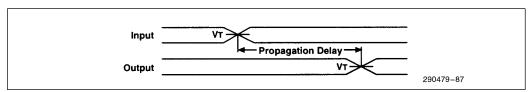

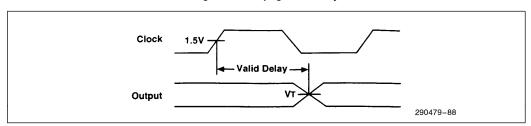

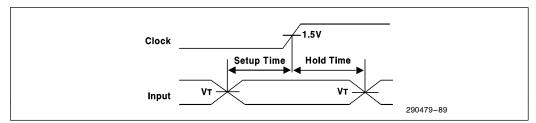

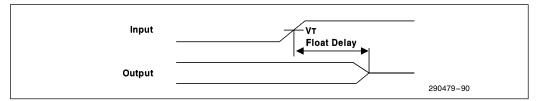

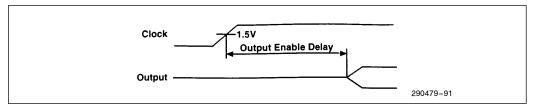

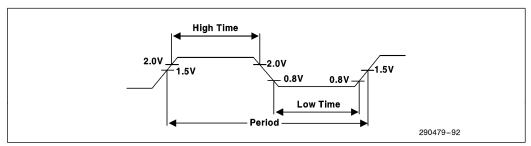

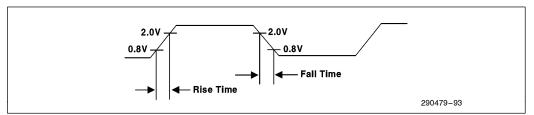

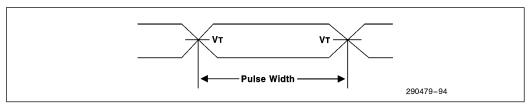

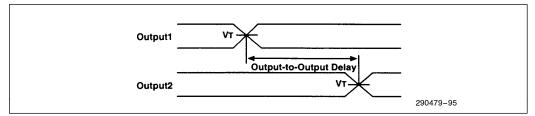

| 9.6.17 TIMING DIAGRAMS                                                       | 179  |

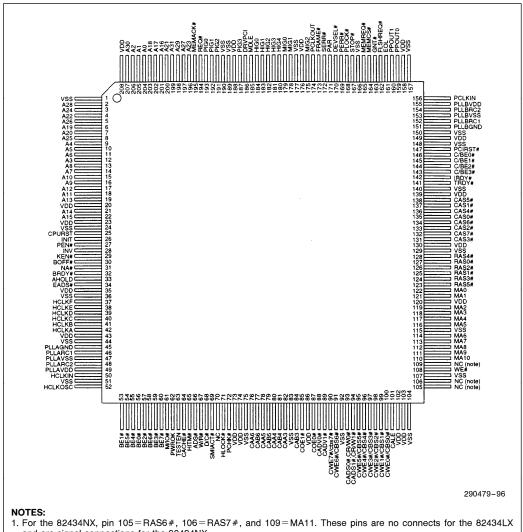

| 10.0 PINOUT AND PACKAGE INFORMATION                                          |      |

| 10.1 Pin Assignment                                                          |      |

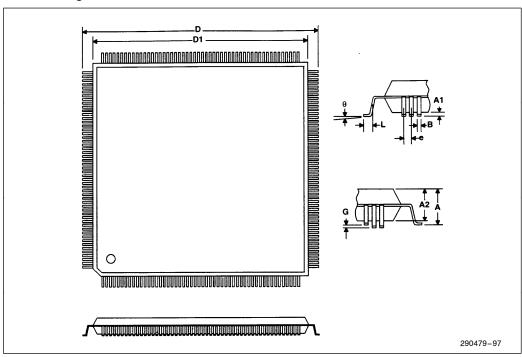

| 10.2 Package Characteristics                                                 | 189  |

| 11.0 TESTABILITY                                                             | 190  |

#### 1.0 ARCHITECTURAL OVERVIEW

This section provides an 82430LX/82430NX PCIset system overview that includes a description of the bus hierarchy and bridges between the buses. The 82430LX PCIset consists of the 82434LX PCMC and 82433LX LBX components plus either a PCI/ISA bridge or a PCI/EISA bridge. The 82430NX PCIset consists of the 82434NX PCMC and 82433NX LBX components plus either a PCI/ISA bridge or a PCI/EISA bridge. The PCMC and LBX provide the core cache and main memory architecture and serve as the Host/PCI bridge. An overview of the PCMC follows the system overview section.

#### 1.1 System Overview

The 82430LX/82430NX PCIset provides the Host/PCI bridge, cache and main memory controller, and an I/O subsystem core (either PCI/EISA or PCI/ISA bridge) for the next generation of high-performance personal computers based on the Pentium processor. System designers can take advantage of the power of the PCI (Peripheral Component Interconnect) local bus while maintaining access to the large base of EISA and ISA expansion cards. Extensive buffering and buffer management within the bridges ensures maximum efficiency in all three buses (Host CPU, PCI, and EISA/ISA Buses).

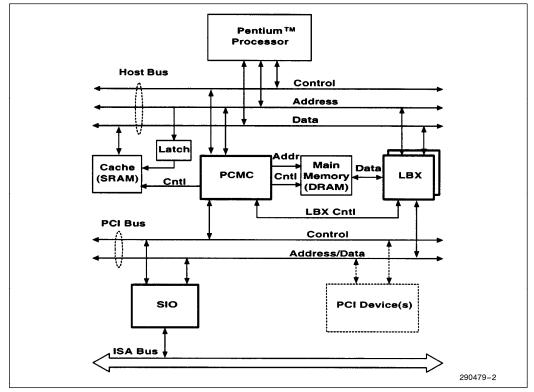

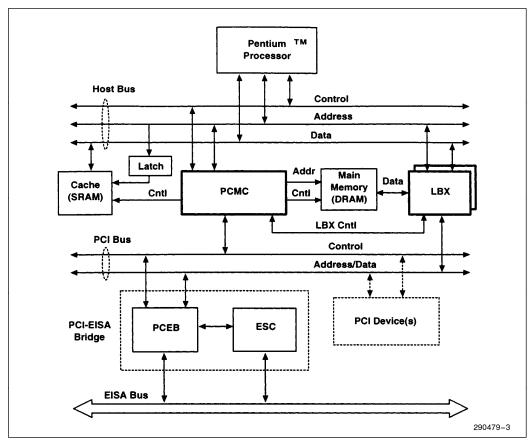

For an ISA-based system, the PCIset includes the System I/O (82378IB SIO) component (Figure 1) as the PCI/ISA bridge. For an EISA-based system (Figure 2), the PCIset includes the PCI-EISA bridge (82375EB PCEB) and the EISA System Component (82374EB ESC). The PCEB and ESC work in tandem to form the complete PCI/EISA bridge.

### 1.1.1. BUS HIERARCHY—CONCURRENT OPERATIONS

Systems based on the 82430LX/82430NX PCIset contain three levels of buses structured in the following hierarchy:

- · Host Bus as the execution bus

- PCI Bus as a primary I/O bus

- ISA or EISA Bus as a secondary I/O bus.

This bus hierarchy allows concurrency for simultaneous operations on all three buses. Data buffering permits concurrency for operations that crossover into another bus. For example, the Pentium processor could post data destined to the PCI in the LBX. This permits the Host transaction to complete in minimum time, freeing up the Host Bus for further transactions. The Pentium processor does not have to wait for the transfer to complete to its final destination. Meanwhile, any ongoing PCI Bus transactions are permitted to complete. The posted data is then transferred to the PCI Bus when the PCI Bus is available. The LBX implements extensive buffering for Host-to-PCI, Host-to-main memory, and PCI-tomain memory transactions. In addition, the PCEB/ ESC chip set and the SIO implement extensive buffering for transfers between the PCI Bus and the EISA and ISA Buses, respectively.

#### **Host Bus**

Designed to meet the needs of high-performance computing, the Host Bus features:

- 64-bit data path

- · 32-bit address bus with address pipelining

- Synchronous frequencies of 60 MHz and 66 MHz

- Synchronous frequency of 50 MHz (82430NX)

- Burst read and write transfers

- Support for first level and second level caches

- Capable of full concurrency with the PCI and memory subsystems

- Byte data parity

- Full support for Pentium processor machine check and DOS compatible parity reporting

- Support for Pentium processor System Management Mode (SMM).

Figure 1. Block Diagram of a 82430LX/82430NX PCIset ISA System

#### **PCI Bus**

The PCI Bus is designed to address the growing industry needs for a standardized *local bus* that is not directly dependent on the speed and the size of the processor bus. New generations of personal computer system software such as Windows<sup>™</sup> and Win-NT™ with sophisticated graphical interfaces, multi-tasking, and multi-threading bring new requirements that traditional PC I/O architectures cannot

satisfy. In addition to the higher bandwidth, reliability and robustness of the I/O subsystem are becoming increasingly important. PCI addresses these needs and provides a future upgrade path. PCI features include:

- Processor independent

- Multiplexed, burst mode operation

- Synchronous at frequencies up to 33 MHz

- 120 MByte/sec usable throughput (132 MByte/sec peak) for a 32-bit data path

- Low latency random access (60 ns write access latency to slave registers from a master parked on the bus)

- Capable of full concurrency with the processor/ memory subsystem

- Full multi-master capability allowing any PCI master peer-to-peer access to any PCI slave

- Hidden (overlapped) central arbitration

- Low pin count for cost effective component packaging (multiplexed address/data)

- Address and data parity

- Three physical address spaces: memory, I/O, and configuration

- Comprehensive support for autoconfiguration through a defined set of standard configuration functions.

Figure 2. Block Diagram of the 82430LX/82430NX PCIset EISA System

#### ISA Bus

Figure 1 represents a system using the ISA Bus as the second level I/O bus. It allows personal computer platforms built around the PCI as a primary I/O bus to leverage the large ISA product base. The ISA Bus has 24-bit addressing and a 16-bit data path.

#### **EISA Bus**

Figure 2 represents a system using the EISA Bus as the second level I/O bus. It allows personal computer platforms built around the PCI as a primary I/O bus to leverage the large EISA/ISA product base. Combinations of PCI and EISA buses, both of which can be used to provide expansion functions, will satisfy even the most demanding applications.

Along with compatibility for 16-bit and 8-bit ISA hardware and software, the EISA bus provides the following key features:

- 32-bit addressing and 32-bit data path

- 33 MByte/sec bus bandwidth

- Multiple bus master support through efficient arbitration

- Support for autoconfiguration.

#### 1.1.2 BUS BRIDGES

#### Host/PCI Bridge Chip Set (PCMC and LBX)

The PCMC and LBX enhance the system performance by allowing for concurrency between the Host CPU Bus and PCI Bus, giving each greater bus throughput and decreased bus latency. The LBX contains posted write buffers for Host-to-PCI, Host-to-main memory, and PCI-to-main memory transfers. The LBX also contains read prefetch buffers for Host reads of PCI, and PCI reads of main memory. There are two LBXs per system. The LBXs are controlled by commands from the PCMC. The PCMC/LBX Host/PCI bridge chip set is covered in more detail in Section 1.2, PCMC Overview.

#### PCI-EISA Bridge Chip Set (PCEB and ESC)

The PCEB provides the master/slave functions on both the PCI Bus and the EISA Bus. Functioning as a bridge between the PCI and EISA buses, the PCEB provides the address and data paths, bus controls, and bus protocol translation for PCI-to-EISA and EISA-to-PCI transfers. Extensive data buffering in both directions increase system perform-

ance by maximizing PCI and EISA Bus efficiency and allowing concurrency on the two buses. The PCEB's buffer management mechanism ensures data coherency. The PCEB integrates central bus control functions including a programmable bus arbiter for the PCI Bus and EISA data swap buffers for the EISA Bus. Integrated system functions include PCI parity generation, system error reporting, and programmable PCI and EISA memory and I/O address space mapping and decoding. The PCEB also contains a BIOS Timer that can be used to implement timing loops. The PCEB is intended to be used with the ESC to provide an EISA I/O subsystem interface.

The ESC integrates the common I/O functions found in today's EISA-based PCs. The ESC incorporates the logic for EISA Bus controller, enhanced seven channel DMA controller with scatter-gather support, EISA arbitration, 14 level interrupt controller, Advanced Programmable Interrupt Controller (APIC), five programmable timer/counters, non-maskable-interrupt (NMI) control, and power management. The ESC also integrates support logic to decode peripheral devices (e.g., the flash BIOS, real time clock, keyboard/mouse controller, floppy controller, two serial ports, one parallel port, and IDE hard disk drive).

#### PCI/ISA Bridge (SIO):

The SIO component provides the bridge between the PCI Bus and the ISA Bus. The SIO also integrates many of the common I/O functions found in today's ISA-based PCs. The SIO incorporates the logic for a PCI interface (master and slave), ISA interface (master and slave), enhanced seven channel DMA controller that supports fast DMA transfers and scatter-gather, data buffers to isolate the PCI Bus from the ISA Bus and to enhance performance, PCI and ISA arbitration, 14 level interrupt controller, a 16-bit BIOS timer, three programmable timer/counters, and non-maskable-interrupt (NMI) control logic. The SIO also provides decode for peripheral devices (e.g., the flash BIOS, real time clock, keyboard/ mouse controller, floppy controller, two serial ports, one parallel port, and IDE hard disk drive).

#### 1.2 PCMC Overview

The PCMC (along with the LBX) provides three basic functions: a cache controller, a main memory DRAM controller, and a Host/PCI bridge. This section provides an overview of these functions. Note that, in this document, operational descriptions assume that the PCMC and LBX components are used together.

#### 1.2.1 CACHE OPERATIONS

The PCMC provides the control for a second level cache memory array implemented with either standard asynchronous SRAMs or synchronous burst SRAMs. The data memory array is external to the PCMC and located on the Host address/data bus. Since the Pentium processor contains an internal cache, there can be two separate caches in a Host subsystem. The cache inside the Pentium processor is referred to as the first level cache (also called primary cache). A detailed description of the first level cache is beyond the scope of this document. The PCMC cache control circuitry and associated external memory array is referred to as the second level cache (also called secondary cache). The second level cache is unified, meaning that both CPU data and instructions are stored in the cache. The 82434LX PCMC supports both write-through and write-back caching policies and the 82434NX supports write-back.

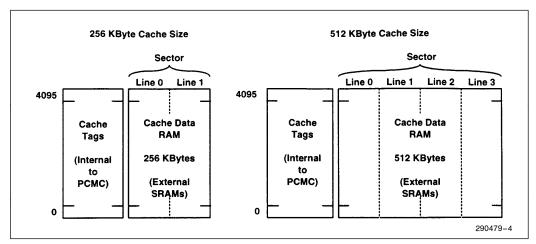

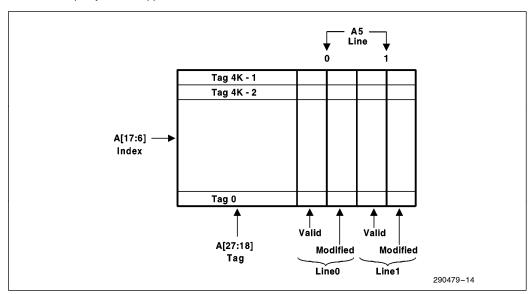

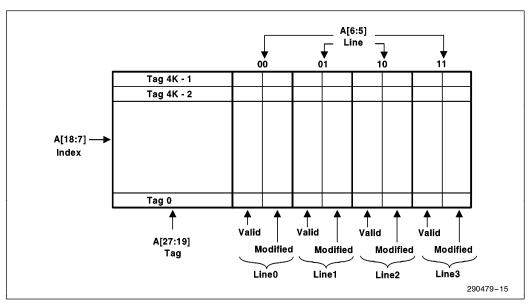

The optional second level cache memory array can be either 256-KBytes or 512-KBytes in size. The cache is direct-mapped and is organized as either 8K or 16K cache lines of 32 bytes per line.

In addition to the cache data RAM, the second level cache contains a 4K set of cache tags that are internal to the PCMC. Each tag contains an address that is associated with the corresponding data sector (2 lines for a 256 KByte cache and 4 lines for a 512 KByte cache) and two status bits for each line in the sector.

During a main memory read or write operation, the PCMC first searches the cache. If the addressed code or data is in the cache, the cycle is serviced by the cache. If the addressed code or data is not in the cache, the cycle is forwarded to main memory.

For the write-through (82434LX only) and write-back (both 82434LX and 82434NX) policies, the cache operation is determined by the CPU read or write cycle as follows:

#### **Write Cycle**

If the caching policy is write-through and the write cycle hits in the cache, both the cache and main memory are updated. Upon a cache miss, only main memory is updated. The cache is not updated (no write-allocate).

If the caching policy is write-back and the write cycle hits in the cache, only the cache is updated; main memory is not affected. Upon a cache miss, only main memory is updated. The cache is not updated (no write-allocate).

#### **Read Cycle**

Upon a cache hit, the cache operation is the same for both write-through and write-back. In this case, data is transferred from the cache to the CPU. Main memory is not accessed.

Figure 3. Second Level Cache Organization

If the read cycle causes a cache miss, the line containing the requested data is transferred from main memory to the cache and to the CPU. In the case of a write-back cache, if the cache line fill is to a sector containing one or more modified lines, the modified lines are written back to main memory and the new line is brought into the cache. For a modified line write-back operation, the PCMC transfers the modified cache lines to main memory via a write buffer in the LBX. Before writing the last modified line from the write buffer to main memory, the PCMC updates the first and second level caches with the new line, allowing the CPU access to the requested data with minimum latency.

#### 1.2.1.1 Cache Consistency

The Snoop mechanism in the PCMC ensures data consistency between cache (both first level and second level) and main memory. The PCMC monitors PCI master accesses to main memory and when needed, initiates an inquire (snoop) cycle to the first and second level caches. The snoop mechanism guarantees that consistent data is always delivered to both the host CPU and PCI masters.

#### 1.2.2 ADDRESS/DATA PATHS

Address paths between the CPU/cache and PCI and data paths between the CPU/cache, PCI, and main memory are supplied by two LBX components. The LBX is a companion component to the PCMC. Together, they form a Host/PCI bridge. The PCMC (via the PCMC/LBX interface signals), controls the address and data flow through the LBXs. Refer to the LBX data sheet for more details on the address and data paths.

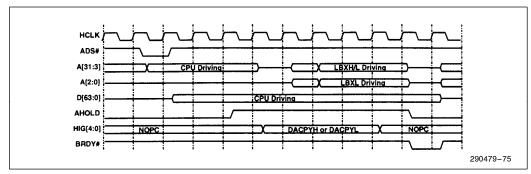

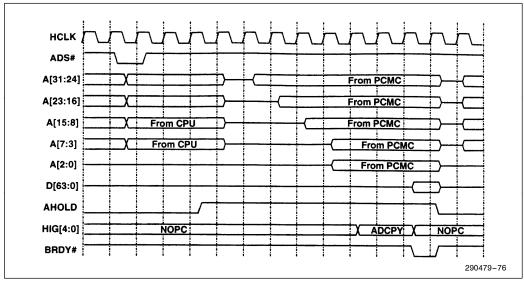

Data is transferred to and from the PCMC internal registers via the PCMC address lines. When the Host CPU performs a write operation, the data is sent to the LBXs. When the PCMC decodes the cycle as an access to one of its internal registers, it asserts AHOLD to the CPU and instructs the LBXs to copy the data onto the Host address lines. When the PCMC decodes a Host read as an access to a PCMC internal register, it asserts AHOLD to the CPU. The PCMC then places the register data on its address lines and instructs the LBX to copy the data on the Host address bus to the Host data bus. When the register data is on the Host data bus, the PCMC negates AHOLD and completes the cycle.

#### 1.2.2.1 Read/Write Buffers

The LBX provides an interface for the CPU address and data buses, PCI Address/Data bus, and the main memory DRAM data bus. There are three posted write buffers and one read-prefetch buffers implemented in the LBXs to increase performance and to maximize concurrency. The buffers are:

- CPU-to-Main Memory Posted Write Buffer (4 Qwords)

- CPU-to-PCI Posted Write Buffer (4 Dwords)

- PCI-to-Main Memory Posted Write Buffer (2 x 4 Dwords)

- PCI-to-Main Memory Read Prefetch Buffer (line buffer, 4 Qwords).

Refer to the LBX data sheet for details on the operation of these buffers.

#### 1.2.3 HOST/PCI BRIDGE OPERATIONS

The PCMC permits the Host CPU to access devices on the PCI Bus. These accesses can be to PCI I/O space, PCI memory space, or PCI configuration space.

As a PCI device, the PCMC can be either a master initiating a PCI Bus operation or a target responding to a PCI Bus operation. The PCMC is a PCI Bus master for Host-to-PCI cycles and a target for PCI-to-main memory transfers. Note that the PCMC does not permit peripherals to be located on the Host Bus. CPU I/O cycles, other than to PCMC internal registers, are forwarded to the PCI Bus and PCI Bus accesses to the Host Bus are not supported.

When the CPU initiates a bus cycle to a PCI device, the PCMC becomes a PCI Bus master and translates the CPU cycle into the appropriate PCI Bus cycle. The Host/PCI Posted write buffer in the LBXs permits the CPU to complete CPU-to-PCI Dword memory writes in three CPU clocks (1 wait-state), even if the PCI Bus is currently busy. The posted data is written to the PCI device when the PCI Bus is available.

When a PCI Bus master initiates a main memory access, the PCMC (and LBXs) become the target of the PCI Bus cycle and responds to the read/write access. During PCI-to-main memory accesses, the PCMC automatically performs cache snoop operations on the Host Bus, when needed, to maintain data consistency.

As a PCI device, the PCMC contains all of the required PCI configuration registers. The Host CPU reads and writes these registers as described in Section 3.0, Register Description.

#### 1.2.4 DRAM MEMORY OPERATIONS

The PCMC contains a DRAM controller that supports CPU and PCI master accesses to main memory. The PCMC DRAM interface supplies the control signals and address lines and the LBXs supply the data path. DRAM parity is generated for main memory writes and checked for memory reads.

For the 82434LX, the memory array is 64-bits wide and ranges in size from 2 MBytes–192 MBytes. The array can be implemented with either single-sided or double-sided SIMMs. DRAM SIMM sizes of 256K x 36, 1M x 36, and 4M x 36 are supported.

For the 82434NX, the memory array is 64-bits wide and ranges in size from 2 MBytes-512 MBytes. The array can be implemented with either single-sided or double-sided SIMMs. DRAM SIMM sizes of 256K x 36, 1M x 36, 4M x 36, and 16M x 36 are supported.

To provide optimum support for the various cache configurations, and the resultant mix of bus cycles, the system designer can select between 0-active RAS# and 1-active RAS# modes. These modes affect the behavior of the RAS# signal following either CPU-to-main memory cycles or PCI-to-main memory cycles.

The PCMC also provides programmable memory and cacheability attributes on 14 memory segments of various sizes in the ISA compatibility range (512 KByte-1 MByte address range). Access rights to these memory segments from the PCI Bus are controlled by the expansion bus bridge.

The PCMC permits a gap to be created in main memory within the 1 MByte-16 MBytes address range, accommodating ISA devices which are mapped into this range (e.g., ISA LAN card or an ISA frame buffer).

#### 1.2.5 3.3V SIGNALS

The 82434NX PCMC drives 3.3V signal levels on the CPU and second level cache interfaces. Thus, no extra logic (i.e. 5V/3.3V translation) is required when interfacing to 3.3V processors and SRAMs. Six of the power pins on the 82434NX are VDD3 pins. These pins are connected to a 3.3V power supply. The VDD3 pins power the output buffers on the CPU and second level cache interfaces. The VDD3 pins also power the output buffers for the HCLK[A-F] outputs.

#### 2.0 SIGNAL DESCRIPTIONS

This section provides a detailed description of each signal. The signals are arranged in functional groups according to their associated interface. The states of all of the signals during hard reset are provided in Section 8.0, System Clocking and Reset.

The "#" symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level. When "#" is not present after the signal name, the signal is asserted when at the high voltage level.

The terms assertion and negation are used extensively. This is done to avoid confusion when working with a mixture of "active-low" and "active-high" signals. The term **assert**, or **assertion** indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term **negate**, or **negation** indicates that a signal is inactive.

The following notations are used to describe the signal type.

in Input is a standard input-only signal

out Totem pole output is a standard active driver

o/d Open drain

t/s Tri-State is a bi-directional, tri-state input/output pin

s/t/s Sustained tri-state is an active low tri-state signal owned and driven by one and only one agent at a time. The agent that drives a s/t/s pin low must drive it high for at least one clock before letting it float. A new agent can not start driving a s/t/s signal any sooner than one clock after the previous owner tri-states it. An external pull-up is required to sustain the inactive state until another agent drives it and must be provided by the central resource.

#### 2.1 Host Interface

| Signal  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[31:0] | t/s  | ADDRESS BUS: A[31:0] are the address lines of the Host Bus. A[31:3] are connected to the CPU A[31:3] lines and to the LBXs. A[2:0] are only connected to the LBXs. Along with the byte enable signals, the A[31:3] lines define the physical area of memory or I/O being accessed. During CPU cycles, the A[31:3] lines are inputs to the PCMC. They are used for address decoding and second level cache tag lookup sequences. Also during CPU cycles, A[2:0] are outputs and are generated from BE[7:0] #. A[27:24] provide hardware strapping options for test features. For more details on theses options, refer to Section 11.0 Testability. |

|         |      | During inquire cycles, A[31:5] are inputs from the LBXs to the CPU and the PCMC to snoop the first and the second level cache tags, respectively. In response to a Flush or Flush Acknowledge Special Cycle, the PCMC asserts AHOLD and drives the addresses of the second level cache lines to be written back to main memory on A[18:7].                                                                                                                                                                                                                                                                                                         |

|         |      | During CPU to PCI configuration cycles, the PCMC drives A[31:0] with the PCI configuration space address that is internally derived from the CPU physical I/O address. All PCMC internal configuration registers are accessed via A[31:0]. During CPU reads from PCMC internal configuration registers, the PCMC asserts AHOLD and drives the contents of the addressed register on A[31:0]. The PCMC then signals the LBXs to copy this value from the address lines onto the host data lines. During writes to PCMC internal configuration registers, the PCMC asserts AHOLD and signals the LBXs to copy the write data onto the A[31:0] lines. |

|         |      | Finally, when in deturbo mode, the PCMC periodically asserts AHOLD and then drives A[31:0] to valid logic levels to keep these lines from floating for an extended period of time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         |      | A[31:28] provide hardware strapping options at powerup. For more details on strapping options, refer to Section 8.0, System Clocking and Reset. A[27:24] provide hardware strapping options for test features. For more details on these options, refer to Section 11.0 Testability.                                                                                                                                                                                                                                                                                                                                                               |

|          |      | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                            |  |  |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Signal   | Туре |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Description                                                                                                                                                                                                                                                                |  |  |

| BE[7:0]# | in   | <b>BYTE ENABLES:</b> The byte enables indicate which byte lanes on the CPU data bus carry valid data during the current bus cycle. In the case of cacheable reads, all 8 byte of data are driven to the Pentium processor, regardless of the state of the byte enable. The byte enable signals indicate the type of special cycle when $M/IO\# = D/C\# = 0$ ar $W/R\# = 1$ . During special cycles, only one byte enable is asserted by the CPU. The following table depicts the special cycle types and their byte enable encodings: |                                                                                                                                                                                                                                                                            |  |  |

|          |      | Special Cycle Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Asserted Byte Enable                                                                                                                                                                                                                                                       |  |  |

|          |      | Shutdown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | BE0#                                                                                                                                                                                                                                                                       |  |  |

|          |      | Flush                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | BE1#                                                                                                                                                                                                                                                                       |  |  |

|          |      | Halt/Stop Grant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | BE2#                                                                                                                                                                                                                                                                       |  |  |

|          |      | Write Back                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | BE3#                                                                                                                                                                                                                                                                       |  |  |

|          |      | Flush Acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | BE4#                                                                                                                                                                                                                                                                       |  |  |

|          |      | Branch Trace Message                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | BE5#                                                                                                                                                                                                                                                                       |  |  |

|          |      | 000000 (the PCI Shutdown S the LBXs to latch the host addr                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | nutdown Special Cycle, it asserts AHOLD, drives pecial Cycle Encoding) on the A[31:0] lines and signals ess bus. The PCMC then drives a Special Cycle on PCI, latched address (0000) on the AD[31:0] lines during n asserts INIT for 16 HCLKs.                             |  |  |

|          |      | inspects the Valid and Modified<br>line is both valid and modified,<br>A[18:7] and CAA/CAB[6:3] line                                                                                                                                                                                                                                                                                                                                                                                                                                  | Acknowledge Special Cycles, the PCMC internally bits for each of the Second Level Cache Sectors. If a the PCMC drives the cache address of the line on the es and writes the line back to main memory. The valid at to 0. All valid and unmodified lines are simply marked |  |  |

|          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ecial cycle, the PCMC simply returns BRDY # to the CPU. written back to main memory in response to the                                                                                                                                                                     |  |  |

|          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | pecial cycle, the 82434NX uses A4 to determine if the pecial Cycle. If A4 = 0, the cycle is a Halt Special Cycle p Grant Special cycle.                                                                                                                                    |  |  |

|          |      | halt special cycle encoding) on address bus. The PCMC then c                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | cle, the PCMC asserts AHOLD, drives 000001 (the PCI the A[31:0] lines, and signals the LBXs to latch the host drives a special cycle on PCI, signaling the LBXs to drive in the AD[31:0] lines during the data phase.                                                      |  |  |

|          |      | D/C#=0, $W/R#=1$ , $A4=1$ , $E$ cycle, with 0002h in the messa                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ects a CPU Stop Grant Special Cycle (M/IO#=0, BE[7:0]#=FBh), it generates a PCI Stop Grant Special ge field (AD[15:0]) and 0012h in the message dependent le first data phase (IRDY# asserted).                                                                            |  |  |

| ADS#     | in   | cycle is beginning. ADS# is dri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | tium processor asserts ADS# to indicate that a new bus ven active in the same clock as the address, byte enable, e PCMC ignores a floating low ADS# that may occur e CPU is asserting ADS#.                                                                                |  |  |

| Signal | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BRDY#  | out  | BURST READY: BRDY # indicates that the system has responded in one of three ways:  1. valid data has been placed on the Pentium processor data pins in response to a read,  2. CPU write data has been accepted by the system, or  3. the system has responded to a special cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| NA#    | out  | <b>NEXT ADDRESS:</b> The PCMC asserts NA# for one clock when the memory system is ready to accept a new address from the CPU, even if all data transfers for the current cycle have not completed. The CPU may drive out a pending cycle two clocks after NA# is asserted and has the ability to support up to two outstanding bus cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| AHOLD  | out  | ADDRESS HOLD: The PCMC asserts AHOLD to force the Pentium processor to stop driving the address bus so that either the PCMC or LBXs can drive the bus. During PCI master cycles, AHOLD is asserted to allow the LBXs to drive a snoop address onto the address bus. If the PCI master locks main memory, AHOLD remains asserted until the PCI master locked sequence is complete and the PCI master negates PLOCK#.  AHOLD is asserted during all accesses to PCMC internal configuration registers to allow configuration register accesses to occur over the A[31:0] lines.  When in deturbo mode, the PCMC periodically asserts AHOLD to prevent the processor from initiating bus cycles in order to emulate a slower system. The duration of AHOLD assertion in deturbo mode is controlled by the Deturbo Frequency Control Register (offset 51h). When PWROK is negated, the PCMC asserts AHOLD to allow the strapping options on A[31:28] to be read. For more details on strapping options, see the System Clocking and Reset section. |

| EADS#  | out  | <b>EXTERNAL ADDRESS STROBE:</b> The PCMC asserts EADS# to indicate to the Pentium processor that a valid snoop address has been driven onto the CPU address lines to perform an inquire cycle. During PCI master cycles, the PCMC signals the LBXs to drive a snoop address onto the host address lines and then asserts EADS# to cause the CPU to sample the snoop address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| INV    | out  | INVALIDATE: The INV signal specifies the final state (invalid or shared) that a first level cache line transitions to in the event of a cache line hit during a snoop cycle. When snooping the caches during a PCI master write, the PCMC asserts INV with EADS#. When INV is asserted with EADS#, an inquire hit results in the line being invalidated. When snooping the caches during a PCI master read, the PCMC does not assert INV with EADS#. In this case, an inquire cycle hit results in a line transitioning to the shared state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| BOFF#  | out  | BACKOFF: The PCMC asserts BOFF# to force the Pentium processor to abort all outstanding bus cycles that have not been completed and float its bus in the next clock. The PCMC uses this signal to force the CPU to re-order a write-back due to a snoop cycle around a currently outstanding bus cycle. The PCMC also asserts BOFF# to obtain the CPU data bus for write-back cycles from the secondary cache due to a snoop hit. The CPU remains in bus hold until BOFF# is negated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| HITM#  | in   | HIT MODIFIED: The Pentium processor asserts HITM# to inform the PCMC that the current inquire cycle hit a modified line. HITM# is asserted by the Pentium processor two clocks after the assertion of EADS# if the inquire cycle hits a modified line in the primary cache.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Signal                | Туре |                                                                                                                                                                         |                                                                                                                    |                                                                                                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M/IO#<br>D/C#<br>W/R# | in   | BUS CYCLE DEFINITION (MEMORY/INPUT-OUTPUT, DATA/CONTROL, WRITE/READ): M/IO, D/C# and W/R# define Host Bus cycles as shown in the table below.                           |                                                                                                                    |                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                       |      | M/IO#                                                                                                                                                                   | D/C#                                                                                                               | W/R#                                                                                                                                | Bus Cycle Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                       |      | Low                                                                                                                                                                     | Low                                                                                                                | Low                                                                                                                                 | Interrupt Acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                       |      | Low                                                                                                                                                                     | Low                                                                                                                | High                                                                                                                                | Special Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                       |      | Low                                                                                                                                                                     | High                                                                                                               | Low                                                                                                                                 | I/O Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                       |      | Low                                                                                                                                                                     | High                                                                                                               | High                                                                                                                                | I/O Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                       |      | High                                                                                                                                                                    | Low                                                                                                                | Low                                                                                                                                 | Code Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                       |      | High                                                                                                                                                                    | Low                                                                                                                | High                                                                                                                                | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                       |      | High                                                                                                                                                                    | High                                                                                                               | Low                                                                                                                                 | Memory Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |