# **DSP16410CG Digital Signal Processor**

# **1** Features

- Twin DSP16000 dual-MAC cores perform up to 780 million MACs per second at 195 MHz

- Low power: — 1 575 V internal si

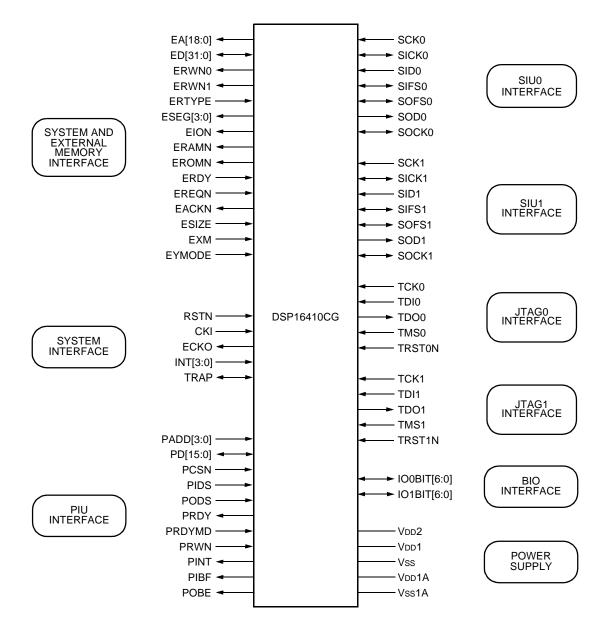

- 1.575 V internal supply for power efficiency

3.3 V I/O pin supply for compatibility

- 194K x 16 on-chip RAM

- Centralized direct memory access unit (DMAU):

- Transparent peripheral-to-memory and memoryto-memory transfers

- Better utilization of DSP MIPS

- Simplifies management of system data flow

- 16-bit parallel interface unit (PIU) with direct memory access (DMA) provides host access to all DSP memory

- Two enhanced serial I/O units (SIU0 and SIU1) with DMA:

- Compatible with TDM highways such as T1/E1 and ST-bus

- Hardware support for µ-law and A-law companding

- Core messaging units (MGU0 and MGU1) for interprocessor communication

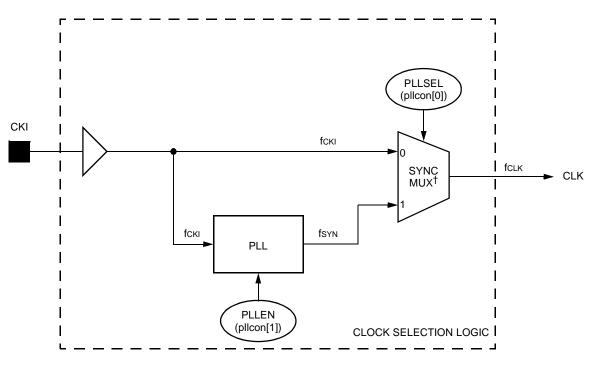

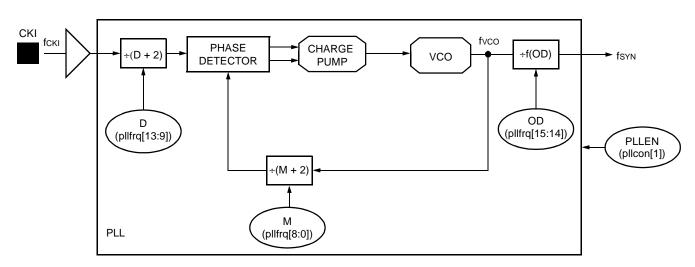

- On-chip, programmable, PLL clock synthesizer eliminates need for high-speed clock input

- Two 7-bit control I/O interfaces (BIOs) for increased flexibility and lower system costs

- 32-bit system and external memory interface (SEMI) supports 16-bit or 32-bit synchronous or asynchronous memories

- Two IEEE<sup>®</sup> 1149.1 test ports (JTAG boundary scan)

- Full-speed, in-circuit emulation hardware for each core with eight address and two data watchpoint units for efficient application development

- Supported by DSP16410CG software and hardware development tools

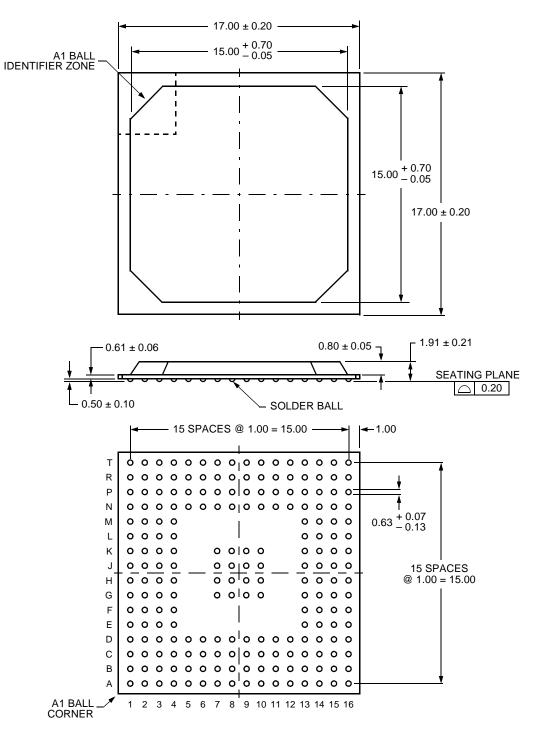

- 208-ball PBGA package for small footprint (17 mm x 17 mm; 1.0 mm ball pitch)

# **2** Description

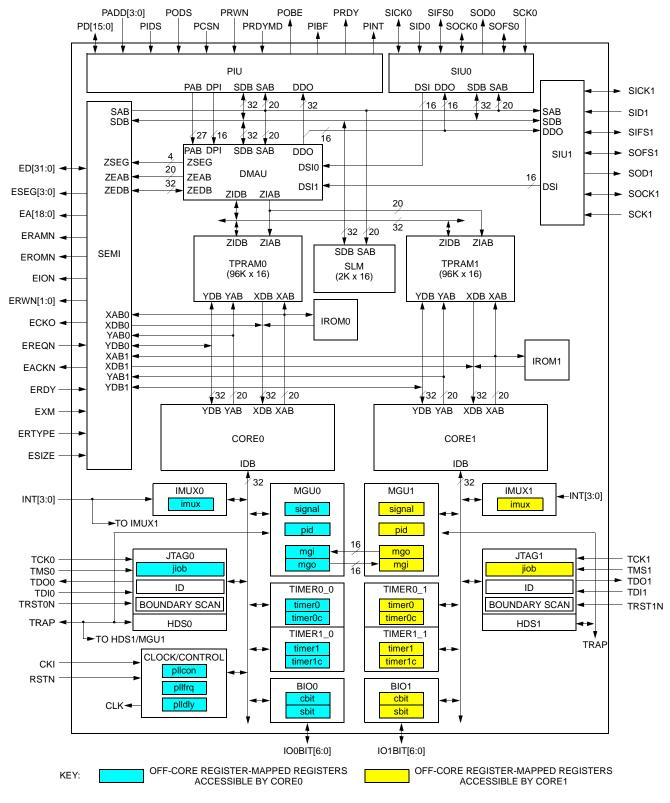

The DSP16410CG, also known as the DSP16410C, is a digital signal processor (DSP) optimized for communications infrastructure applications. Large, onchip memory enables it to be programmed to perform numerous fixed-point signal processing functions, including equalization, channel coding, or speech coding. This is the first Agere wireless product to feature twin DSP16000 dual-MAC DSP cores and enhanced DMA capabilities. Together, these features deliver the performance required for second- and third-generation infrastructure equipment.

The DSP16410CG achieves best-in-class signal processing performance while maintaining efficient software code density, low power consumption, and small physical size.

Page

# **Table of Contents**

# Contents

| ≻       | 1                |                                         | atures                                                                       |    |

|---------|------------------|-----------------------------------------|------------------------------------------------------------------------------|----|

| $\succ$ | 2                | De                                      | scription                                                                    | 1  |

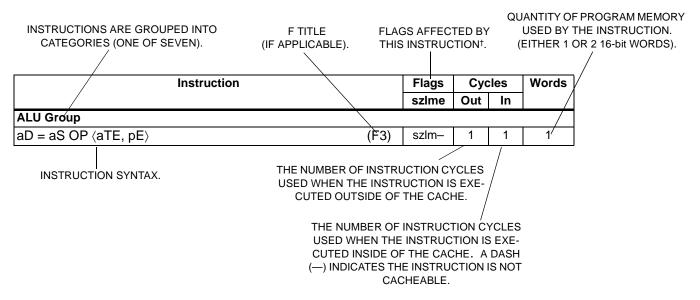

| $\geq$  | 3                | Not                                     | tation Conventions                                                           | 14 |

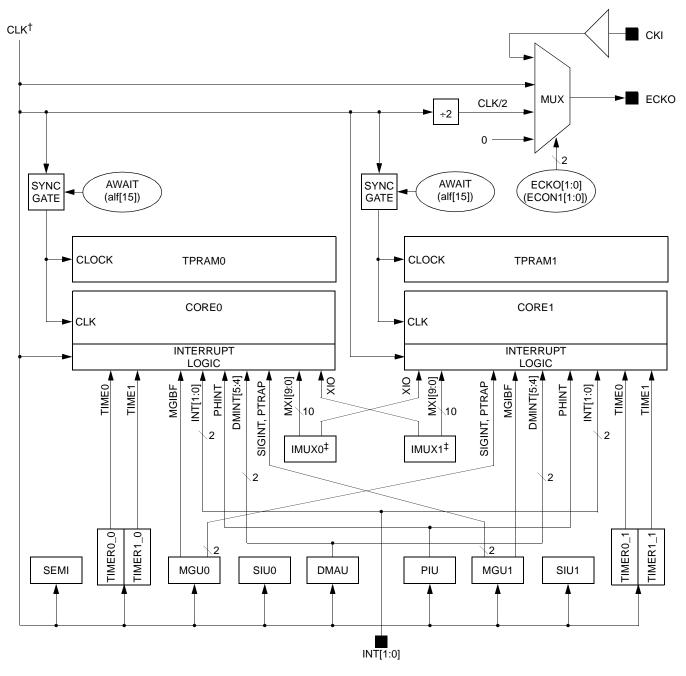

| $\succ$ | 4                | Ha                                      | rdware Architecture                                                          | 14 |

|         | $\succ$          | 4.1                                     | DSP16410CG Architectural Overview                                            | 14 |

|         |                  | $\succ$                                 | 4.1.1 DSP16000 Cores                                                         | 17 |

|         |                  | $\succ$                                 | 4.1.2 Clock Synthesizer (PLL)                                                | 17 |

|         |                  | $\succ$                                 | 4.1.3 Triport RAMs (TPRAM(0—1))                                              | 17 |

|         |                  | $\succ$                                 | 4.1.4 Shared Local Memory (SLM)                                              | 17 |

|         |                  | $\succ$                                 | 4.1.5 Internal Boot ROMs (IROM(0-1))                                         |    |

|         |                  | $\succ$                                 | 4.1.6 Messaging Units (MGU $\langle 0-1 \rangle$ )                           |    |

|         |                  | $\succ$                                 | 4.1.7 System and External Memory Interface (SEMI)                            |    |

|         |                  | $\succ$                                 | 4.1.8 Bit Input/Output Units (BIO(0—1))                                      |    |

|         |                  | $\succ$                                 | 4.1.9 Timer Units (TIMER0_(0—1) and TIMER1_(0—1))                            |    |

|         |                  | $\geq$                                  | 4.1.10 Direct Memory Access Unit (DMAU)                                      |    |

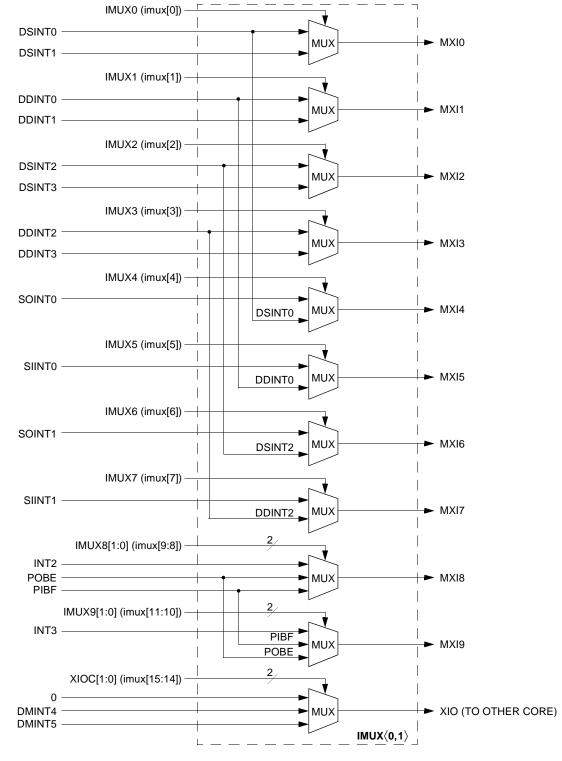

|         |                  | $\geq$                                  | 4.1.11 Interrupt Multiplexers (IMUX(0—1))                                    |    |

|         |                  | >                                       | 4.1.12 Parallel Interface Unit (PIU)                                         |    |

|         |                  |                                         | 4.1.13 Serial Interface Units (SIU $\langle 0-1 \rangle$ )                   |    |

|         |                  |                                         | 4.1.14 Test Access Ports (JTAG $(0-1)$ )                                     |    |

|         |                  |                                         | 4.1.15 Hardware Development Systems (HDS(0–1))                               |    |

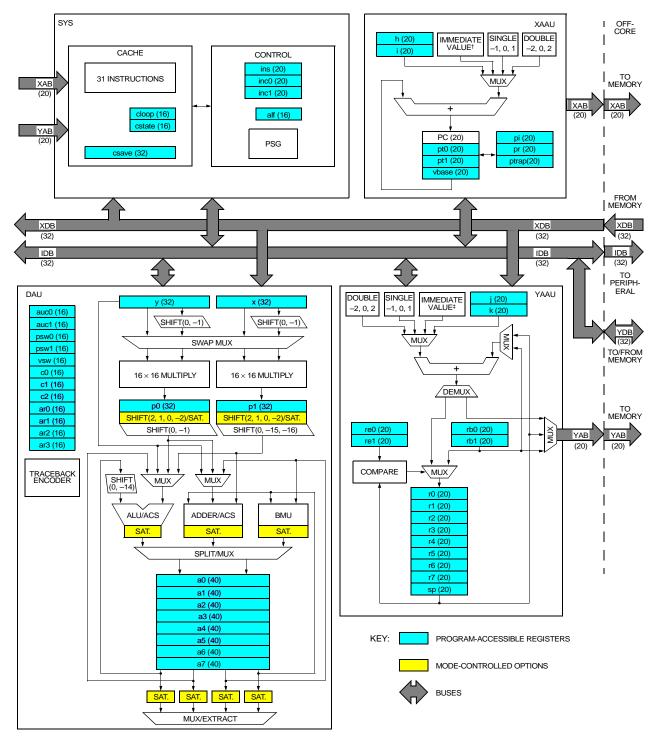

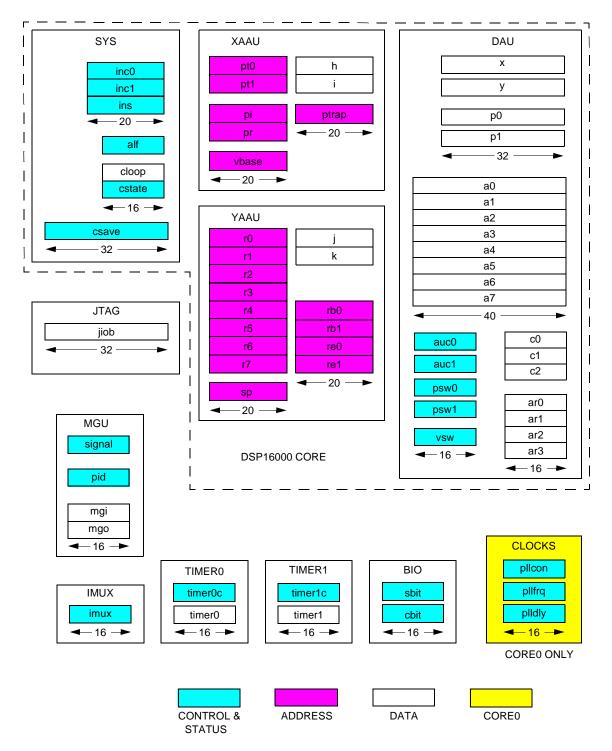

|         | $\triangleright$ |                                         | DSP16000 Core Architectural Overview                                         |    |

|         |                  | >                                       | 4.2.1 System Control and Cache (SYS)                                         |    |

|         |                  | 5                                       | 4.2.2 Data Arithmetic Unit (DAU)                                             |    |

|         |                  | 5                                       | 4.2.3 Y-Memory Space Address Arithmetic Unit (YAAU)                          |    |

|         |                  | 5                                       | 4.2.4 X-Memory Space Address Arithmetic Unit (XAAU)                          |    |

|         |                  | 5                                       | 4.2.5 Core Block Diagram                                                     |    |

|         |                  | 4.3                                     | •                                                                            |    |

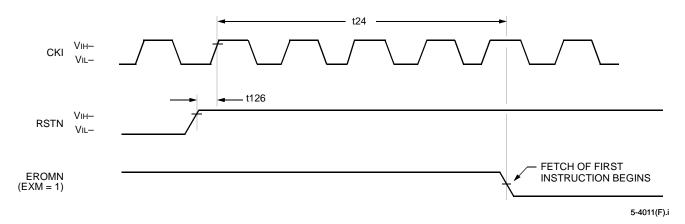

|         |                  | 4.5                                     | 4.3.1 Reset After Powerup or Power Interruption                              |    |

|         |                  |                                         | 4.3.2 RSTN Pin Reset                                                         |    |

|         |                  |                                         | 4.3.3 JTAG Controller Reset                                                  |    |

|         |                  | 4.4                                     |                                                                              |    |

|         |                  | 4.4                                     |                                                                              |    |

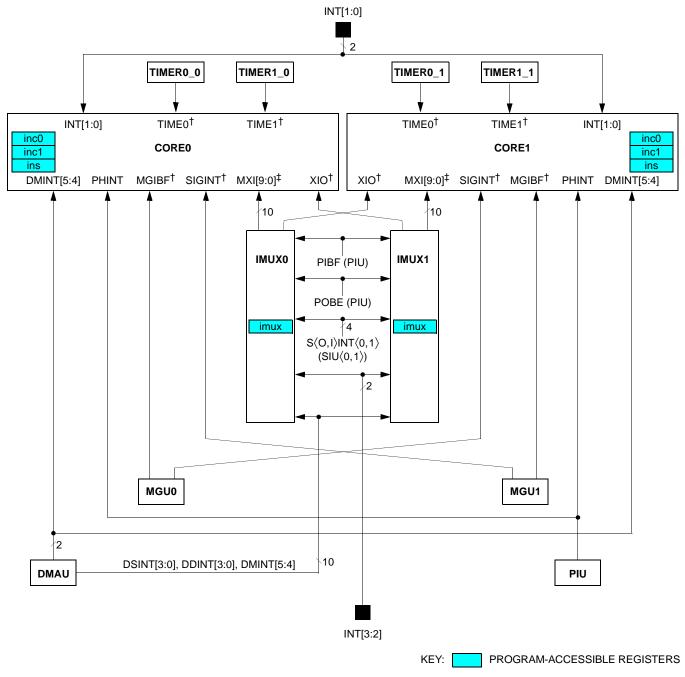

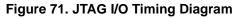

|         |                  |                                         | 4.4.1 Hardware Interrupt Logic                                               |    |

|         |                  |                                         | 4.4.2 Hardware Interrupt Multiplexing                                        |    |

|         |                  |                                         | <b>o</b> 1 1                                                                 |    |

|         |                  |                                         | 4.4.4 Host Interrupt Output                                                  |    |

|         |                  |                                         | 4.4.5 Globally Enabling and Disabling Hardware Interrupts                    |    |

|         |                  |                                         | 4.4.6 Individually Enabling, Disabling, and Prioritizing Hardware Interrupts |    |

|         |                  |                                         | 4.4.7 Hardware Interrupt Status                                              |    |

|         |                  | <                                       | 4.4.8 Interrupt and Trap Vector Table                                        |    |

|         |                  |                                         | 4.4.9 Software Interrupts                                                    |    |

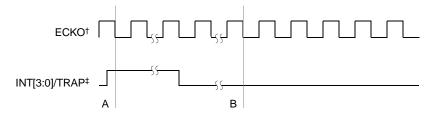

|         |                  |                                         | 4.4.10 INT[3:0] and TRAP Pins                                                |    |

|         |                  | <                                       | 4.4.11 Nesting Interrupts                                                    |    |

|         |                  | $\sim$                                  | 4.4.12 Interrupts and Cache Usage                                            |    |

|         |                  | ~                                       | 4.4.13 Interrupt Polling                                                     |    |

|         |                  |                                         | Memory Maps                                                                  |    |

|         |                  |                                         | 4.5.1 Private Internal Memory                                                |    |

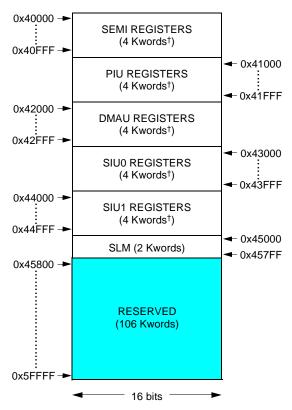

|         |                  | $\sim$                                  | 4.5.2 Shared Internal I/O                                                    |    |

|         |                  | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | 4.5.3 Shared External I/O and Memory                                         |    |

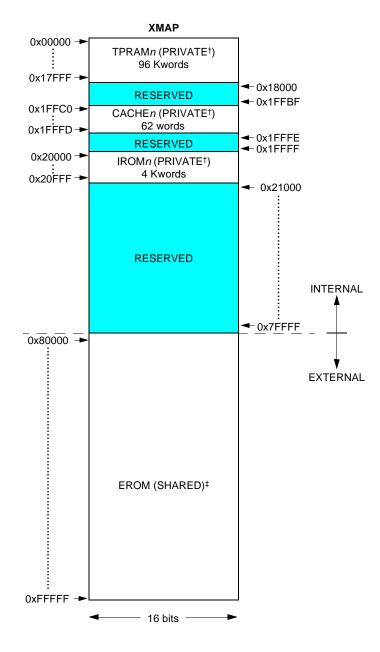

|         |                  | >                                       | 4.5.4 X-Memory Map                                                           |    |

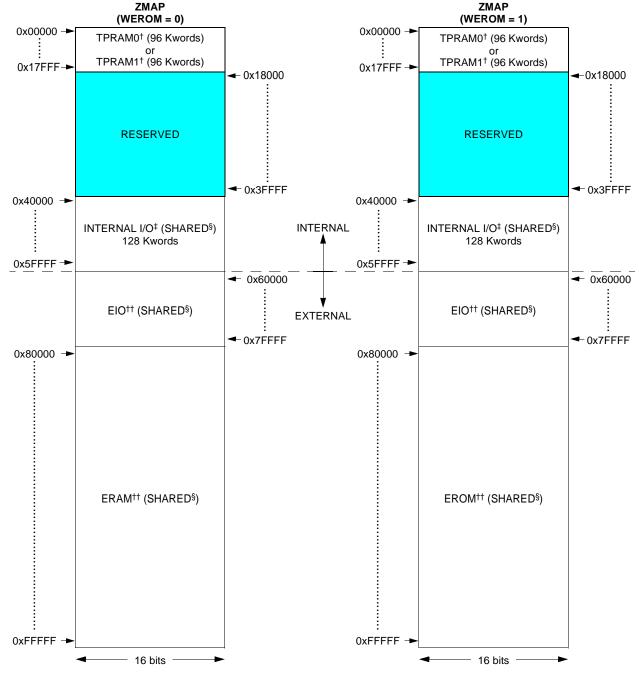

|         |                  | >                                       | 4.5.5 Y-Memory Maps                                                          |    |

|         |                  | $\succ$                                 | 4.5.6 Z-Memory Maps                                                          | 42 |

# Contents

| 4.5.7 Internel I/O Detailed Momeny Man                                                                       | 40  |

|--------------------------------------------------------------------------------------------------------------|-----|

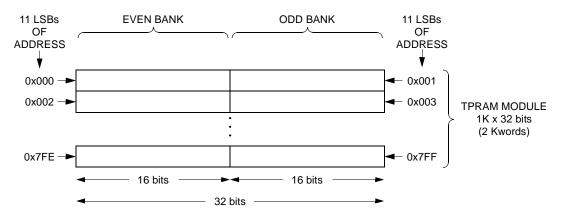

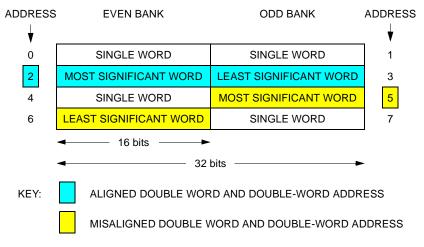

| <ul> <li>4.5.7 Internal I/O Detailed Memory Map</li> <li>4.6 Triport Random-Access Memory (TPRAM)</li> </ul> |     |

| <ul> <li>A.7 Shared Local Memory (SLM)</li> </ul>                                                            |     |

| <ul> <li>4.7 Shared Local Memory (SLM)</li></ul>                                                             |     |

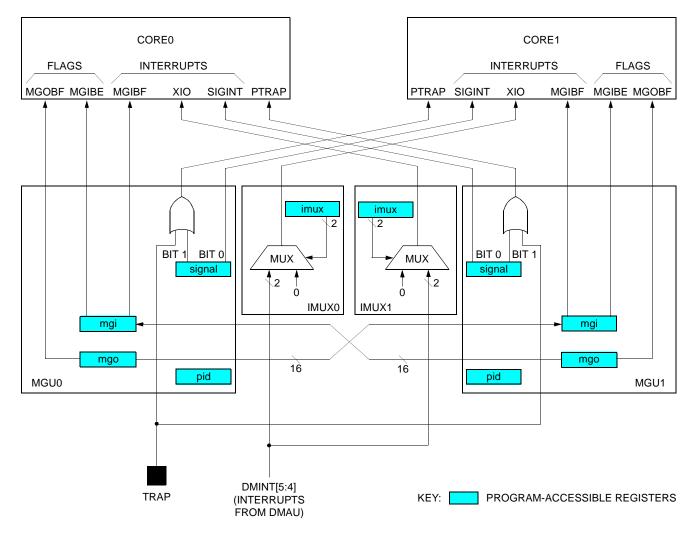

| <ul> <li>4.8 1 Core-to-Core Interrupts and Traps</li> </ul>                                                  |     |

| <ul> <li>4.8.2 Message Buffer Data Exchange</li> </ul>                                                       |     |

| <ul> <li>4.8.2.1 Message Buffer Write Protocol</li> </ul>                                                    |     |

| <ul> <li>4.8.2.2 Message Buffer Read Protocol</li> </ul>                                                     |     |

| <ul> <li>4.8.3 DMAU Data Transfer.</li> </ul>                                                                |     |

| > 4.9 Bit Input/Output Units (BIO $\langle 0-1 \rangle$ )                                                    |     |

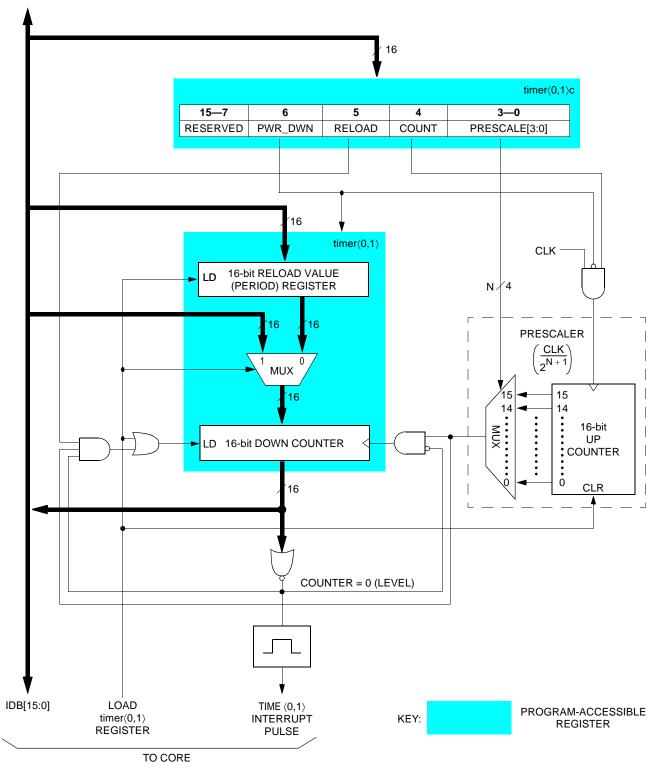

| $\rightarrow$ 4.10 Timer Units (TIMER0_(0-1) and TIMER1_(0-1))                                               | 53  |

| $\rightarrow$ 4.11 Hardware Development System (HDS $\langle 0-1 \rangle$ )                                  |     |

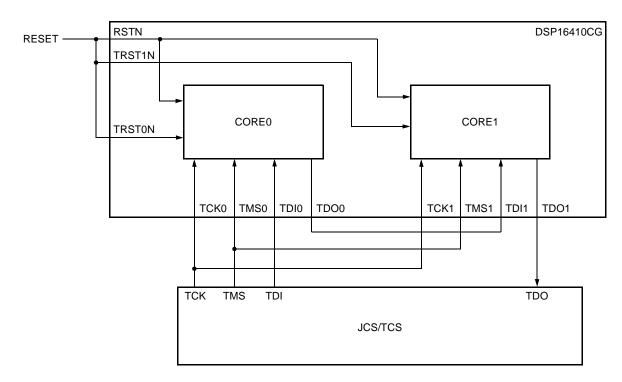

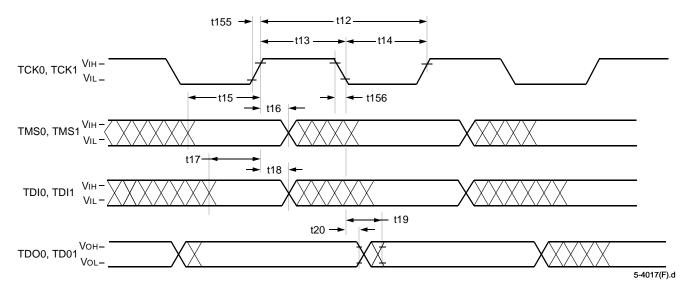

| > 4.12 JTAG Test Port (JTAG $\langle 0-1 \rangle$ )                                                          |     |

| <ul> <li>4.12.1 Port Identification</li> </ul>                                                               |     |

| 4.12.2 Emulation Interface Signals to the DSP16410CG                                                         |     |

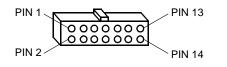

| ▶ 4.12.2.1 TCS 14-Pin Header                                                                                 |     |

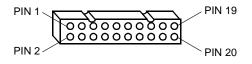

| > 4.12.2.2 JCS 20-Pin Header                                                                                 |     |

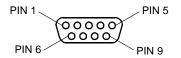

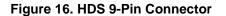

| 4.12.2.3 HDS 9-Pin, D-Type Connector                                                                         |     |

| 4.12.3 Multiprocessor JTAG Connections                                                                       |     |

| 4.12.4 Boundary Scan                                                                                         |     |

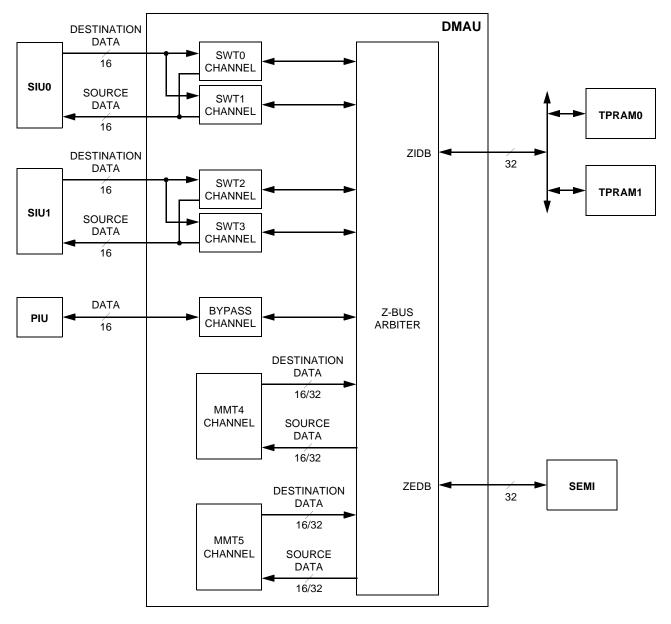

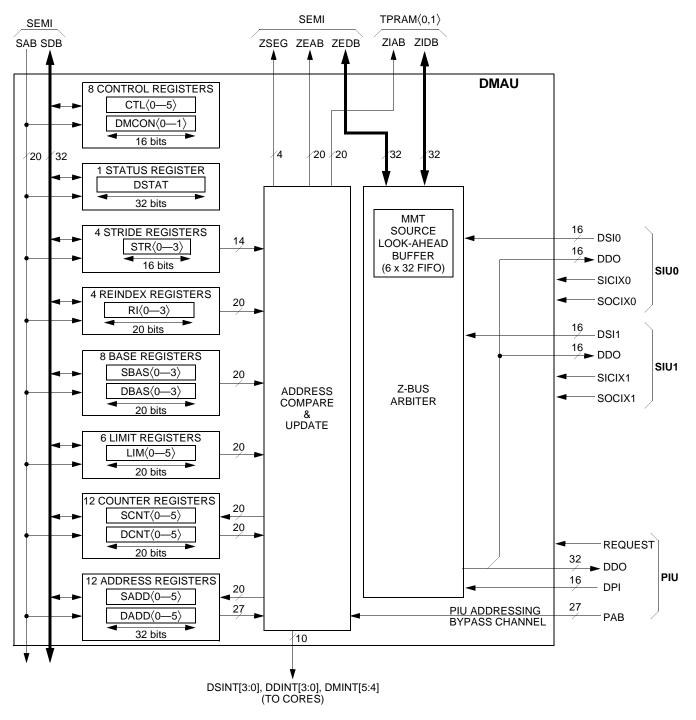

| > 4.13 Direct Memory Access Unit (DMAU)                                                                      |     |

| > 4.13.1 Overview                                                                                            |     |

| 4.13.2 Registers                                                                                             |     |

| 4.13.3 Data Structures                                                                                       | 83  |

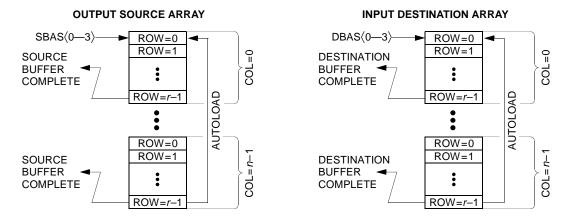

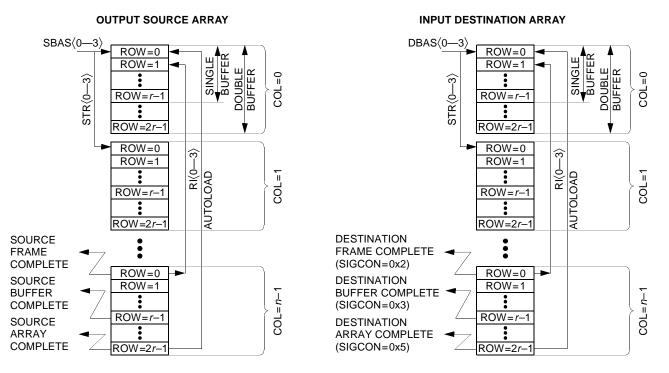

| 4.13.3.1 One-Dimensional Data Structure (SWT Channels)                                                       | 83  |

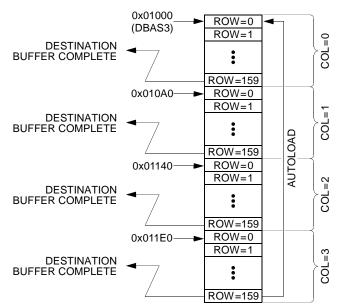

| 4.13.3.2 Two-Dimensional Data Structure (SWT Channels)                                                       |     |

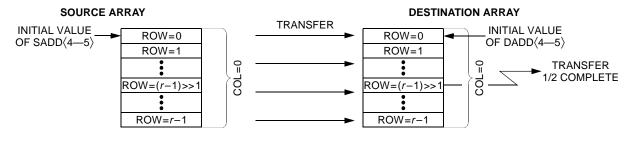

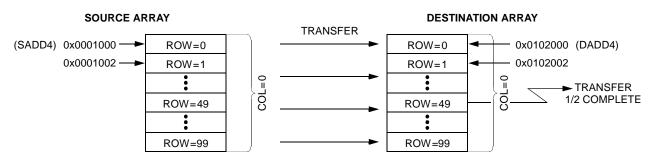

| 4.13.3.3 Memory-to-Memory Block Transfers (MMT Channels)                                                     |     |

| 4.13.4 The PIU Addressing Bypass Channel                                                                     | 86  |

| 4.13.5 Single-Word Transfer Channels (SWT)                                                                   | 87  |

| 4.13.6 Memory-to-Memory Transfer Channels (MMT)                                                              | 90  |

| 4.13.7 Interrupts and Priority Resolution                                                                    | 92  |

| 4.13.8 Error Reporting and Recovery                                                                          | 94  |

| 4.13.9 Programming Examples                                                                                  |     |

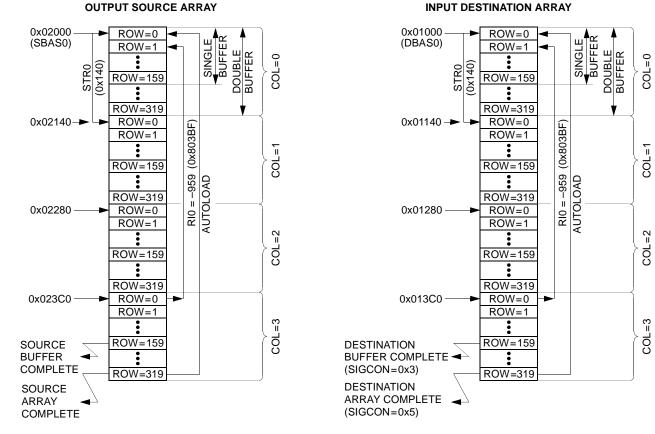

| 4.13.9.1 SWT Example 1: A Two-Dimensional Array                                                              |     |

| 4.13.9.2 SWT Example 2: A One-Dimensional Array                                                              |     |

| 4.13.9.3 MMT Example                                                                                         |     |

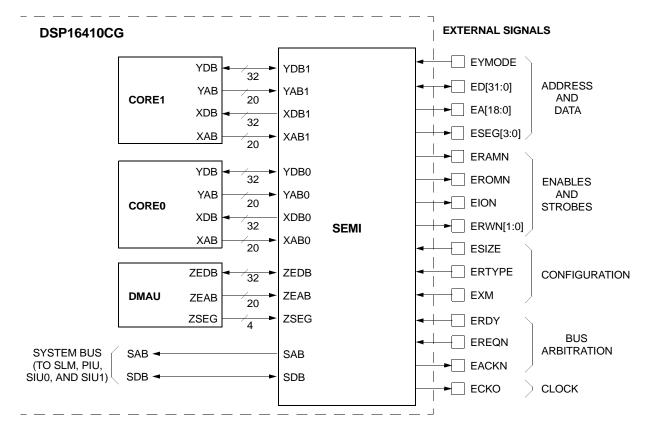

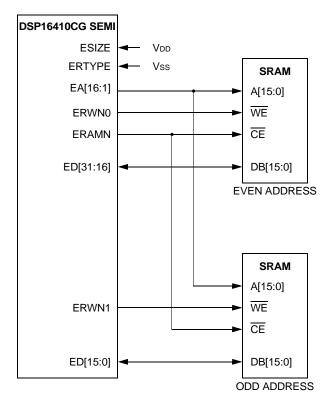

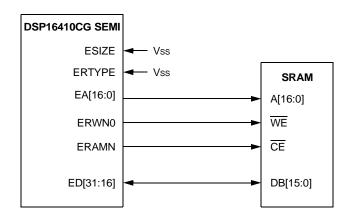

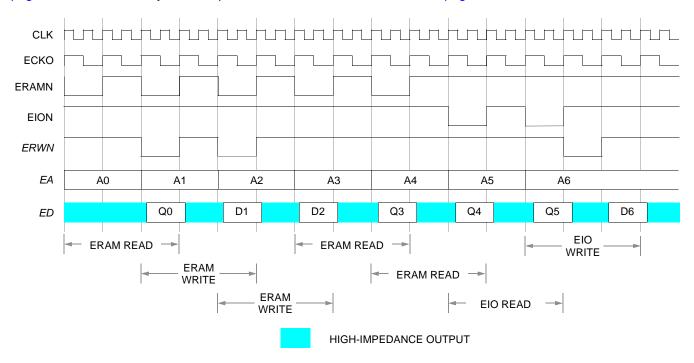

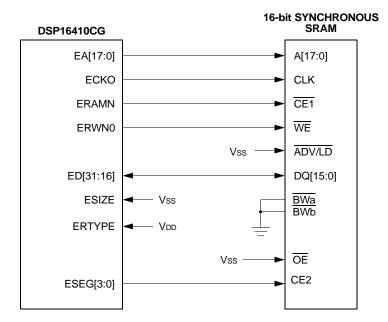

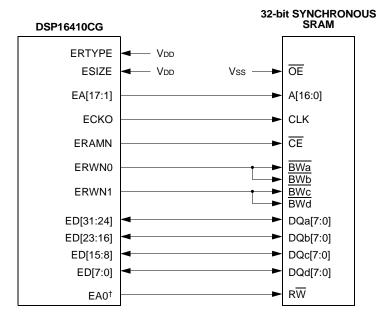

| 4.14 System and External Memory Interface (SEMI)                                                             | 100 |

| 4.14.1 External Interface                                                                                    |     |

| 4.14.1.1 Configuration                                                                                       |     |

| 4.14.1.2 Asynchronous Memory Bus Arbitration                                                                 |     |

| 4.14.1.3 Enables and Strobes                                                                                 |     |

| 4.14.1.4 Address and Data                                                                                    |     |

| 4.14.2 16-Bit External Bus Accesses                                                                          |     |

| 4.14.3 32-Bit External Bus Accesses                                                                          |     |

| 4.14.4 Registers                                                                                             |     |

| 4.14.4.1 ECON0 Register                                                                                      |     |

| 4.14.4.2 ECON1 Register                                                                                      |     |

| 4.14.4.3 Segment Registers                                                                                   |     |

| 4.14.5 Asynchronous Memory                                                                                   |     |

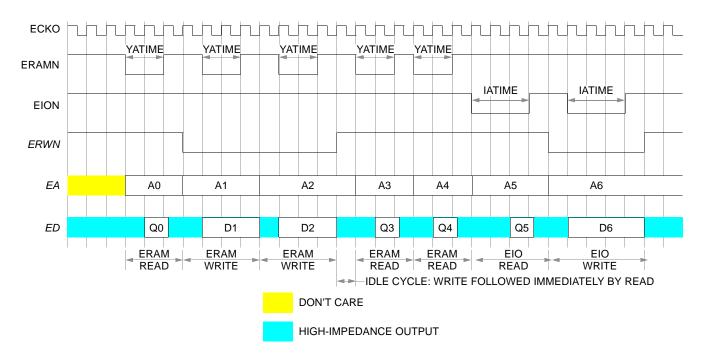

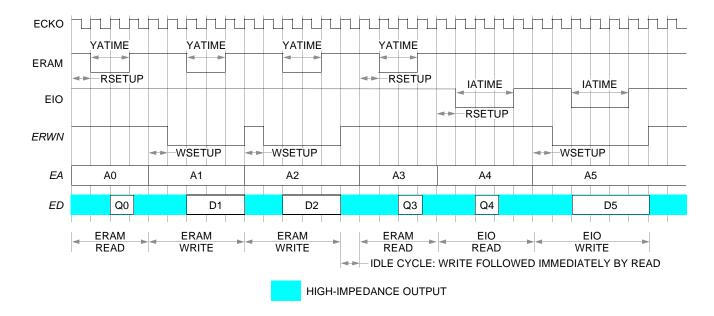

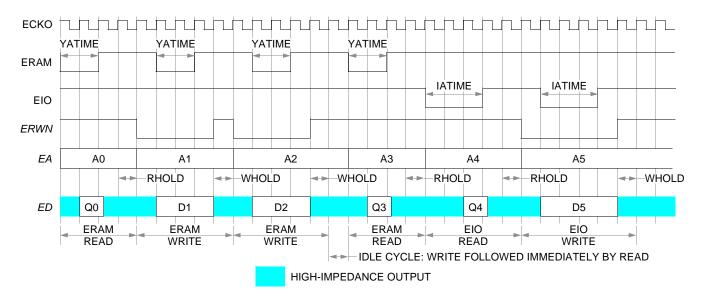

| 4.14.5.1 Functional Timing                                                                                   |     |

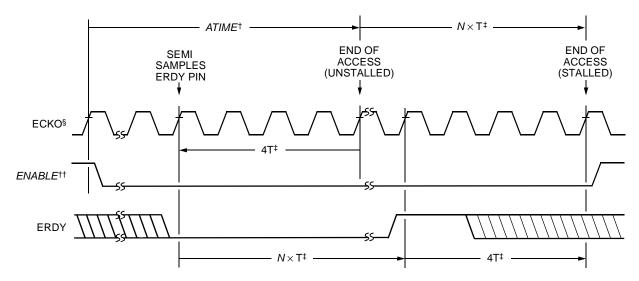

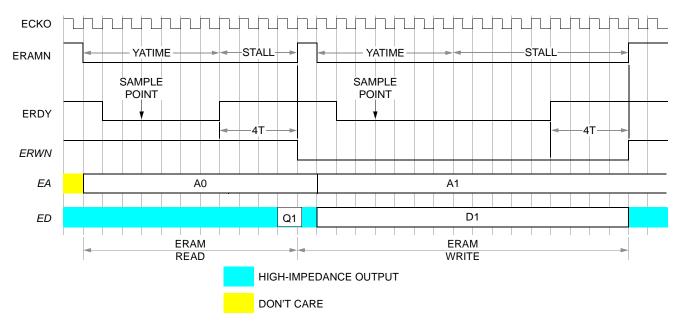

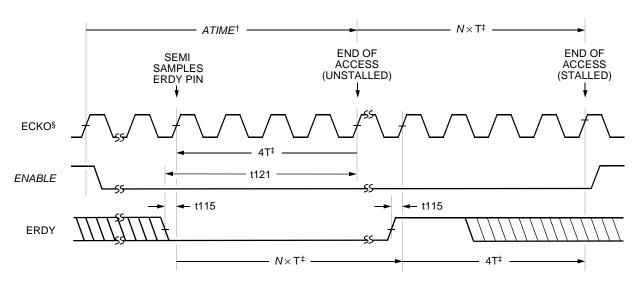

| 4.14.5.2 Extending Access Time Via the ERDY Pin                                                              | 118 |

# Contents

| 4.14.5.3 Interfacing Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 120                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 4.14.6 Synchronous Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 122                                                                                                                                      |

| 4.14.6.1 Functional Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 122                                                                                                                                      |

| 4.14.6.2 Interfacing Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                          |

| 4.14.7 Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 126                                                                                                                                      |

| 4.14.7.1 System Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                          |

| 4.14.7.2 External Memory, Asynchronous Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                          |

| 4.14.7.3 External Memory, Synchronous Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                          |

| 4.14.7.4 Summary of Access Times                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 131                                                                                                                                      |

| 4.14.8 Priority                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                          |

| > 4.15 Parallel Interface Unit (PIU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 133                                                                                                                                      |

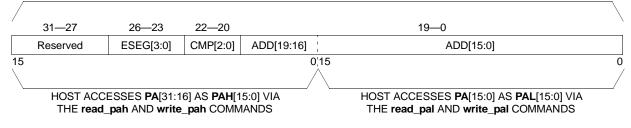

| 4.15.1 Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 133                                                                                                                                      |

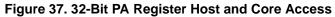

| 4.15.2 Hardware Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                          |

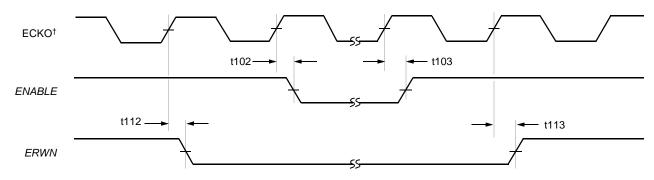

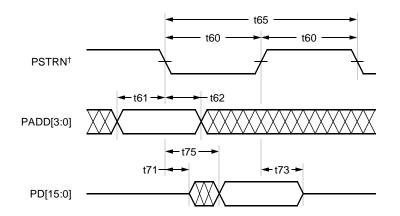

| 4.15.2.1 Enables and Strobes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                          |

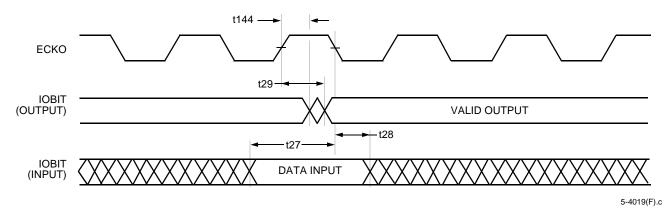

| 4.15.2.2 Address and Data Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                          |

| 4.15.2.3 Flags, Interrupt, and Ready Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 140                                                                                                                                      |

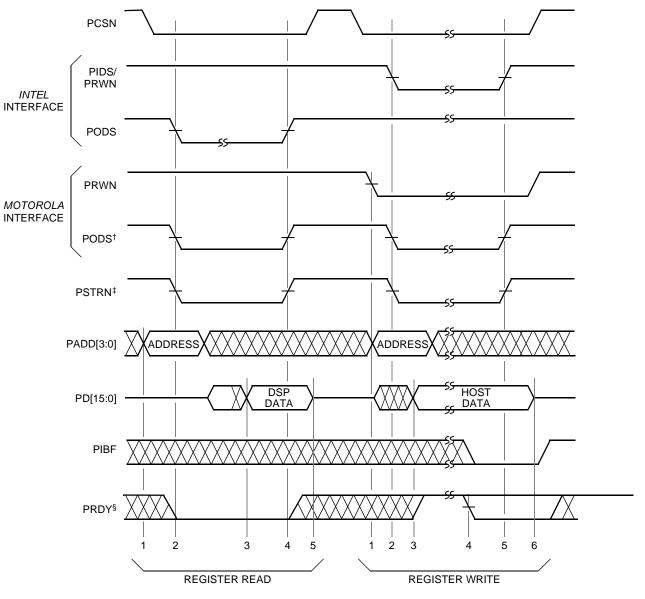

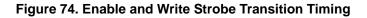

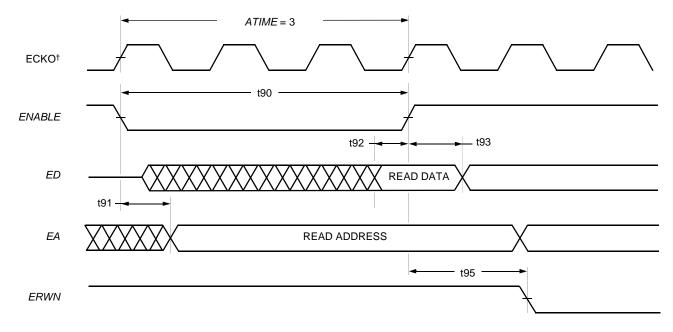

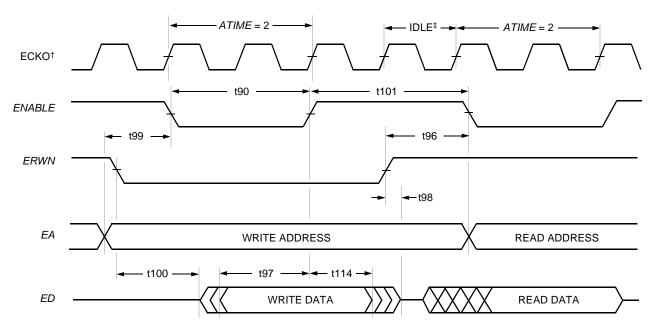

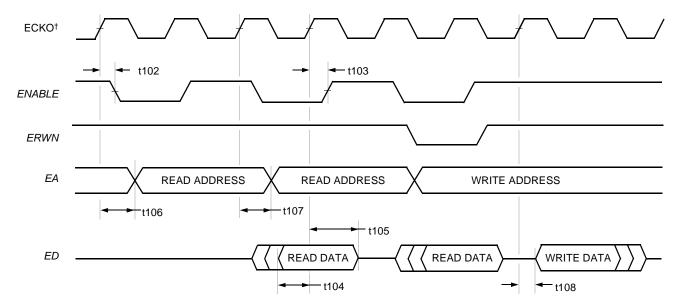

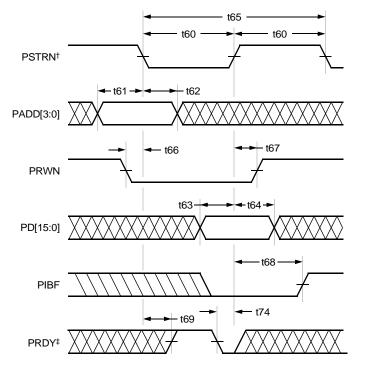

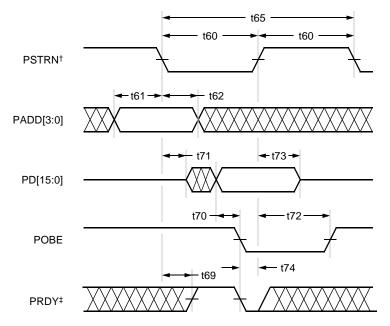

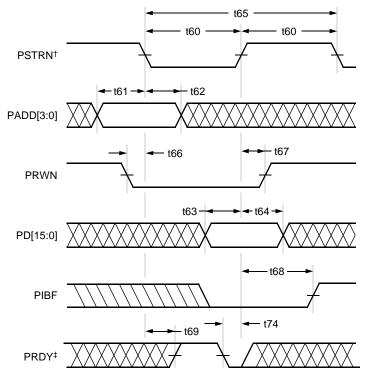

| 4.15.3 Host Data Read and Write Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                          |

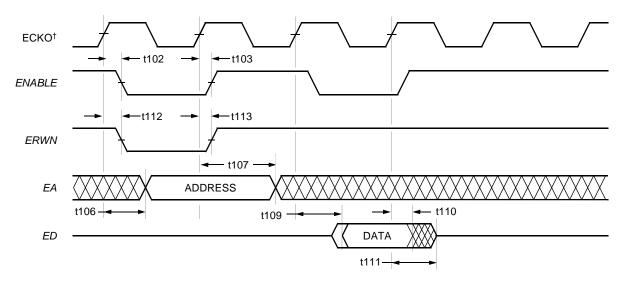

| 4.15.4 Host Register Read and Write Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                          |

| 4.15.5 Host Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                          |

| 4.15.5.1 Status/Control/Address Register Read Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                          |

| 4.15.5.2 Status/Control/Address Register Write Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                          |

| 4.15.5.3 Memory Read Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                          |

| 4.15.5.4 Flow Control for Memory Read Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                          |

| 4.15.5.5 Memory Write Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                          |

| 4.15.5.6 Flow Control for Control/Status/Address Register and Memory Write Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                          |

| 4.15.6 Host Command Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 150                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                          |

| 4.15.6.1 Download of Program or Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                          |

| <ul> <li>4.15.6.1 Download of Program or Data</li> <li>4.15.6.2 Upload of Data</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 150                                                                                                                                      |

| <ul> <li>4.15.6.1 Download of Program or Data</li> <li>4.15.6.2 Upload of Data</li> <li>4.15.7 PIU Interrupts</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 150<br>151                                                                                                                               |

| <ul> <li>4.15.6.1 Download of Program or Data</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 150<br>151<br>152                                                                                                                        |

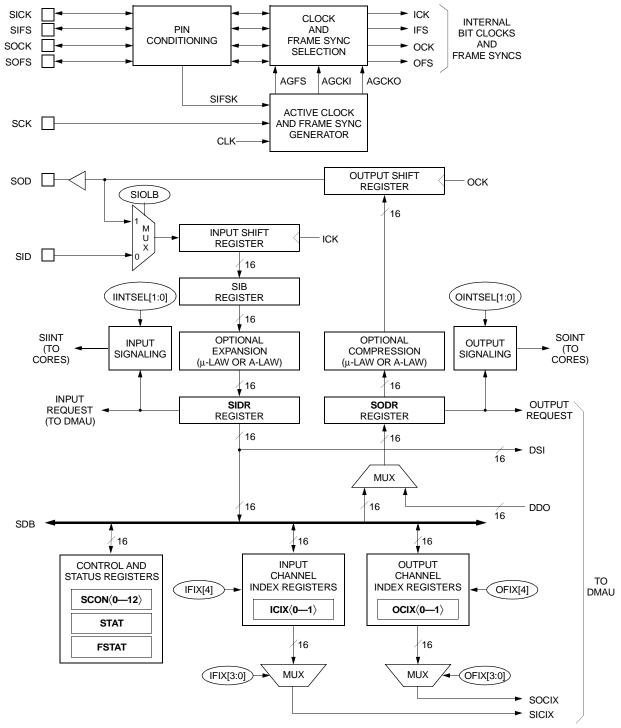

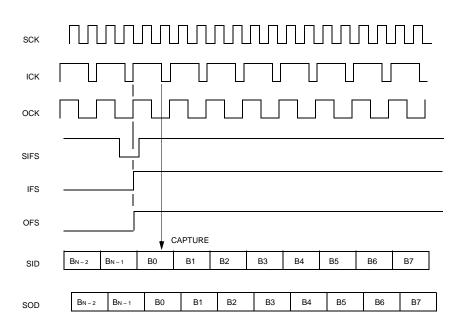

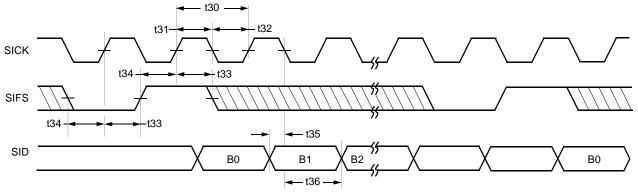

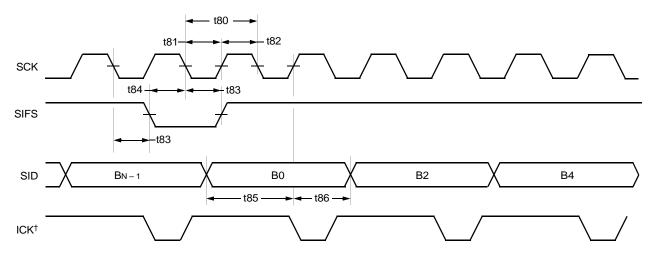

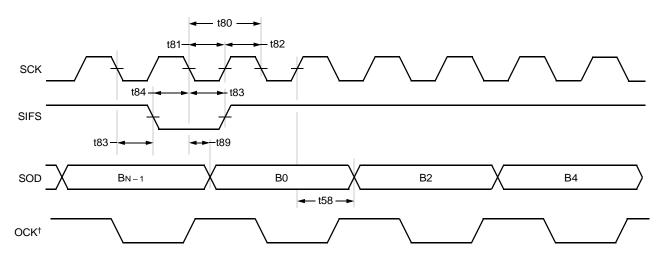

| <ul> <li>4.15.6.1 Download of Program or Data</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 150<br>151<br>152<br>154                                                                                                                 |

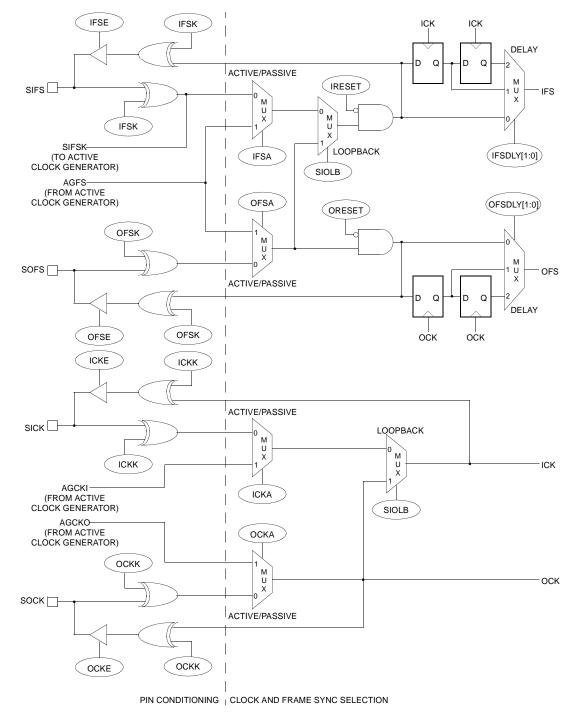

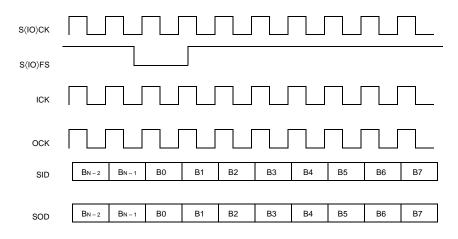

| <ul> <li>4.15.6.1 Download of Program or Data</li> <li>4.15.6.2 Upload of Data</li> <li>4.15.7 PIU Interrupts</li> <li>4.16 Serial Interface Unit (SIU)</li> <li>4.16.1 Hardware Interface</li> <li>4.16.2 Pin Conditioning Logic, Bit Clock Selection Logic, and Frame Sync Selection Logic</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 150<br>151<br>152<br>154<br>155                                                                                                          |

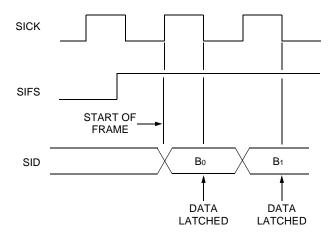

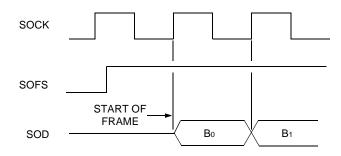

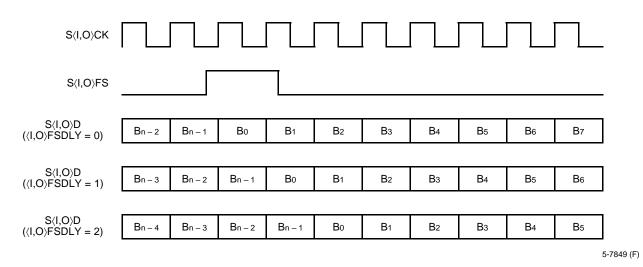

| <ul> <li>4.15.6.1 Download of Program or Data</li> <li>4.15.6.2 Upload of Data</li> <li>4.15.7 PIU Interrupts</li> <li>4.16 Serial Interface Unit (SIU)</li> <li>4.16.1 Hardware Interface</li> <li>4.16.2 Pin Conditioning Logic, Bit Clock Selection Logic, and Frame Sync Selection Logic</li> <li>4.16.3 Basic Input Processing</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 150<br>151<br>152<br>154<br>155<br>157                                                                                                   |

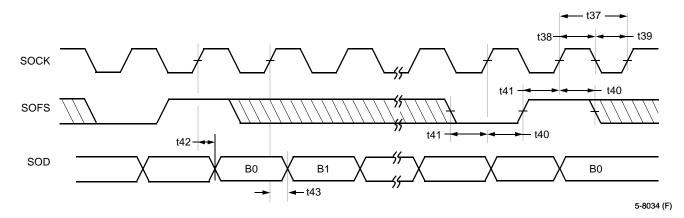

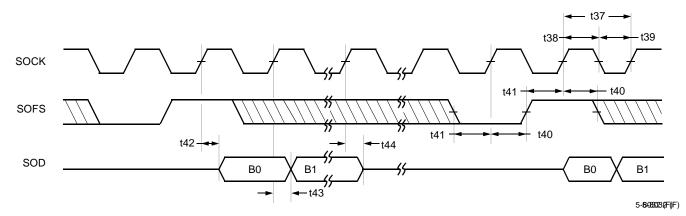

| <ul> <li>4.15.6.1 Download of Program or Data</li> <li>4.15.6.2 Upload of Data</li> <li>4.15.7 PIU Interrupts</li> <li>4.16 Serial Interface Unit (SIU)</li> <li>4.16.1 Hardware Interface</li> <li>4.16.2 Pin Conditioning Logic, Bit Clock Selection Logic, and Frame Sync Selection Logic</li> <li>4.16.3 Basic Input Processing</li> <li>4.16.4 Basic Output Processing</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 150<br>151<br>152<br>154<br>155<br>157<br>158                                                                                            |

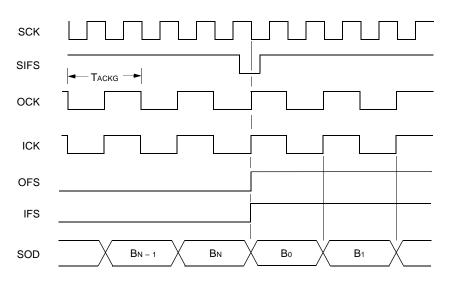

| <ul> <li>4.15.6.1 Download of Program or Data</li> <li>4.15.6.2 Upload of Data</li> <li>4.15.7 PIU Interrupts</li> <li>4.16 Serial Interface Unit (SIU)</li> <li>4.16.1 Hardware Interface</li> <li>4.16.2 Pin Conditioning Logic, Bit Clock Selection Logic, and Frame Sync Selection Logic</li> <li>4.16.3 Basic Input Processing</li> <li>4.16.4 Basic Output Processing</li> <li>4.16.5 Clock and Frame Sync Generation</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 150<br>151<br>152<br>154<br>155<br>157<br>158<br>159                                                                                     |

| <ul> <li>4.15.6.1 Download of Program or Data</li> <li>4.15.6.2 Upload of Data</li> <li>4.15.7 PIU Interrupts</li> <li>4.16 Serial Interface Unit (SIU)</li> <li>4.16.1 Hardware Interface</li> <li>4.16.2 Pin Conditioning Logic, Bit Clock Selection Logic, and Frame Sync Selection Logic</li> <li>4.16.3 Basic Input Processing</li> <li>4.16.4 Basic Output Processing</li> <li>4.16.5 Clock and Frame Sync Generation</li> <li>4.16.6 ST-Bus Timing Examples</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 150<br>151<br>152<br>154<br>155<br>157<br>158<br>159<br>164                                                                              |

| <ul> <li>4.15.6.1 Download of Program or Data</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 150<br>151<br>152<br>154<br>155<br>157<br>158<br>159<br>164<br>166                                                                       |

| <ul> <li>4.15.6.1 Download of Program or Data</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 150<br>151<br>152<br>154<br>155<br>157<br>158<br>159<br>164<br>166<br>166                                                                |

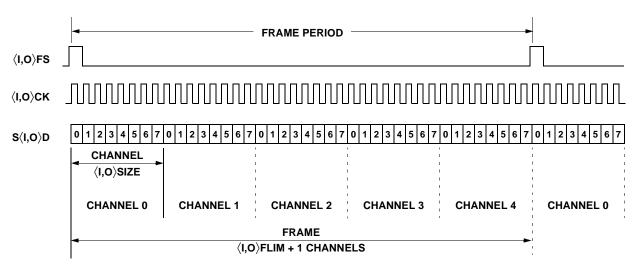

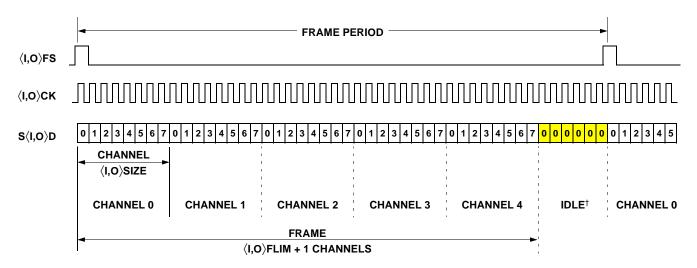

| <ul> <li>4.15.6.1 Download of Program or Data</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 150<br>151<br>152<br>154<br>155<br>157<br>158<br>159<br>164<br>166<br>166                                                                |

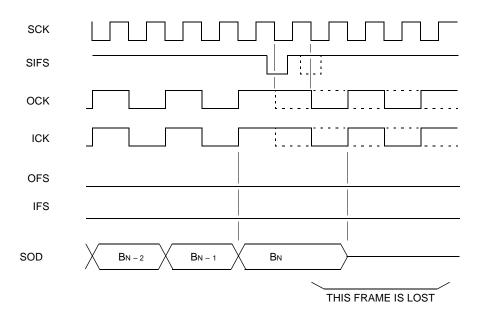

| <ul> <li>4.15.6.1 Download of Program or Data</li> <li>4.15.6.2 Upload of Data</li> <li>4.15.7 PIU Interrupts</li> <li>4.16 Serial Interface Unit (SIU)</li> <li>4.16.1 Hardware Interface</li> <li>4.16.2 Pin Conditioning Logic, Bit Clock Selection Logic, and Frame Sync Selection Logic</li> <li>4.16.3 Basic Input Processing</li> <li>4.16.4 Basic Output Processing</li> <li>4.16.5 Clock and Frame Sync Generation</li> <li>4.16.6 ST-Bus Timing Examples</li> <li>4.16.7 SIU Loopback</li> <li>4.16.8 Basic Frame Structure</li> <li>4.16.9 Assigning SIU Logical Channels to DMAU Channels</li> <li>4.16.10 Frame Error Detection and Reporting</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 150<br>151<br>152<br>154<br>155<br>157<br>158<br>159<br>164<br>166<br>166<br>167<br>168                                                  |

| <ul> <li>4.15.6.1 Download of Program or Data</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 150<br>151<br>152<br>154<br>155<br>157<br>158<br>159<br>164<br>166<br>166<br>167<br>168<br>168                                           |

| <ul> <li>4.15.6.1 Download of Program or Data</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 150<br>151<br>152<br>154<br>155<br>157<br>158<br>159<br>164<br>166<br>166<br>167<br>168<br>168<br>169                                    |

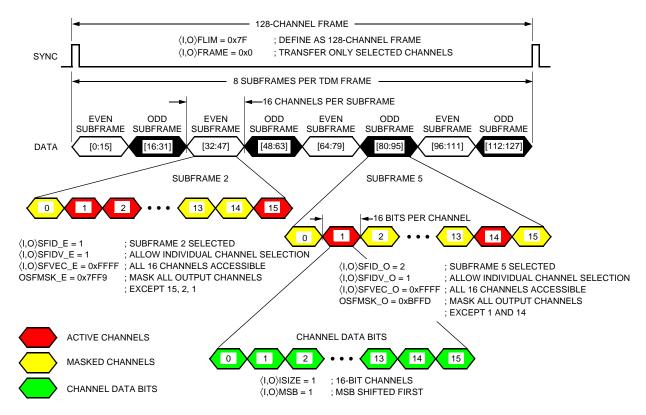

| <ul> <li>4.15.6.1 Download of Program or Data</li> <li>4.15.6.2 Upload of Data</li> <li>4.15.7 PIU Interrupts</li> <li>4.16 Serial Interface Unit (SIU)</li> <li>4.16.1 Hardware Interface</li> <li>4.16.2 Pin Conditioning Logic, Bit Clock Selection Logic, and Frame Sync Selection Logic</li> <li>4.16.3 Basic Input Processing</li> <li>4.16.4 Basic Output Processing</li> <li>4.16.5 Clock and Frame Sync Generation</li> <li>4.16.6 ST-Bus Timing Examples</li> <li>4.16.7 SIU Loopback</li> <li>4.16.8 Basic Frame Structure</li> <li>4.16.9 Assigning SIU Logical Channels to DMAU Channels</li> <li>4.16.10 Frame Error Detection and Reporting</li> <li>4.16.11 Frame Mode</li> <li>4.16.12 Channel Mode—Up to 128 Channels in a Maximum of Eight Subframes</li> </ul>                                                                                                                                                                                                                                                                                                                                                              | 150<br>151<br>152<br>154<br>155<br>157<br>158<br>159<br>164<br>166<br>166<br>167<br>168<br>168<br>169<br>175                             |

| <ul> <li>4.15.6.1 Download of Program or Data</li> <li>4.15.6.2 Upload of Data</li> <li>4.15.7 PIU Interrupts</li> <li>4.16 Serial Interface Unit (SIU)</li> <li>4.16.1 Hardware Interface</li> <li>4.16.2 Pin Conditioning Logic, Bit Clock Selection Logic, and Frame Sync Selection Logic</li> <li>4.16.3 Basic Input Processing</li> <li>4.16.4 Basic Output Processing</li> <li>4.16.5 Clock and Frame Sync Generation</li> <li>4.16.6 ST-Bus Timing Examples</li> <li>4.16.7 SIU Loopback</li> <li>4.16.8 Basic Frame Structure</li> <li>4.16.9 Assigning SIU Logical Channels to DMAU Channels</li> <li>4.16.10 Frame Error Detection and Reporting</li> <li>4.16.11 Frame Mode</li> <li>4.16.12 Channel Mode—32 Channels or Less in Two Subframes or Less</li> <li>4.16.13 Channel Mode—Up to 128 Channels in a Maximum of Eight Subframes</li> <li>4.16.14 SIU Examples</li> </ul>                                                                                                                                                                                                                                                     | 150<br>151<br>152<br>154<br>155<br>157<br>158<br>159<br>164<br>166<br>167<br>168<br>168<br>169<br>175<br>178                             |

| <ul> <li>4.15.6.1 Download of Program or Data</li> <li>4.15.6.2 Upload of Data</li> <li>4.15.7 PIU Interrupts</li> <li>4.16 Serial Interface Unit (SIU)</li> <li>4.16.1 Hardware Interface</li> <li>4.16.2 Pin Conditioning Logic, Bit Clock Selection Logic, and Frame Sync Selection Logic</li> <li>4.16.3 Basic Input Processing</li> <li>4.16.4 Basic Output Processing</li> <li>4.16.5 Clock and Frame Sync Generation</li> <li>4.16.6 ST-Bus Timing Examples</li> <li>4.16.7 SIU Loopback</li> <li>4.16.9 Assigning SIU Logical Channels to DMAU Channels</li> <li>4.16.10 Frame Error Detection and Reporting</li> <li>4.16.11 Frame Mode</li> <li>4.16.12 Channel Mode—32 Channels or Less in Two Subframes or Less</li> <li>4.16.14 SIU Examples</li> <li>4.16.14 Single-Channel I/O.</li> </ul>                                                                                                                                                                                                                                                                                                                                       | 150<br>151<br>152<br>154<br>155<br>157<br>158<br>159<br>164<br>166<br>167<br>168<br>168<br>169<br>175<br>178<br>178                      |

| <ul> <li>4.15.6.1 Download of Program or Data</li> <li>4.15.6.2 Upload of Data</li> <li>4.15.7 PIU Interrupts</li> <li>4.16 Serial Interface Unit (SIU)</li> <li>4.16.1 Hardware Interface</li> <li>4.16.2 Pin Conditioning Logic, Bit Clock Selection Logic, and Frame Sync Selection Logic.</li> <li>4.16.3 Basic Input Processing</li> <li>4.16.4 Basic Output Processing.</li> <li>4.16.5 Clock and Frame Sync Generation</li> <li>4.16.5 T-Bus Timing Examples</li> <li>4.16.7 SIU Loopback</li> <li>4.16.9 Assigning SIU Logical Channels to DMAU Channels</li> <li>4.16.10 Frame Error Detection and Reporting.</li> <li>4.16.11 Frame Mode</li> <li>4.16.12 Channel Mode—Up to 128 Channels in a Maximum of Eight Subframes</li> <li>4.16.14.1 Single-Channel I/O.</li> <li>4.16.14.2 ST-Bus Interface</li> </ul>                                                                                                                                                                                                                                                                                                                       | 150<br>151<br>152<br>154<br>155<br>157<br>158<br>159<br>164<br>166<br>167<br>168<br>168<br>168<br>169<br>175<br>178<br>178<br>178        |

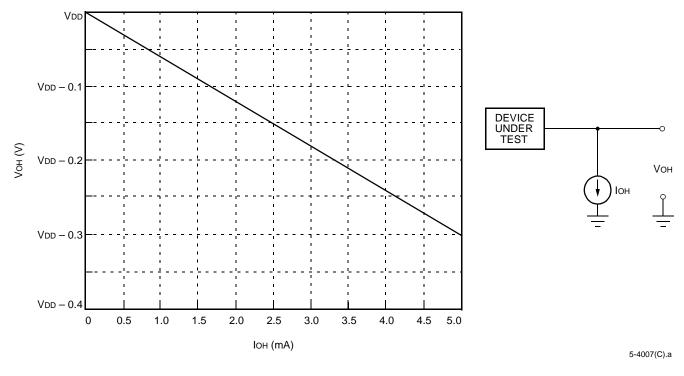

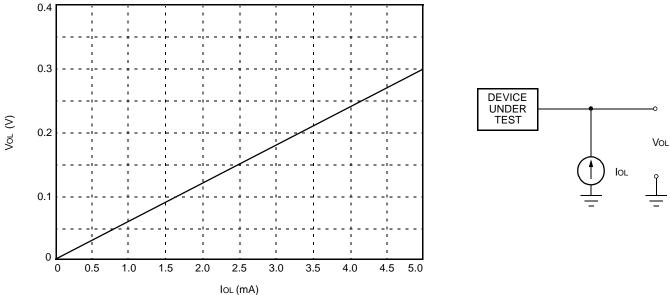

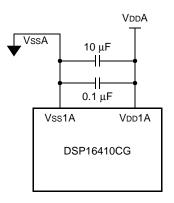

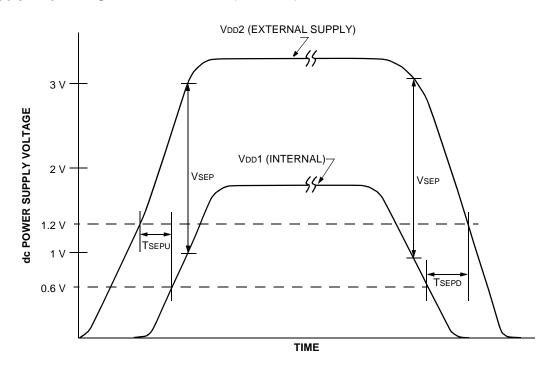

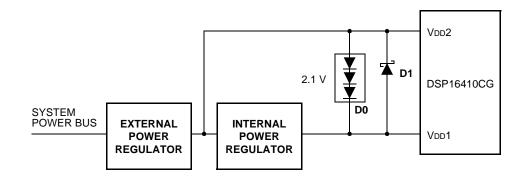

| <ul> <li>4.15.6.1 Download of Program or Data</li> <li>4.15.6.2 Upload of Data</li> <li>4.15.7 PIU Interrupts.</li> <li>4.16 Serial Interface Unit (SIU)</li> <li>4.16.1 Hardware Interface</li> <li>4.16.2 Pin Conditioning Logic, Bit Clock Selection Logic, and Frame Sync Selection Logic.</li> <li>4.16.3 Basic Input Processing.</li> <li>4.16.4 Basic Output Processing.</li> <li>4.16.5 Clock and Frame Sync Generation.</li> <li>4.16.6 ST-Bus Timing Examples.</li> <li>4.16.7 SIU Loopback</li> <li>4.16.9 Assigning SIU Logical Channels to DMAU Channels.</li> <li>4.16.9 Assigning SIU Logical Channels to DMAU Channels.</li> <li>4.16.10 Frame Error Detection and Reporting.</li> <li>4.16.12 Channel Mode—Up to 128 Channels in a Maximum of Eight Subframes.</li> <li>4.16.14 SIU Examples.</li> <li>4.16.14.1 Single-Channel I/O.</li> <li>4.16.15 Registers.</li> </ul>                                                                                                                                                                                                                                                    | 150<br>151<br>152<br>154<br>155<br>157<br>158<br>159<br>164<br>166<br>167<br>168<br>168<br>169<br>175<br>178<br>178<br>179<br>182        |