# **RFMA5880-0.5W-Q7**

5.8 – 8.0 GHz High Gain Surface-Mounted PA

#### UPDATED: 04/24/2008

### FEATURES

- 5.8 8.0GHz Operating Frequency Range

- 27.0dBm Output Power @1dB Compression

- 34.0dB Typical Power Gain @1dB Compression

- -41dBc OIMD3 @Pout 17dBm/tone

- 7X7mm QFN Package •

### **APPLICATIONS**

- Point-to-point and point-to-multipoint radio

- Military Radar Systems

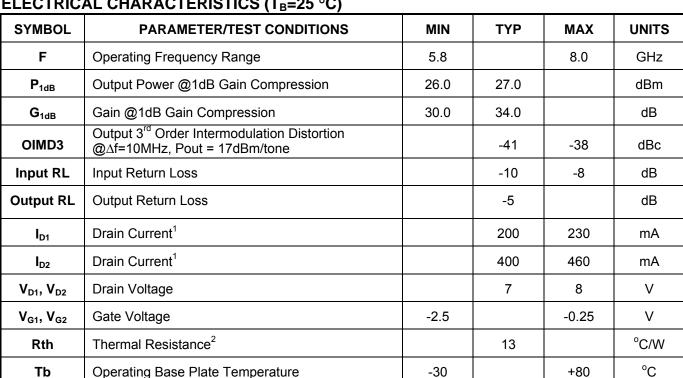

# ELECTRICAL CHARACTERISTICS (T<sub>B</sub>=25 °C)

1. Recommended to bias each amplifier stage separately using a gate voltage range, starting from -2.5 to -0.3V to achieve typical current levels. 2. Rth is mounting dependent. Measured result when used with Excelics recommended evaluation board.

### MAXIMUM RATINGS AT 25°C<sup>3,4</sup>

| SYMBOL                            | CHARACTERISTIC          | ABSOLUTE  | CONTINOUS         |

|-----------------------------------|-------------------------|-----------|-------------------|

| $V_{D1}, V_{D2}$                  | Drain to Source Voltage | 12V       | 8 V               |

| $V_{G1}, V_{G2}$                  | Gate to Source Voltage  | -5V       | -2.5 V            |

| I <sub>D1</sub> , I <sub>D2</sub> | Drain Current           | ldss      | 230, 460mA        |

| P <sub>IN</sub>                   | Input Power             | 20dBm     | @ 3dB compression |

| Т <sub>СН</sub>                   | Channel Temperature     | 175°C     | 150°C             |

| T <sub>STG</sub>                  | Storage Temperature     | -65/175°C | -65/150°C         |

| PT                                | Total Power Dissipation | 8.8W      | 7.4W              |

3. Operation beyond absolute or continuous ratings may result in permanent damage or reduction of MTTF respectively.

4. Bias conditions must also satisfy the following equation  $V_{DS}*I_{DS} < (T_{CH} - T_B)/R_{TH}$ ; where  $T_B$  = Temperature of Base Plate

Specifications are subject to change without notice. Excelics Semiconductor, Inc. 310 De Guigne Drive, Sunnyvale, CA 94085 Phone: 408-737-1711 Fax: 408-737-1868 Web: www.excelics.com

page 1 of 3 Revised May 2008

# RFMA5880-0.5W-Q7

# 5.8 – 8.0 GHz High Gain Surface-Mounted PA

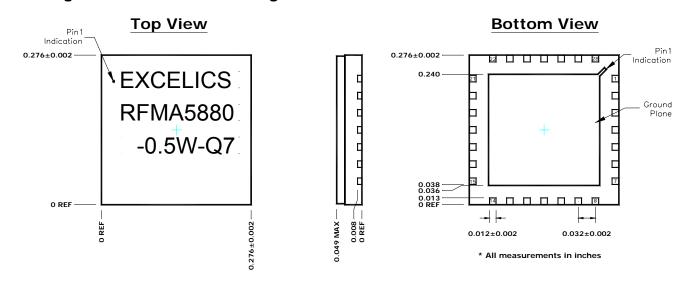

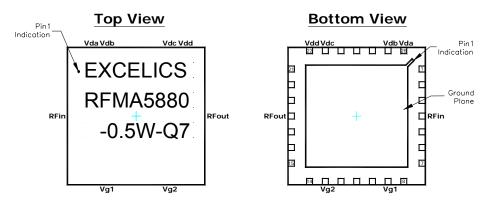

# Package Dimension and Pin Assignment

UPDATED: 04/24/2008

#### Additional Notes:

- 1) Ground Plane must be soldered to PCB RF ground

- 2) All dimensions are in inches

- 3) Refer to Excelics application notes on QFNs for further guidelines

- 4) Pin Assignment:

| Pin                                        | Assignment                        |

|--------------------------------------------|-----------------------------------|

| 1, 2, 3, 5, 6, 7, 8, 10, 11, 12, 14        | NC                                |

| 4                                          | RF <sub>in</sub>                  |

| 9                                          | V <sub>q1</sub>                   |

| 13                                         | V <sub>g2</sub>                   |

| 15, 16, 17, 19, 20, 21, 22, 24, 25, 26, 28 | NC                                |

| 18                                         | RF <sub>out</sub>                 |

| 22, 23                                     | V <sub>dd</sub> , V <sub>dc</sub> |

| 27, 28                                     | V <sub>db</sub> , V <sub>da</sub> |

Specifications are subject to change without notice. Excelics Semiconductor, Inc. 310 De Guigne Drive, Sunnyvale, CA 94085 Phone: 408-737-1711 Fax: 408-737-1868 Web: www.excelics.com

page 2 of 3 Revised May 2008

# RFMA5880-0.5W-Q7

UPDATED: 04/24/2008

# 5.8 – 8.0 GHz High Gain Surface-Mounted PA

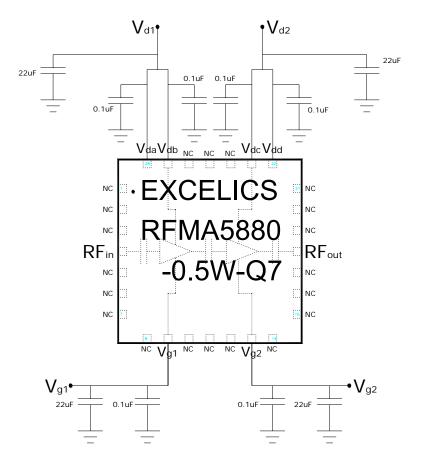

# **Recommended Circuit Schematic:**

Notes:

- 1) External bypass capacitors should be placed as close to the package as possible.

- 2) Dual biasing sequence required:

- a. Turn-on Sequence: Apply  $V_{g1} = -2.5V$ ,  $V_{g2} = -2.5V$ , followed by  $V_{d1} = V_{d2} = 7V$ , lastly increase  $V_{g1} \& V_{g2}$  in sequence until required  $I_{d1}$  and  $I_{d2}$  is obtained.

- b. Turn-off Sequence: Turn off  $V_{d1}$  &  $V_{d2}$ , followed by  $V_{g1}$  &  $V_{g2}$

- 3) Demonstration board available upon request.

page 3 of 3 Revised May 2008