# 16-Bit, 80/100 MSPS, A/D Converter

# **Preliminary Technical Data**

# AD9446

### FEATURES

100 MSPS guaranteed sampling rate 100 dB two-tone SFDR with 30 MHz and 31 MHz 81.6 dB SNR with 30 MHz input (3.2 V p-p input, 80Msps) 90 dBc SFDR with30 MHz input (3.2 V p-p input, 80Msps) Excellent linearity DNL = ±0.5 LSB typical INL = ±3.0 LSB typical 2.3 W power dissipation 3.3 V and 5 V supply operation 2.0 V p-p to 3.2 V p-p differential full-scale input LVDS outputs (ANSI-644 compatible) or CMOS outputs Data format select (offset binary or twos compliment)

APPLICATIONS

**Output clock available**

Multicarrier, multimode cellular receivers Antenna array positioning Power amplifier linearization Broadband wireless Radar Infrared imaging Communications instrumentation

## **GENERAL DESCRIPTION**

The AD9446 is a 16-bit monolithic, sampling analog-to-digital converter (ADC) with an on-chip track-and-hold circuit. It is optimized for power, small size, and ease of use. The product operates at up to a 100 MSPS conversion rate and is optimized for multicarrier, multimode receivers, such as those found in cellular infrastructure equipment.

The ADC requires 3.3 V and 5.0 V power supplies and a low voltage differential input clock for full performance operation. No external reference or driver components are required for many applications. Data outputs are LVDS-compatible (ANSI-644) or CMOS-compatible and include the means to reduce the overall current needed for short trace distances.

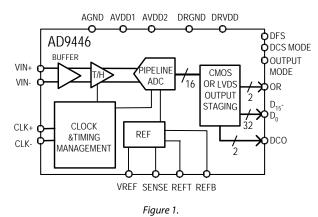

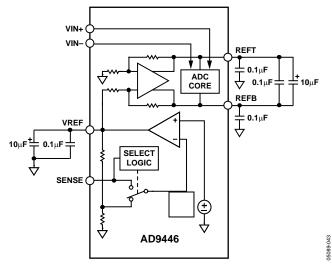

# FUNCTIONAL BLOCK DIAGRAM

Optional features allow users to implement various selectable operating conditions, including data format select and output data mode.

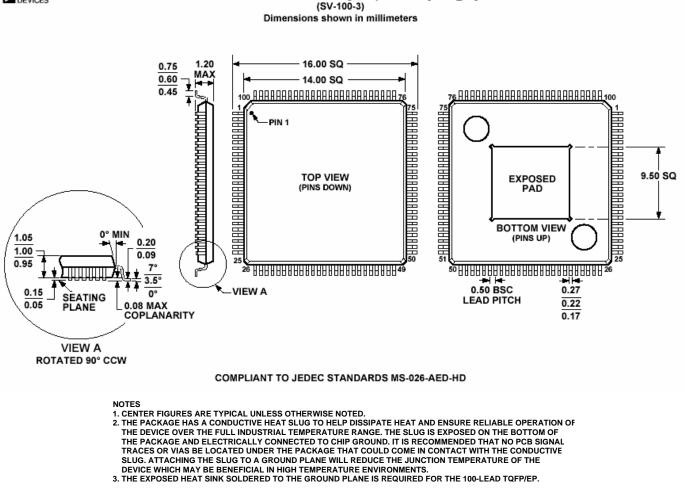

The AD9446 is available in a 100-lead surface-mount plastic package (100-lead TQFP/EP) specified over the industrial temperature range  $-40^{\circ}$ C to  $+85^{\circ}$ C.

# **PRODUCT HIGHLIGHTS**

- 1. True 16 bit linearity.

- 2. High performance: outstanding SFDR performance for multicarrier, multimode 3G and 4G cellular base station receivers.

- 3. Ease of use: on-chip reference and track-and-hold. An output clock simplifies data capture.

- 4. Packaged in a Pb-free, 100-lead TQFP/EP.

- 5. Clock duty cycle stabilizer (DCS) maintains overall ADC performance over a wide range of clock pulse widths.

- 6. OR (out-of-range) outputs indicate when the signal is beyond the selected input range.

#### Rev. PrF

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

© 2005 Analog Devices, Inc. All rights reserved.

# TABLE OF CONTENTS

| DC Specifications                              |

|------------------------------------------------|

| AC Specifications                              |

| Digital Specifications                         |

| Switching Specifications7                      |

| Explanation of Test Levels                     |

| Absolute Maximum Ratings                       |

| Thermal Resistance                             |

| ESD Caution9                                   |

| Definitions of Specifications10                |

| Pin Configurations and Function Descriptions11 |

| Equivalent Circuits                            |

### **REVISION HISTORY**

5/05—PrF: Preliminary Version

| Typical Performance Characteristics 17 |

|----------------------------------------|

| Theory of Operation18                  |

| Analog Input and Reference Overview 18 |

| Clock Input Considerations             |

| Power Considerations                   |

| Digital Outputs                        |

| Timing                                 |

| Operational Mode Selection             |

| Evaluation Board 22                    |

| Outline Dimensions                     |

| Ordering Guide                         |

# **DC SPECIFICATIONS**

AVDD1 = 3.3 V, AVDD2 = 5.0 V, DRVDD = 3.3 V, LVDS mode, specified minimum sampling rate, 3.2 V p-p differential input, internal trimmed reference (1.6 V mode),  $A_{IN} = -1.0 dBFS$ , DCS on, unless otherwise noted.

### Table 1.

|                                               |       | Test  |      | AD9446BSVZ | -80  |      | AD9446BSV2 | Z-100 |         |

|-----------------------------------------------|-------|-------|------|------------|------|------|------------|-------|---------|

| Parameter                                     | Temp  | Level | Min  | Тур        | Мах  | Min  | Тур        | Мах   | Unit    |

| RESOLUTION                                    | Full  | VI    |      |            |      |      | 16         |       | Bits    |

| ACCURACY                                      |       |       |      |            |      |      |            |       |         |

| No Missing Codes                              | Full  | VI    |      | Guarantee  | d    |      | Guaranteed |       |         |

| Offset Error                                  | Full  | VI    |      |            |      |      |            |       | mV      |

| Gain Error <sup>1</sup>                       | Full  | VI    |      | ±0.3       |      |      | ±0.3       |       | % FSR   |

| Differential Nonlinearity (DNL) <sup>2</sup>  | Full  | VI    |      | ±0.5       |      |      | ±0.5       |       | LSB     |

| Integral Nonlinearity (INL) <sup>2</sup>      | 25°C  | I.    |      | ±3.0       |      |      | ±3.0       |       | LSB     |

|                                               | Full  | VI    |      |            |      |      | 1.5        |       | LSB     |

| TEMPERATURE DRIFT                             |       |       |      |            |      |      |            |       |         |

| Offset Error                                  | Full  | V     |      |            |      |      |            |       | μV/°C   |

| Gain Error                                    | Full  | v     |      |            |      |      |            |       | %FS/°C  |

| VOLTAGE REFERENCE                             |       | 1     | 1    |            |      |      |            |       |         |

| Output Voltage <sup>1</sup> (VREF = $1.6 V$ ) | Full  | VI    |      | 1.6        |      |      | 1.6        |       | v       |

| (VREF = 1.0 V)                                | Full  | VI    |      | 1.0        |      |      | 1.0        |       | v       |

| Load Regulation @ 1.0 mA                      | Full  | v     |      | ±2         |      |      | ±2         |       | mV      |

| Reference Input Current                       | Full  | VI    |      |            |      |      |            |       | μA      |

| (External 1.6 V Reference)                    |       |       |      |            |      |      |            |       | T.,     |

| INPUT REFERRED NOISE                          | 25°C  | V     |      | 2.50       |      |      | 2.75       |       | LSB rms |

| ANALOG INPUT                                  |       |       |      |            |      |      |            |       |         |

| Input Span (VREF = 1.6 V)                     | Full  | v     |      | 3.2        |      |      | 3.2        |       | V р-р   |

| (VREF = 1.0 V)                                | Full  | v     |      | 2.0        |      |      | 2.0        |       | V p-p   |

| Input Common-Mode Voltage                     | Full  | v     |      | 3.5        |      |      | 3.5        |       | v       |

| Input Resistance <sup>3</sup>                 | Full  | v     |      | 1          |      |      | 1          |       | kΩ      |

| Input Capacitance <sup>3</sup>                | Full  | v     |      | 2.5        |      |      | 2.5        |       | pF      |

| POWER SUPPLIES                                |       |       |      |            |      |      |            |       |         |

| Supply Voltage                                |       |       |      |            |      |      |            |       |         |

| AVDD1                                         | Full  | IV    | 3.14 | 3.3        | 3.46 | 3.14 | 3.3        | 3.46  | v       |

| AVDD2                                         | Full  | IV    | 4.75 | 5.0        | 5.25 | 4.75 | 5.0        | 5.25  | v       |

| DRVDD—LVDS Outputs                            | Full  | IV    | 3.0  |            | 3.6  | 3.0  |            | 3.6   | V       |

| DRVDD—CMOS Outputs                            | Full  | IV    | 3.0  | 3.3        | 3.6  | 3.0  | 3.3        | 3.6   | V       |

| Supply Current                                |       |       |      |            |      |      |            |       |         |

| AVDD1                                         | Full  | VI    |      | 338        |      |      | 366        |       | mA      |

| AVDD2 <sup>2</sup>                            | Full  | VI    |      | 209        |      |      | 220        |       | mA      |

| IDRVDD <sup>2</sup> —LVDS Outputs             | Full  | VI    |      | 65         |      |      | 65         |       | mA      |

| IDRVDD <sup>2</sup> —CMOS Outputs             | Full  | V     |      | 14         |      |      | 14         |       | mA      |

| PSRR                                          |       |       |      |            |      |      |            |       |         |

| Offset                                        | Full  | v     |      | 1          |      |      | 1          |       | mV/V    |

| Gain                                          | Full  | v     |      | 0.2        |      |      | 0.2        |       | %/V     |

| POWER CONSUMPTION                             | 1 011 | · ·   |      |            |      |      | 0.2        |       | 707 V   |

| DC Input—LVDS Outputs                         | Full  | VI    |      | 2.3        |      |      | 2.5        |       | w       |

| DC Input—CMOS Outputs                         | Full  | V     |      | 2.5        |      |      | 2.3        |       | W       |

<sup>1</sup> The internal voltage reference is trimmed at final test to minimize the gain error of the AD9446.

<sup>2</sup> Measured at the maximum clock rate,  $f_{IN} = 15$  MHz, full-scale sine wave, with a 100  $\Omega$  differential termination on each pair of output bits for LVDS output mode and approximately 5 pF loading on each output bit for CMOS output mode.

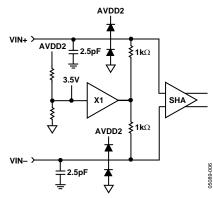

<sup>3</sup> Input capacitance or resistance refers to the effective impedance between one differential input pin and AGND. Refer to Figure 6 for the equivalent analog input structure.

# AC SPECIFICATIONS

AVDD1 = 3.3 V, AVDD2 = 5.0 V, DRVDD = 3.3 V, LVDS mode, specified minimum sample rate, 3.2 V p-p differential input, internal trimmed reference (1.6 V mode),  $A_{IN} = -1 dBFS$ , DCS on, unless otherwise noted.

### Table 2.

|                                                         |      | Test  | AD9446BS | AD9446BSVZ-100 |     |      |     |      |

|---------------------------------------------------------|------|-------|----------|----------------|-----|------|-----|------|

| Parameter                                               | Temp | Level | Min Typ  | Мах            | Min | Тур  | Max | Unit |

| SIGNAL-TO-NOISE RATIO (SNR)                             |      |       |          |                |     |      |     |      |

| $f_{IN} = 10 \text{ MHz}$                               | 25°C | IV    | 81.9     |                |     | 79.6 |     | dB   |

|                                                         | Full | IV    |          |                |     |      |     | dB   |

| f <sub>IN</sub> = 10 MHz (2 V p-p Input)                | 25°C | IV    | 77.5     |                |     | 76   |     | dB   |

|                                                         | Full | IV    |          |                |     |      |     | dB   |

| $f_{IN} = 35 \text{ MHz}$                               | 25°C | 1     | 81.6     |                |     | 79.5 |     | dB   |

|                                                         | Full | IV    |          |                |     |      |     | dB   |

| $f_{IN} = 70 \text{ MHz}$                               | 25°C | IV    | 80.3     |                |     | 79.0 |     | dB   |

|                                                         | Full | IV    |          |                |     |      |     | dB   |

| $f_{IN} = 100 \text{ MHz}$                              | 25°C | V     | 78.5     |                |     | 78.6 |     | dB   |

| SIGNAL-TO-NOISE AND DISTORTION                          |      |       |          |                |     |      |     |      |

| $f_{\rm IN} = 10  \rm MHz$                              | 25°C | IV    | 80.9     |                |     | 78.9 |     | dB   |

|                                                         | Full | IV    |          |                |     | ,    |     | dB   |

| f <sub>™</sub> = 10 MHz (2 V p-p Input)                 | 25°C | IV    | 77.3     |                |     | 75.5 |     | dB   |

|                                                         | Full | IV    | ,,,,,,   |                |     | 75.5 |     | dB   |

| f <sub>iℕ</sub> = 35 MHz                                | 25°C | 1     | 80.7     |                |     | 78.5 |     | dB   |

|                                                         | Full | IV    | 00.7     |                |     | 70.5 |     | dB   |

| f <sub>iℕ</sub> = 70 MHz                                | 25°C | IV    | 78.7     |                |     | 77.2 |     | dB   |

| IIN = 70 IVII IZ                                        | Full | IV    | 70.7     |                |     | //.2 |     | dB   |

| $f_{IN} = 100 \text{ MHz}$                              | 25°C | V     | 78.0     |                |     | 76.6 |     | dB   |

| EFFECTIVE NUMBER OF BITS (ENOB)                         | 25 C | v     | 70.0     |                |     | 70.0 |     | ub   |

| $f_{\rm IN} = 10 \rm MHz$                               | 25°C | v     | 13.2     |                |     | 13.0 |     | Bits |

| $f_{\rm IN} = 35 \rm MHz$                               | 25°C | v     | 13.2     |                |     | 12.9 |     | Bits |

| $f_{\rm IN} = 70 \rm MHz$                               | 25°C | v     | 13.1     |                |     | 12.9 |     | Bits |

| $f_{\rm IN} = 100 \rm MHz$                              | 25°C | v     | 12.7     |                |     | 12.7 |     | Bits |

| SPURIOUS-FREE DYNAMIC RANGE (SFDR)                      | 25 C | v     | 12.7     |                |     | 12.0 |     | Dits |

| $f_{\rm IN} = 10 \rm MHz$                               | 25°C | IV    | 90       |                |     | 90   |     | dBc  |

| $\Pi_{\rm N} = 10$ MHz                                  | Full | IV    | 90       |                |     | 90   |     | dBc  |

| f <sub>iℕ</sub> = 10 MHz (2 V p-p)                      | 25°C | IV    | 90       |                |     | 90   |     | dBc  |

| $I_{\rm IN} = 10 \text{ MHz} (2 \text{ V} \text{ p-p})$ | Full | IV    | 90       |                |     | 90   |     | dBc  |

| f <sub>IN</sub> = 35 MHz                                | 25°C |       | 00       |                |     | 00   |     |      |

| $I_{\rm IN} = 35 \rm MHz$                               |      |       | 90       |                |     | 88   |     | dBc  |

| ( <u>70</u> MU                                          | Full | IV    | 00       |                |     | 0.4  |     | dBc  |

| $f_{IN} = 70 \text{ MHz}$                               | 25°C | IV    | 83       |                |     | 84   |     | dBc  |

| ( 100 MU                                                | Full | IV    |          |                |     | 00   |     | dBc  |

|                                                         | 25°C | V     | 82       |                | -   | 82   |     | dBc  |

| WORST HARMONIC, SECOND OR THIRD                         | 2505 | n /   |          |                |     |      |     | 10   |

| $f_{IN} = 10 \text{ MHz}$                               | 25°C | IV    | -90      |                |     | -90  |     | dBc  |

|                                                         | Full | IV    |          |                |     |      |     | dBc  |

| f <sub>IN</sub> = 10 MHz (2 V p-p)                      | 25°C | IV    | -90      |                |     | -90  |     | dBc  |

|                                                         | Full | IV    |          |                |     |      |     | dBc  |

| $f_{IN} = 35 \text{ MHz}$                               | 25°C | I     | -90      |                |     | -89  |     | dBc  |

|                                                         | Full | IV    |          |                |     |      |     | dBc  |

| $f_{IN} = 70 \text{ MHz}$                               | 25°C | IV    | -83      |                |     | -84  |     | dBc  |

|                                                         | Full | IV    |          |                |     |      |     | dBc  |

| $f_{IN} = 100 \text{ MHz}$                              | 25°C | V     | -82      |                |     | -82  |     | dBc  |

# Preliminary Technical Data

# AD9446

|                                                             |      | Test  | Α   | D9446BS\ | /Z-80 | A   | 09446BSV | Z-100 |      |

|-------------------------------------------------------------|------|-------|-----|----------|-------|-----|----------|-------|------|

| Parameter                                                   | Temp | Level | Min | Тур      | Max   | Min | Тур      | Max   | Unit |

| WORST SPUR EXCLUDING SECOND<br>OR THIRD HARMONICS           |      |       |     |          |       |     |          |       |      |

| $f_{IN} = 10 \text{ MHz}$                                   | 25°C | IV    |     | -95      |       |     | -96      |       | dBc  |

|                                                             | Full | IV    |     |          |       |     |          |       | dBc  |

| f <sub>IN</sub> = 10 MHz (2 V р-р)                          | 25°C | IV    |     | -95      |       |     | -95      |       | dBc  |

|                                                             | Full | IV    |     |          |       |     |          |       | dBc  |

| $f_{IN} = 35 \text{ MHz}$                                   | 25°C | 1     |     | -90      |       |     | -95      |       | dBc  |

|                                                             | Full | IV    |     |          |       |     |          |       | dBc  |

| $f_{IN} = 70 \text{ MHz}$                                   | 25°C | IV    |     | -90      |       |     | -95      |       | dBc  |

|                                                             | Full | IV    |     |          |       |     |          |       | dBc  |

| $f_{IN} = 100 \text{ MHz}$                                  | 25°C | V     |     | -85      |       |     | -94      |       | dBc  |

| TWO-TONE SFDR                                               |      |       |     |          |       |     |          |       |      |

| f <sub>IN</sub> = 10.8 MHz @ −7 dBFS,<br>9.8 MHz @ −7 dBFS  | 25°C | V     |     | 95       |       |     | 95       |       | dBFS |

| f <sub>IN</sub> = 70.3 MHz @ −7 dBFS,<br>69.3 MHz @ −7 dBFS | 25°C | V     |     |          |       |     |          |       | dBFS |

| ANALOG BANDWIDTH                                            | Full | V     |     | 325      |       |     | 540      |       | MHz  |

# **DIGITAL SPECIFICATIONS**

AVDD1 = 3.3 V, AVDD2 = 5.0 V, DRVDD = 3.3 V,  $R_{LVDSBIAS}$  = 3.74 k $\Omega$ , unless otherwise noted.

#### Table 3.

|                                                             |      | Test  | AD9   | 446BSV | Z-80  | AD9   | 446BSV | Z-100 |      |

|-------------------------------------------------------------|------|-------|-------|--------|-------|-------|--------|-------|------|

| Parameter                                                   | Temp | Level | Min   | Тур    | Max   | Min   | Тур    | Max   | Unit |

| CMOS LOGIC INPUTS (DFS, DCS MODE, OUTPUT MODE)              |      |       |       |        |       |       |        |       |      |

| High Level Input Voltage                                    | Full | IV    | 2.0   |        |       | 2.0   |        |       | V    |

| Low Level Input Voltage                                     | Full | IV    |       |        | 0.8   |       |        | 0.8   | V    |

| High Level Input Current                                    | Full | VI    |       |        | 200   |       |        | 200   | μΑ   |

| Low Level Input Current                                     | Full | VI    | -10   |        | +10   | -10   |        | +10   | μΑ   |

| Input Capacitance                                           | Full | V     |       | 2      |       |       | 2      |       | рF   |

| DIGITAL OUTPUT BITS—CMOS MODE (D0 to D13, OTR) <sup>1</sup> |      |       |       |        |       |       |        |       |      |

| DRVDD = 3.3 V                                               |      |       |       |        |       |       |        |       |      |

| High Level Output Voltage                                   | Full | IV    | 3.25  |        |       | 3.25  |        |       | V    |

| Low Level Output Voltage                                    | Full | IV    |       |        | 0.2   |       |        | 0.2   | V    |

| DIGITAL OUTPUT BITS—LVDS MODE (D0 to D13, OTR)              |      |       |       |        |       |       |        |       |      |

| Vod Differential Output Voltage <sup>2</sup>                | Full | VI    | 247   |        | 545   | 247   |        | 545   | mV   |

| Vos Output Offset Voltage                                   | Full | VI    | 1.125 |        | 1.375 | 1.125 |        | 1.375 | V    |

| CLOCK INPUTS (CLK+, CLK–)                                   |      |       |       |        |       |       |        |       |      |

| Differential Input Voltage                                  | Full | IV    | 0.2   |        |       | 0.2   |        |       | V    |

| Common-Mode Voltage                                         | Full | VI    | 1.3   | 1.5    | 1.6   | 1.3   | 1.5    | 1.6   | V    |

| Differential Input Resistance                               | Full | V     | 8     | 10     | 12    | 8     | 10     | 12    | kΩ   |

| Differential Input Capacitance                              | Full | V     |       | 4      |       |       | 4      |       | рF   |

$^1$  Output voltage levels measured with 5 pF load on each output.  $^2$  LVDS  $R_{TERM}$  = 100  $\Omega.$

# SWITCHING SPECIFICATIONS

AVDD1 = 3.3 V, AVDD2 = 5.0 V, DRVDD = 3.3 V, unless otherwise noted.

#### Table 4.

|                                                                              |      | Test  | ADS | 446BSV | Z-80 | AD  | 9446BSV | Z-100 | Unit   |

|------------------------------------------------------------------------------|------|-------|-----|--------|------|-----|---------|-------|--------|

| Parameter                                                                    | Temp | Level | Min | Тур    | Max  | Min | Тур     | Max   |        |

| CLOCK INPUT PARAMETERS                                                       |      |       |     |        |      |     |         |       |        |

| Maximum Conversion Rate                                                      | Full | VI    | 100 |        |      | 100 |         |       | MSPS   |

| Minimum Conversion Rate                                                      | Full | V     |     |        | 10   |     |         | 10    | MSPS   |

| CLK Period                                                                   | Full | V     | 9.5 |        |      | 10  |         |       | ns     |

| CLK Pulse Width High <sup>1</sup> (t <sub>CLKH</sub> )                       | Full | V     | 5.0 |        |      | 4.0 |         |       | ns     |

| CLK Pulse Width Low <sup>1</sup> (t <sub>CLKL</sub> )                        | Full | V     | 5.0 |        |      | 4.0 |         |       | ns     |

| DATA OUTPUT PARAMETERS                                                       |      |       |     |        |      |     |         |       |        |

| Output Propagation Delay—CMOS<br>(t <sub>PD</sub> ) <sup>2</sup> (DX, DCO+)  | Full | IV    |     | 3.35   |      |     | 3.35    |       | ns     |

| Output Propagation Delay—LVDS<br>(t <sub>PD</sub> ) <sup>3</sup> (DX+, DCO+) | Full | VI    | 1.3 | 3.1    | 6    | 1.3 | 3.1     | 6     | ns     |

| Pipeline Delay (Latency)                                                     | Full | V     |     | 13     |      |     | 13      |       | Cycles |

| Aperture Delay (t <sub>A</sub> )                                             | Full | V     |     |        |      |     |         |       | ns     |

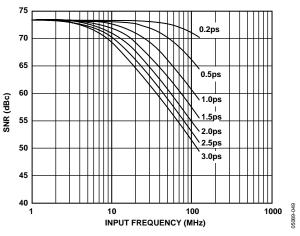

| Aperture Uncertainty (Jitter, t <sub>J</sub> )                               | Full | V     |     | 60     |      |     | 60      |       | fs rms |

<sup>1</sup> With duty cycle stabilizer (DCS) enabled.

<sup>2</sup> Output propagation delay is measured from clock 50% transition to data 50% transition with 5 pF load. <sup>3</sup> LVDS R<sub>TERM</sub> = 100  $\Omega$ . Measured from the 50% point of the rising edge of CLK+ to the 50% point of the data transition.

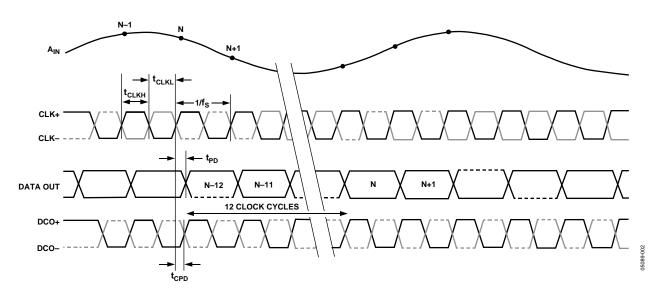

Figure 2. LVDS Mode Timing Diagram

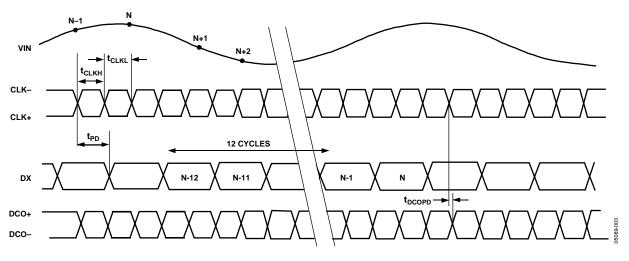

Figure 3. CMOS Timing Diagram

### **EXPLANATION OF TEST LEVELS**

| Test Level | Definitions                                                                                                    |

|------------|----------------------------------------------------------------------------------------------------------------|

|            | 100% production tested.                                                                                        |

| II         | 100% production tested at 25°C and sample tested at specified temperatures.                                    |

| III        | Sample tested only.                                                                                            |

| IV         | Parameter is guaranteed by design and characterization testing.                                                |

| V          | Parameter is a typical value only.                                                                             |

| VI         | 100% production tested at 25°C and guaranteed by design and characterization for industrial temperature range. |

# **ABSOLUTE MAXIMUM RATINGS**

| Table | 5. |

|-------|----|

|       |    |

| Table 5.                                     |                |      |             |      |

|----------------------------------------------|----------------|------|-------------|------|

|                                              | With           |      |             |      |

| Parameter                                    | Respect to     | Min  | Max         | Unit |

| ELECTRICAL                                   |                |      |             |      |

| AVDD1                                        | AGND           | -0.3 | +4          | V    |

| AVDD2                                        | AGND           | -0.3 | +6          | V    |

| DRVDD                                        | DGND           | -0.3 | +4          | V    |

| AGND                                         | DGND           | -0.3 | +0.3        | V    |

| AVDD1                                        | DRVDD          | -4   | +4          | V    |

| AVDD2                                        | DRVDD          | -4   | +6          | V    |

| AVDD2                                        | AVDD1          | -4   | +6          | V    |

| D0 to D13                                    | DGND           | -0.3 | DRVDD + 0.3 | V    |

| CLK, MODE                                    | AGND           | -0.3 | AVDD1 + 0.3 | V    |

| VIN+, VIN-                                   | AGND           | -0.3 | AVDD2 + 0.3 | V    |

| VREF                                         | AGND           | -0.3 | AVDD1 + 0.3 | V    |

| SENSE                                        | AGND           | -0.3 | AVDD1 + 0.3 | V    |

| REFT, REFB                                   | AGND           | -0.3 | AVDD1 + 0.3 | V    |

| ENVIRONMENTA                                 | <u>L</u>       |      |             |      |

| Storage Temper                               | rature         | -65  | +125        | °C   |

| Operating Temp                               | perature Range | -40  | +85         | °C   |

| Lead Temperature Range<br>(Soldering 10 sec) |                |      | 300         | °C   |

| Junction Tempe                               | erature        |      | 150         | °C   |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect

### THERMAL RESISTANCE

device reliability.

The heat sink of the AD9446 package must be soldered to ground.

| Ta | ıble | ۰ <b>6</b> |

|----|------|------------|

| De ales un Trus a | •    | •           | ^   | 11 14 |

|-------------------|------|-------------|-----|-------|

| Package Type      | AIA  | <b>A</b> 1B | οισ | Unit  |

| 100-Lead TQFP/EP  | 19.8 | 8.3         | 2   | °C/W  |

Typical  $\theta_{JA}$  = 19.8°C/W (heat sink soldered) for multilayer board in still air.

Typical  $\theta_{\rm JB}$  = 8.3°C/W (heat sink soldered) for multilayer board in still air.

Typical  $\theta_{JC} = 2^{\circ}C/W$  (junction to exposed heat sink) represents the thermal resistance through heat sink path.

Airflow increases heat dissipation, effectively reducing  $\theta_{JA}$ . Also, more metal directly in contact with the package leads, from metal traces through holes, ground, and power planes, reduces the  $\theta_{JA}$ . It is required that the exposed heat sink be soldered to the ground plane.

**ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

# **DEFINITIONS OF SPECIFICATIONS**

#### Analog Bandwidth (Full Power Bandwidth)

The analog input frequency at which the spectral power of the fundamental frequency (as determined by the FFT analysis) is reduced by 3 dB.

#### Aperture Delay (t<sub>A</sub>)

The delay between the 50% point of the rising edge of the clock and the instant at which the analog input is sampled.

### Aperture Uncertainty (Jitter, t<sub>J</sub>)

The sample-to-sample variation in aperture delay.

#### Clock Pulse Width and Duty Cycle

Pulse width high is the minimum amount of time that the clock pulse should be left in the Logic 1 state to achieve rated performance. Pulse width low is the minimum time the clock pulse should be left in the low state. At a given clock rate, these specifications define an acceptable clock duty cycle.

### Differential Nonlinearity (DNL, No Missing Codes)

An ideal ADC exhibits code transitions that are exactly 1 LSB apart. DNL is the deviation from this ideal value. Guaranteed no missing codes to 16-bit resolution indicates that all 65536 codes must be present over all operating ranges.

### Effective Number of Bits (ENOB)

The effective number of bits for a sine wave input at a given input frequency can be calculated directly from its measured SINAD using the following formula:

$$ENOB = \frac{(SINAD - 1.76)}{6.02}$$

#### **Gain Error**

The first code transition should occur at an analog value of ½ LSB above negative full scale. The last transition should occur at an analog value of 1 ½ LSB below the positive full scale. Gain error is the deviation of the actual difference between first and last code transitions and the ideal difference between first and last code transitions.

#### Integral Nonlinearity (INL)

The deviation of each individual code from a line drawn from negative full scale through positive full scale. The point used as negative full scale occurs ½ LSB before the first code transition. Positive full scale is defined as a level 1 ½ LSBs beyond the last code transition. The deviation is measured from the middle of each particular code to the true straight line.

### Maximum Conversion Rate

The clock rate at which parametric testing is performed.

#### **Minimum Conversion Rate**

The clock rate at which the SNR of the lowest analog signal frequency drops by no more than 3 dB below the guaranteed limit.

#### **Offset Error**

The major carry transition should occur for an analog value of  $\frac{1}{2}$  LSB below VIN+ = VIN-. Offset error is defined as the deviation of the actual transition from that point.

#### **Out-of-Range Recovery Time**

The time it takes for the ADC to reacquire the analog input after a transition from 10% above positive full scale to 10% above negative full scale, or from 10% below negative full scale to 10% below positive full scale.

#### Output Propagation Delay (tpd)

The delay between the clock rising edge and the time when all bits are within valid logic levels.

#### **Power-Supply Rejection Ratio**

The change in full scale from the value with the supply at the minimum limit to the value with the supply at its maximum limit.

#### Signal-to-Noise and Distortion (SINAD)

The ratio of the rms input signal amplitude to the rms value of the sum of all other spectral components below the Nyquist frequency, including harmonics but excluding dc.

#### Signal-to-Noise Ratio (SNR)

The ratio of the rms input signal amplitude to the rms value of the sum of all other spectral components below the Nyquist frequency, excluding the first six harmonics and dc.

### Spurious-Free Dynamic Range (SFDR)

The ratio of the rms signal amplitude to the rms value of the peak spurious spectral component. The peak spurious component may or may not be a harmonic. SFDR may be reported in dBc (that is, degrades as signal level is lowered) or dBFS (always related back to converter full scale).

#### **Temperature Drift**

The temperature drift for offset error and gain error specifies the maximum change from the initial (25°C) value to the value at  $T_{\text{MIN}}$  or  $T_{\text{MAX}}$ .

#### **Total Harmonic Distortion (THD)**

The ratio of the rms input signal amplitude to the rms value of the sum of the first six harmonic components.

#### **Two-Tone SFDR**

The ratio of the rms value of either input tone to the rms value of the peak spurious component. The peak spurious component may or may not be an IMD product.

# AD9446

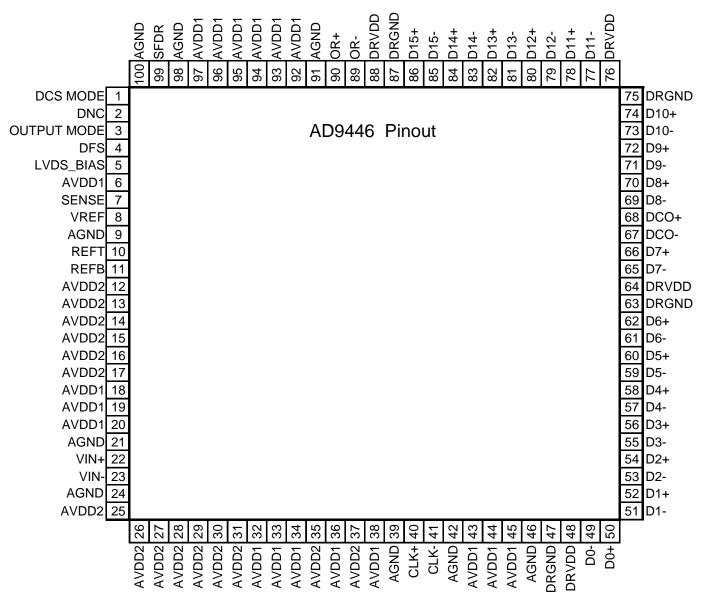

# **PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS**

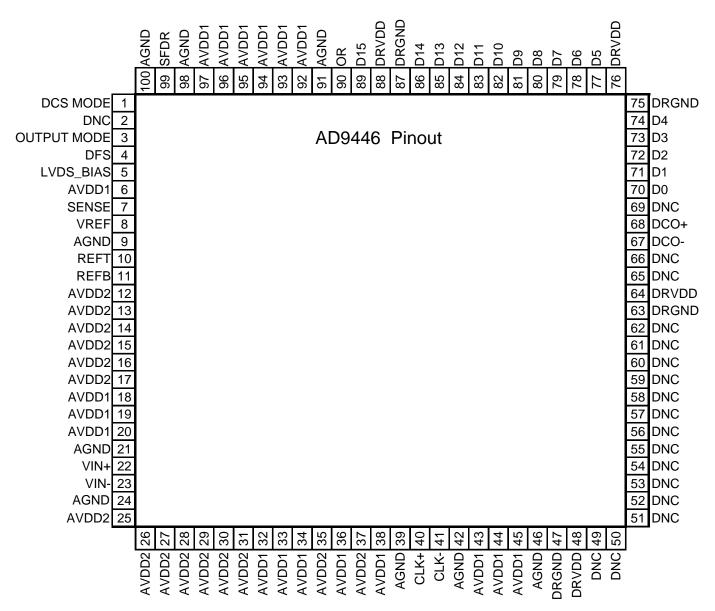

Figure 4. 100-Lead TQFP/EP Pin Configuration in LVDS Mode

| Pin No.                                                  | Mnemonic       | Description                                                                                                                                                                  |  |

|----------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

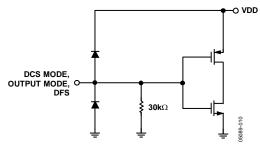

| 1                                                        | DCS MODE       | Clock Duty Cycle Stabilizer (DCS) Control Pin, CMOS-Compatible. DCS = low (AGND) to enable DCS (recommended). DCS = high (AVDD1) to disable DCS.                             |  |

| 2                                                        | DNC            | Do Not Connect. These pins should float.                                                                                                                                     |  |

| 3                                                        | OUTPUT<br>MODE | CMOS-Compatible Output Logic Mode Control Pin. OUTPUT MODE = 0 for CMOS mode, and OUTPUT MODE = 1 (AVDD1) for LVDS outputs.                                                  |  |

| 4                                                        | DFS            | Data Format Select Pin. CMOS control pin that determines the format of the output data. DFS = high (AVDD1) for twos complement, DFS = low (ground) for offset binary format. |  |

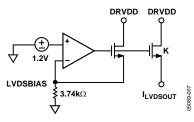

| 5                                                        | LVDS_BIAS      | Set Pin for LVDS Output Current. Place 3.7 k $\Omega$ resistor terminated to DRGND.                                                                                          |  |

| 6, 18 to 20, 32 to 34, 36, 38,<br>43 to 45, 92 to 97     | AVDD1          | 3.3 V (±5%) Analog Supply.                                                                                                                                                   |  |

| 7                                                        | SENSE          | Reference Mode Selection. Connect to AGND for internal 1 V reference; connect to AVDD2 for external reference.                                                               |  |

| 8                                                        | VREF           | 1.0 V Reference I/O—Function Dependent on SENSE. Decouple to ground with 0.1 $\mu F$ and 10 $\mu F$ capacitors.                                                              |  |

| 9, 21, 24, 39, 42, 46, 91, 98,<br>100, Exposed Heat Sink | AGND           | Analog Ground. The exposed heat sink on the bottom of the package must be connected to AGND.                                                                                 |  |

| 10                                                       | REFT           | Differential Reference Output. Decoupled to ground with 0.1 $\mu$ F capacitor and to REFB (Pin 11) with 0.1 $\mu$ F and 10 $\mu$ F capacitors.                               |  |

| 11                                                       | REFB           | Differential Reference Output. Decoupled to ground with a 0.1 $\mu$ F capacitor and to REFT (Pin 10) with 0.1 $\mu$ F and 10 $\mu$ F capacitors.                             |  |

| 12 to 17, 25 to 31, 35, 37                               | AVDD2          | 5.0 V Analog Supply (±5%).                                                                                                                                                   |  |

| 22                                                       | VIN+           | Analog Input—True.                                                                                                                                                           |  |

| 23                                                       | VIN-           | Analog Input—Complement.                                                                                                                                                     |  |

| 40                                                       | CLK+           | Clock Input—True.                                                                                                                                                            |  |

| 41                                                       | CLK–           | Clock Input—Complement.                                                                                                                                                      |  |

| 47, 63, 75, 87,                                          | DRGND          | Digital Output Ground.                                                                                                                                                       |  |

| 48, 64, 76, 88                                           | DRVDD          | 3.3 V Digital Output Supply (3.0 V to 3.6 V).                                                                                                                                |  |

| 49                                                       | D0– (LSB)      | D0 Complement Output Bit (LVDS Levels).                                                                                                                                      |  |

| 50                                                       | D0+            | D0 True Output Bit.                                                                                                                                                          |  |

| 51                                                       | D1–            | D1 Complement Output Bit.                                                                                                                                                    |  |

| 52                                                       | D1+            | D1 True Output Bit.                                                                                                                                                          |  |

| 53                                                       | D2-            | D2 Complement Output Bit.                                                                                                                                                    |  |

| 54                                                       | D2+            | D2 True Output Bit.                                                                                                                                                          |  |

| 55                                                       | D3-            | D3 Complement Output Bit.                                                                                                                                                    |  |

| 56                                                       | D3+            | D3 True Output Bit.                                                                                                                                                          |  |

| 57                                                       | D4-            | D4 Complement Output Bit.                                                                                                                                                    |  |

| 58                                                       | D4+            | D4 True Output Bit.                                                                                                                                                          |  |

| 59                                                       | D5-            | D5 Complement Output Bit.                                                                                                                                                    |  |

| 60                                                       | D5+            | D5 True Output Bit.                                                                                                                                                          |  |

| 61                                                       | D6-            | D6 Complement Output Bit.                                                                                                                                                    |  |

| 62                                                       | D6+            | D6 True Output Bit.                                                                                                                                                          |  |

| 65                                                       | D7–            | D7 Complement Output Bit.                                                                                                                                                    |  |

| 66                                                       | D7+            | D7 True Output Bit.                                                                                                                                                          |  |

| 67                                                       | DCO-           | Data Clock Output—Complement.                                                                                                                                                |  |

| 68                                                       | DCO+           | Data Clock Output—True.                                                                                                                                                      |  |

| 69                                                       | D8-            | D8 Complement Output Bit.                                                                                                                                                    |  |

| 70                                                       | D8+            | D8 True Output Bit.                                                                                                                                                          |  |

| 71                                                       | D9-            | D9 Complement Output Bit.                                                                                                                                                    |  |

| 72                                                       | D9+            | D9 True Output Bit.                                                                                                                                                          |  |

| 73                                                       | D10-           | D10 Complement Output Bit.                                                                                                                                                   |  |

| 74                                                       | D10+           | D10 True Output Bit.                                                                                                                                                         |  |

| 77                                                       | D11-           | D11 Complement Output Bit.                                                                                                                                                   |  |

| 78                                                       | D11+           | D11 True Output Bit.                                                                                                                                                         |  |

# Preliminary Technical Data

| Pin No. | Mnemonic   | Description                                                                                                                                                                                                                                                                                                                                                                        |

|---------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 79      | D12-       | D12 Complement Output Bit.                                                                                                                                                                                                                                                                                                                                                         |

| 80      | D12+       | D12 True Output Bit.                                                                                                                                                                                                                                                                                                                                                               |

| 81      | D13–       | D13 Complement Output.                                                                                                                                                                                                                                                                                                                                                             |

| 82      | D13+       | D13 True Output Bit.                                                                                                                                                                                                                                                                                                                                                               |

| 83      | D14–       | D14 Complement Output.                                                                                                                                                                                                                                                                                                                                                             |

| 84      | D14+       | D14 True Output Bit.                                                                                                                                                                                                                                                                                                                                                               |

| 85      | D15–       | D15 Complement Output.                                                                                                                                                                                                                                                                                                                                                             |

| 86      | D15+ (MSB) | D15 True Output Bit.                                                                                                                                                                                                                                                                                                                                                               |

| 89      | OR-        | Out-of-Range Complement Output Bit.                                                                                                                                                                                                                                                                                                                                                |

| 90      | OR+        | Out-of-Range True Output Bit.                                                                                                                                                                                                                                                                                                                                                      |

| 99      | SFDR       | CMOS control pin that enables (SFDR MODE = 1) a proprietary circuit that may improve the spurious-free dynamic range (SFDR) performance of the AD9446. It is useful in applications where the dynamic range of the system is limited by discrete spurious frequency content caused by nonlinearities in the ADC transfer function. SFDR MODE = 0 for normal operation; floats low. |

AD9446

Figure 5. 100-Lead TQFP/EP Pin Configuration in CMOS Mode

| Pin No.                                                  | Mnemonic           | Description                                                                                                                                                                                                                                                                               |  |

|----------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                                                        | DCS MODE           | Clock Duty Cycle Stabilizer (DCS) Control Pin, CMOS-Compatible. DCS = low (AGND) to enable DCS (recommended). DCS = high (AVDD1) to disable DCS.                                                                                                                                          |  |

| 2, 49 to 62, 65 to 66, 69,                               | DNC                | Do Not Connect. These pins should float.                                                                                                                                                                                                                                                  |  |

| 3                                                        | OUTPUT MODE        | CMOS-Compatible Output Logic Mode Control Pin. OUTPUT MODE = 0 for CMOS mode, and OUTPUT MODE = 1 (AVDD1) for LVDS outputs.                                                                                                                                                               |  |

| 4                                                        | DFS                | Data Format Select Pin. CMOS control pin that determines the format of the output data. DFS high (AVDD1) for twos complement, DFS = low (ground) for offset binary format.                                                                                                                |  |

| 5                                                        | LVDS_BIAS          | Set Pin for LVDS Output Current. Place 3.7 k $\Omega$ resistor terminated to DRGND.                                                                                                                                                                                                       |  |

| 6, 18 to 20,                                             | AVDD1              | 3.3 V (±5%) Analog Supply.                                                                                                                                                                                                                                                                |  |

| 32 to 34,                                                |                    |                                                                                                                                                                                                                                                                                           |  |

| 36, 38,<br>43 to 45                                      |                    |                                                                                                                                                                                                                                                                                           |  |

| 43 to 45,<br>92 to 97                                    |                    |                                                                                                                                                                                                                                                                                           |  |

| 7                                                        | SENSE              | Reference Mode Selection. Connect to AGND for internal 1 V reference; connect to AVDD2 for external reference.                                                                                                                                                                            |  |

| 8                                                        | VREF               | 1.0 V Reference I/O—Function Dependent on SENSE. Decouple to ground with 0.1 $\mu F$ and 10 $\mu F$ capacitors.                                                                                                                                                                           |  |

| 9, 21, 24, 39, 42, 46, 91, 98,<br>100, Exposed Heat Sink | AGND               | Analog Ground. The exposed heat sink on the bottom of the package must be connected to AGND.                                                                                                                                                                                              |  |

| 10                                                       | REFT               | Differential Reference Output. Decoupled to ground with 0.1 $\mu$ F capacitor and to REFB (Pin 11) with 0.1 $\mu$ F and 10 $\mu$ F capacitors.                                                                                                                                            |  |

| 11                                                       | REFB               | Differential Reference Output. Decoupled to ground with a 0.1 $\mu$ F capacitor and to REFT (Pin 10) with 0.1 $\mu$ F and 10 $\mu$ F capacitors.                                                                                                                                          |  |

| 12 to 17, 25 to 31, 35, 37                               | AVDD2              | 5.0 V Analog Supply (±5%).                                                                                                                                                                                                                                                                |  |

| 22                                                       | VIN+               | Analog Input—True.                                                                                                                                                                                                                                                                        |  |

| 23                                                       | VIN-               | Analog Input—Complement.                                                                                                                                                                                                                                                                  |  |

| 40                                                       | CLK+               | Clock Input—True.                                                                                                                                                                                                                                                                         |  |

| 41                                                       | CLK–               | Clock Input—Complement.                                                                                                                                                                                                                                                                   |  |

| 47, 63, 75, 87,                                          | DRGND              | Digital Output Ground.                                                                                                                                                                                                                                                                    |  |

| 48, 64, 76, 88                                           | DRVDD              | 3.3 V Digital Output Supply (3.0 V to 3.6 V).                                                                                                                                                                                                                                             |  |

| 67                                                       | DCO-               | Data Clock Output—Complement.                                                                                                                                                                                                                                                             |  |

| 68                                                       | DCO+               | Data Clock Output—True.                                                                                                                                                                                                                                                                   |  |

| 70                                                       | D0(LSB)            | D0 True Output Bit. (CMOS Levels)                                                                                                                                                                                                                                                         |  |

| 71                                                       | D1+                | D1 True Output Bit.                                                                                                                                                                                                                                                                       |  |

| 72                                                       | D2+                | D2 True Output Bit.                                                                                                                                                                                                                                                                       |  |

| 73                                                       | D3+                | D3 True Output Bit.                                                                                                                                                                                                                                                                       |  |

| 74                                                       | D4+                | D4 True Output Bit.                                                                                                                                                                                                                                                                       |  |

| 77                                                       | D5+                | D5 True Output Bit.                                                                                                                                                                                                                                                                       |  |

| 78                                                       | D6+                | D6 True Output Bit.                                                                                                                                                                                                                                                                       |  |

| 79                                                       | D7+                | D7 True Output Bit.<br>D8 True Output Bit.                                                                                                                                                                                                                                                |  |

| 80                                                       | D8+<br>D9+         | D9 True Output Bit.                                                                                                                                                                                                                                                                       |  |

| 81                                                       | D9+<br>D10+        | D10 True Output Bit.                                                                                                                                                                                                                                                                      |  |

| 82<br>83                                                 | D10+               | D11 True Output Bit.                                                                                                                                                                                                                                                                      |  |

| 84                                                       | D12+               | D12 True Output Bit.                                                                                                                                                                                                                                                                      |  |

| 85                                                       | D12+               | D13 True Output Bit.                                                                                                                                                                                                                                                                      |  |

| 86                                                       | D13+<br>D14+       | D14 True Output Bit.                                                                                                                                                                                                                                                                      |  |

| 89                                                       | D14+<br>D15+ (MSB) | D15 True Output Bit.                                                                                                                                                                                                                                                                      |  |

| 90                                                       | OR+                | Out-of-Range True Output Bit.                                                                                                                                                                                                                                                             |  |

| 99                                                       | SFDR               | CMOS control pin that enables (SFDR MODE = 1) a proprietary circuit that may improve the                                                                                                                                                                                                  |  |

|                                                          |                    | spurious-free dynamic range (SFDR) performance of the AD9446. It is useful in applications where the dynamic range of the system is limited by discrete spurious frequency content caused by nonlinearities in the ADC transfer function. SFDR MODE = 0 for normal operation; floats low. |  |

### Table 8. Pin Function Descriptions—100-Lead TQFP/EP in CMOS Mode

# **EQUIVALENT CIRCUITS**

Figure 6. Equivalent Analog Input Circuit

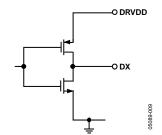

Figure 9. Equivalent CMOS Digital Output Circuit

Figure 10. Equivalent Digital Input Circuit, DFS, DCS MODE, OUTPUT MODE

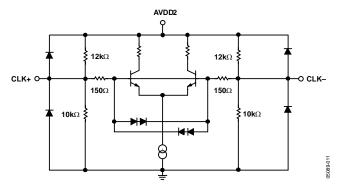

Figure 11. Equivalent Sample Clock Input Circuit

Figure 7. Equivalent LVDS\_BIAS Circuit

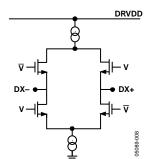

Figure 8. Equivalent LVDS Digital Output Circuit

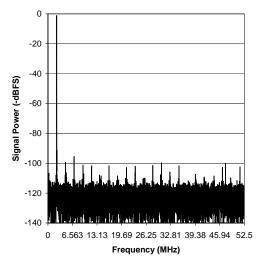

# **TYPICAL PERFORMANCE CHARACTERISTICS**

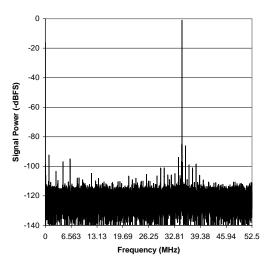

AVDD1 = 3.3 V, AVDD2 = 5.0 V, DRVDD = 3.3 V, sample rate = 100 MSPS, LVDS mode, DCS enabled,  $T_A = 25^{\circ}C$ , 3.2 V p-p differential input, AIN = -0.5 dBFS, internal trimmed reference (nominal VREF = 1.6 V), unless otherwise noted.

Figure 12. 32K Point Single-Tone FFT/105 MSPS/2.3 MHz

Figure 13. 32K Point Single-Tone FFT/105 MSPS/70.3 MHz

# THEORY OF OPERATION

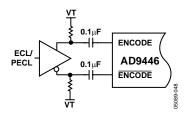

The AD9446 architecture is optimized for high speed and ease of use. The analog inputs drive an integrated, high bandwidth track-and-hold circuit that samples the signal prior to quantization by the 16-bit pipeline ADC core. The device includes an on-board reference and input logic that accepts TTL, CMOS, or LVPECL levels. The digital output logic levels are user selectable as standard 3 V CMOS or LVDS (ANSI-644 compatible) via the OUTPUT MODE pin.

## ANALOG INPUT AND REFERENCE OVERVIEW

A stable and accurate 0.5 V voltage reference is built into the AD9446. The input range can be adjusted by varying the reference voltage applied to the AD9446, using either the internal reference or an externally applied reference voltage. The input span of the ADC tracks reference voltage changes linearly. The various reference modes are described in the next few sections.

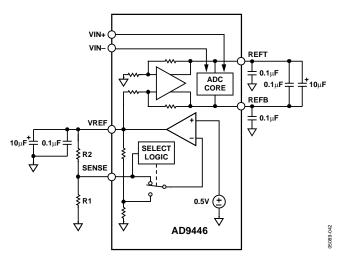

### Internal Reference Connection

A comparator within the AD9446 detects the potential at the SENSE pin and configures the reference into four possible states, which are summarized in Table 9. If SENSE is grounded, the reference amplifier switch is connected to the internal resistor divider (see Figure 14), setting VREF to ~1.6 V. Connecting the SENSE pin to VREF switches the reference amplifier output to the SENSE pin, completing the loop and providing a ~1.0 V reference output. If a resistor divider is connected, as shown in Figure 15, the switch again sets to the SENSE pin. This puts the reference amplifier in a noninverting mode with the VREF output defined as

$$VREF = 0.5 V \times \left(1 + \frac{R2}{R1}\right)$$

In all reference configurations, REFT and REFB drive the A/D conversion core and establish its input span. The input range of the ADC always equals twice the voltage at the reference pin for either an internal or an external reference.

### Internal Reference Trim

The internal reference voltage is trimmed during the production test to adjust the gain (analog input voltage range) of the AD9446. Therefore, there is little advantage to the user supplying an external voltage reference to the AD9446. The gain trim is performed with the AD9446's input range set to 3.2 V p-p nominal (SENSE connected to AGND). Because of this trim and the fact that the 3.2 V p-p analog input range provides maximum ac performance, there is little benefit to using analog input ranges <2 V p-p. Users are cautioned that the differential nonlinearity of the ADC varies with the reference voltage. Configurations that use <3.2 V p-p may exhibit missing codes and, therefore, degraded noise and distortion performance.

Figure 14. Internal Reference Configuration

Figure 15. Programmable Reference Configuration

#### **Table 9. Reference Configuration Summary**

### **External Reference Operation**

**Internal Fixed Reference**

The AD9446's internal reference is trimmed to enhance the gain accuracy of the ADC. An external reference may be more stable over temperature, but the gain of the ADC is not likely to be improved. Figure X shows the typical drift characteristics of the internal reference in both 1 V and 0.5 V modes.

AGND to 0.2 V

1.6

When the SENSE pin is tied to AVDD, the internal reference is disabled, allowing the use of an external reference. An internal reference buffer loads the external reference with an equivalent 7 k $\Omega$  load. The internal buffer still generates the positive and negative full-scale references, REFT and REFB, for the ADC core. The input span is always twice the value of the reference voltage; therefore, the external reference must be limited to a maximum of 1.6 V.

#### **Analog Inputs**

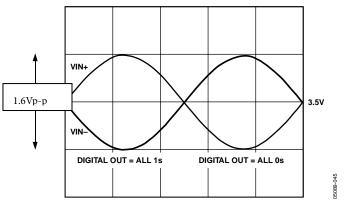

As with most new high speed, high dynamic range ADCs, the analog input to the AD9446 is differential. Differential inputs improve on-chip performance because signals are processed through attenuation and gain stages. Most of the improvement is a result of differential analog stages having high rejection of even-order harmonics. There are also benefits at the PCB level. First, differential inputs have high common-mode rejection of stray signals, such as ground and power noise. Second, they provide good rejection of common-mode signals, such as local oscillator feedthrough. The specified noise and distortion of the AD9446 cannot be realized with a single-ended analog input, so such configurations are discouraged. Contact ADI for recommendations of other 16-bit ADCs that support single-ended analog input configurations.

With the 1 V reference (nominal value, see the Internal Reference Trim section), the differential input range of the AD9446's analog input is nominally 3.2 V p-p or 1.6 V p-p on each input (VIN+ or VIN-).

3.2 V p-p

AD9446

Figure 16. Differential Analog Input Range for VREF = 1.6 V

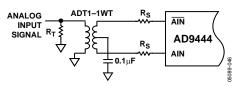

The AD9446 analog input voltage range is offset from ground by 3.5 V. Each analog input connects through a 1 k $\Omega$  resistor to the 3.5 V bias voltage and to the input of a differential buffer. The internal bias network on the input properly biases the buffer for maximum linearity and range (see the Equivalent Circuits section). Therefore, the analog source driving the AD9446 should be ac-coupled to the input pins. The recommended method for driving the analog input of the AD9446 is to use an RF transformer to convert single-ended signals to differential (see Figure 18). Series resistors between the output of the transformer and the AD9446 analog inputs help isolate the analog input source from switching transients caused by the internal sample-and-hold circuit. The series resistors, along with the 1 k $\Omega$  resisters connected to the internal 3.5 V bias. must be considered in impedance matching the transformers input. For example, if  $R_T$  is set to 51  $\Omega$ ,  $R_S$  is set to 33  $\Omega$ , and there is a 1:1 impedance ratio transformer, the input will match a 50  $\Omega$  source with a full-scale drive of 10.0 dBm. The 50  $\Omega$ impedance matching can also be incorporated on the secondary side of the transformer, as shown in the evaluation board schematic (see Figure X and Figure X).

Figure 17. Transformer-Coupled Analog Input Circuit

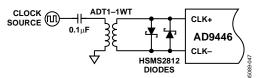

## **CLOCK INPUT CONSIDERATIONS**

Any high speed ADC is extremely sensitive to the quality of the sampling clock provided by the user. A track-and-hold circuit is essentially a mixer, and any noise, distortion, or timing jitter on the clock is combined with the desired signal at the A/D output. For that reason, considerable care was taken in the design of the clock inputs of the AD9446, and the user is advised to give careful thought to the clock source.

Typical high speed ADCs use both clock edges to generate a variety of internal timing signals and, as a result, may be sensitive to the clock duty cycle. Commonly a 5% tolerance is required on the clock duty cycle to maintain dynamic performance characteristics. The AD9446 contains a clock duty cycle stabilizer (DCS) that retimes the nonsampling edge, providing an internal clock signal with a nominal 50% duty cycle. As shown in Figure X, noise and distortion performance are nearly flat for a 30% to 70% duty cycle with the DCS enabled. The DCS circuit locks to the rising edge of CLK+ and optimizes timing internally. This allows for a wide range of input duty cycles at the input without degrading performance. Jitter in the rising edge of the input is still of paramount concern and is not reduced by the internal stabilization circuit. The duty cycle control loop does not function for clock rates less than 30 MHz nominally. The loop has a time constant associated with it that needs to be considered in applications where the clock rate can change dynamically, which requires a wait time of 1.5 µs to 5 µs after a dynamic clock frequency increase (or decrease) before the DCS loop is relocked to the input signal. During the time period that the loop is not locked, the DCS loop is bypassed, and the internal device timing is dependant on the duty cycle of the input clock signal. In such an application, it may be appropriate to disable the duty cycle stabilizer. In all other applications, enabling the DCS circuit is recommended to maximize ac performance.

The DCS circuit is controlled by the DCS MODE pin; a CMOS logic low (AGND) on DCS MODE enables the duty cycle stabilizer, and logic high (AVDD1 = 3.3 V) disables the controller.