# PE4220

# **Product Description**

The PE4220 MOSFET RF Switch is designed to cover a broad range of uses in the 10 MHz through 2.5 GHz frequency range. This switch integrates on-board CMOS control logic with an internal charge pump, eliminating the need for a negative voltage supply. The control inputs are low voltage CMOS compatible.

The PE4220 MOSFET RF Switch is manufactured in Peregrine's patented Ultra Thin Silicon (UTSi⊚) CMOS process, offering the performance of GaAs with the economy and integration of conventional CMOS.

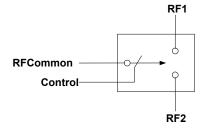

Figure 1. Functional Schematic Diagram

# SPDT Low Insertion Loss MOSFET RF Switch

#### **Features**

- Single 3.0 V Power Supply

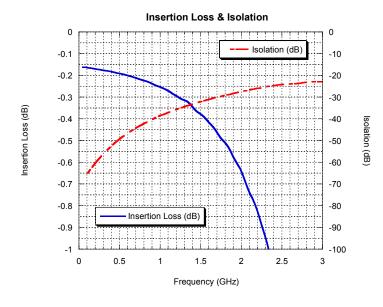

- Low Insertion loss: 0.25 dB at 1.0 GHz, 0.65 dB at 2.0 GHz

- High isolation of 36 dB at 1.0 GHz, 26 dB at 2.0 GHz

- Typical 1 dB compression of +21 dBm

- Low voltage CMOS logic control

- Low Cost

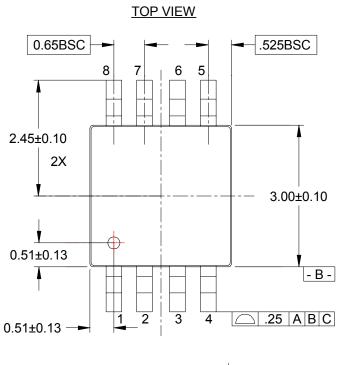

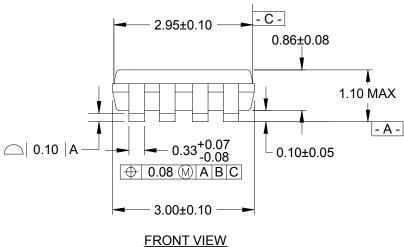

Figure 2. Package Drawings

Table 1. Electrical Specifications @ +25 °C,  $V_{DD}$  = 3 V (Zs = ZL = 50  $\Omega$ )

| Parameter                      | Conditions                        | Minimum | Typical      | Maximum | Units     |

|--------------------------------|-----------------------------------|---------|--------------|---------|-----------|

| Operating Frequency            |                                   | 10      |              | 2500    | MHz       |

| Insertion Loss                 | 1000 MHz<br>2000 MHz              |         | 0.25<br>0.65 |         | dB<br>dB  |

| Isolation                      | 1000 MHz<br>2000 MHz              |         | 36<br>26     |         | dB<br>dB  |

| Return Loss                    | 1000 MHz<br>2000 MHz              |         | 20<br>14     |         | dB<br>dB  |

| 'ON' Switching Time            | CTRL to 0.1 dB final value, 2 GHz |         | 200          |         | ns        |

| 'OFF' Switching Time           | CTRL to 25 dB isolation, 2 GHz    |         | 90           |         | ns        |

| Full Cycle Switching Time      |                                   |         | 5            |         | μS        |

| Video Feedthrough <sup>1</sup> |                                   |         | 5.0          |         | $mV_{pp}$ |

| Input 1 dB Compression         | 2000 MHz                          |         | 21           |         | dBm       |

| Input IP3                      | 2000 MHz, 8 dBm                   |         | 39           |         | dBm       |

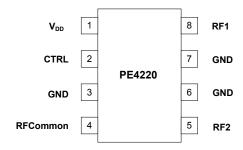

Figure 3. Pin Configuration

**Table 2. Pin Descriptions**

| Pin No. | Pin<br>Name  | Description                                                                                                                     |

|---------|--------------|---------------------------------------------------------------------------------------------------------------------------------|

| 1       | $V_{DD}$     | Nominal 3 V supply connection. A bypass capacitor (100 pF) to the ground plane should be placed as close as possible to the pin |

| 2       | CTRL         | CMOS or TTL logic level: High = RFCommon to RF1 signal path Low = RFCommon to RF2 signal path                                   |

| 3       | GND          | Ground connection. Traces should be physically short and connected to ground plane for best performance.                        |

| 4       | RF<br>Common | Common RF port for switch (Note 1)                                                                                              |

| 5       | RF2          | RF2 port (Note 1)                                                                                                               |

| 6       | GND          | Ground connection. Traces should be physically short and connected to ground plane for best performance.                        |

| 7       | GND          | Ground connection. Traces should be physically short and connected to ground plane for best performance.                        |

| 8       | RF1          | RF1 port (Note 1)                                                                                                               |

**Note 1:** All RF pins must be DC blocked with an external series capacitor.

**Table 3. Absolute Maximum Ratings**

| Symbol           | Parameter/Conditions              | Min  | Max                      | Units |

|------------------|-----------------------------------|------|--------------------------|-------|

| $V_{DD}$         | Power supply voltage              | -0.3 | 4.0                      | V     |

| Vı               | Voltage on any input              | -0.3 | V <sub>DD</sub><br>+ 0.3 | ٧     |

| T <sub>ST</sub>  | Storage temperature range         | -65  | 150                      | °C    |

| T <sub>OP</sub>  | Operating temperature range       | -40  | 85                       | °C    |

| V <sub>ESD</sub> | ESD voltage (Human Body<br>Model) | 200  |                          | V     |

**Table 4. DC Electrical Specifications**

| Parameter                            | Min                     | Тур | Max                     | Units |

|--------------------------------------|-------------------------|-----|-------------------------|-------|

| V <sub>DD</sub> Power Supply Voltage | 2.7                     | 3.0 | 3.3                     | V     |

| Power Supply Current                 |                         | 29  |                         | μΑ    |

| Control Voltage High                 | 0.7x<br>V <sub>DD</sub> |     |                         | V     |

| Control Voltage Low                  |                         |     | 0.3x<br>V <sub>DD</sub> | V     |

**Table 5. Control Logic Truth Table**

| Control Voltage | Signal Path     |  |

|-----------------|-----------------|--|

| CTRL = High     | RFCommon to RF1 |  |

| CTRL = Low      | RFCommon to RF2 |  |

# **Electrostatic Discharge (ESD) Precautions**

When handling this UTSi device, observe the same precautions that you would use with other ESD-sensitive devices. Although this device contains circuitry to protect it from damage due to ESD, precautions should be taken to avoid exceeding the rating specified in Table 3.

# Latch-Up Avoidance

Unlike conventional CMOS devices, UTSi CMOS devices are immune to latch-up.

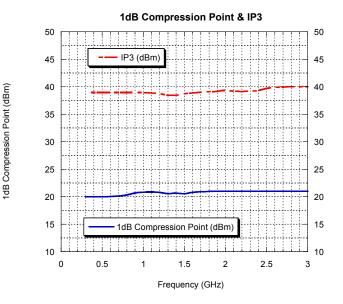

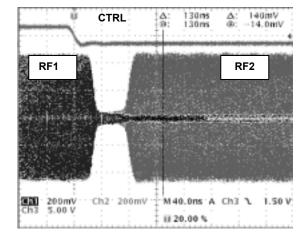

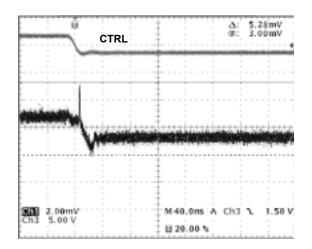

# Typical Performance Data @ +25 °C

Figure 4. Insertion Loss & Isolation

Figure 5. 1dB Compression Point & IP3

Figure 6. Switching Time

Figure 7. Video Feedthrough\*

\*The DC transient at the output of any port of the switch when the control voltage is switched from Low to High or High to Low in a 50 ohm test set-up, measured with 1ns risetime pulses and 500 MHz bandwidth.

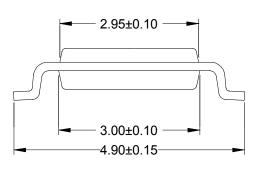

# Figure 8. Package Drawing

8-lead MSOP

SIDE VIEW

# **Table 6. Ordering Information**

| Order<br>Code | Part Marking | Description | Package        | Shipping<br>Method |

|---------------|--------------|-------------|----------------|--------------------|

| 4220-21       | 4220         |             | 8-lead MSOP    | 50 pcs. / Tube     |

| 4220-22       | 4220         |             | 8-lead MSOP    | 2000 pcs. / T&R    |

| 4220-00       | PE4220-EK    |             | Evaluation Kit | 1 / Box            |

## Sales Offices

#### **United States**

#### Peregrine Semiconductor Corp.

6175 Nancy Ridge Drive San Diego, CA 92121 Tel 1-858-455-0660 Fax 1-858-455-0770

# **Europe**

## **Peregrine Semiconductor Europe**

Aix-En-Provence Office Parc Club du Golf, bat 9 13856 Aix-En-Provence Cedex 3 France Tel 33-0-4-4239-3360 Fax 33-0-4-4239-7227

### Japan

#### Peregrine Semiconductor K.K.

The Imperial Tower, 15th floor 1-1-1 Uchisaiawaicho, Chiyoda-ku Tokyo 100-0011 Japan

Tel: 03-3507-5755 Fax: 03-3507-5601

#### Australia

### Peregrine Semiconductor Australia

8 Herb Elliot Ave. Homebush, NSW 2140 Australia

Tel: 011-61-2-9763-4111 Fax: 011-61-2-9746-1501

For a list of representatives in your area, please refer to our Web site at: http://www.peregrine-semi.com

# **Data Sheet Identification**

### Advance Information

The product is in a formative or design stage. The data sheet contains design target specifications for product development. Specifications and features may change in any manner without notice.

#### Preliminary Specification

The data sheet contains preliminary data. Additional data may be added at a later date. Peregrine reserves the right to change specifications at any time without notice in order to supply the best possible product.

#### **Product Specification**

The data sheet contains final data. In the event Peregrine decides to change the specifications, Peregrine will notify customers of the intended changes by issuing a PCN (Product Change Notice).

The information in this data sheet is believed to be reliable. However, Peregrine assumes no liability for the use of this information. Use shall be entirely at the user's own risk.

No patent rights or licenses to any circuits described in this data sheet are implied or granted to any third party.

Peregrine's products are not designed or intended for use in devices or systems intended for surgical implant, or in other applications intended to support or sustain life, or in any application in which the failure of the Peregrine product could create a situation in which personal injury or death might occur. Peregrine assumes no liability for damages, including consequential or incidental damages, arising out of the use of its products in such applications.

Peregrine products are protected under one or more of the following U.S. patents: 6,090,648; 6,057,555; 5,973,382; 5,973,363; 5,930,638; 5,920,233; 5,895,957; 5,883,396; 5,864,162; 5,863,823; 5,861,336; 5,663,570; 5,610,790; 5,600,169; 5,596,205; 5,572,040; 5,492,857; 5,416,043. Other patents may be pending or applied for.

UTSi, the Peregrine logotype, SEL Safe, and Peregrine Semiconductor Corp. are registered trademarks of Peregrine Semiconductor Corp. All PE product names and prefixes are trademarks of Peregrine Semiconductor Corp. Copyright © 2001 Peregrine Semiconductor Corp. All rights reserved.