#### **General Description**

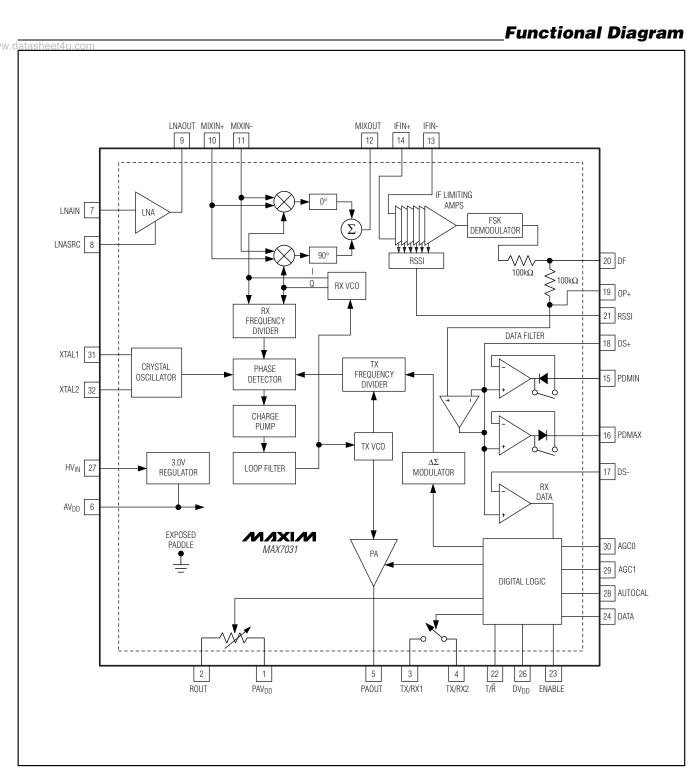

www.datashgax7031 crystal-based, fractional-N transceiver is designed to transmit and receive FSK data at factorypreset carrier frequencies of 308MHz<sup>†</sup>, 315MHz, or 433.92MHz with data rates up to 33kbps (Manchester encoded) or 66kbps (NRZ encoded). This device generates a typical output power of +10dBm into a  $50\Omega$ load, and exhibits typical sensitivity of -110dBm. The MAX7031 features separate transmit and receive pins (PAOUT and LNAIN) and provides an internal RF switch that can be used to connect the transmit and receive pins to a common antenna.

The MAX7031 transmit frequency is generated by a 16bit, fractional-N, phase-locked loop (PLL), while the receiver's local oscillator (LO) is generated by an integer-N PLL. This hybrid architecture eliminates the need for separate transmit and receive crystal reference oscillators because the fractional-N PLL is preset to be 10.7MHz above the receive LO. Retaining the fixed-N PLL for the receiver avoids the higher current-drain requirements of a fractional-N PLL and keeps the receiver current drain as low as possible.

The fractional-N architecture of the MAX7031 transmit PLL allows the transmit FSK signal to be preset for exact frequency deviations, and completely eliminates the problems associated with oscillator-pulling FSK signal generation. All frequency-generation components are integrated on-chip, and only a crystal, a 10.7MHz IF filter, and a few discrete components are required to implement a complete antenna/digital data solution.

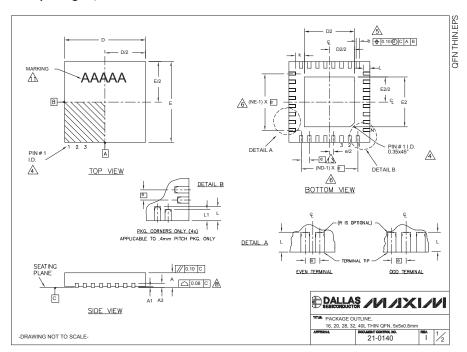

The MAX7031 is available in a small, 5mm x 5mm, 32pin, thin QFN package, and is specified to operate in the automotive -40°C to +125°C temperature range.

<sup>†</sup>Consult factory for availability.

## **Applications**

2-Way Remote Keyless Entry

Security Systems

Home Automation

Remote Controls

Remote Sensing

Smoke Alarms

Garage-Door Openers

Local Telemetry Systems

#### **Features**

- ♦ +2.1V to +3.6V or +4.5V to +5.5V Single-Supply Operation

- ♦ Single-Crystal Transceiver

- **♦** Factory-Preset Frequency (No Serial Interface Required)

- **♦ FSK Modulation**

- **♦** Factory-Preset FSK Frequency Deviation

- ♦ +10dBm Output Power into 50Ω Load

- ♦ Integrated TX/RX Switch

- ♦ Integrated Transmit and Receive PLL, VCO, and **Loop Filter**

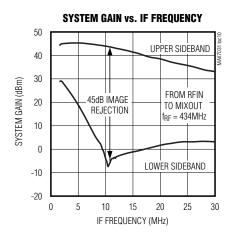

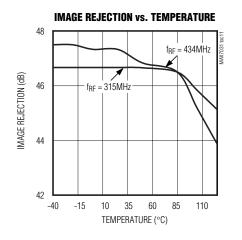

- ♦ > 45dB Image Rejection

- ♦ Typical RF Sensitivity\*: -110dBm

- ♦ Selectable IF Bandwidth with External Filter

- ♦ RSSI Output with High Dynamic Range

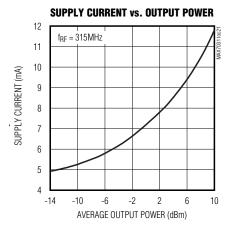

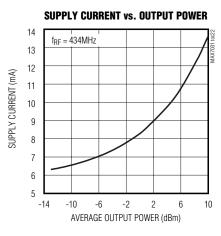

- ♦ < 12.5mA Transmit-Mode Current

</p>

- ♦ < 6.7mA Receive-Mode Current

- ♦ < 800nA Shutdown Current

- ♦ Fast-On Startup Feature, < 250µs</p>

- ♦ Small, 32-Pin, Thin QFN Package

### **Ordering Information**

| PART        | TEMP<br>RANGE      | PIN-PACKAGE      | PKG<br>CODE |

|-------------|--------------------|------------------|-------------|

| MAX7031_ATJ | -40°C to<br>+125°C | 32 Thin QFN-EP** | T3255-3     |

<sup>\*\*</sup>EP = Exposed paddle.

**Note:** The MAX7031 is available with factory-preset operating frequencies. See the Selector Guide for complete part num-

Pin Configuration, Selector Guide, Typical Application Circuit, and Functional Diagram appear at end of data sheet.

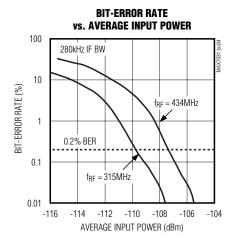

<sup>\*0.2%</sup> BER, 4kbps Manchester-encoded data, 280kHz IF BW

# **MAX7031**

# Low-Cost, 308MHz, 315MHz, and 433.92MHz FSK Transceiver with Fractional-N PLL

#### **ABSOLUTE MAXIMUM RATINGS**

| <sup>.d</sup> Atasheetanom     | 0.3V to +6.0V         |

|--------------------------------|-----------------------|

| PAVDD, AVDD, DVDD to GND       |                       |

| ENABLE, T/R, DATA, AGC0, AGC1, |                       |

| AUTOCAL to GND                 | 0.3V to (HVIN + 0.3)V |

| All Other Pins to GND          | 0.3V to (_VDD + 0.3)V |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) 32-Pin Thin QFN (derate 21.3mW/°C |                |

|-----------------------------------------------------------------------------------------|----------------|

| above +70°C)                                                                            | 1702mW         |

| Operating Temperature Range                                                             | 40°C to +125°C |

| Storage Temperature Range                                                               | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                                                       | +300°C         |

|                                                                                         |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

$(Typical\ Application\ Circuit,\ 50\Omega\ system\ impedance,\ PAV_{DD}=AV_{DD}=DV_{DD}=HV_{IN}=+2.1V\ to\ +3.6V,\ f_{RF}=308MHz,\ 315MHz,\ or\ 433.92MHz,\ T_A=-40^{\circ}C\ to\ +125^{\circ}C,\ unless\ otherwise\ noted.$  Typical values are at  $PAV_{DD}=AV_{DD}=DV_{DD}=HV_{IN}=+2.7V,\ T_A=+25^{\circ}C,\ unless\ otherwise\ noted.$ ) (Note 1)

| PARAMETER                | SYMBOL          | C                                                            | ONDITIONS                                         | MIN                       | TYP                        | MAX                       | UNITS |

|--------------------------|-----------------|--------------------------------------------------------------|---------------------------------------------------|---------------------------|----------------------------|---------------------------|-------|

| Supply Voltage (3V Mode) | V <sub>DD</sub> | HV <sub>IN</sub> , PAV <sub>DD</sub> , AV<br>to power supply | <sub>DD</sub> , and DV <sub>DD</sub> connected    | 2.1                       | 2.7                        | 3.6                       | V     |

| Supply Voltage (5V Mode) | HVIN            |                                                              | nd DV <sub>DD</sub> unconnected onnected together | 4.5                       | 5.0                        | 5.5                       | V     |

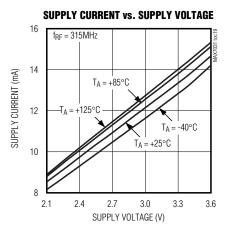

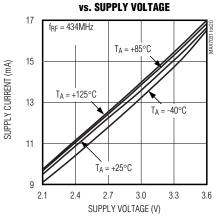

|                          |                 | Transmit mode                                                | f <sub>RF</sub> = 315MHz                          |                           | 11.6                       | 19.1                      |       |

|                          |                 | (Note 2)                                                     | $f_{RF} = 434MHz$                                 |                           | 12.4                       | 20.4                      | m ^   |

|                          |                 |                                                              | Receiver 315MHz                                   |                           | 6.4                        | 8.4                       | mA    |

|                          |                 | T <sub>A</sub> < +85°C,                                      | Receiver 434MHz                                   |                           | 6.7                        | 8.7                       |       |

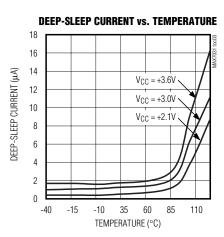

| Cura hu Curra at         | 1               | typ at +25°C<br>(Note 3)                                     | Deep-sleep (3V mode)                              |                           | 0.8                        | 8.8                       | ^     |

| Supply Current           | IDD             | (11010 0)                                                    | Deep-sleep (5V mode)                              |                           | 2.4                        | 10.9                      | μΑ    |

|                          |                 |                                                              | Receiver 315MHz                                   |                           | 6.8                        | 8.7                       | mA    |

|                          |                 | T <sub>A</sub> < +125°C,<br>typ at +125°C<br>(Note 2)        | Receiver 434MHz                                   |                           | 7.0                        | 8.8                       |       |

|                          |                 |                                                              | Deep-sleep (3V mode)                              |                           | 8.0                        | 34.2                      |       |

|                          |                 |                                                              | Deep-sleep (5V mode)                              |                           | 14.9                       | 39.3                      | μΑ    |

| Voltage Regulator        | VREG            | HV <sub>IN</sub> = 5V, I <sub>LOAD</sub> = 15mA              |                                                   |                           | 3.0                        |                           | V     |

| DIGITAL I/O              |                 |                                                              |                                                   |                           |                            |                           |       |

| Input-High Threshold     | VIH             | (Note 2)                                                     |                                                   | 0.9<br>x HV <sub>IN</sub> |                            |                           | V     |

| Input-Low Threshold      | VIL             | (Note 2)                                                     |                                                   |                           |                            | 0.1<br>x HV <sub>IN</sub> | V     |

| Pulldown Sink Current    |                 | AGC0-1, AUTOCAL, ENABLE, T/R, DATA (HV <sub>IN</sub> = 5.5V) |                                                   |                           | 20                         |                           | μΑ    |

| Output Low Voltage       | VoL             | I <sub>SINK</sub> = 500μA                                    |                                                   |                           | 0.15                       |                           | V     |

| Output High Voltage      | V <sub>OH</sub> | ISOURCE = 500µA                                              | 4                                                 |                           | HV <sub>IN</sub><br>- 0.26 |                           | V     |

\_\_\_ /N/XI/W

#### **AC ELECTRICAL CHARACTERISTICS**

$^{WWW.d}$  (Typical Application Circuit, 50Ω system impedance, PAV<sub>DD</sub> = AV<sub>DD</sub> = DV<sub>DD</sub> = HV<sub>IN</sub> = +2.1V to +3.6V, f<sub>RF</sub> = 308MHz, 315MHz. or 433.92MHz, T<sub>A</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at PAV<sub>DD</sub> = AV<sub>DD</sub> = DV<sub>DD</sub> = HV<sub>IN</sub> = +2.7V, T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                    | SYMBOL   | CONDIT                                                                        | TIONS                        | MIN | TYP       | MAX  | UNITS       |

|------------------------------|----------|-------------------------------------------------------------------------------|------------------------------|-----|-----------|------|-------------|

| GENERAL CHARACTERISTICS      | i        | _                                                                             |                              |     |           |      | _           |

| Frequency Range              |          |                                                                               |                              | 30  | 8/315/433 | 3.92 | MHz         |

| Maximum Input Level          | PRFIN    |                                                                               |                              |     | 0         |      | dBm         |

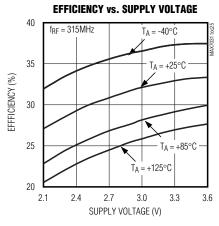

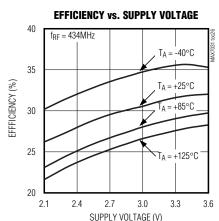

| Transmit Efficiency (Note 5) |          | f <sub>RF</sub> = 315MHz                                                      |                              |     | 32        |      | %           |

| Transmit Emerency (Frete e)  |          | $f_{RF} = 434MHz$                                                             |                              |     | 30        |      | , ,         |

|                              |          | ENABLE or T/R transition transmitter frequency set 50kHz of the desired care. | ettled to within             |     | 200       |      |             |

| Power-On Time                | ton      | ENABLE or T/R transition transmitter frequency set of the desired carrier     | •                            |     | 350       |      | μs          |

|                              |          | ENABLE transition low t transition high to low, re (Note 4)                   | •                            |     | 250       |      |             |

| RECEIVER                     | <b>.</b> |                                                                               |                              |     |           |      | l           |

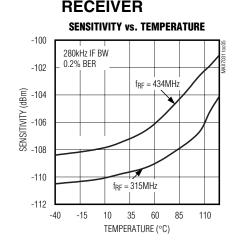

| Sensitivity                  |          | 0.2% BER, 4kbps<br>Manchester data rate,                                      | 315MHz                       |     | -110      |      | - dBm       |

| Constitution                 |          | 280kHz IF BW, FSK<br>±50kHz deviation                                         | 434MHz                       |     | -107      |      | dbiii       |

| Image Rejection              |          |                                                                               |                              |     | 46        |      | dB          |

| POWER AMPLIFIER              |          |                                                                               |                              |     |           |      |             |

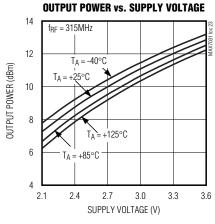

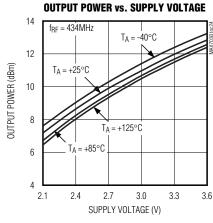

|                              |          | $T_A = +25^{\circ}C \text{ (Note 3)}$                                         |                              | 4.6 | 10.0      | 15.5 |             |

| Output Power                 | Роит     | $T_A = +125$ °C, $PAV_{DD} = HV_{IN} = +2.1V$ (Note 2)                        | $AV_{DD} = DV_{DD} =$        | 3.9 | 6.7       |      | dBm         |

|                              |          | $T_A = -40^{\circ}C$ , $PAV_{DD} = A$<br>= +3.6V (Note 3)                     | $V_{DD} = DV_{DD} = HV_{IN}$ |     | 13.1      | 15.8 |             |

| Maximum Carrier Harmonics    |          | With output matching no                                                       | etwork                       |     | -40       |      | dBc         |

| Reference Spur               |          |                                                                               |                              |     | -50       |      | dBc         |

| PHASE-LOCKED LOOP            |          |                                                                               |                              |     |           |      |             |

| Transmit VCO Gain            | Kvco     |                                                                               |                              |     | 340       |      | MHz/V       |

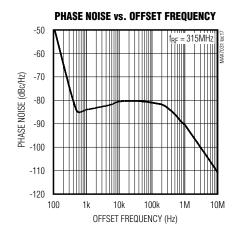

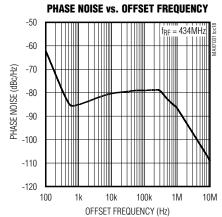

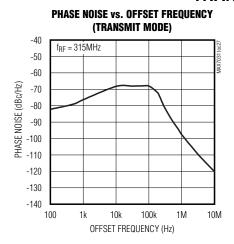

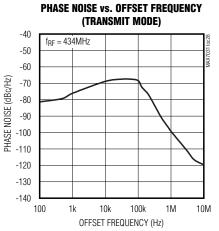

| Transmit DLL Dlass Naiss     |          | 10kHz offset, 200kHz lo                                                       | op BW                        |     | -68       |      | -ID - /I I- |

| Transmit PLL Phase Noise     |          | 1MHz offset, 200kHz loo                                                       | op BW                        |     | -98       |      | dBc/Hz      |

| Receive VCO Gain             |          |                                                                               |                              |     | 340       |      | MHz/V       |

| Descine DI L Die L N. 1      |          | 10kHz offset, 500kHz lo                                                       | op BW                        | -80 |           | T.,  |             |

| Receive PLL Phase Noise      |          | 1MHz offset, 500kHz loo                                                       | op BW                        |     | -90       |      | dBc/Hz      |

| Lance Daniel della           |          | Transmit PLL                                                                  |                              |     | 200       |      | 1.4.1       |

| Loop Bandwidth               |          | Receive PLL                                                                   |                              |     | 500       |      | kHz         |

### **AC ELECTRICAL CHARACTERISTICS (continued)**

(Typical Application Circuit,  $50\Omega$  system impedance,  $PAV_{DD} = AV_{DD} = DV_{DD} = HV_{IN} = +2.1V$  to +3.6V,  $f_{RF} = 308MHz$ , 315MHz. or 433.92MHz,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $PAV_{DD} = AV_{DD} = DV_{DD} = HV_{IN} = +2.7V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                            | SYMBOL   | COND                     | DITIONS           | MIN TYP                | MAX | UNITS            |

|--------------------------------------|----------|--------------------------|-------------------|------------------------|-----|------------------|

| Reference Frequency Input Level      |          |                          |                   | 0.5                    |     | V <sub>P-P</sub> |

| LOW-NOISE AMPLIFIER/MIXER            | (Note 7) |                          |                   |                        |     |                  |

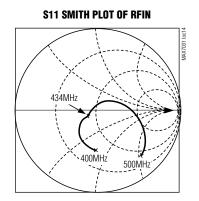

| LNA Input Impedance                  | ZINLNA   | Normalized to $50\Omega$ | $f_{RF} = 315MHz$ | 1 - j4.7               |     |                  |

| Er v i input impodanoo               | ZINLINA  | Normanzed to 3032        | $f_{RF} = 434MHz$ | 1 - j3.3               |     |                  |

|                                      |          | High-gain state          | $f_{RF} = 315MHz$ | 50                     |     |                  |

| Voltage-Conversion Gain              |          | Tilgii-gaiii state       | $f_{RF} = 434MHz$ | 45                     |     | dB               |

| Voltage-Conversion dain              |          | Low-gain state           | $f_{RF} = 315MHz$ | 13                     |     | db db            |

|                                      |          | Low-gain state           | $f_{RF} = 434MHz$ | 9                      |     |                  |

| Input-Referred 3rd-Order             | IIP3     | High-gain state          |                   | -42                    |     | dBm              |

| Intercept Point                      | III J    | Low-gain state           |                   | -6                     |     | GDIII            |

| Mixer Output Impedance               |          |                          |                   | 330                    |     | Ω                |

| LO Signal Feedthrough to<br>Antenna  |          |                          |                   | -100                   |     | dBm              |

| RSSI                                 | •        |                          |                   |                        |     |                  |

| Input Impedance                      |          |                          |                   | 330                    |     | Ω                |

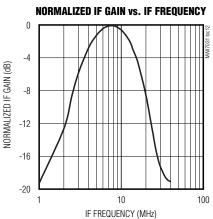

| Operating Frequency                  | fIF      |                          |                   | 10.7                   |     | MHz              |

| 3dB Bandwidth                        |          |                          |                   | 10                     |     | MHz              |

| Gain                                 |          |                          |                   | 15                     |     | mV/dB            |

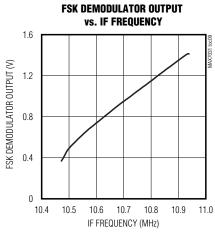

| FSK DEMODULATOR                      |          |                          |                   |                        |     |                  |

| Conversion Gain                      |          |                          |                   | 2.0                    | ,   | mV/kHz           |

| ANALOG BASEBAND                      |          |                          |                   |                        |     |                  |

| Maximum Data Filter Bandwidth        |          |                          |                   | 50                     |     | kHz              |

| Maximum Data Slicer Bandwidth        |          |                          |                   | 100                    |     | kHz              |

| Maximum Peak Detector<br>Bandwidth   |          |                          |                   | 50                     |     | kHz              |

|                                      |          | Manchester coded         |                   | 33                     |     |                  |

| Maximum Data Rate                    |          | Nonreturn to zero (NF    | RZ)               | 66                     |     | kbps             |

| CRYSTAL OSCILLATOR                   | •        |                          |                   | •                      |     | •                |

| Crystal Frequency                    | fXTAL    |                          |                   | (f <sub>RF</sub> - 10. | 7)  | MHz              |

| Maximum Crystal Inductance           |          |                          |                   | 50                     |     | mH               |

| Frequency Pulling by V <sub>DD</sub> |          |                          |                   | 2                      |     | ppm/V            |

| Crystal Load Capacitance             |          | (Note 6)                 |                   | 4.5                    |     | рF               |

#### **AC ELECTRICAL CHARACTERISTICS (continued)**

WWW.d (Typical Application Circuit, 50Ω system impedance, PAV<sub>DD</sub> = AV<sub>DD</sub> = DV<sub>DD</sub> = HV<sub>IN</sub> = +2.1V to +3.6V, f<sub>RF</sub> = 308MHz, 315MHz. or 433.92MHz, T<sub>A</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at PAV<sub>DD</sub> = AV<sub>DD</sub> = DV<sub>DD</sub> = HV<sub>IN</sub> = +2.7V, T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 1)

- Note 1: Supply current, output power, and efficiency are greatly dependent on board layout and PAOUT match.

- Note 2: 100% tested at T<sub>A</sub> = +125°C. Guaranteed by design and characterization over temperature.

- Note 3: Guaranteed by design and characterization. Not production tested.

- Note 4: Time for final signal detection; does not include baseband filter settling.

- **Note 5:** Efficiency = P<sub>OUT</sub> / (V<sub>DD</sub> x I<sub>DD</sub>).

- Note 6: Dependent on PC board trace capacitance.

- Note 7: Input impedance is measured at the LNAIN pin. Note that the impedance at 315MHz includes the 12nH inductive degeneration from the LNA source to ground. The impedance at 434MHz includes a 10nH inductive degeneration connected from the LNA source to ground. The equivalent input circuit is 50Ω in series with ~2.2pF. The voltage conversion is measured with the LNA input-matching inductor, the degeneration inductor, and the LNA/mixer tank in place, and does not include the IF filter insertion loss.

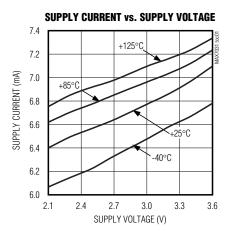

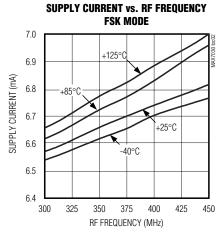

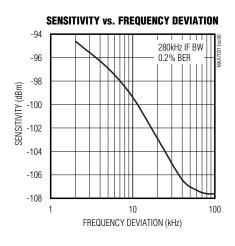

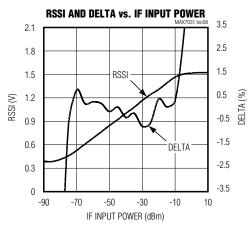

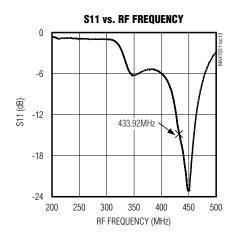

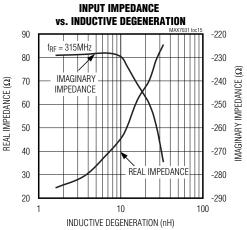

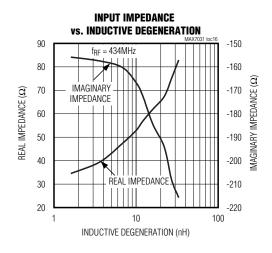

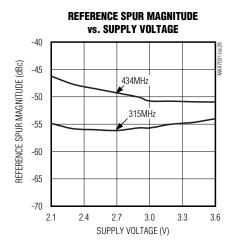

### \_Typical Operating Characteristics

(*Typical Operating Circuit*,  $PAV_{DD} = AV_{DD} = DV_{DD} = HV_{IN} = +3.0V$ ,  $f_{RF} = 433.92MHz$ , IF BW = 280kHz. 4kbps Manchester encoded, 0.2% BER deviation =  $\pm 50$ kHz,  $T_A = +25$ °C, unless otherwise noted.)

#### RECEIVER

### Typical Operating Characteristics (continued)

Typical Operating Circuit,  $PAV_{DD} = AV_{DD} = DV_{DD} = HV_{IN} = +3.0V$ ,  $f_{RF} = 433.92$ MHz, IF BW = 280kHz. 4kbps Manchester encoded, 0.2% BER deviation =  $\pm 50$ kHz,  $T_A = +25$ °C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

www.datypical\_Operating Circuit, PAV<sub>DD</sub> = AV<sub>DD</sub> = DV<sub>DD</sub> = HV<sub>IN</sub> = +3.0V, f<sub>RF</sub> = 433.92MHz, IF BW = 280kHz. 4kbps Manchester encoded, 0.2% BER deviation = ±50kHz, T<sub>A</sub> = +25°C, unless otherwise noted.)

#### **RECEIVER**

### Typical Operating Characteristics (continued)

.d. Typical-Operating Circuit, PAV<sub>DD</sub> = AV<sub>DD</sub> = DV<sub>DD</sub> = HV<sub>IN</sub> = +3.0V, f<sub>RF</sub> = 433.92MHz, IF BW = 280kHz. 4kbps Manchester encoded, 0.2% BER deviation = ±50kHz, T<sub>A</sub> = +25°C, unless otherwise noted.)

#### **TRANSMITTER**

**SUPPLY CURRENT**

### \_Typical Operating Characteristics (continued)

www.d*Typical\_Operating Circuit*, PAV<sub>DD</sub> = AV<sub>DD</sub> = DV<sub>DD</sub> = HV<sub>IN</sub> = +3.0V, f<sub>RF</sub> = 433.92MHz, IF BW = 280kHz. 4kbps Manchester encoded, 0.2% BER deviation = ±50kHz, T<sub>A</sub> = +25°C, unless otherwise noted.)

#### TRANSMITTER

### **Pin Description**

| datasheet4u.coı PIN | NAME              | FUNCTION                                                                                                                                                                                                                                                                                                                  |  |  |  |

|---------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1                   | PAV <sub>DD</sub> | Power-Amplifier Supply Voltage. Bypass to GND with 0.01µF and 220pF capacitors placed as close to the pin as possible.                                                                                                                                                                                                    |  |  |  |

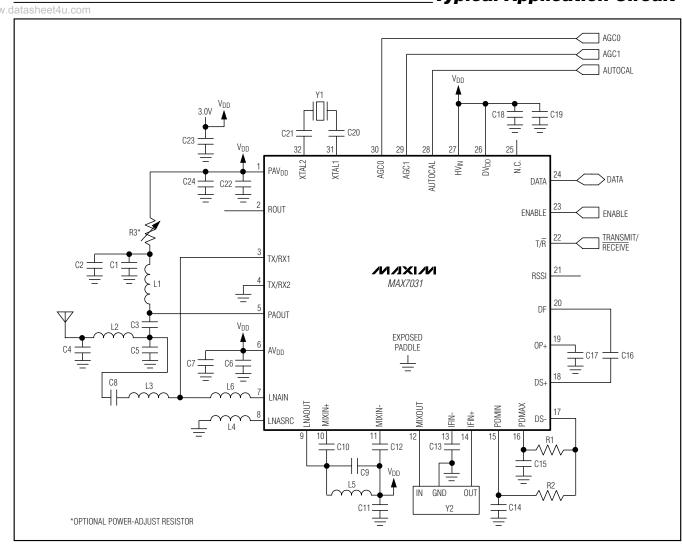

| 2                   | ROUT              | Envelope-Shaping Output. ROUT controls the power-amplifier envelope's rise and fall times. Connect ROUT to the PA pullup inductor or optional power-adjust resistor. Bypass the inductor to GND as close to the inductor as possible with 680pF and 220pF capacitors as shown in the <i>Typical Application Circuit</i> . |  |  |  |

| 3                   | TX/RX1            | Transmit/Receive Switch Throw. Drive T/R high to short TX/RX1 to TX/RX2. Drive T/R low to disconnect TX/RX1 from TX/RX2. Functionally identical to TX/RX2.                                                                                                                                                                |  |  |  |

| 4                   | TX/RX2            | Transmit/Receive Switch Pole. Typically connected to ground. See the <i>Typical Application Circuit</i> .                                                                                                                                                                                                                 |  |  |  |

| 5                   | PAOUT             | Power-Amplifier Output. Requires a pullup inductor to the supply voltage (or ROUT if envelope shaping is desired), which can be part of the output-matching network to an antenna.                                                                                                                                        |  |  |  |

| 6                   | AV <sub>DD</sub>  | Analog Power-Supply Voltage. AV <sub>DD</sub> is connected to an on-chip +3.0V regulator in 5V operation. Bypass AV <sub>DD</sub> to GND with a 0.1µF and 220pF capacitor placed as close to the pin as possible.                                                                                                         |  |  |  |

| 7                   | LNAIN             | Low-Noise Amplifier Input. Must be AC-coupled.                                                                                                                                                                                                                                                                            |  |  |  |

| 8                   | LNASRC            | Low-Noise Amplifier Source for External Inductive Degeneration. Connect an inductor to GND to set the LNA input impedance.                                                                                                                                                                                                |  |  |  |

| 9                   | LNAOUT            | Low-Noise Amplifier Output. Must be connected to AV <sub>DD</sub> through a parallel LC tank filter. AC-couple to MIXIN+.                                                                                                                                                                                                 |  |  |  |

| 10                  | MIXIN+            | Noninverting Mixer Input. Must be AC-coupled to the LNA output.                                                                                                                                                                                                                                                           |  |  |  |

| 11                  | MIXIN-            | Inverting Mixer Input. Bypass to AV <sub>DD</sub> with a capacitor as close to the LNA LC tank filter as possible.                                                                                                                                                                                                        |  |  |  |

| 12                  | MIXOUT            | 330Ω Mixer Output. Connect to the input of the 10.7MHz filter.                                                                                                                                                                                                                                                            |  |  |  |

| 13                  | IFIN-             | Inverting 330Ω IF Limiter Amplifier Input. Bypass to GND with a capacitor.                                                                                                                                                                                                                                                |  |  |  |

| 14                  | IFIN+             | Noninverting 330Ω IF Limiter Amplifier Input. Connect to the output of the 10.7MHz IF filter.                                                                                                                                                                                                                             |  |  |  |

| 15                  | PDMIN             | Minimum-Level Peak Detector for Demodulator Output                                                                                                                                                                                                                                                                        |  |  |  |

| 16                  | PDMAX             | Maximum-Level Peak Detector for Demodulator Output                                                                                                                                                                                                                                                                        |  |  |  |

| 17                  | DS-               | Inverting Data Slicer Input                                                                                                                                                                                                                                                                                               |  |  |  |

| 18                  | DS+               | Noninverting Data Slicer Input                                                                                                                                                                                                                                                                                            |  |  |  |

| 19                  | OP+               | Noninverting Op-Amp Input for the Sallen-Key Data Filter                                                                                                                                                                                                                                                                  |  |  |  |

| 20                  | DF                | Data-Filter Feedback Node. Input for the feedback capacitor of the Sallen-Key data filter.                                                                                                                                                                                                                                |  |  |  |

| 21                  | RSSI              | Buffered Received-Signal-Strength-Indicator Output                                                                                                                                                                                                                                                                        |  |  |  |

| 22                  | T/R               | Transmit/Receive. Drive high to put the device in transmit mode. Drive low or leave unconnected to put the device in receive mode. It is internally pulled down.                                                                                                                                                          |  |  |  |

| 23                  | ENABLE            | Enable. Drive high for normal operation. Drive low or leave unconnected to put the device into shutdown mode.                                                                                                                                                                                                             |  |  |  |

| 24                  | DATA              | Receiver Data Output/Transmitter Data Input                                                                                                                                                                                                                                                                               |  |  |  |

| 25                  | N.C.              | No Connection. Do not connect to this pin.                                                                                                                                                                                                                                                                                |  |  |  |

| 26                  | DV <sub>DD</sub>  | Digital Power-Supply Voltage. Bypass to GND with a 0.01µF and 220pF capacitor placed as close the pin as possible.                                                                                                                                                                                                        |  |  |  |

| 27                  | HVIN              | High-Voltage Supply Input. For 3V operation, connect $HV_{IN}$ to $AV_{DD}$ , $PAV_{DD}$ , and $DV_{DD}$ . For 5V operation, tie only $HV_{IN}$ to 5V. Bypass $HV_{IN}$ to GND with a 0.01 $\mu$ F and 220 $\mu$ F capacitor placed as close to the pin as possible.                                                      |  |  |  |

#### Pin Description (continued)

| www.d | atasheet4u.con | n       |                                                                                                |

|-------|----------------|---------|------------------------------------------------------------------------------------------------|

|       | PIN            | NAME    | FUNCTION                                                                                       |

|       | 28             | AUTOCAL | Enable for FSK demodulator autocalibration (~1min cycle). Bypass to GND with a 10pF capacitor. |

|       | 29             | AGC1    | AGC Enable/Dwell Time Control 1. See Table 1. Bypass to GND with a 10pF capacitor.             |

|       | 30             | AGC0    | AGC Enable/Dwell Time Control 0 (LSB). See Table 1. Bypass to GND with a 10pF capacitor.       |

|       | 31             | XTAL1   | Crystal Input 1. Bypass to GND if XTAL2 is driven by an AC-coupled external reference.         |

|       | 32             | XTAL2   | Crystal Input 2. XTAL2 can be driven from an external AC-coupled reference.                    |

|       | EP             | GND     | Exposed Paddle. Solder evenly to the board's ground plane for proper operation.                |

#### **Detailed Description**

The MAX7031 308MHz, 315MHz, and 433.92MHz CMOS transceiver and a few external components provide a complete transmit and receive chain from the antenna to the digital data interface. This device is designed for transmitting and receiving FSK data. All transmit frequencies are generated by a fractional-N-based synthesizer, allowing for very fine frequency steps in increments of  $f_{\text{XTAL}}$  / 4096. The receive local oscillator (LO) is generated by a traditional integer-N-based synthesizer. Depending on component selection, data rates as high as 33kbps (Manchester encoded) or 66kbps (NRZ encoded) can be achieved.

#### Receiver

#### Low-Noise Amplifier (LNA)

The LNA is a cascode amplifier with off-chip inductive degeneration that achieves approximately 30dB of voltage gain that is dependent on both the antenna-matching network at the LNA input, and the LC tank network between the LNA output and the mixer inputs.

The off-chip inductive degeneration is achieved by connecting an inductor from LNASRC to AGND. This inductor sets the real part of the input impedances at LNAIN, allowing for a more flexible match for low-input impedances such as a PC board trace antenna. A nominal value for this inductor with a 50 $\Omega$  input impedance is 12nH at 315MHz and 10nH at 434MHz, but the inductance is affected by PC board trace length. LNASRC can be shorted to ground to increase sensitivity by approximately 1dB, but the input match must then be reoptimized.

The LC tank filter connected to LNAOUT consists of L5 and C9 (see the *Typical Application Circuit*). Select L5 and C9 to resonate at the desired RF input frequency. The resonant frequency is given by:

$$f = \frac{1}{2\pi\sqrt{L_{TOTAL} \times C_{TOTAL}}}$$

where  $L_{TOTAL} = L_5 + L_{PARASITICS}$  and  $C_{TOTAL} = C_9 + C_{PARASITICS}$ .

LPARASITICS and CPARASITICS include inductance and capacitance of the PC board traces, package pins, mixer input impedance, LNA output impedance, etc. These parasitics at high frequencies cannot be ignored, and can have a dramatic effect on the tank filter center frequency. Lab experimentation should be done to optimize the center frequency of the tank. The parasitic capacitance is generally 5pF to 7pF.

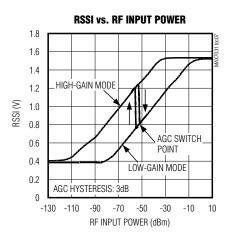

#### Automatic Gain Control (AGC)

When the AGC is enabled, it monitors the RSSI output. When the RSSI output reaches 1.28V, which corresponds to an RF input level of approximately -55dBm, the AGC switches on the LNA gain-reduction attenuator. The attenuator reduces the LNA gain by 36dB, thereby reducing the RSSI output by about 540mV to 740mV. The LNA resumes high-gain mode when the RSSI output level drops back below 680mV (approximately -59dBm at the RF input) for a programmable interval called the AGC dwell time (see Table 1). The AGC has a hysteresis of approximately 4dB. With the AGC function, the RSSI dynamic range is increased. AGC is not necessary for most FSK applications.

#### AGC Dwell Time Settings

The AGC dwell timer holds the AGC in a low-gain state for a set amount of time after the power level drops below the AGC switching threshold. After that set amount of time, if the power level is still below the AGC threshold, the LNA goes into high-gain state.

Table 1. AGC Dwell Time Settings for w.dMAX7031

| AGC1 | AGC0 | DESCRIPTION                      |  |

|------|------|----------------------------------|--|

| 0    | 0    | AGC disabled, high gain selected |  |

| 0    | 1    | K = 11, short dwell time         |  |

| 1    | 0    | 0 K = 14, medium dwell time      |  |

| 1    | 1    | K = 20, long dwell time          |  |

The MAX7031 uses the two AGC control pins (AGC0 and AGC1) to enable or disable the AGC and set three user-controlled dwell timer settings. The AGC dwell time is dependent on the crystal frequency and the bit settings of the AGC control pins. To calculate the dwell time, use the following equation:

Dwell Time =

$$\frac{2^K}{f_{XTAL}}$$

where K is an integer in decimal, determined by the control pin settings shown in Table 1.

For example, a receiver operating at 315MHz has a crystal oscillator frequency of 12.679MHz. For K=11 (AGC setting = 0, 1), the dwell timer is 162 $\mu$ s; for K=14 (AGC setting = 1, 0), the dwell timer is 1.3ms; for K=20 (AGC setting = 1, 1), the dwell time is 83ms.

#### Mixer

A unique feature of the MAX7031 is the integrated image rejection of the mixer. This eliminates the need for a costly front-end SAW filter for many applications. The advantage of not using a SAW filter is increased sensitivity, simplified antenna matching, less board space, and lower cost.

The mixer cell is a pair of double-balanced mixers that perform an IQ downconversion of the RF input to the 10.7MHz intermediate frequency (IF) with low-side injection (i.e.,  $f_{LO} = f_{RF} - f_{IF}$ ). The image-rejection circuit

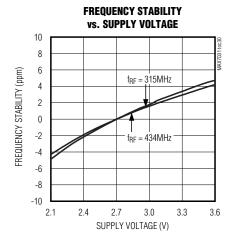

Figure 1. FSK Demodulator PLL Block Diagram

then combines these signals to achieve a typical 46dB of image rejection over the full temperature range. Low-side injection is required as high-side injection is not possible due to the on-chip image rejection. The IF output is driven by a source follower, biased to create a driving impedance of  $330\Omega$  to interface with an off-chip  $330\Omega$  ceramic IF filter. The voltage conversion gain driving a  $330\Omega$  load is approximately 20dB. Note that the MIXIN+ and MIXIN- inputs are functionally identical.

#### Integer-N, Phase-Locked Loop (PLL)

The MAX7031 utilizes a fixed integer-N PLL to generate the receive LO. All PLL components, including the loop filter, voltage-controlled oscillator, charge pump, asynchronous 24x divider, and phase-frequency detector are internal. The loop bandwidth is approximately 500kHz. The relationship between RF, IF, and reference frequencies is given by:

$$f_{REF} = (f_{RF} - f_{IF}) / 24$$

#### Intermediate Frequency (IF)

The IF section presents a differential  $330\Omega$  load to provide matching for the off-chip ceramic filter. The internal six AC-coupled limiting amplifiers produce an overall gain of approximately 65dB, with a bandpass filter-type response centered near the 10.7MHz IF frequency with a 3dB bandwidth of approximately 10MHz. The RSSI circuit demodulates the IF to baseband by producing a DC output proportional to the log of the IF signal level with a slope of approximately 15mV/dB.

#### FSK Demodulator

The FSK demodulator uses an integrated 10.7MHz PLL that tracks the input RF modulation and converts the frequency deviation into a voltage difference. The PLL is illustrated in Figure 1. The input to the PLL comes from the output of the IF limiting amplifiers. The PLL control voltage responds to changes in the frequency of the input signal with a nominal gain of 2.0mV/kHz. For example, an FSK peak-to-peak deviation of 50kHz

Figure 2. Sallen-Key Lowpass Data Filter

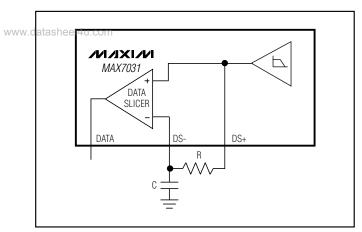

Figure 3. Generating Data Slicer Threshold Using a Lowpass Filter

generates a 100mV<sub>P-P</sub> signal on the control line. This control voltage is then filtered and sliced by the baseband circuitry.

The FSK demodulator PLL requires calibration to overcome variations in process, voltage, and temperature. This is done by using the AUTOCAL pin, or by cycling the ENABLE pin. If the AUTOCAL pin is a logic 1, calibration occurs approximately every minute. If the AUTOCAL pin is a logic 0, calibration occurs only after the MAX7031 is enabled.

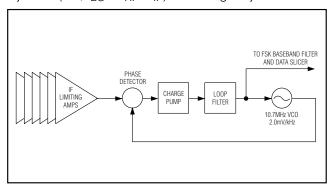

#### Data Filter

The data filter for the demodulated data is implemented as a 2nd-order, lowpass Sallen-Key filter. The pole locations are set by the combination of two on-chip resistors and two external capacitors. Adjusting the value of the external capacitors changes the corner frequency to optimize for different data rates. Set the corner frequency in kHz to approximately 2 times the fastest expected Manchester data rate in kbps from the transmitter (1.0 times the fastest expected NRZ data rate). Keeping the corner frequency near the data rate rejects any noise at higher frequencies, resulting in an increase in receiver sensitivity.

Table 2. Coefficients to Calculate CF1 and CF2

| FILTER TYPE             | а      | b     |

|-------------------------|--------|-------|

| Butterworth (Q = 0.707) | 1.414  | 1.000 |

| Bessel<br>(Q = 0.577)   | 1.3617 | 0.618 |

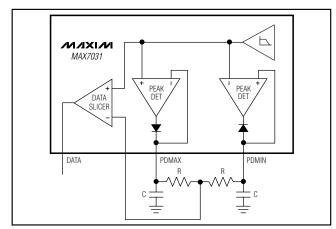

Figure 4. Generating Data Slicer Threshold Using the Peak Detectors

The configuration shown in Figure 2 can create a Butterworth or Bessel response. The Butterworth filter offers a very-flat-amplitude response in the passband and a rolloff rate of 40dB/decade for the two-pole filter. The Bessel filter has a linear phase response, which works well for filtering digital data. To calculate the value of the capacitors, use the following equations, along with the coefficients in Table 2:

$$C_{F1} = \frac{b}{a(100k\Omega)(\pi)(f_C)}$$

$$C_{F2} = \frac{a}{4(100k\Omega)(\pi)(f_C)}$$

where fC is the desired 3dB corner frequency.

For example, choose a Butterworth filter response with a corner frequency of 5kHz:

$$\begin{split} C_{F1} &= \frac{1.000}{(1.414)(100k\Omega)(3.14)(5kHz)} \approx 450 \text{pF} \\ C_{F2} &= \frac{1.414}{(4)(100k\Omega)(3.14)(5kHz)} \approx 225 \text{pF} \end{split}$$

Choosing standard capacitor values changes  $C_{F1}$  to 470pF and  $C_{F2}$  to 220pF. In the *Typical Application Circuit*,  $C_{F1}$  and  $C_{F2}$  are named C16 and C17, respectively.

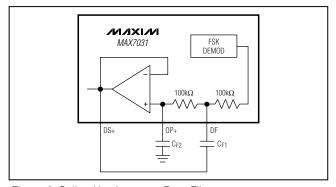

#### Data Slicer

The data slicer takes the analog output of the data filter and converts it to a digital signal. This is achieved by using a comparator and comparing the analog input to a threshold voltage. The threshold voltage is set by the voltage on the DS- pin, which is connected to the negative input of the data-slicer comparator.

Numerous configurations can be used to generate the data-slicer threshold. For example, the circuit in Figure 3 shows a simple method using only one resistor and one capacitor. This configuration averages the analog output of the filter and sets the threshold to approximately 50% of that amplitude. With this configuration, the threshold automatically adjusts as the analog signal varies, minimizing the possibility for errors in the digital data. The values of R and C affect how fast the threshold tracks the analog amplitude. Be sure to keep the corner frequency of the RC circuit much lower (about 10 times) than the lowest expected data rate.

With this configuration, a long string of NRZ zeros or ones can cause the threshold to drift. This configuration works best if a coding scheme, such as Manchester coding, which has an equal number of zeros and ones, is used.

Figure 4 shows a configuration that uses the positive and negative peak detectors to generate the threshold. This configuration sets the threshold to the midpoint between a high output and a low output of the data filter.

#### Peak Detectors

The maximum peak detector (PDMAX) and minimum peak detector (PDMIN), with resistors and capacitors shown in Figure 4, create DC output voltages equal to the high- and low-peak values of the filtered demodulated signal. The resistors provide a path for the capacitors to discharge, allowing the peak detectors to dynamically follow peak changes of the data filter output voltages.

The maximum and minimum peak detectors can be used together to form a data slicer threshold voltage at a value midway between the maximum and minimum voltage levels of the data stream (see the *Data Slicer* section and Figure 4). Set the RC time constant of the peak-detector combining network to at least 5 times the data period.

If there is an event that causes a significant change in the magnitude of the baseband signal, such as an AGC gain switch or a power-up transient, the peak detectors may "catch" a false level. If a false peak is detected, the slicing level is incorrect. The MAX7031 peak detectors correct these problems by temporarily tracking the incoming baseband filter voltage when an AGC state

switch occurs, or by forcing the peak detectors to track the baseband filter output voltage until all internal circuits are stable following an enable pin low-to-high transition. The peak detectors exhibit a fast attack/slow decay response. This feature allows for an extremely fast startup or AGC recovery.

#### **Transmitter**

#### Power Amplifier (PA)

The PA of the MAX7031 is a high-efficiency, opendrain, Class C amplifier. The PA with proper output-matching network can drive a wide range of antenna impedances, which includes a small-loop PC board trace and a  $50\Omega$  antenna. The output-matching network for a  $50\Omega$  antenna is shown in the Typical Application Circuit. The output-matching network suppresses the carrier harmonics and transforms the antenna impedance to an optimal impedance at PAOUT (pin 5). The optimal impedance at PAOUT is  $250\Omega$ .

When the output-matching network is properly tuned, the PA transmits power with a high overall efficiency of up to 32%. The efficiency of the PA itself is more than 46%. The output power is set by an external resistor at PAOUT, and is also dependent on the external antenna and antenna-matching network at the PA output.

#### Envelope Shaping

The MAX7031 features an internal envelope-shaping resistor, which connects between the open-drain output of the PA and the power supply. The envelope-shaping resistor slows the turn-on/turn-off of the PA. Envelope shaping is not necessary for FSK. For most applications, the PA pullup inductor should be tied to PAVDD instead of ROUT.

#### Fractional-N Phase-Locked Loop (PLL)

The MAX7031 utilizes a fully integrated, fractional-N PLL for its transmit frequency synthesizer. All PLL components, including the loop filter, are integrated internally. The loop bandwidth is approximately 200kHz.

#### **Power-Supply Connections**

The MAX7031 can be powered from a 2.1V to 3.6V supply or a 4.5V to 5.5V supply. If a 4.5V to 5.5V supply is used, then the on-chip linear regulator reduces the 5V supply to the 3V needed to operate the chip.

To operate the MAX7031 from a 3V supply, connect PAVDD, AVDD, DVDD, and HVIN to the 3V supply. When using a 5V supply, connect the supply to HVIN only and connect AVDD, PAVDD, and DVDD together. In both cases, bypass PAVDD, DVDD, and HVIN to GND with a 0.01 $\mu$ F and 220pF capacitor and bypass AVDD to GND with a 0.1 $\mu$ F and 220pF capacitor. Bypass T/R,

ENABLE, DATA, AGC0-1, and AUTOCAL with 10pF www.dcapacitors.to GND. Place all bypass capacitors as close to the respective pins as possible.

#### Transmit/Receive Antenna Switch

The MAX7031 features an internal SPST RF switch that, when combined with a few external components, allows the transmit and receive pins to share a common antenna (see the *Typical Application Circuit*). In receive mode, the switch is open and the power amplifier is shut down, presenting a high impedance to minimize the loading of the LNA. In transmit mode, the switch closes to complete a resonant tank circuit at the PA output and forms an RF short at the input to the LNA. In this mode, the external passive components couple the output of the PA to the antenna to protect the LNA input from strong transmitted signals.

The switch state is controlled by the  $T/\overline{R}$  pin (pin 22). Drive  $T/\overline{R}$  high to put the device in transmit mode; drive  $T/\overline{R}$  low to put the device in receive mode.

#### **Crystal Oscillator (XTAL)**

The XTAL oscillator in the MAX7031 is designed to present a capacitance of approximately 3pF between the XTAL1 and XTAL2 pins. In most cases, this corresponds to a 4.5pF load capacitance applied to the external crystal when typical PC board parasitics are added. It is very important to use a crystal with a load capacitance that is equal to the capacitance of the MAX7031 crystal oscillator plus PC board parasitics. If a crystal designed to oscillate with a different load capacitance is used, the crystal is pulled away from its stated operating frequency, introducing an error in the reference frequency. Crystals designed to operate with higher differential load capacitance always pull the reference frequency higher.

In actuality, the oscillator pulls every crystal. The crystal's natural frequency is really below its specified frequency, but when loaded with the specified load capacitance, the crystal is pulled and oscillates at its specified frequency. This pulling is already accounted for in the specification of the load capacitance.

Additional pulling can be calculated if the electrical parameters of the crystal are known. The frequency pulling is given by:

$$f_{P} = \frac{C_{m}}{2} \left( \frac{1}{C_{CASE} + C_{LOAD}} - \frac{1}{C_{CASE} + C_{SPEC}} \right) \times 10^{6}$$

where:

fp is the amount the crystal frequency is pulled in ppm.

Cm is the motional capacitance of the crystal.

CCASE is the case capacitance.

CSPEC is the specified load capacitance.

CLOAD is the actual load capacitance.

When the crystal is loaded as specified, i.e., CLOAD = CSPEC, the frequency pulling equals zero.

\_Chip Information

PROCESS: CMOS

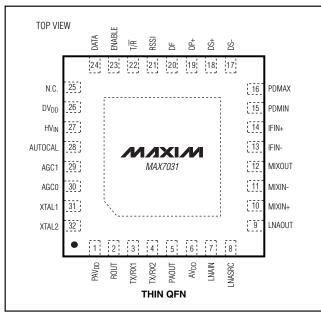

### Pin Configuration

### **Typical Application Circuit**

#### **Selector Guide**

| PART          | CARRIER<br>FREQUENCY (MHz) | FSK DEVIATION<br>FREQUENCY (kHz) |

|---------------|----------------------------|----------------------------------|

| MAX7031LATJ   | 308                        | ±51.413                          |

| MAX7031MATJ15 | 315                        | ±15.477                          |

| MAX7031MATJ50 | 315                        | ±49.528                          |

| MAX7031HATJ17 | 433.92                     | ±17.221                          |

| MAX7031HATJ51 | 433.92                     | ±51.663                          |

**Table 3. Component Values for Typical Application Circuit**

| COMPONENT | VALUE FOR<br>433.92MHz RF | VALUE FOR<br>315MHz RF | DESCRIPTION                     |

|-----------|---------------------------|------------------------|---------------------------------|

| C1        | 220pF                     | 220pF                  | 10%                             |

| C2        | 680pF                     | 680pF                  | 10%                             |

| C3        | 6.8pF                     | 12pF                   | 5%                              |

| C4        | 6.8pF                     | 10pF                   | 5%                              |

| C5        | 10pF                      | 22pF                   | 5%                              |

| C6        | 220pF                     | 220pF                  | 10%                             |

| C7        | 0.1µF                     | 0.1µF                  | 10%                             |

| C8        | 100pF                     | 100pF                  | 5%                              |

| C9        | 1.8pF                     | 2.7pF                  | ±0.1pF                          |

| C10       | 100pF                     | 100pF                  | 5%                              |

| C11       | 220pF                     | 220pF                  | 10%                             |

| C12       | 100pF                     | 100pF                  | 5%                              |

| C13       | 1500pF                    | 1500pF                 | 10%                             |

| C14       | 0.047µF                   | 0.047µF                | 10%                             |

| C15       | 0.047µF                   | 0.047µF                | 10%                             |

| C16       | 470pF                     | 470pF                  | 10%                             |

| C17       | 220pF                     | 220pF                  | 10%                             |

| C18       | 220pF                     | 220pF                  | 10%                             |

| C19       | 0.01µF                    | 0.01µF                 | 10%                             |

| C20       | 100pF                     | 100pF                  | 5%                              |

| C21       | 100pF                     | 100pF                  | 5%                              |

| C22       | 220pF                     | 220pF                  | 10%                             |

| C23       | 0.01µF                    | 0.01µF                 | 10%                             |

| C24       | 0.01µF                    | 0.01µF                 | 10%                             |

| L1        | 22nH                      | 27nH                   | Coilcraft 0603CS                |

| L2        | 22nH                      | 30nH                   | Coilcraft 0603CS                |

| L3        | 22nH                      | 30nH                   | Coilcraft 0603CS                |

| L4        | 10nH                      | 12nH                   | Coilcraft 0603CS                |

| L5        | 16nH                      | 30nH                   | Murata LQW18A                   |

| L6        | 68nH                      | 100nH                  | Coilcraft 0603CS                |

| R1        | 100kΩ                     | 100kΩ                  | 5%                              |

| R2        | 100kΩ                     | 100kΩ                  | 5%                              |

| R3        | 0Ω                        | 0Ω                     | _                               |

| Y1        | 17.63416MHz               | 12.67917MHz            | Crystal, 4.5pF load capacitance |

| Y2        | 10.7MHz ceramic filter    | 10.7MHz ceramic filter | Murata SFECV10.7 seri           |

Note: Component values vary depending on PC board layout.

#### Package Information

www.defne package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

|                                                              |                                                             | С                                | OMMO                              | IID NC                           | MENS                   | SIONS                          | 3                               |                           |                        |           |        |              |          |      |         | EX     | POSE                                                        | D PAD | VARI | ATION      | NS    |           |           |

|--------------------------------------------------------------|-------------------------------------------------------------|----------------------------------|-----------------------------------|----------------------------------|------------------------|--------------------------------|---------------------------------|---------------------------|------------------------|-----------|--------|--------------|----------|------|---------|--------|-------------------------------------------------------------|-------|------|------------|-------|-----------|-----------|

| PKG.                                                         | 16L 5x5                                                     |                                  | 20L 5x5                           |                                  |                        | 28L 5x5                        |                                 |                           | 32L 5x5                |           |        | 40L 5x5      |          |      | PKG     | D2     |                                                             |       | E2   |            |       | _L_       | DOWN      |

| SYMBOL                                                       | MIN. NOM                                                    | MAX.                             | MIN.                              | NOM.                             | MAX.                   | MIN.                           | NOM. MA                         | K. MIN.                   | NOM.                   | MAX.      | MIN.   | NOM.         | MAX.     |      | CODES   | MIN.   | NOM.                                                        | MAX   | MIN. | NOM        | MAX.  | ±0.15     | BONDS     |

| Α                                                            | 0.70 0.75                                                   | 0.80                             | 0.70                              | 0.75                             | 0.80                   | 0.70                           | 0.75 0.8                        | 0 0.70                    | 0.75                   | 0.80      | 0.70   | 0.75         | 0.80     |      | T1655-2 | 3.00   | 3.10                                                        | 3.20  | 3.00 | 3.10       | 3.20  | **        | YES       |

| A1                                                           | 0 0.02                                                      | 0.05                             | 0                                 | 0.02                             | 0.05                   | 0                              | 0.02 0.0                        | 5 0                       | 0.02                   | 0.05      | 0      | 0.02         | 0.05     |      | T1655-3 | 3.00   | 3.10                                                        | 3.20  | 3.00 | 3.10       | 3.20  | **        | NO        |

| A3                                                           | 0.20 REF.                                                   |                                  | 0.20 REF.                         |                                  | 0.20 REF.              |                                | -                               | 0.20 REF.                 |                        | 0.20 REF. |        |              | T1655N-1 | 3.00 | 3.10    | 3.20   | 3.00                                                        | 3.10  | 3.20 | **         | NO    |           |           |

| b                                                            | 0.25 0.30                                                   |                                  |                                   |                                  |                        |                                |                                 |                           |                        |           |        | 0.20         |          |      | T2055-3 | 3.00   | 3.10                                                        | 3.20  | 3.00 | 3.10       | 3.20  | **        | YES       |

| D                                                            | 4.90 5.00                                                   |                                  |                                   |                                  |                        | 4.90                           |                                 | 0 4.90                    |                        | 5.10      |        | 5.00         | 5.10     |      | T2055-4 | 3.00   | 3.10                                                        | 3.20  | 3.00 | 3.10       | 3.20  | **        | NO        |

| E                                                            | 4.90 5.00                                                   | _                                | _                                 | 65 BS                            | -                      |                                | 5.00   5.1<br>50 BSC            | -                         | 5.00<br>50 B           | _         | -      | 40 B         | _        |      | T2055-5 | 3.15   | 3.25                                                        | 3.35  | 3.15 | 3.25       | 3.35  | 0.40      | YES       |

| e<br>k                                                       | 0.80 B                                                      | SC.                              | 0.25                              | 00 BS                            | U.                     | 0 25                           | DU BSC.                         | 0.25                      |                        | SU.       | _      | 0.35         |          |      | T2855-3 | 3.15   | 3.25                                                        | 3.35  | 3.15 | 3.25       | 3.35  | **        | YES       |

| I I                                                          | 0.30 0.40                                                   | 0.50                             | 0.20                              | 0.55                             | 0.65                   | 0.120                          | 0.55 0.6                        | 0.20                      | +                      | 0.50      | 0.20   | 0.00         | 0.45     |      | T2855-4 | 2.60   | 2.70                                                        |       | 2.60 | 2.70       | 2.80  | **        | YES       |

| 11                                                           |                                                             | 0.50                             | 0.45                              | 0.55                             | 0.00                   | 0.45                           | 0.55 0.6                        | 5 0.30                    | 0.40                   | 0.50      | -      | 0.40         |          |      | T2855-5 | 2.60   | 2.70                                                        | 2.80  | 2.60 | 2.70       | 2.80  | **        | NO        |

| N                                                            | 16                                                          | -                                | -                                 | 20                               | -                      | -                              | 28                              | +-                        | 32                     | <u> </u>  | 0.30   | 40           | 0.50     |      | T2855-6 | 3.15   | 3.25                                                        | 3.35  | 3.15 | 3.25       | 3.35  | **        | NO        |

| ND                                                           | 4                                                           |                                  | 5                                 |                                  | 7                      |                                | +                               | 8                         |                        | 10        |        |              | T2855-7  | 2.60 | 2.70    | 2.80   | 2.60                                                        | 2.70  | 2.80 | **         | YES   |           |           |

| NE                                                           | 4                                                           |                                  | 5                                 |                                  | 7                      |                                | $\top$                          | 8                         |                        | 10        |        |              | T2855-8  | 3.15 | 3.25    | 3.35   | 3.15                                                        | 3.25  | 3.35 | 0.40       | YES   |           |           |

| JEDEC                                                        | В                                                           | WHHC                             |                                   |                                  | WHHD-1                 |                                | 1                               | WHHD-2                    |                        |           |        |              | T2855N-1 | 3.15 | 3.25    | 3.35   | 3.15                                                        | 3.25  | 3.35 | **         | NO    |           |           |

|                                                              |                                                             |                                  |                                   |                                  |                        |                                |                                 |                           |                        |           |        |              |          |      | T3255-3 | 3.00   | 3.10                                                        | 3.20  | 3.00 | 3.10       | 3.20  | **        | YES       |

| IOTES:                                                       |                                                             |                                  |                                   |                                  |                        |                                |                                 |                           |                        |           |        |              |          |      | T3255-4 | 3.00   | 3.10                                                        |       | 3.00 | 3.10       | 3.20  | **        | NO        |

| DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.      |                                                             |                                  |                                   |                                  |                        |                                |                                 |                           |                        |           |        | T3255-5      | 3.00     | 3.10 |         | 3.00   | 3.10                                                        | 3.20  | **   | YES        |       |           |           |

| 2. ALL DIMENSIONS ARE IN MILLIMETERS, ANGLES ARE IN DEGREES. |                                                             |                                  |                                   |                                  |                        |                                |                                 |                           |                        |           |        |              | T3255N-1 | 3.00 |         | 3.20   | 3.00                                                        | 3.10  | 3.20 | **         | NO    |           |           |

| 3. N IS                                                      | THE TOTA                                                    | L NUI                            | MBER                              | OF TE                            | RMIN                   | IALS.                          |                                 |                           |                        |           |        |              |          |      | T4055-1 | 3.20   | 3.30                                                        | 3.40  | 3.20 | 3.30       |       | **        | YES       |

| CON<br>OPT<br>IDEI                                           | TERMINA<br>NFORM TO<br>TONAL, BU<br>NTIFIER MA<br>ENSION ba | JESD<br>IT MUS<br>AY BE<br>APPLI | 95-1 S<br>ST BE<br>EITHE<br>ES TO | SPP-01<br>LOCA<br>ER A M<br>META | 12. D<br>TED 1<br>10LD | ETAIL<br>WITH<br>OR N<br>ED TE | S OF TE<br>N THE ZO<br>IARKED I | RMINAI<br>ONE IN<br>EATUR | L#1 ID<br>DICAT<br>RE. | ED. T     | FIER A | ARE<br>ERMIN | IAL #1   |      |         |        |                                                             |       |      | OLL O      | SAMON | DANIE 143 | IONS TABI |

|                                                              | AND NE RE                                                   |                                  |                                   |                                  |                        |                                |                                 | S ON E                    | ACH                    | D ANI     | ESI    | DE RE        | SPECT    | IVE  | LY.     |        |                                                             |       |      |            |       |           |           |

| 7. DEF                                                       | OPULATIO                                                    | N IS F                           | POSSI                             | BLE IN                           | A SY                   | YMME                           | TRICAL F                        | ASHIC                     | N.                     |           |        |              |          |      |         |        |                                                             |       |      |            |       |           |           |

| A COF                                                        | PLANARITY                                                   | 'APPL                            | JES T                             | O THE                            | EXP                    | OSEC                           | HEAT S                          | NK SLI                    | JG AS                  | WEL       | L AS   | HE T         | ERMIN.   | ALS. |         |        |                                                             |       |      |            |       |           |           |

|                                                              | WING CON                                                    |                                  |                                   | JEDE                             | СМС                    | )220,                          | EXCEPT                          | EXPOS                     | ED PA                  | AD DI     | MENS   | ION F        | OR       |      |         |        |                                                             |       |      |            |       |           |           |

| ^                                                            | RPAGE SH                                                    |                                  |                                   | CEED                             | 0 10                   | mm                             |                                 |                           |                        |           |        |              |          |      |         |        |                                                             |       | AC   | 48         | 48    | 4170      | . 40      |

|                                                              | . MARKING IS FOR PACKAGE ORIENTATION REFERENCE ONLY.        |                                  |                                   |                                  |                        |                                |                                 |                           |                        |           |        |              |          |      | ᆘᇪ      | MICOND | UCTOR .                                                     | N     |      | <b>1</b> X |       |           |           |

|                                                              | 2. NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY.            |                                  |                                   |                                  |                        |                                |                                 |                           |                        |           |        |              |          | ļ    |         |        |                                                             |       |      |            |       |           |           |

|                                                              |                                                             |                                  |                                   |                                  |                        |                                |                                 |                           |                        |           |        |              |          |      |         |        | PACKAGE OUTLINE,<br>16, 20, 28, 32, 40L THIN QFN, 5x5x0.8mm |       |      |            |       |           |           |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_\_\_\_\_\_