Jun 13, 2001 Ver. 3.1

# 16/32 BIT RISC/DSP

# GMS30C2116 GMS30C2132

**USER'S MANUAL**

# **Revision 3.1** Published by IDA Team in Hynix Semiconductor Inc. " ÏHynix Semiconductor 2001. All Right Reserved. Hynix Offices in Korea or Distributors and Representatives listed at address directory may serve

Hynix reserves the right to make changes to any Information here in at any time without notice.

The information, diagrams, and other data in this manual are correct and reliable; however, Hynix is in no way responsible for any violations of patents or other rights of the third party generated by the

additional information of this manual.

use of this manual.

Specifications and information in this document are subject to change without notice and do not represent a commitment on the part of Hynix. Hynix reserves the right to make changes to improve functioning. Although the information in this document has been carefully reviewed, Hynix does not assume any liability arising out of the use of the product or circuit described herein.

Hynix does not authorize the use of the Hynix microprocessor in life support applications wherein a failure or malfunction of the microprocessor may directly threaten life or cause injury. The user of the Hynix microprocessor in life support applications assumes all risks of such use and indemnifies Hynix against all damages.

For further information please contact:

SEOUL OFFICE: Hynix Semiconductor YOUNG DONG Bldg.

891, Daechi-dong, Kangnam-gu,

Seoul, Korea.

PHONE: (02) 3459-3662~3

FAX: (02) 3459-3942

SYSTEM IC: 1, Hyangjeong-dong, Hungduk-gu,

Cheongju, 361-725, Korea.

PHONE: (0431) 270-4030~47

FAX : (0431) 270-4075

TABLE OF CONTENTS

# **Table of Contents**

|    | 0.1 ( | GMS300                  | C2116/32 RISC/DSP                                     | 0-1  |

|----|-------|-------------------------|-------------------------------------------------------|------|

|    | 0.2 E | Block Di                | iagram                                                | 0-6  |

|    | 0.3 F | Pin Conf                | iguration                                             | 0-7  |

|    |       | 0.3.1                   | GMS30C2132, 160-Pin MQFP-Package - View from Top Side | 0-7  |

|    |       | 0.3.2                   | Pin Cross Reference by Pin Name                       | 0-8  |

|    |       | 0.3.3                   | Pin Fuction                                           | 0-9  |

| 1. | Arc   | hitectu                 | re                                                    |      |

|    | 1.1   | Introdu                 | action                                                | 1-1  |

|    |       | 1.1.1                   | RISC Architecture                                     | 1-1  |

|    |       | 1.1.2                   | Techniques to reduce CPI (Cycles per Instruction)     | 1-2  |

|    |       | 1.1.3                   | The pipeline structure of GMS30C2132                  | 1-6  |

|    | 1.2   | Global                  | Register Set                                          | 1-7  |

|    |       | 1.2.1                   | Program Counter PC, G0                                | 1-8  |

|    |       | 1.2.2                   | Status Register SR, G1                                | 1-9  |

|    |       | 1.2.3                   | Floating-Point Exception Register FER, G2             | 1-12 |

|    |       | 1.2.4                   | Stack Pointer SP, G18                                 | 1-13 |

|    |       | 1.2.5                   | Upper Stack Bound UB, G19                             | 1-13 |

|    |       | 1.2.6                   | Bus Control Register BCR, G20                         | 1-13 |

|    |       | 1.2.7                   | Timer Prescaler Register TPR, G21                     | 1-14 |

|    |       | 1.2.8                   | Timer Compare Register TCR, G22                       | 1-14 |

|    |       | 1.2.9                   | Timer Register TR, G23                                | 1-14 |

|    |       | 1.2.10                  | Watchdog Compare Register WCR, G24                    | 1-14 |

|    |       | 1.2.11                  | Input Status Register ISR, G25                        | 1-14 |

|    |       | 1.2.12                  | Function Control Register FCR, G26                    | 1-14 |

|    |       | 1.2.13                  | Memory Control Register MCR, G27                      | 1-15 |

|    | 1.3   | Local I                 | Register Set                                          | 1-15 |

|    | 1.4   | Privile                 | ge States                                             | 1-16 |

|    | 1.5   | Register Data Types1-17 |                                                       |      |

|    | 1.6   | Memor                   | ry Organization                                       | 1-18 |

|    | 1.7   | Stack                   |                                                       | 1-20 |

|    | 1.8   | Instruc                 | tion Cache                                            | 1-25 |

|    | 1.9   | On-Ch                   | ip Memory (IRAM)                                      | 1-28 |

|    |       |                         |                                                       |      |

ii TABLE OF CONTENTS

| Z. IIISH UCHOHS Genera | 2. Instructions Gen | era |

|------------------------|---------------------|-----|

|------------------------|---------------------|-----|

| 2.1      | Instruction Notation                          | 2-1  |

|----------|-----------------------------------------------|------|

| 2.2      | Instruction Execution                         | 2-2  |

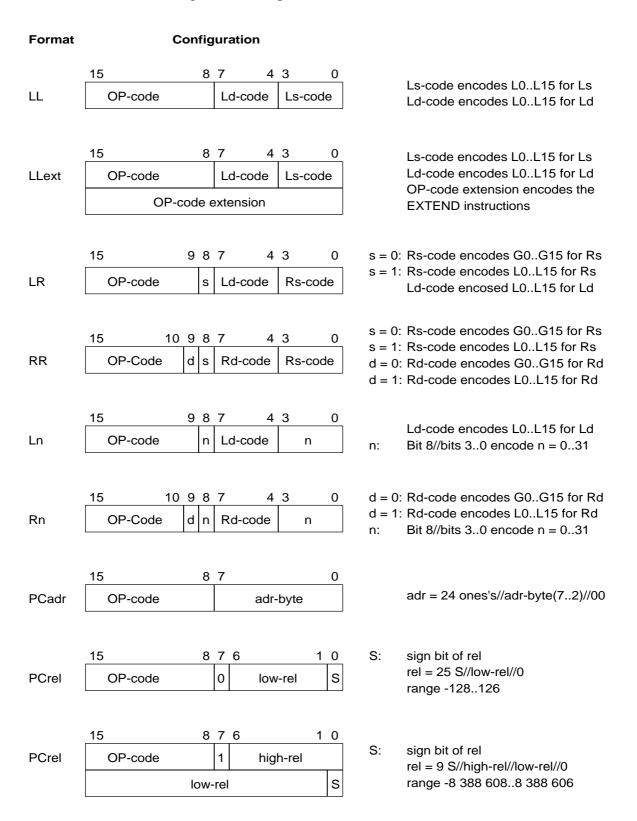

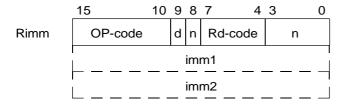

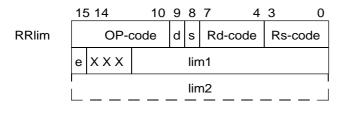

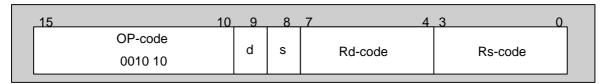

| 2.3      | Instruction Formats                           | 2-3  |

|          | 2.3.1 Table of Immediate Values               | 2-5  |

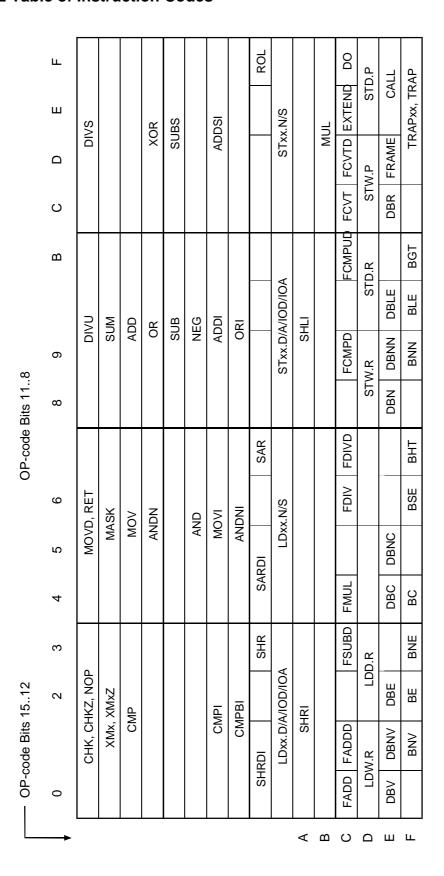

|          | 2.3.2 Table of Instruction Codes              | 2-6  |

|          | 2.3.3 Table of Extended DSP Instruction Codes | 2-7  |

| 2.4      | Entry Tables                                  | 2-8  |

| 2.5      | Instruction Timing                            | 2-12 |

| 3. Insti | ruction Set                                   |      |

|          |                                               | 2.1  |

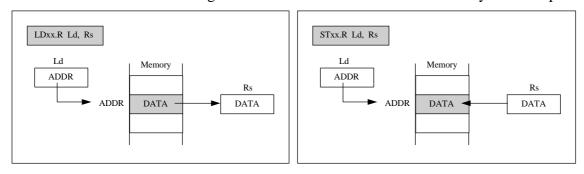

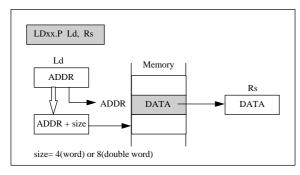

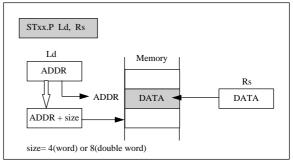

| 3.1      | Memory Instructions                           |      |

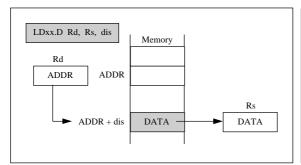

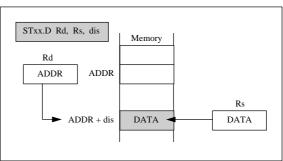

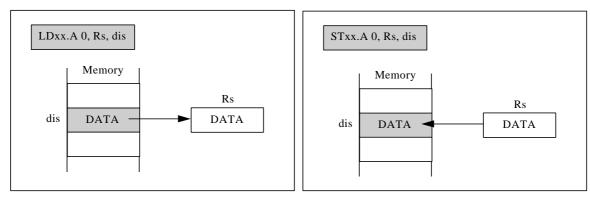

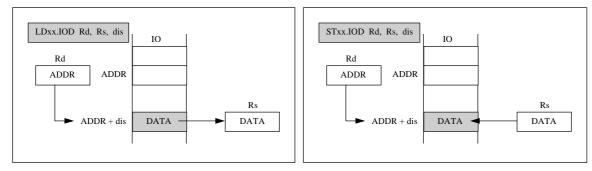

|          | 3.1.1 Address Modes                           |      |

|          | 3.1.2 Load Instructions.                      |      |

| 2.2      | 3.1.3 Store Instructions                      |      |

| 3.2      | Move Word Instructions                        |      |

| 3.3      | Move Double-Word Instruction                  |      |

| 3.4      | Logical Instructions                          |      |

| 3.5      | Invert Instruction                            |      |

| 3.6      | Mask Instruction                              |      |

| 3.7      | Add Instructions                              |      |

| 3.8      | Sum Instructions                              |      |

| 3.9      | Subtract Instructions                         |      |

| 3.10     | Negate Instructions                           |      |

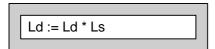

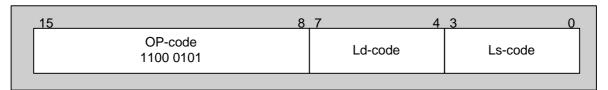

| 3.11     | Multiply Word Instruction                     |      |

| 3.12     | · · · · · · · · · · · · · · · · · · ·         |      |

| 3.13     | Divide Instructions                           |      |

| 3.14     | Shift Left Instructions                       |      |

| 3.15     | Shift Right Instructions                      |      |

| 3.16     |                                               |      |

| 3.17     |                                               |      |

| 3.18     | Check Instructions                            |      |

| 3.19     | No Operation Instruction                      |      |

| 3.20     | 1                                             |      |

| 3.21     | Compare Bit Instructions                      |      |

| 3.22     | 8                                             |      |

| 3.23     | Set Stack Address Instruction                 |      |

| 3.24     | Set Conditional Instructions                  |      |

| 3.25     |                                               |      |

| 3.26     | Delayed Branch Instructions                   | 3-31 |

TABLE OF CONTENTS iii

| 3.27   | 7 Call I  | Instruction       |                                       | 3-33 |  |  |

|--------|-----------|-------------------|---------------------------------------|------|--|--|

| 3.28   | 3 Trap    | Trap Instructions |                                       |      |  |  |

| 3.29   | 9 Fram    | e Instructio      | on                                    | 3-35 |  |  |

| 3.30   | ) Retur   | eturn Instruction |                                       |      |  |  |

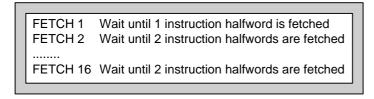

| 3.31   | l Fetch   | etch Instruction  |                                       |      |  |  |

| 3.32   | 2 Exter   | nded DSP I        | nstructions                           | 3-39 |  |  |

| 3.33   | 3 Softw   | are Instru        | ctions                                | 3-41 |  |  |

|        | 3.33.1    | Do Instr          | ruction                               | 3-42 |  |  |

|        | 3.33.2    | Floating          | -Point Instructions                   | 3-43 |  |  |

| 4. Exc | eptions   | S                 |                                       |      |  |  |

| 4.1    | -         |                   | sing                                  |      |  |  |

| 4.2    | Except    |                   |                                       |      |  |  |

|        | 4.2.1     |                   |                                       |      |  |  |

|        | 4.2.2     | _                 | ointer, Frame and Privilege Error     |      |  |  |

|        | 4.2.3     |                   | Overflow                              |      |  |  |

|        | 4.2.4     | -                 | or                                    |      |  |  |

|        | 4.2.5     | -                 |                                       |      |  |  |

|        | 4.2.6     | Trace Ex          | ception                               | 4-3  |  |  |

| 4.3    | Except    | tion Backtı       | racking                               | 4-4  |  |  |

| 5. Tim | ner       |                   |                                       |      |  |  |

| 5.1    | Overvi    | ew                |                                       | 5-1  |  |  |

|        | 5.1.1     | Timer Pro         | escaler Register TPR                  | 5-1  |  |  |

|        | 5.1.2     | Timer Re          | gister TR                             | 5-2  |  |  |

|        | 5.1.3     | Timer Co          | ompare Register TCR                   | 5-2  |  |  |

| 6. Bus | s Interfa | ace               |                                       |      |  |  |

| 6.1    | Bus Co    | ontrol Gen        | eral                                  | 6-1  |  |  |

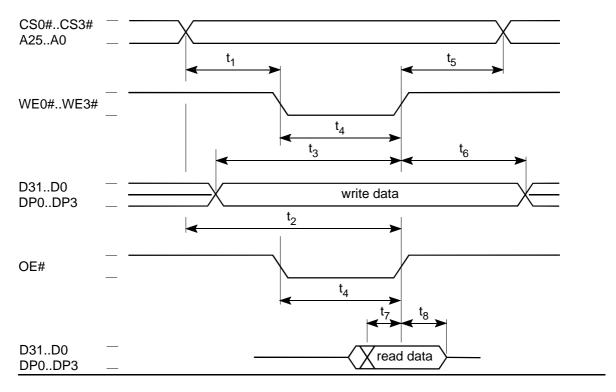

|        | 6.1.1     | SRAM an           | nd ROM Bus Access                     | 6-1  |  |  |

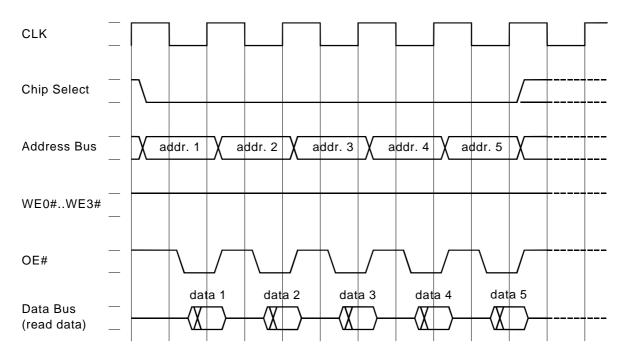

|        |           | 6.1.1.1           | SRAM and ROM Single-Cycle Read Access | 6-2  |  |  |

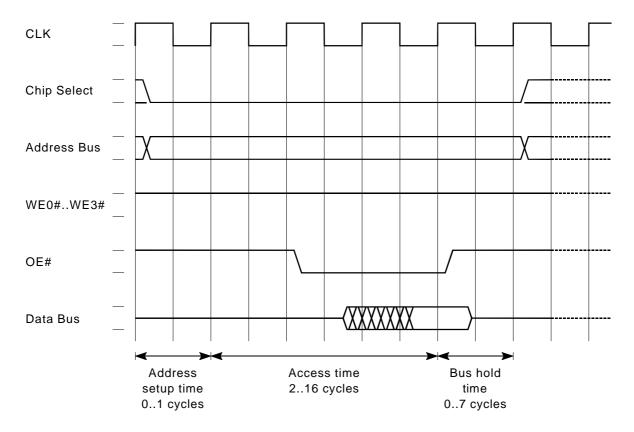

|        |           | 6.1.1.2           | SRAM and ROM Multi-Cycle Read Access  | 6-2  |  |  |

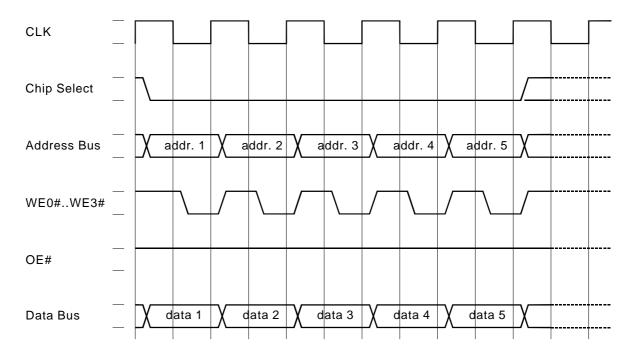

|        |           | 6.1.1.3           | SRAM Single-Cycle Write Access        | 6-3  |  |  |

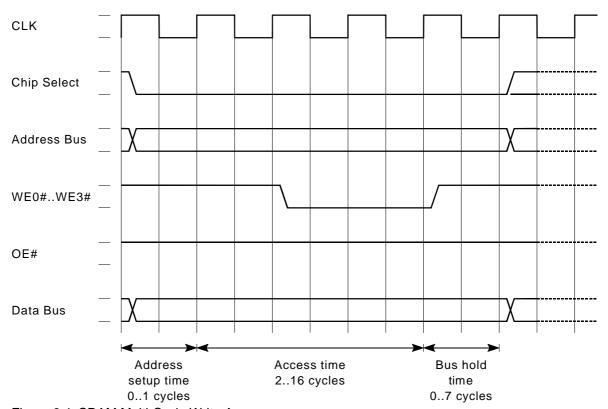

|        |           | 6.1.1.4           | SRAM Multi-Cycle write Access         | 6-3  |  |  |

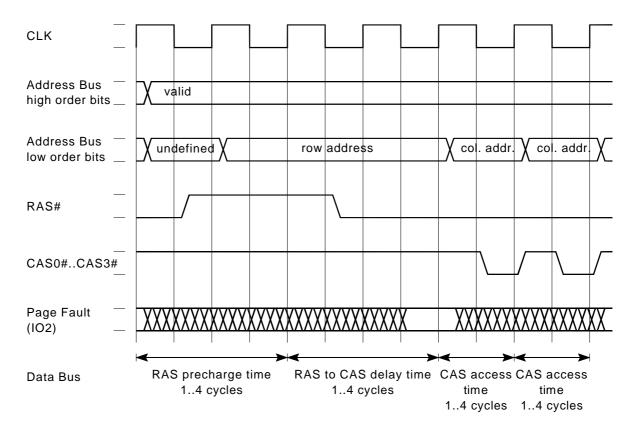

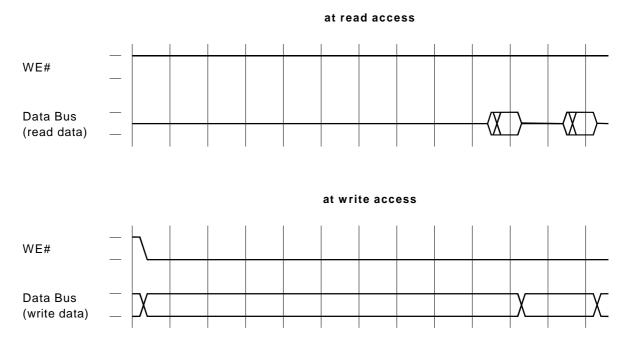

|        | 6.1.2     | DRAM E            | Sus Access                            | 6-4  |  |  |

|        |           | 6.1.2.1           | DRAM Access                           | 6-5  |  |  |

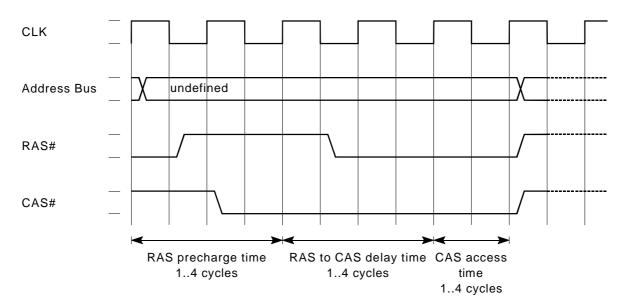

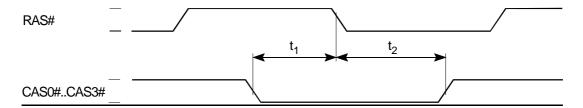

|        |           | 6.1.2.2           | DRAM Refresh (CAS before RAS Refresh) | 6-6  |  |  |

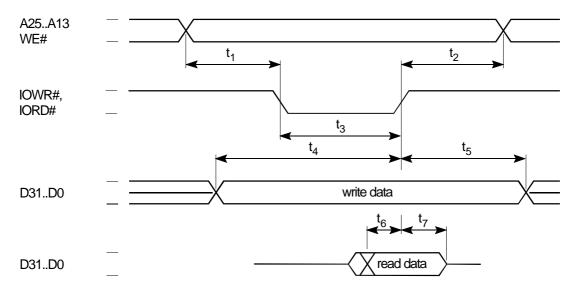

|        | 6.1.3     | I/O Bus A         | Access                                | 6-7  |  |  |

|        |           | 6.1.3.1           | I/O Read Access                       | 6-7  |  |  |

|        |           | 6.1.3.2           | I/O Write Access                      | 6-8  |  |  |

iv TABLE OF CONTENTS

| I/O Bu   | O Bus Control6-9                                                                                                                                                                                                                            |                                                                             |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|

| Bus Co   | ontrol Register BCR6-10                                                                                                                                                                                                                     |                                                                             |  |  |  |  |

| Memor    | ry Control Register MCR                                                                                                                                                                                                                     | 6-13                                                                        |  |  |  |  |

| 6.4.1    | Output Voltage6-                                                                                                                                                                                                                            |                                                                             |  |  |  |  |

| 6.4.2    | Input Threshold                                                                                                                                                                                                                             | 6-14                                                                        |  |  |  |  |

| 6.4.3    | Power Down                                                                                                                                                                                                                                  | 6-14                                                                        |  |  |  |  |

| 6.4.4    | IRAM Refresh Test                                                                                                                                                                                                                           | 6-15                                                                        |  |  |  |  |

| 6.4.5    | IRAM Refresh Rate6-1                                                                                                                                                                                                                        |                                                                             |  |  |  |  |

| 6.4.6    | Entry Table Map                                                                                                                                                                                                                             | 6-15                                                                        |  |  |  |  |

| 6.4.7    | MEMx Bus Hold Break                                                                                                                                                                                                                         | 6-15                                                                        |  |  |  |  |

| Input S  | tatus Register ISR                                                                                                                                                                                                                          | 6-16                                                                        |  |  |  |  |

| Function | on Control Register FCR                                                                                                                                                                                                                     | 6-17                                                                        |  |  |  |  |

| Watch    | dog Compare Register WCR                                                                                                                                                                                                                    | 6-19                                                                        |  |  |  |  |

| IO3 Co   | ontrol Modes                                                                                                                                                                                                                                | 6-19                                                                        |  |  |  |  |

| 6.8.1    | IO3Standard Mode                                                                                                                                                                                                                            | 6-19                                                                        |  |  |  |  |

| 6.8.2    | Watchdog Mode                                                                                                                                                                                                                               | 6-19                                                                        |  |  |  |  |

| 6.8.3    | IO3Timing Mode                                                                                                                                                                                                                              | 6-20                                                                        |  |  |  |  |

| 6.8.4    | IO3TimerInterrupt Mode                                                                                                                                                                                                                      | 6-20                                                                        |  |  |  |  |

| Bus Sig  | gnals                                                                                                                                                                                                                                       | 6-21                                                                        |  |  |  |  |

| 6.9.1    | Bus Signals for the GMS30C2132 Processor                                                                                                                                                                                                    | 6-21                                                                        |  |  |  |  |

| 6.9.2    | Bus Signals for the GMS30C2116 Processor                                                                                                                                                                                                    | 6-22                                                                        |  |  |  |  |

| 6.9.3    | Bus Signal Description                                                                                                                                                                                                                      | 6-23                                                                        |  |  |  |  |

| DC C     | haracteristics                                                                                                                                                                                                                              | 6-27                                                                        |  |  |  |  |

| AC C     | haracteristics                                                                                                                                                                                                                              | 6-29                                                                        |  |  |  |  |

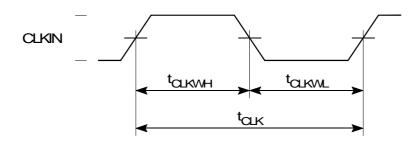

| 6.11.1   | Processor Clock                                                                                                                                                                                                                             | 6-29                                                                        |  |  |  |  |

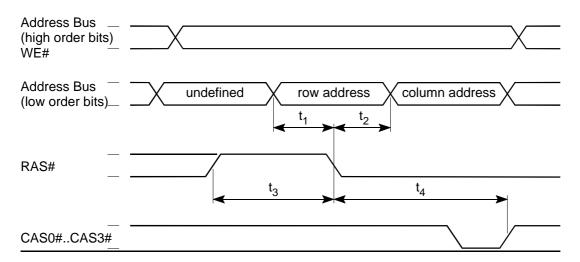

| 6.11.2   | DRAM RAS Access                                                                                                                                                                                                                             | 6-30                                                                        |  |  |  |  |

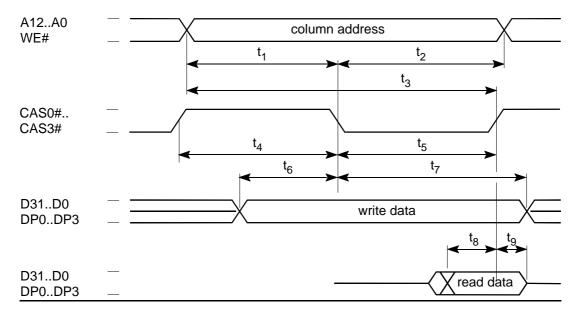

| 6.11.3   | DRAM Fast Page Mode Access                                                                                                                                                                                                                  | 6-31                                                                        |  |  |  |  |

|          | 6.11.3.1 Multi-Cycle Access                                                                                                                                                                                                                 | 6-31                                                                        |  |  |  |  |

|          | 6.11.3.2 Single-Cycle Access                                                                                                                                                                                                                | 6-32                                                                        |  |  |  |  |

| 6.11.4   | DRAM CAS-Before-RAS Refresh                                                                                                                                                                                                                 | 6-34                                                                        |  |  |  |  |

| 6.11.5   | SRAM Access                                                                                                                                                                                                                                 | 6-35                                                                        |  |  |  |  |

|          | 6.11.5.1 Multi-Cycle Access                                                                                                                                                                                                                 | 6-35                                                                        |  |  |  |  |

|          | 6.11.5.2 Single-Cycle Access                                                                                                                                                                                                                | 6-37                                                                        |  |  |  |  |

| 6.11.6   |                                                                                                                                                                                                                                             |                                                                             |  |  |  |  |

|          | Bus Co<br>Memor<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>6.4.5<br>6.4.6<br>6.4.7<br>Input S<br>Function<br>Watcher<br>IO3 Co<br>6.8.1<br>6.8.2<br>6.8.3<br>6.8.4<br>Bus Sig<br>6.9.1<br>6.9.2<br>6.9.3<br>DC Co<br>6.11.1<br>6.11.2<br>6.11.3 | Bus Control Register BCR  Memory Control Register MCR  6.4.1 Output Voltage |  |  |  |  |

TABLE OF CONTENTS

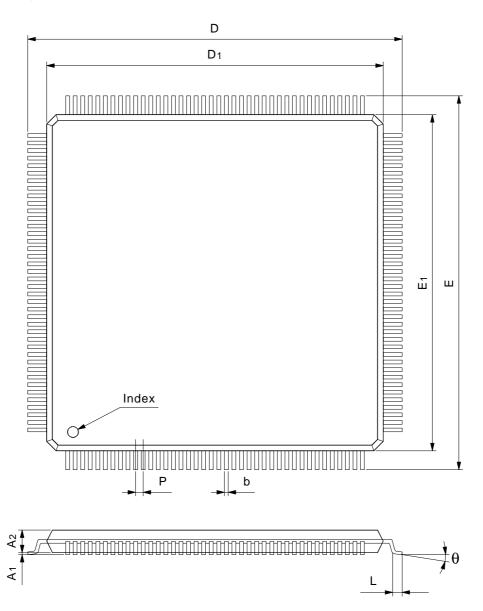

# 7. Mechanical Data

| 7.1 | GMS   | 30C2132, 160-Pin MQFP-Package          | 7-1 |

|-----|-------|----------------------------------------|-----|

|     | 7.1.1 | Pin Configuration - View from Top Side | 7-1 |

|     | 7.1.2 | Pin Cross Reference by Pin Name        | 7-2 |

|     | 7.1.3 | Pin Cross Reference by Location        | 7-3 |

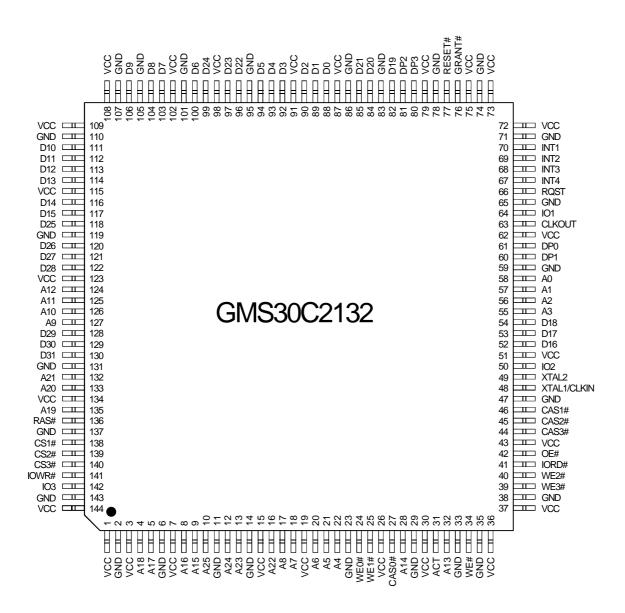

| 7.2 | GMS   | 30C2132, 144-Pin TQFP-Package          | 7-4 |

|     | 7.2.1 | Pin Configuration - View from Top Side | 7-4 |

|     | 7.2.2 | Pin Cross Reference by Pin Name        | 7-5 |

|     | 7.2.3 | Pin Cross Reference by Location        | 7-6 |

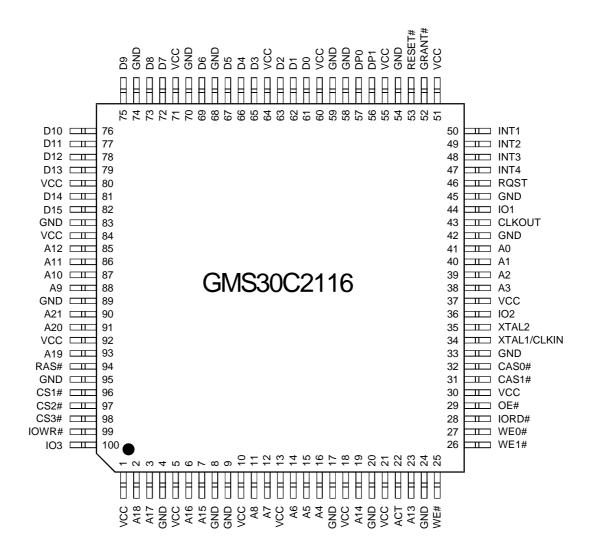

| 7.3 |       | 30C2116, 100-Pin TQFP-Package          |     |

|     | 7.3.1 | Pin Configuration - View from Top Side | 7-7 |

|     |       | Pin Cross Reference by Pin Name        |     |

|     |       | Pin Cross Reference by Location        |     |

| 7.4 |       | ge-Dimensions                          |     |

# Appendix. Instruction Set Details

Overview 0-1

# 0. Overview

# 0.1 GMS30C2116/32 RISC/DSP

The GMS30C2116 and GMS30C2132 RISC/DSP present a new class of microprocessors: The combination of a high-performance *RISC* microprocessor with an additional powerful *DSP instruction set* and *on-chip micro-controller functions*. The high throughput is not achieved by raw clock speed, it is due to a sophisticated novel architecture, combining the advantages of RISC and DSP technology.

The speed is obtained by an optimized combination of the following features:

- i "The most recent stack frames are kept in a register stack, thereby reducing data memory accesses to a minimum by keeping almost all local data in registers.

- i #Pipelined memory access allows overlapping of memory accesses with execution.

- i ü4KByte on-chip memory.

- i # On-chip instruction cache omits instruction fetch in inner loops and provides pre-fetch.

- i *Wariable-length instructions* of 16, 32 or 48 bits provide a large, powerful instruction set, thereby reducing the number of instructions to be executed.

- i Primarily used 16-bit instructions halve the memory bandwidth required for instruction fetch in comparison to conventional RISC architectures with fixed-length 32-bit instructions, yielding also even better code economy than conventional CISC architectures.

- i "Regular instruction set allows hardwiring of control logic at low component count.

- i "Most instructions execute in one cycle."

- i "Pipelined DSP instructions.

- i "Parallel execution of ALU and DSP instructions.

- i "Single-cycle half word multiply-accumulate operation.

- i #Fast Call and Return by parameter passing via registers.

- i #An instruction pipeline depth of only two stages decode/execute provides branching without insertion of wait cycles in combination with Delayed Branch instructions.

- i #Range and pointer checks are performed without speed penalty, thus, these checks need no longer be turned off, thereby providing higher runtime reliability.

- i "Separate address and data buses provide a throughput of one 32-bit word each cycle.

The features noted above contribute to reduce the number of idle wait cycles to a bare minimum. The processor is designed to sustain its execution rate with a standard DRAM memory.

The low power consumption is of advantage for mobile (portable) applications or in temperature-sensitive environments.

In the current version, the GMS30C2116 and GMS30C2132 RISC/DSP are implemented in a 0.6 µm-CMOS-process.

The GMS30C2116 and GMS30C2132 RISC/DSP are based on *hyperstone* architecture.

0-2 CHAPTER 0

# **0.1. GMS30C2116/32 RISC/DSP** (continued)

Most of the transistors are used for the on-chip memory, the instruction cache, the register stack and the multiplier, whereas only a small-number is required for the control logic.

Due to the Hynix's low system cost, the GMS30C2116 and GMS30C2132 RISC/DSP are very well suited for embedded-systems applications requiring high performance and lowest cost. To simplify board design as well as to reduce system costs, the GMS30C2116 and GMS30C2132 already come with integrated periphery, such as a timer and memory and bus control logic. Therefore, complete systems with the Hynix's microprocessor can be implemented with a minimum of external components. To connect any kind of memory or I/O, no glue logic is necessary. It is even suitable for systems where up to now microprocessors with 16-bit architecture have been used for cost reasons. Its improved performance compared to conventional micro-controllers can be used to software-substitute many external peripherals like graphics controllers or DSPs.

The software development tools include an optimizing C compiler, assembler, source-level debugger with profiler as well as a real-time kernel with an extremely fast response time. Using this real-time kernel, up to 31 tasks, each with its own virtual timer, can be developed independently of each other. The synchronization of these tasks is effected almost automatically by the real-time kernel. To the developer, it seems as if he has up to 31 Hynix's microprocessors to which he can allocate his programs accordingly. Real-time debugging of multiple tasks is assisted in an optimized way.

The following description gives a brief architectural overview:

# Registers:

- i #32 global and 64 local registers of 32 bits each

- i # 16 global and up to 16 local registers are addressable directly

#### Flags:

- i "Zero(Z), negative(N), carry(C) and overflow(V) flag

- i "Interrupt-mode, interrupt-lock, trace-mode, trace-pending, supervisor state, cache-mode and high global flag

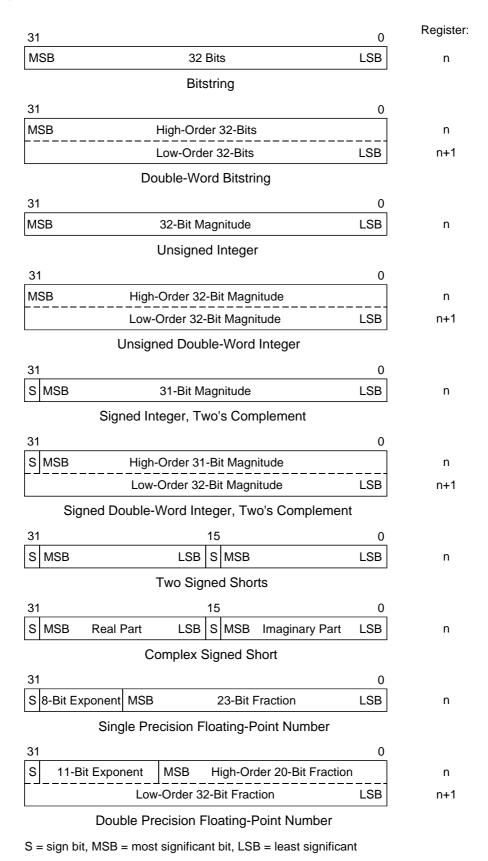

# **Register Data Types:**

i Unsigned integer, signed integer, signed short, signed complex short, 16-bit fixed-point, bit-string, IEEE-754 floating-point, each either 32 or 64 bits

# **External Memory:**

- i Ü Address space of 4Gbytes, divided into five areas

- i ü Separate I/O address space

- i "Load/Store architecture

- i "Pipelined memory and I/O accesses

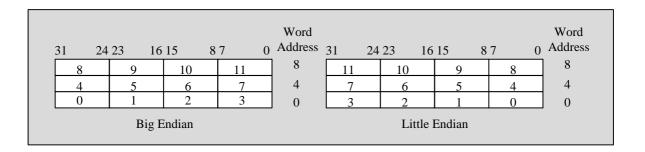

- i "High-order data located and addressed at lower address (big endian)

- i "Instructions and double-word data may cross DRAM page boundaries

Overview 0-3

# 0.1. GMS30C2116/32 RISC/DSP (continued)

#### **On-chip Memory:**

i #4KByte internal (on-chip) memory

#### **Memory Data Types:**

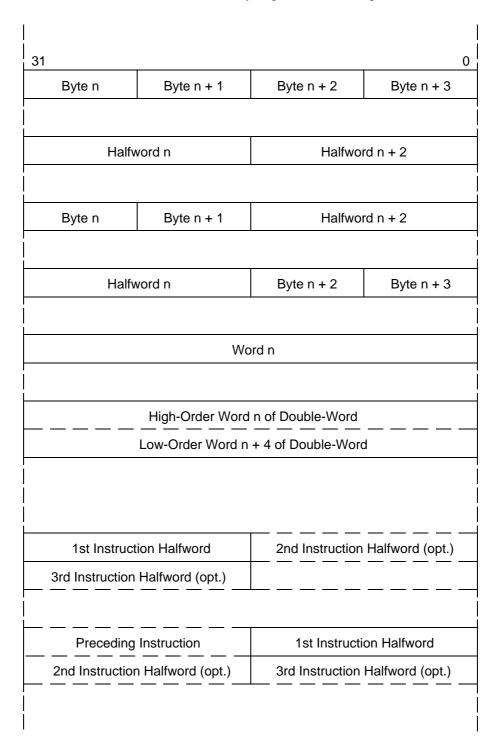

- i Unsigned and signed byte (8 bit)

- i Unsigned and signed half word (16 bit), located on half word boundary

- i Undedicated word (32 bit), located on word boundary

- i ÜUndedicated double-word (64 bit), located on word boundary

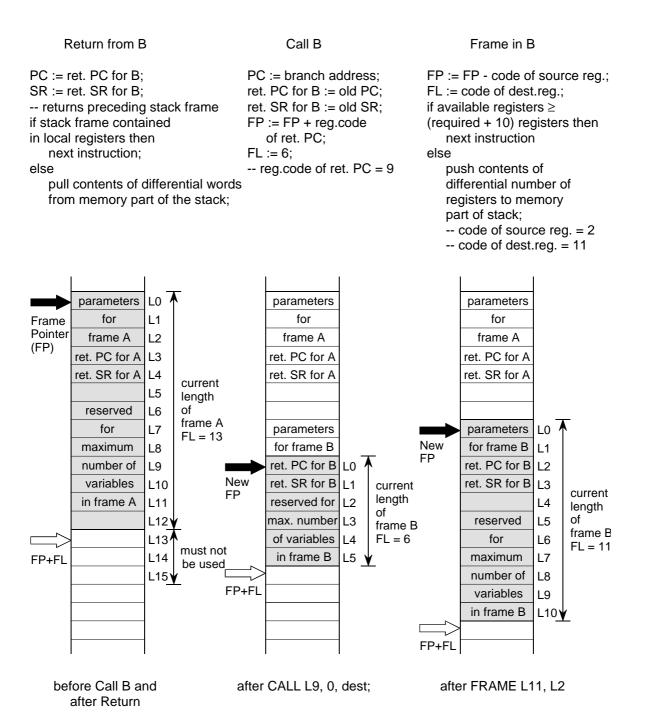

#### **Runtime Stack:**

- i #Runtime stack is divided into memory part and register part

- i #Register part is implemented by the 64 local registers holding the most recent stack frame(s)

- i "Current stack frame (maximum 16 registers) is always kept in register part of the stack

- i "Data transfer between memory and register part of the stack is automatic

- i ÜUpper stack bound is guarded

#### **Instruction Cache:**

i ÜAn on-chip instruction cache reduces instruction memory access substantially

#### Instructions General:

- i #Variable-length instructions of one, two or three half words halve required memory bandwidth

- i "Pipeline depth of only two stages, assures immediate refill after branches

- i #Register instructions of type "source operator destination ⇒ destination" or "source operator immediate ⇒ destination"

- i ü All register bits participate in an operation

- i Ummediate operands of 5, 16 and 32 bits, zero- or sign-expanded

- i "Large address displacement of up to 28 bits

- i "Two sets of signed arithmetical instructions: instructions set or clear either only the overflow flag or trap additionally to a Range Error routine on overflow

- i #DSP instructions operate on 16-bit integer, real and complex fixed-point data and 32-bit integer data into 32-bit and 64-bit hardware accumulators

#### **Instruction Summary:**

i #Memory instructions pipelined to a depth of two stages, trap on address register equal to zero (check for invalid pointers)

0-4 CHAPTER 0

# 0.1. GMS30C2116/32 RISC/DSP (continued)

i "Memory address modes: register address, register post-increment, register + displacement (including PC relative), register post-increment by displacement (next address), absolute, stack address, I/O absolute and I/O displacement

- i #Load, all data types, bytes and half words right adjusted and zero- or sign-expanded, execution proceeds after Load until data is needed

- i "Store, all data types, trap when range of signed byte or half word is exceeded

- i "Move, Move immediate, Move double-word

- i #Logical instructions AND, AND not, OR, XOR, NOT, AND not immediate, OR immediate, XOR immediate

- i ÜMask source and immediate ⇒ destination

- i ÜAdd unsigned/signed, Add signed with trap on overflow, Add with carry

- i #Add unsigned/signed immediate, Add signed immediate with trap on overflow

- i USum source + immediate ⇒ destination, unsigned/signed and signed with trap on overflow

- i "Subtract unsigned/signed, Subtract signed with trap on overflow, Subtract with carry

- i "Negate unsigned/signed, Negate signed with trap on overflow

- i  $\forall$  Multiply word \* word  $\Rightarrow$  low-order word unsigned or signed, Multiply word \* word  $\Rightarrow$  double-word unsigned and signed

- i ÜDivide double-word by word ⇒ quotient and remainder, unsigned and signed

- i #Shift left unsigned/signed, single and double-word, by constant and by content of register, Shift left signed by constant with trap on loss of high-order bits

- i #Shift right unsigned and signed, single and double-word, by constant and by content of register

- i "Rotate left single word by content of register

- i lindex Move, move an index value scaled by 1, 2, 4 or 8, optionally with bounds check

- i "Check a value for an upper bound specified in a register or check for zero

- i "Compare unsigned/signed, Compare unsigned/signed immediate

- i "Compare bits, Compare bits immediate, Compare any byte zero

- i "Test number of leading zeros

- i "Set Conditional, save conditions in a register

- i "Branch unconditional and conditional (12 conditions)

- i "Delayed Branch unconditional and conditional (12 conditions)

- i üCall subprogram, unconditional and on overflow

- i "Trap to supervisor subprogram, unconditional and conditional (11 conditions)

- i "Frame, structure a new stack frame, include parameters in frame addressing, set frame length, restore reserve frame length and check for upper stack bound

- i "Return from subprogram, restore program counter, status register and return-frame

Overview 0-5

# **0.1. GMS30C2116/32 RISC/DSP** (continued)

- i "Software instructions, call an associated subprogram and pass a source operand and the address of a destination operand to it

- i ÜDSP Multiply instructions: signed and/or unsigned multiplication ⇒ single and double word product

- i ÜDSP Multiply-Accumulate instructions:

signed multiply-add and multiply-subtract ⇒ single and double word product sum and difference

- i ÜDSP Half word Multiply-Accumulate instructions: signed multiply-add operating on four half word operands ⇒ single and double word product sum

- i UDSP Complex Half word Multiply instruction: signed complex half word multiplication ⇒ real and imaginary single word product

- i ÜDSP Complex Half word Multiply-Accumulate instruction: signed complex half word multiply-add ⇒ real and imaginary single word product sum

- i UDSP Add and Subtract instructions: signed half word add and subtract with and without fixed-point adjustment ⇒ single word sum and difference

- i "Floating-point instructions are architecturally fully integrated, they are executed as Software instructions by the present version. Floating-point Add, Subtract, Multiply, Divide, Compare and Compare unordered for single and double-precision, and Convert single ⇔ double are provided.

#### **Exceptions:**

- i #Pointer, Privilege, Frame and Range Error, Extended Overflow, Parity Error, Interrupt and Trace mode exception

- i "Watchdog function

- i #Error-causing instructions can be identified by backtracking, thus allowing a very detailed error analysis

#### Timer:

i "Two multifunctional timers

#### **Bus Interface:**

- i ÜSeparate address bus of 26 (GMS30C2132) or 22 (GMS30C2116) bits and data bus of up to 32 (GMS30C2132) or 16 bits (GMS30C2116) provide a throughput of four or two bytes at each clock cycle

- tData bus width of 32, 16 or 8 bits, individually selectable for each external memory area.

- i ÜUp to seven vectored interrupts

- i ü Configurable I/O pins

- i "Internal generation of all memory and I/O control signals

0-6 CHAPTER 0

# 0.2 Block Diagram

Figure 0.1: Block Diagram

Overview 0-7

# 0.3 Pin Configuration

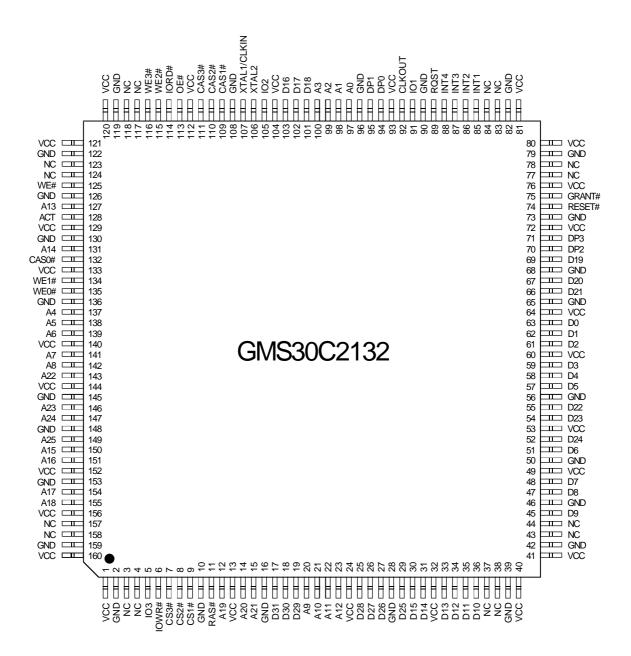

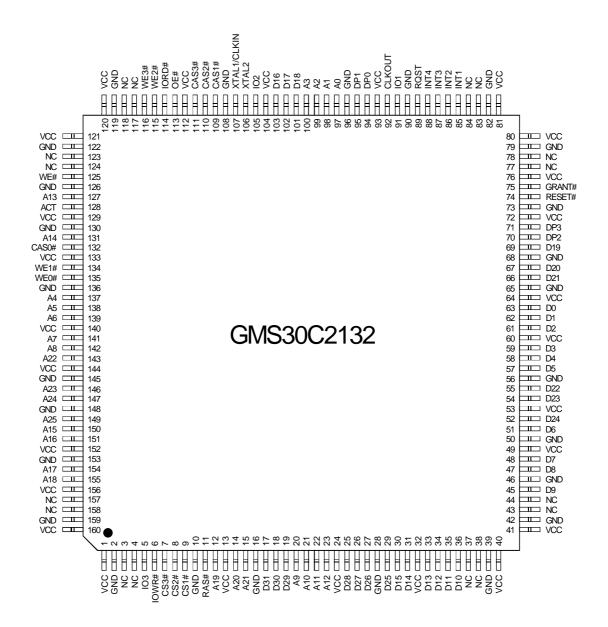

# 0.3.1 GMS30C2132, 160-Pin MQFP-Package - View from Top Side

Figure 0.2: GMS30C2132, 160-Pin MQFP-Package

0-8 CHAPTER 0

# **0.3. Pin Configuration** (continued)

# 0.3.2 Pin Cross Reference by Pin Name

| Signal Location | Signal Location | Signal Location | Signal Location   |

|-----------------|-----------------|-----------------|-------------------|

| A097            | D557            | GND 65          | NC124             |

| A1 98           | D651            | GND 68          | NC157             |

| A299            | D748            | GND73           | NC158             |

| A3100           | D847            | GND79           | OE#113            |

| A4137           | D945            | GND 82          | RAS#11            |

| A5138           | D1036           | GND 90          | RESET#74          |

| A6139           | D1135           | GND 96          | RQST89            |

| A7141           | D1234           | GND 108         | VCC1              |

| A8142           | D1333           | GND 119         | VCC13             |

| A920            | D1431           | GND 122         | VCC24             |

| A1021           | D1530           | GND 126         | VCC32             |

| A1122           | D16103          | GND 130         | VCC40             |

| A1223           | D17102          | GND 136         | VCC41             |

| A13127          | D18101          | GND 145         | VCC49             |

| A14131          | D1969           | GND 148         | VCC53             |

| A15150          | D2067           | GND 153         | VCC60             |

| A16151          | D2166           | GND 159         | VCC64             |

| A17154          | D2255           | GRANT#75        | VCC72             |

| A18155          | D2354           | INT1 85         | VCC76             |

| A1912           | D2452           | INT2 86         | VCC80             |

| A2014           | D2529           | INT3 87         | VCC81             |

| A21 15          | D2627           | INT4 88         | VCC93             |

| A22143          | D2726           | IO1 91          | VCC104            |

| A23146          | D2825           | IO2 105         | VCC112            |

| A24147          | D2919           | IO35            | VCC120            |

| A25149          | D3018           | IORD# 114       | VCC121            |

| ACT128          | D3117           | IOWR#6          | VCC133            |

| CAS0#132        | DP094           | NC3             | VCC140            |

| CAS1#109        | DP195           | NC 4            | VCC156            |

| CAS2#110        | DP270           | NC 37           | VCC160            |

| CAS3#111        | DP371           | NC 38           | VCC129            |

| CLKOUT92        | GND2            | NC 43           | VCC144            |

| CS1#9           | GND10           | NC 44           | VCC152            |

| CS2#8           | GND16           | NC 77           | WE#125            |

| CS3#7           | GND28           | NC78            | WE0#135           |

| D063            | GND39           | NC 83           | WE1#134           |

| D162            | GND42           | NC 84           | WE2#115           |

| D261            | GND46           | NC 117          | WE3#116           |

| D359            | GND50           | NC 118          | XTAL1/CLKIN . 107 |

| D458            | GND56           | NC 123          | XTAL2106          |

Overview 0-9

# **0.3. Pin Configuration** (continued)

# 0.3.3 Pin Function

| Type        | Name           | State | Use                                                                                                                                                              |

|-------------|----------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power       | VCC            | I     | Power. Connected to the power supply. It can be selected 5.0V or 3.3V power supply.                                                                              |

|             | GND            | Ι     | Ground. Connected to the system ground. All GND pins must be connected to the system ground.                                                                     |

| Clock       | XTAL1          | Ι     | Input for Quartz Clock. When external clock generator generates the clock, XTAL1 is used as clock input.                                                         |

|             | XTAL2          | O     | Output for Quartz Clock.                                                                                                                                         |

|             | CLKOUT         | О     | Clock Signal Output. It can be used to supply a clock signal to peripheral devices.                                                                              |

| Address Bus | A25A0          | O/Z   | Address Bus. With the GMS30C2132, only A22A0 are connected to the address bus pins                                                                               |

| Data Bus    | D31D0          | I/O   | Data Bus. 32-bit bi-directional data bus                                                                                                                         |

|             | DP0DP3         | I/O   | Data Parity Signal. Bi-directional parity signals                                                                                                                |

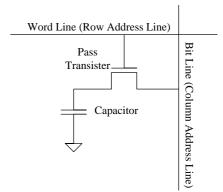

| Bus Control | RAS#           | O/Z   | Row Address Strobe. RAS# is activated when the processor accesses a DRAM or refresh cycle. When a SRAM is placed in MEM0, RAS# is used as the chip select signal |

|             | CAS0#CAS<br>3# | O/Z   | Column Address Strobe. They are only used by a DRAM for column access cycles and for "CAS before RAS" refresh.                                                   |

|             | WE#            | O/Z   | Write Enable. Active low indicates a write access, active high indicates a read access.                                                                          |

|             | CS1#CS3#       | O/Z   | Chip Select. Active low of CS1#CS3# indicates chip select for the memory areas MEM1MEM3.                                                                         |

|             | WE0#WE3#       | O/Z   | SRAM Write Enable. Active low indicates write enable for the corresponding byte.                                                                                 |

|             | OE#            | O/Z   | Output Enable for SRAM's and EPROM's.                                                                                                                            |

|             | IORD#          | O/Z   | I/O Read Strobe, optionally I/O Data Strobe. The use of IORD# is specified in the I/O address bit 10.                                                            |

|             | IOWR#          | O/Z   | I/O Write Strobe.                                                                                                                                                |

0-10 CHAPTER 0

# **0.3. Pin Configuration** (continued)

| Type              | Name     | State | Use                                                                                                                                                                                   |

|-------------------|----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bus Control       | RQST     | О     | RQST signals the request for a memory or I/O access                                                                                                                                   |

|                   | GRANT#   | I     | Bus Grant. GRANT# is signaled low by an bus arbiter to grant access to the bus for memory and I/O cycles                                                                              |

|                   | ACT      | O     | Active as bus master. ACT is signaled high when GRANT# is low and it is kept high during a current bus access                                                                         |

| Interrupt         | INT1INT4 | I     | Interrupt Request A signal of INT1INT4 interrupt request pins causes an interrupt exception when interrupt lock flag L is clear and the corresponding INTxMask bit in FCR is not set. |

| I/O Port          | IO1IO3   | I/O   | General Input-Output Port. IO1IO3 can be individually configured via IOxDirection bits in the FCR as either input or output pins (port).                                              |

| System<br>Control | RESET#   | I     | Reset Processor. RESET# low resets the processor to the initial state and halts all activity. RESET# must be low for at least two cycles                                              |

# 1. Architecture

#### 1.1 Introduction

#### 1.1.1 RISC Architecture

In the early days of computer history, most computer families started with an instruction set which was rather simple. The main reason for being simple then was the high cost for hardware. The hardware cost has dropped and the software cost has gone up steadily in the past three decades.

The net result is that more and more functions have been built into the hardware, making the instruction set very large and very complex. The growth of instruction sets was also encouraged by the popularity of microprogrammed control in the 1960s and 1970s. Even user-defined instruction sets were implemented using microcodes in some processors for special-purpose applications.

The evolution of computer architectures has been dominated by families of increasingly complex processors. Under market pressures to preserve existing software, *Complex Instruction Set Computer (CISC)* architectures evolved by the gradual addition of microcode and increasingly elaborate operations. The intent was to supply more support for high-level languages and operating systems, as semiconductor advances made it possible to fabricate more complex integrated circuits. It seemed self-evident that architectures should become more complex as these technological advances made it possible to hold more complexity on VLSI devices.

In recent years, however, *Reduced Instruction Set Computer (RISC)* architectures have implemented a much more sophisticated handling of the complex interaction between hardware, firmware and software. RISC concepts emerged from statistical analysis of how software actually uses the resources of a processor. Dynamic measurement of system kernels and object modules generated by optimizing compilers show an overwhelming predominance of the simplest instruction, even in the code for CISC machine. Complex instructions are often ignored because a single way of performing a complex operation needs of high-level language and system environments. RISC designs eliminate the microcoded routines and turn the low-level control of the machine over to software.

This approach is not new. But its application is more universal in recent years thanks to the prevalence of high-level languages, the development of compilers that can optimize at the microcode level, and dramatic advances in semiconductor memory and packaging. It is now feasible to replace machine microcode ROM with faster RAM, organized as an instruction cache. Machine control then resides in the instruction cache and is, in fact, customized on the fly. The instruction stream generated by system- and compiler-generated code provides a precise fit between the requirements of high-level software and the capabilities of the hardware. So compilers are playing a vital role in RISC performance.

The advantage of RISC architecture is described as follows:

- Simplicity made VLSI implementation possible and thus higher clock rates.

- Hardwired control and separated data and program caches lower the average CPI (Cycles per Instruction) significantly.

- Dynamic instruction count in a RISC program only increased slightly (less than 2) in ordinary program.

1-2 CHAPTER 1

• Recently, the MIPS (Million Instructions per Second) rate of a typical RISC microprocessor increased with a factor of 5/(2\*0.1) = 25 times from that of a typical CISC microprocessor.

- The clock rate increased from 10 MHz on a CISC processor to 50 MHz on a CMOS/ RISC microprocessor.

- The instruction count in a typical RISC program increased less than 2 times form that of a typical CISC program.

- The average CPI for a RISC microprocessor decreased to 1.2 (instead of 12 as in a typical CISC processor).

# 1.1.2 Techniques to reduce CPI (Cycles per Instruction)

If the work each instruction performs is simple and straightforward, the time required to execute each instruction can be shortened and the number of cycles reduced. The goal of RISC designs has been to achieve an execution rate of one instruction per machine cycle (multiple-instruction-issue designs now seek to increase this rate to more than one instruction per cycle). Techniques that help achieve this goal include:

- Instruction pipelines

- Load and store (load/store) architecture

- Delayed load instructions

- Delayed branch instructions

# (1) Instruction Pipelines

One way to reduce the number of cycles required to execute an instruction is to overlap the execution of multiple instructions. Instruction pipelines divide the execution of each instruction into several discrete portions and then execute multiple instructions simultaneously. The instruction pipeline technique can be likened to an assembled line the instruction progresses from one specialized stage to the next until it is complete (or issued) - just as an automobile moves along an assembly line. (This is contrast to the nonpipeline, microcode approach, where all the work is done by one general unit and is less capable at each individual task.) For example, the execution of an instruction might be subdivided into four portions, or clock cycles, as shown in Figure 1.1:

| Cycle                 | Cycle #2                | Cycle                   | Cycle             |

|-----------------------|-------------------------|-------------------------|-------------------|

| #1                    |                         | #3                      | #1                |

| Fetch Instruction (F) | ALU<br>Operation<br>(A) | Access<br>Memory<br>(M) | Write Results (W) |

Figure 1.1: Functional Division of a Hypothetical Pipeline

An Instruction pipeline can potentially reduce the number of cycles/instructions by a factor equal to the depth of the pipeline (the depth of the pipeline = the number of resource). For example, in Figure 1.2 each instruction still requires a total of four clock cycles to execute. However, if a four-level instruction pipeline is used, a new instruction can be initiated at

Clock Cycles Instruction #1 F Α M W #2 F W Α M F A M W #3 F #4 M W A

each clock cycle and the effective execution rate is one cycle per instruction.

Figure 1.2: Multiple Instructions in a Hypothetical Pipeline

#### (2) Load/Store Architecture

The discussion of the instruction pipeline illustrates how each instruction can be subdivided into several discrete parts that permit the processor to execute multiple instructions in parallel. For this technique to work efficiently, the time required to execute each instruction subpart should be approximately equal. If one part requires an excessive length of time, there is an unpleasant choice: either halting the pipeline (inserting wait or idle cycles), or making all cycles longer to accommodate this lengthier portion of the instruction.

Instructions that perform operations on operands in memory tend to increase either the cycle time or the number of cycles/instruction. Such instruction require additional time for execution to calculate the addresses of the operands, read the required operands from memory, calculate the result, and store the results of the operation back to memory. To eliminate the negative impact of such instruction, RISC designs implement a load and store (load/store) architecture in which the processor has many register, all operations are performed on operands held in processor registers, and main memory is accessed only by load and store instructions.

This approach produces several benefits

- Reducing the number of memory accesses eases memory bandwidth requirements

- Limiting all operations to registers helps simplicity the instruction set

- Eliminating memory operations makes it easier for compilers to optimize register allocation - this further reduces memory accesses and also reduces the instructions/task factor

All of these factors help RISC design approach their goal of executing one cycle/instruction. However, two classes of instructions hinder achievement of this goal load instructions and branch instructions. The following sections discuss how RISC designs overcome obstacles raised by these classes of instructions.

1-4 CHAPTER 1

#### (3) Delayed Load Instructions

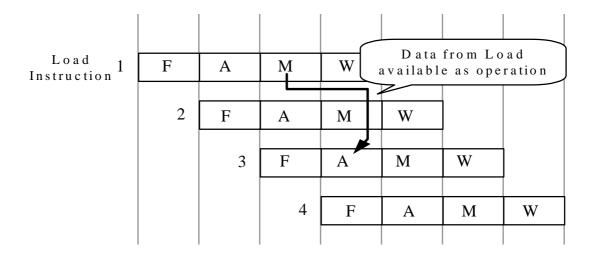

Load instruction read operands from memory into processor register for subsequent operation by other instructions. Because memory typically operates at much slower speeds than processor clock rates, the loaded operand is not immediately available to subsequent instructions in an instruction pipeline. The data dependency is illustrated in Figure 1.3.

Figure 1.3: Data Dependency Resulting From a Load Instruction

In this illustration, the operand loaded by instruction 1 is not available for use in a cycle (ALU, or Arithmetic/Logic Unit operation) of instruction 2. One way to handle this dependency is to delay the pipeline by inserting additional clock cycles into the execution of instruction 2 until the loaded data becomes available. This approach obviously introduces delays that would increase the cycles/instructions factor.

In many RISC designs the technique used to handle this data dependency is to recognize and make visible to compilers the fact that all load instructions have an inherent latency or load delay. Figure 1.3 illustrates a load delay or latency of one instruction. The instruction that immediately follows the load is in the load delay slot. If the instruction in this slot does not require the data from the load, then no pipeline delay is required.

If this load delay is made visible to software, a compiler can arrange instructions to ensure that there is no data dependency a load instruction and the instruction in the load delay slot. The simplest way of ensuring that there is no data dependency is to insert a No Operation (NOP) instruction to fill the slot, as follow:

Although filling the delay slot with NOP instructions eliminates the need for hardware-controlled pipeline stalls in this case, it still is not a very efficient use of the pipeline stream since these additional NOP instructions increase code size and perform no useful work. (In practice, however, this technique need not have much negative impact on performance.)

A more effective solution to handling the data dependency is to fill the load delay slot with a useful instruction. Good optimizing compilers can usually accomplish this, especially if

the load delay is only one instruction. Below example program illustrates how a compiler might rearrange instruction to handle a potential data dependency.

```

# Consider the code for C := A+B; F := D

Load

R1, A

Load

R2. B

Add

R2, R1, R2

<= This instruction stalls because R2 data is not available

R4, D

Load

# An alternative code sequence (where delay length = 1)

Load

R1, A

Load

R2, B

Load

R4, D

Add

R3, R1, R2

<= No stall since R2 data is available

```

# (4) Delayed Branch Instructions

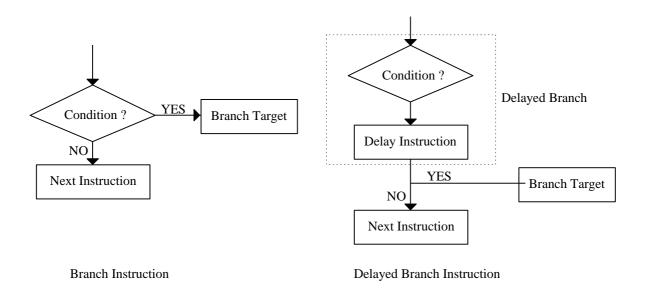

Branch instructions usually delay the instruction pipeline because the processor must calculate the effective destination of the branch and fetch that instruction. When a cache access requires an entire cycle, and the fetched branch instruction specifies the target address, it is impossible to perform this fetch (of the destination instruction) without delaying the pipeline for at least one pipe stage (one cycle). Conditional branches can cause further delays because they require the calculation of a condition, as well as the target address.

Instead of stalling the instruction pipeline to wait for the instruction at the target address, RISC designs typically use an approach similar to that used with Load instruction: Branch instructions are delayed and do not take effect until after one or more instructions immediately following the Branch instruction have been executed. The instruction or instructions immediately following the Branch instruction (delay instruction) have been executed. Branch and delayed branch instruction are illustrated in Figure 1.4

Figure 1.4: Block Diagram of Branch/Delayed Branch Instruction

1-6 CHAPTER 1

# 1.1.3 The pipeline structure of GMS30C2132

GMS30C2132 has a two-stage pipeline structure and each stage is composed of two phases (TM and TV). The basic structure of GMS30C2132 pipeline is two-stage pipeline, but actually it is lengthened by the need of some instruction. As an example, standard ALU instruction uses 5 phases (2 stage pipeline (4 phases) + additional 1 phase). This additional phase doesn't use the datapath that is used next instruction, so next instruction execution need not wait until previous ALU instruction is ended. DSP instruction takes over 2 stage pipeline for execution, and requires same resource in the datapath that is required to next DSP instruction. So next DSP instruction is delayed.

The pipeline structure of GMS30C2132 and the action of datapath are described in Table 1.1.

| Stage                | Phase     | Datapath Action                                                                                                                                 |  |

|----------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Fetch/Decode         | TM (Low)  | 1. The instruction is read from the instruction cache according to the address of instruction.                                                  |  |

|                      | TV (High) | 2. The control signal of Rd (destination operand) and Rs (source operand) is activated according to the instruction that was loaded in TM phase |  |

|                      |           | 2.1 The control signal of IR (immediate register (operand)) and IL (instruction length) is activated.                                           |  |

|                      |           | 2.2 The address of next instruction is calculated and saved in PC                                                                               |  |

| Execute/Write        | TM (Low)  | 1. The next instruction is read from the instruction cache.                                                                                     |  |

|                      |           | 1.1 The address of Rs and Rs are determined.                                                                                                    |  |

|                      |           | 1.2 The immediate operand is determined.                                                                                                        |  |

|                      |           | 1.3 The operand is read from register stack using the address of Rs and Rd.                                                                     |  |

|                      |           | 1.4 The operand XR, YR and QR are controlled.                                                                                                   |  |

| TV (High)            |           | 2. The input data of ALU is attained.                                                                                                           |  |

|                      |           | 2.1 The control of ALU datapath is made and instruction is executed in ALU.                                                                     |  |

|                      |           | 2.2 The result of ALU operation is saved in the register file.                                                                                  |  |

| Additional Insertion | Next TM   | Additional ALU operation is continued and its result is saved in the register file.                                                             |  |

Table 1.1: The pipeline structure of GMS30C2132 and the action of datapath.

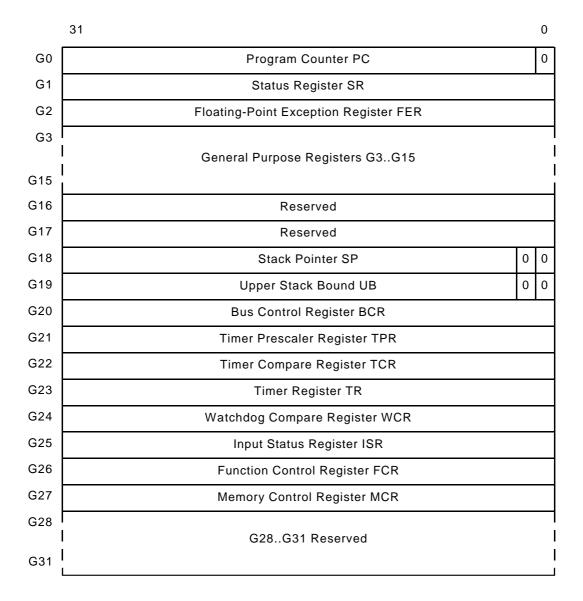

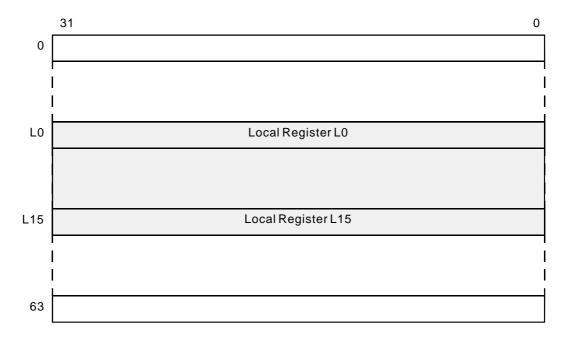

# 1.2 Global Register Set

The architecture provides 32 global registers of 32 bit each. These are:

| $\mathbf{G0}$ | Program Counter PC                                           |

|---------------|--------------------------------------------------------------|

| G1            | Status Register SR                                           |

| G2            | Floating-point Exception Register FER                        |

| G3G15         | General purpose registers                                    |

| G16G17        | Reserved                                                     |

| G18           | Stack Pointer SP                                             |

| G19           | Upper stack Bound UB                                         |

| G20           | Bus Control Register BCR (see section 6. Bus Interface)      |

| G21           | Timer Prescaler Register TPR (see section 5. Timer)          |

| G22           | Timer Compare Register TCR (see section 5. Timer)            |

| G23           | Timer Register TR (see section 5. Timer)                     |

| G24           | Watchdog Compare Register WCR (see section 6. Bus Interface) |

| G25           | Input Status Register ISR (see section 6. Bus Interface)     |

| G26           | Function Control Register FCR (see section 6. Bus Interface) |

| G27           | Memory Control Register MCR (see section 6. Bus Interface)   |

| G28G31        | Reserved                                                     |

Registers G0..G15 can be addressed directly by the register code (0..15) of an instruction. Registers G18..G27 can be addressed only by a MOV or MOVI instruction with the high global flag H set to 1.

```

(Example)

```

```

MOVI G2, 0x20 ; G2 := 0x20 (set H flag)

```

MOV G3, G19; G3 := G19 (G19 (UB) is copied to G3)

1-8 CHAPTER 1

Figure 1.5: Global Register Set

# 1.2.1 Program Counter PC, G0

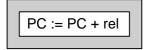

G0 is the program counter PC. It is updated to the address of the next instruction through instruction execution. Besides this implicit updating, the PC can also be addressed like a regular source or destination register. When the PC is referenced as an operand, the supplied value is the address of the first byte after the instruction which references it (the address of next instruction), except when referenced by a delay instruction with a preceding delayed branch taken. At delay branch instruction, when the branch condition is met, place the branch address PC + rel (relative to the address of the first byte after the Delayed Branch Instruction) in the PC (see section 3.26. Delayed Branch Instructions).

Placing a result in the PC has the effect of a branch taken. When branch is taken, the target address of branch is placed in PC.

Bit zero of the PC is always zero, regardless of any value placed in the PC.

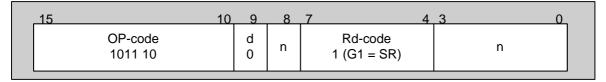

# 1.2.2 Status Register SR, G1

G1 is the status register SR. Its content is updated by instruction execution. Besides this implicit updating, the SR can also be addressed like a regular register (when H flag is set). When addressed as source or destination operand, all 32 bits are used as an operand. However, only bits 15..0 of a result can be placed in bits 15..0 of the SR, bits 31..16 of the result are discarded and bits 31..16 of the SR remain unchanged. When SR addressed as source operand, it represents 0x0 value. The full content of the SR is replaced only by the Return Instruction. A result placed in the SR overrules any setting or clearing of the condition flags as a result of an instruction.

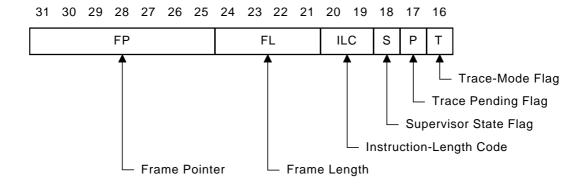

Figure 1.6: Status Register SR (bits 31..16)

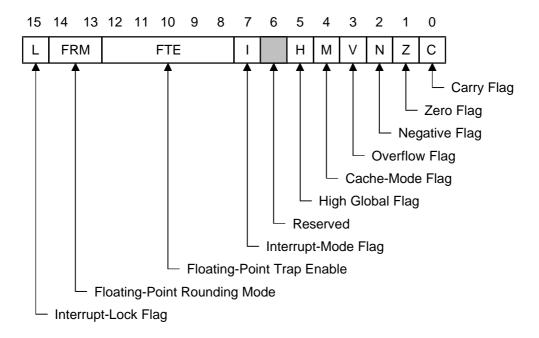

Figure 1.7: Status Register SR (bits 15..0)

1-10 CHAPTER 1

# 1.2.2 Status Register SR, G1 (continued)

The status register SR contains the following status information:

C Carry Flag. Bit zero is the carry condition flag C. In general, when set it indicates that the unsigned integer range is exceeded (overflow). At add operations, it indicates a carry out of bit 31 of the result. At subtract operations, it indicates a borrow (inverse carry) into bit 31 of the result.

- **Z** Zero Flag. Bit one is the zero condition flag Z. When set, it indicates that all 32 or 64 result bits are equal to zero regardless of any carry, borrow or overflow.

- N Negative Flag. Bit two is the negative condition flag N. On compare instructions, it indicates the arithmetic correct (true) sign of the result regardless of an overflow. On all other instructions, it is derived from result bit 31, which is the true sign bit when no overflow occurs. In the case of overflow, result bit 31 and N reflect the inverted sign bit.

- V Overflow Flag. Bit three is the overflow condition flag V. In general, when set it indicates a signed overflow. At the Move instructions, it indicates a floating-point NaN (Not a Number).

- M Cache-Mode Flag. Bit four is the cache-mode flag M. Besides being set or cleared under program control, it is also automatically cleared by a Frame instruction and by any branch taken except a delayed branch. See section 1.8. Instruction Cache for details.

- H High Global Flag. Bit five is the high global flag H. When H is set, denoting G0..G15 addresses G16..G31 instead. Thus, the registers G18..G27 may be addressed by denoting G2..G11 respectively.

The H flag is effective only in the first cycle of the next instruction after it was set; then it is cleared automatically.

Only the MOV or MOVI instruction issued as the next instructions must be used to copy the content of a local register or an immediate value to one of the high global registers. The MOV instruction may be used to copy the content of a high global register (except the BCR, TPR, FCR and MCR register, which are write-only) to a local register. With all other instructions, the result may be invalid.

If one of the high global registers is addressed as the destination register in user state (S=0), the condition flags are undefined, the destination register remains unchanged and a trap to Privilege Error occurs.

**Reserved** Bit six is reserved for future use. It must always be zero.

- I Interrupt-Mode Flag. Bit seven is the interrupt-mode flag I. It is set automatically on interrupt entry and reset to its old value by a Return instruction. The I flag is used by the operating system; it must be never changed by any user program.

- FTE Floating-Point Trap Enable Flag. Bits 12..8 are the floating-point trap enable flags They determine the Exception type and Trap execution flow(see section 3.33.2. Floating-Point Instructions).

# 1.2.2 Status Register SR, G1 (continued)

FRM Floating-Point Rounding Mode. Bits 14..13 are the floating-point rounding modes (see section 3.33.2. Floating-Point Instructions).

L Interrupt-Lock Flag. Bit 15 is the interrupt-lock flag L. When the L flag is one, all Interrupt, Parity Error and Extended Overflow exceptions are inhibited regardless of individual mode bits. The state of the L flag is effective immediately after any instruction that changed it. The L flag is set to one by any exception.

The L flag can be cleared or kept set in any or on return to any privilege state (user or supervisor). Changing the L flag from zero to one is privileged to supervisor or return from supervisor to supervisor state. A trap to Privilege Error occurs if the L flag is set under program control from zero to one in user or on return to user state.

The following status information can be changed only internally or replaced by the saved return value of the SR via a Return instruction:

Trace-Mode Flag. Bit 16 is the trace-mode flag T. When both the T flag and the trace pending flag P are one, a trace exception occurs after every instruction except after a Delayed Branch instruction. The T flag is cleared by any exception.

Note: The T flag can only be changed in the saved return SR and is then effective after execution of a Return instruction.

P Trace Pending Flag. Bit 17 is the trace pending flag P. It is automatically set to one by all instructions except by the Return instruction, which restores the P flag from bit 17 of the saved return SR.

Since for a Trace exception both the P and the T flag must be one, the P flag determines whether a trace exception occurs (P = 1) or does not occur (P = 0) immediately after a Return instruction that restored the T flag to one.

When an instruction is ended, the T and P flag set to one. Therefore trace exception is occurred. After trace exception trap is ended the process returns to main program, and if T and P flag is set to one, trace exception occurs again. To avoid tracing the same instruction in an endless loop, the P flag is cleared at return instruction in trace exception trap routine.

Note: The P flag can only be changed in the saved SR. No program except the trace exception handler should affect the saved P flag. The trace exception handler must clear the saved P flag to prevent a trace exception on return, in order to avoid tracing the same instruction in an endless loop.

- Supervisor State Flag. Bit 18 is the supervisor state flag S (see section 1.4. Privilege States). The S flag determine whether user state (S=0) or supervisor state (S=1). It is set to one by any exception.

- ILC Instruction-Length Code. Bits 20 and 19 represent the instruction-length code ILC. It is updated by instruction execution. The ILC holds (in general) the length of the last instruction: ILC values of one, two or three represent an instruction length of one, two or three half words respectively. After a branch taken, the ILC is invalid. The Return instruction clears the ILC.

1-12 CHAPTER 1

# 1.2.2 Status Register SR, G1 (continued)

Note: Since a Return instruction following an exception clears the ILC, a program must not rely on the current value of the ILC.

FL Frame Length. Bits 24..21 represent the frame length FL. The FL holds the number of usable local registers (maximum 16) assigned to the current stack frame. FL = 0 is always interpreted as FL = 16.

FP Frame Pointer. Bits 31..25 represent the frame pointer FP. The least significant six bits of the FP point to the beginning of the current stack frame in the local register set, that is, they point to L0.

The FP contains bit 8..2 of the address at which the content of L0 would be stored if pushed onto the memory part of the stack.

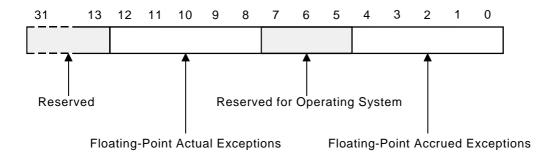

# 1.2.3 Floating-Point Exception Register FER, G2

G2 is the floating-point exception register. All bits must be cleared to zero after Reset. Only bits 12..8 and 4..0 may be changed by a user program, all other bits must remain unchanged.

Figure 1.8: Floating-Point Exception Register

The floating-point trap enable flags FTE and the exception flags are assigned as:

| floating-point trap enable FTE | accrued exceptions | actual<br>exceptions | exception type    |

|--------------------------------|--------------------|----------------------|-------------------|

| SR(12)                         | G2(4)              | G2(12)               | Invalid Operation |

| SR(11)                         | G2(3)              | G2(11)               | Division by Zero  |

| SR(10)                         | G2(2)              | G2(10)               | Overflow          |

| SR(9)                          | G2(1)              | G2(9)                | Underflow         |

| SR(8)                          | G2(0)              | G2(8)                | Inexact           |

The reserved bits G2(31..13) and G2(7..5) must be zero.

A floating-point instruction, except a Floating-point Compare, can raise any of the exceptions Invalid Operation, Division by Zero, Overflow, Underflow or Inexact. FCMP and FCMPD can raise only the Invalid Operation exception (at unordered). FCMPU and FCMPUD cannot raise any exception.

At an exception, the following additional action is performed:

i #Any corresponding accrued-exception flag whose corresponding trap-enable flag is zero (not enabled) is set to one; all other accrued-exception flags remain unchanged.

i #If a corresponding trap-enable flag is one (enabled), any corresponding actual-exception flag is set to one; all other actual-exception flags are cleared. The destination remains unchanged.

In the present software version, the software emulation routine must branch to the corresponding user-supplied exception trap handler. The (modified) result, the source operand, the stack address of the destination operand and the address of the floating-point instruction are passed to the trap handler. In the future hardware version, a trap to Range Error will occur; the Range Error handler will then initiate re-execution of the floating-point instruction by branching to the entry of the corresponding software emulation routine, which will then act as described before.

The only exceptions that can coincide are Inexact with Overflow and Inexact with Underflow. An Overflow or Underflow trap, if enabled, takes precedence over an Inexact trap; the Inexact accrued-exception flag G2(0) must then be set as well.

# 1.2.4 Stack Pointer SP, G18

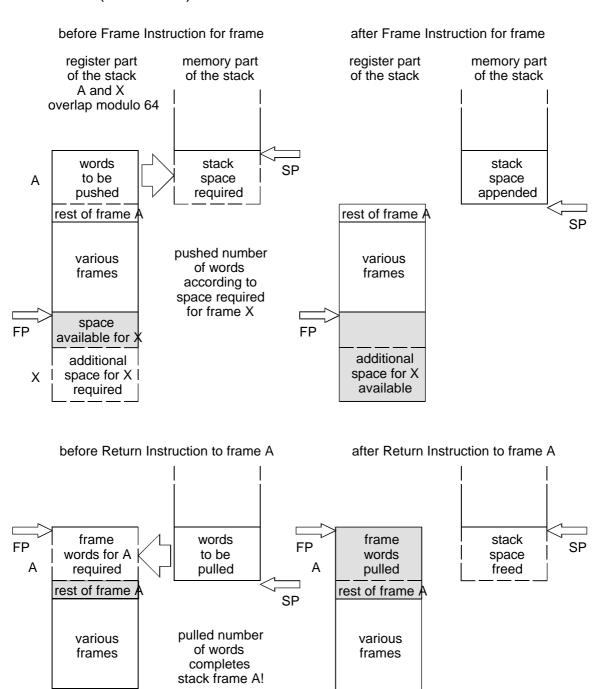

G18 is the stack pointer SP. The SP contains the top address + 4 of the memory part of the stack, that is the address of the first free memory location in which the first local register would be saved by a push operation (see section 3.29. Frame Instruction for details). Stack growth is from low to high address.

Bits one and zero of the SP must always be cleared to zero. The SP can be addressed only via the high global flag H being set. Copying an operand to the SP is a privileged operation.

Note: Stack Pointer SP contains the top address + 4 of the memory part of the stack (memory part stack), and Frame Pointer FP points to the beginning of the current stack frame in the local register set (register part stack).

# 1.2.5 Upper Stack Bound UB, G19

G19 is the upper stack bound UB. The UB contains the address beyond the highest legal memory stack location. It is used by the Frame instruction to inhibit stack overflow.

Bits one and zero of the UB must always be cleared to zero. The UB can be addressed only via the high global flag H being set. Copying an operand to the UB is a privileged operation.

# 1.2.6 Bus Control Register BCR, G20

G20 is the write-only bus control register BCR. Its content defines the options possible for bus cycle, parity and refresh control. The BCR defines the parameters (bus timing, refresh control, page fault and parity error disable) for accessing external memory located in address spaces MEM0..MEM3. The BCR can be addressed only via the high global flag H being set. Copying an operand to the BCR is a privileged operation. The BCR register is described in detail in the bus interface description in section 6.

1-14 CHAPTER 1

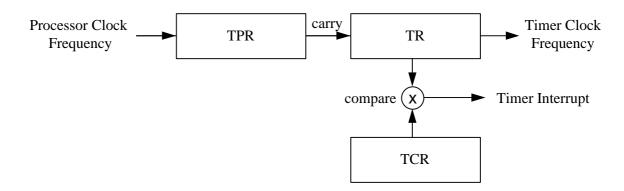

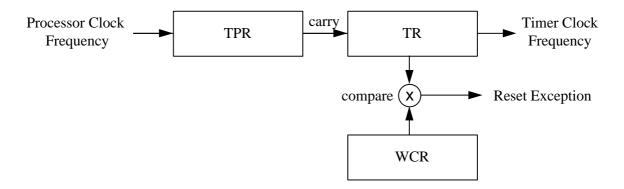

# 1.2.7 Timer Prescaler Register TPR, G21

G21 is the write-only timer prescaler register TPR. It adapts the timer clock to different processor clock frequencies. The TCR can be addressed only via the high global flag H being set. Copying an operand to the TPR is a privileged operation. The TPR is described in the timer description in section 5.

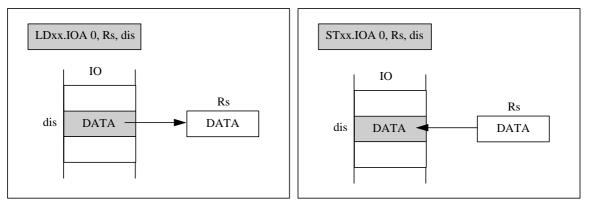

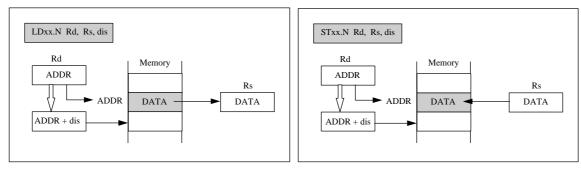

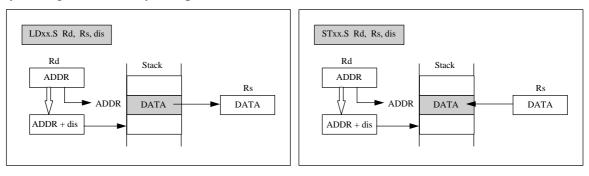

# 1.2.8 Timer Compare Register TCR, G22