PURPOSE

# 1.0 INTRODUCTION

This section introduces anat mode d describes the Western Digital WD90C26 Integrated Low Power VGA LCD Controller with Simultaneous Display (hereinafter referred to as WD90C26 or WD90C26 controller). The introduction is divided into the following subsections:

- Purpose

- WD90C26 Features

- General Description

#### 1.1 PURPOSE

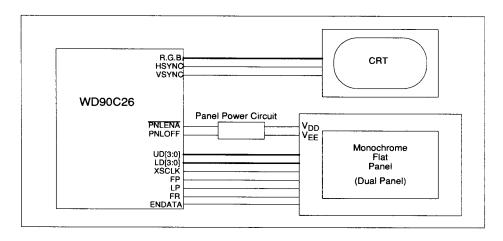

The WD90C26 controller provides control of all flat-panel displays along with simultaneous display on a traditional CRT. The WD90C26 supports all current monochrome and color flat-panel technologies.

The WD90C26 has improved power management and a performance-scaling capabilities that make it an ideal video solution for low battery drain portable computer applications.

#### 1.2 WD90C26 FEATURES

- Supports VGA flat panel or CRT video displays or both simultaneously

- Fully supports LCD, plasma, and Electro-Luminescent (EL) flat-panel technologies.

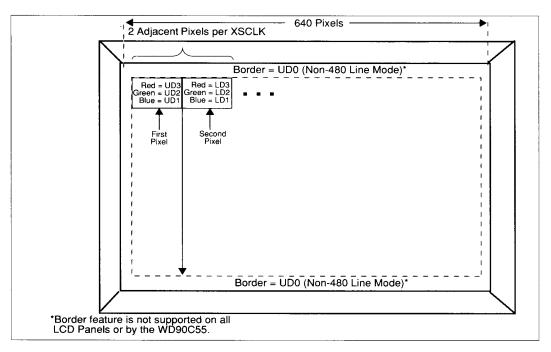

- Provides 256K colors on 8-bit STN LCD panels (16-bit with WD90C55), 27K colors on 9-bit TFT color LCD panels and 4K direct undithered colors on 12-bit TFT color LCD panels

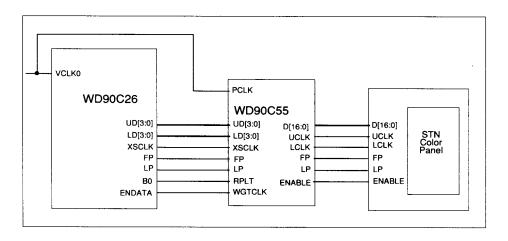

- Compatible with WD90C55 color STN LCD interface

- True 64-gray scale with programmable gray shade mapping including in 640 x 480 x 256 color video modes

- Up to 45 Mhz maximum video clock rate on flat panel display

- Up to 65 Mhz maximum video clock rate on CRT display

- Supports 800 x 600 x 256 and 1024 x 768 x 16 non-interlaced modes on CRT display

- Simultaneous display with all types of flat panels (patent pending)

- Up to 36 Mhz maximum video clock rate in dual-panel simultaneous display or 45 Mhz for single panel.

- Full screen presentation on both CRT and flatpanel for all video modes during simultaneous display

- Full downward compatibility with CGA, MDA, and Hercules graphics standards

- Hardware vertical expansion and autocentering

- Up to 16 loadable fonts

- Hidden register support for 100% hardware compatibility with IBM's VGA standards

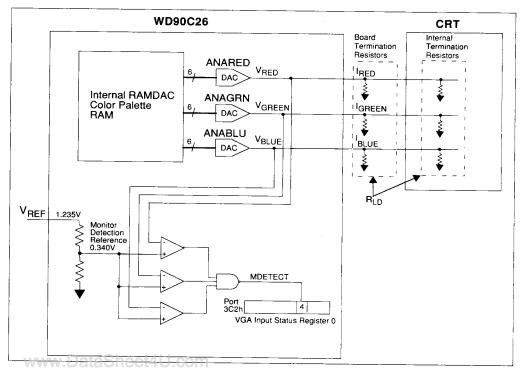

- On-board VGA compatible RAMDAC with internal CRT detection circuit

- On-chip 16-bit MicroChannel interface

- True 16-bit CPU to display memory data transfer in all video plane modes

- Flexible display memory configuration (2, 3 or 4 256Kx4 DRAMs or one 256Kx16 DRAM)

- Up to 44.3 Mhz maximum memory clock rate

- Selectable 8- or 16-bit I/O and memory interface

- Zero wait-state performance

- Adjustable video FIFO depth and fast page mode memory timing

- System interface write buffering

- Typical power dissipation of 450 mW at 5 VDC

- Enhanced power down modes

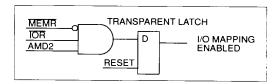

- I/O mapping to improve board level testability

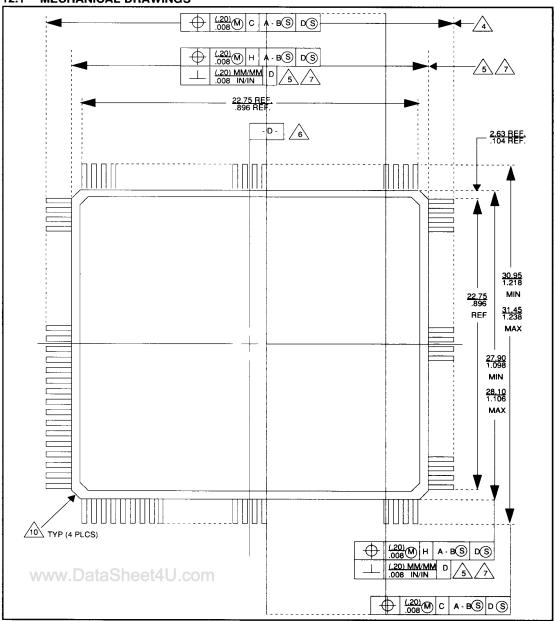

- 144-pin MQFP package

- On-chip 8/16-bit ISA Bus (AT bus) interface

- Supports 8-bit video BIOS

- Virtual memory/linear addressing support

WD90C26 FEATURES

### 1.3 GENERAL DESCRIPTION

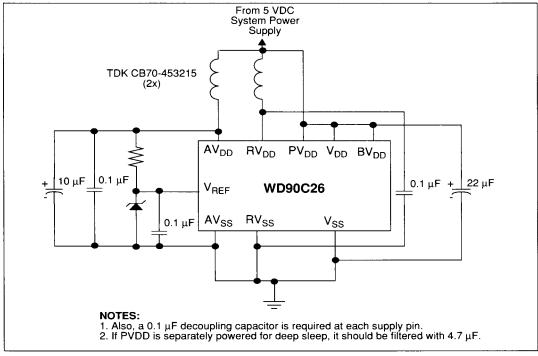

The WD90C26 is a 0.9 micron CMOS VGA controller designed to simultaneously drive a flat-panel display and the traditional analog CRT with a minimum of external components. The only additional components required for a complete flat-panel VGA subsystem are 1, 2, 3, or 4 DRAMs and video/memory clock sources. Contained on-chip are a flat-panel interface and a RAMDAC. The full-featured flat-panel interface is capable of supporting LCD, plasma, and EL flat-panel technologies. The full-featured RAMDAC is capable of directly driving PS/2 style analog color or monochrome monitors.

The WD90C26's scalable architecture allows it to be used with either 2, 3, or 4 external 256Kx4 DRAMs or one 256Kx16 DRAM. Basic VGA performance is available with the minimum 2 DRAM configuration or the single 256Kx16 DRAM configuration. Added panel support and enhanced VGA modes are available using 3 or 4 256Kx4 DRAMs. 16-bit video memory performance is also available using the four 256Kx4 or the single 256Kx16 DRAM configuration. DRAM utilization is firmware controllable, allowing the decrease of DRAM power consumption or the increase of system performance.

Western Digital's superior orthogonal 64-gray scale to 64-gray shade mapping technology allows system developers to 'hand tune' each of the shades in the 64-gray scale to provide the most realistic and visually linear gray scale shading for a particular model of panel. This is achieved through use of a system programmable on-chip 64-word gray scale lookup table or mapping RAM.

As with all Western Digital VGA controllers, the WD90C26 is fully compatible with IBM VGA, CGA, MDA, and Hercules video standards.

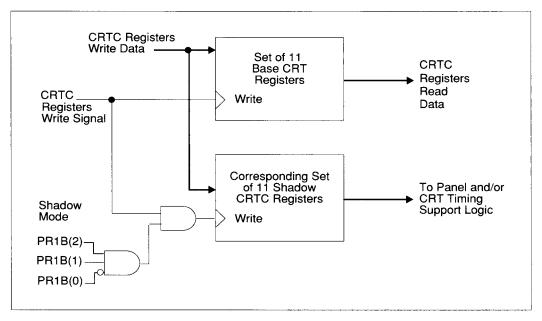

Through the use of its hidden, or "shadow" registers, the WD90C26 can be programmed to support various video modes and standards using fixed resolution flat-panel screen sizes, yet appear to the system as capable of displaying the variety of screen sizes and resolutions available with analog monitors. System modification of register content, thus shadowed or hidden, does not destroy the WD90C26 controller's ability to display the desired information on a flat-panel display as well.

The WD90C26 controller's vertical expansion and auto-centering features provide full-screen flat-panel displays even in video modes with lower resolutions than those of the panel. A unique expansion algorithm provides for realistic appearance of both text and graphics on expanded displays, without requiring the use of special expanded display fonts.

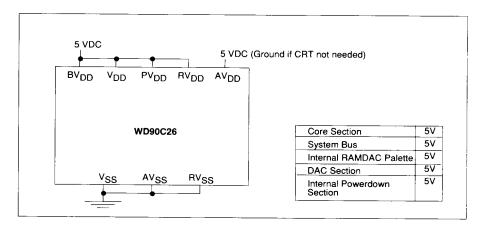

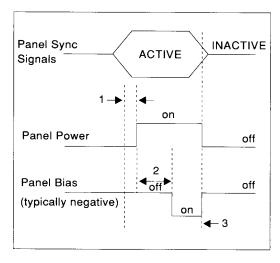

Advanced power management features include:

- Separate supply pins for certain functions so that parts of the chip may be externally powered off

- The capability to slow down internal clocks to conserve power

- Power sequencing that can be used to control power supply and interface signals to prevent panel burnout

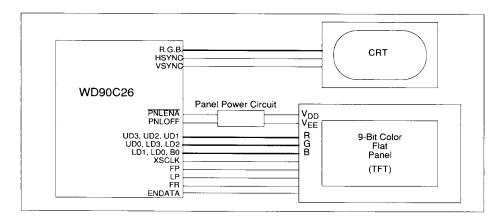

Also included in the WD90C26 is an advanced TFT support circuit that allows display from a palette of 27K colors on 9-bit interface color panels.

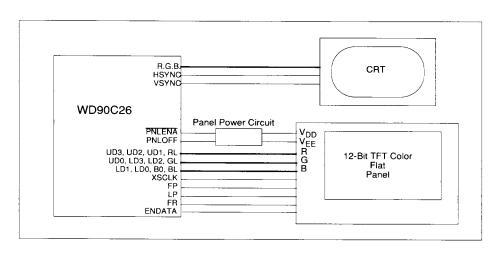

The WD90C26 directly supports TFT LCD displays with 12-bit interfaces by using undithered 12-bit direct colors from a 4K palette for optimum 12-bit display performance.

SYSTEM INTERFACE LOGIC

# 2.0 ARCHITECTURE

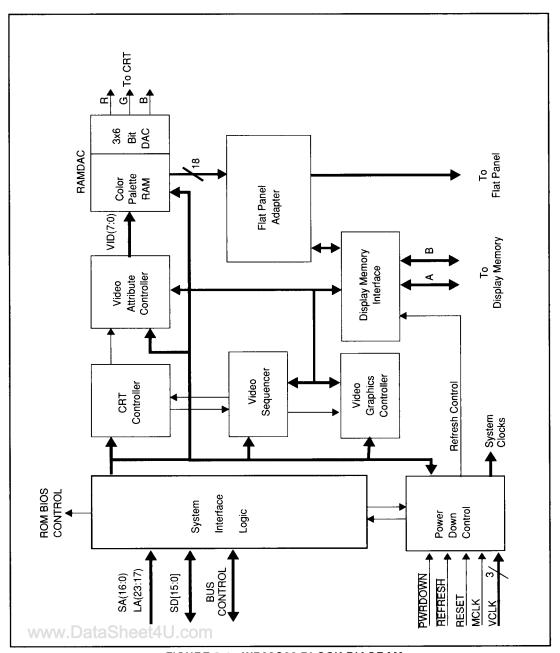

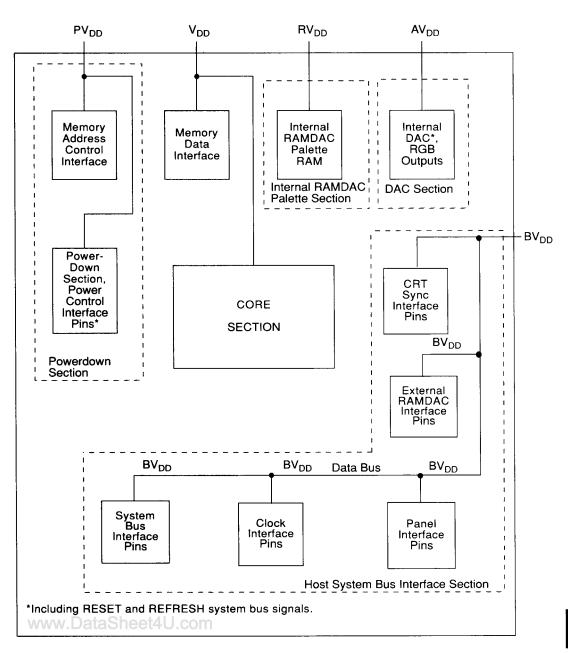

This section describes the architecture of the WD90C26. A block diagram of the architecture is shown in Figure 2-1. The components described are:

- System Interface Logic

- CRT Controller

- Video Sequencer

- Video Graphics Controller

- Video Attribute Controller

- RAMDAC

- Flat Panel Adapter

- Display Memory Interface

- Power-Down Control

### 2.1 SYSTEM INTERFACE LOGIC

The WD90C26 includes a host system interface for direct connection to an Industry Standard Architecture (ISA) bus or IBM compatible Micro-Channel bus. The interface allows the following features:

- Full 16-bit I/O and memory cycles

- Zero wait-state performance capability

- 16-bit to 8-bit memory data path conversion

- Full decoding of 16 MBytes of memory space for mapping of video memory, without requiring external decode logic

- Internal buffering of system operations to speed performance

- External video BIOS ROM

### 2.2 CRT CONTROLLER

A VGA-compatible CRT controller includes the following functions:

- Generates video buffer addresses for screen refresh operations

- Generates monitor synchronization signals

- Controls an alpha-numeric cursor

- May be set with remapped register locations to operate as a CGA, MDA, or Hercules CRT controller

- Register shadowing

#### 2.3 VIDEO SEQUENCER

The VGA compatible video sequencer is the central timing and memory control section of the WD90C26. Its functions include the following:

- · Generation of memory handshake signals

- Control of CRT controller timings

- Provision of general interface timing and control signals to the balance of the WD90C26

### 2.4 VIDEO GRAPHICS CONTROLLER

The VGA video graphics controller performs VGA graphics operations on video data such as AND, OR, XOR, rotate, and color comparison functions.

#### 2.5 VIDEO ATTRIBUTE CONTROLLER

The WD90C26 controller's video attributes are added to display data by the Video Attribute Controller. Data added includes:

- Standard text attributes

- VGA graphics mode attributes

- Cursor display

- Screen border color

The Video Attribute Controller also performs data conversion from modes like packed pixel, planar, or text mode into video data to be presented to the RAMDAC.

#### 2.6 RAMDAC

Integrated into the WD90C26 is a fully VGA-compatible high-speed 6-bit RAMDAC. This RAMDAC directly drives VGA and super-VGA color or monochrome analog monitors.

RAMDAC

FIGURE 2-1 WD90C26 BLOCK DIAGRAM

RAMDAC

#### 2.7 FLAT-PANEL ADAPTER

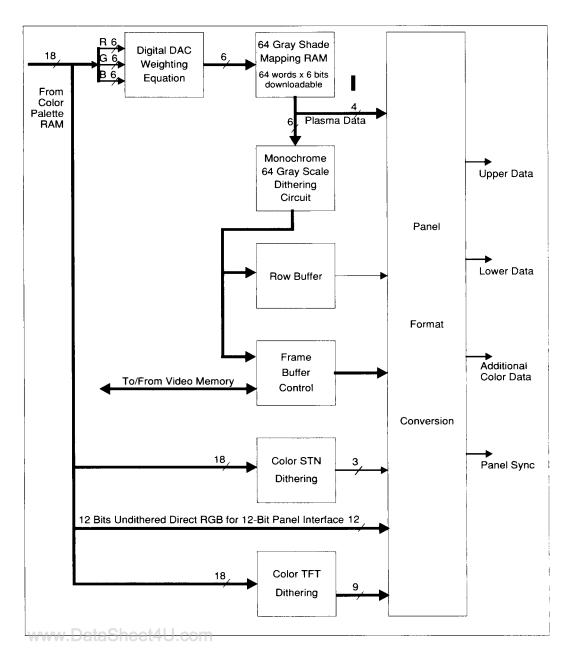

The flat-panel adapter takes video information from the WD90C26 controller's internal RAMDAC color palette RAM and converts it into the format appropriate for the type of panel to be attached.

The following functions occur in the flat-panel adapter:

- "Digital DAC" color to monochrome gray scale conversion

- Gray scale mapping

- Gray shade dithering

- Color STN LCD panel dithering circuitry

- Color TFT LCD panel dithering

- Direct 12-bit panel support

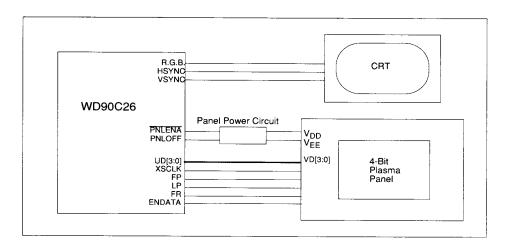

- Plasma panel support

- Row buffering

- Frame buffering

- Panel format conversion

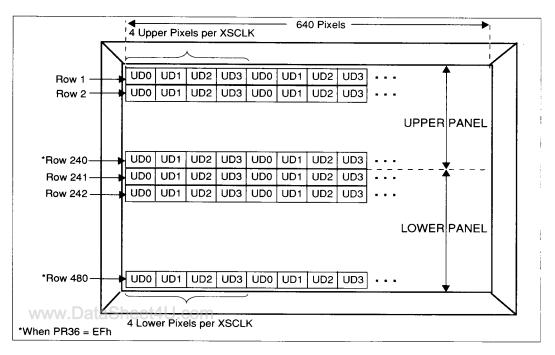

These functions are shown in Figure 2-2.

# 2.7.1 Color to Gray Scale Conversion

For monochrome flat-panel display of what normally would be a color analog video output, a digital equivalent of the RAMDAC function is required to sum color information together into video signals. This function is accomplished through use of a digital equivalent of the DAC function, which takes the RGB color palette RAM outputs and converts them to their digitally weighted monochrome equivalent. Weighting is performed using NTSC standard algorithms. Color to gray scale conversion can be disabled for Monochrome Display Adapter emulation applications.

# 2.7.2 Gray Scale Mapping

The WD90C26 controller's flat-panel adapter circuits incorporate an orthogonal 64-word x 6 bit gray-scale to gray-shade mapping RAM. This mapping RAM serves as a firmware-programmable lookup table that can be configured to map gray scale values from color-to-gray scale conversion into the dithered gray-scale shades best suited to a particular panel model.

Maximum flexibility in 'tuning' the WD90C26 to work with the characteristics of a particular panel is possible via this mapping RAM. Its size also allows finer control when selecting dithering patterns from the 64-shade monochrome dithering circuit, allowing any monochrome panel to perform to its best in displaying visually accurate gray scales.

Western Digital utility programs are available for the WD90C26 that can simplify the task of selecting mapping RAM programming values for a panel type (refer to Appendix B). Gray scale mapping may be bypassed for 1:1 gray scale to gray scale mapping.

# 2.7.3 Gray Shade Dithering

Monochrome gray shade dithering circuit provides a total of 64 shades of gray on monochrome flat-panel displays. All 64 shades can be simultaneously displayed. Simultaneous display of 64 shades in VGA modes is possible in 256 color video modes only.

# 2.7.4 Color STN Dithering

The WD90C26 dithering circuity supports color display from the full 256K VGA palette for dual-bit interface color STN panels.

# 2.7.5 Color TFT Panel Dithering Circuit

For 9-bit interface color TFT panels, the dithering circuit supports a total of 27K colors.

### 2.7.6 Direct 12-Bit TFT Panel Support

The WD90C26 drives 12-bit TFT panels with direct undithered color for a palette of 4K colors.

### 2.7.7 Plasma Panel Support

The WD90C26 drives plasma panels with undithered data direct from the outputs of the mapping RAM. Plasma panels are also "tunable" though the use of the mapping RAM for optimum use of their limited gray scale capability.

RAMDAC

FIGURE 2-2 FLAT PANEL ADAPTER SECTION BLOCK DIAGRAM

DISPLAY MEMORY INTERFACE

#### 2.7.8 Row Buffering

Monochrome dual-panel displays (most monochrome LCDs) are directly supported by the WD90C26 due to its capability to internally buffer alternating panel data without requiring external memory buffering.

### 2.7.9 Frame Buffering

The WD90C26 includes a frame buffering capability that allows simultaneous display on a CRT and on a dual-panel monochrome display. This function requires that a 256Kx4 DRAM be attached to the Bank B memory interface.

When simultaneous display is not required, the WD90C26 controller's internal row buffering provides all the required support for a dual-panel display.

#### 2.7.10 Panel Format Conversion

The internal panel format conversion circuit provides the flexibility to reformat color or monochrome panel data into the particular pixel grouping required. The panel format conversion also includes the conversion circuits needed for the WD90C26 to drive the WD90C55 VGA Color LCD Interface.

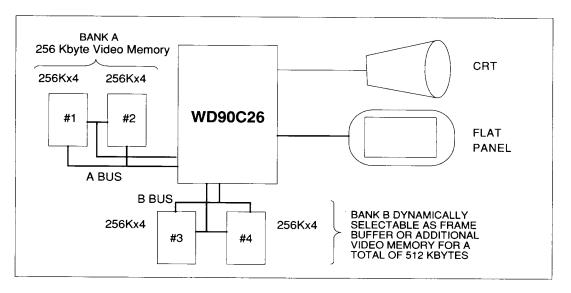

#### 2.8 DISPLAY MEMORY INTERFACE

The display memory interface that controls videomemory DRAM connects to video memory DRAM via two separate external memory buses. These buses allow accommodation of the changing needs of performance, feature support, and power conservation. Descriptions of these buses follow.

The Bank A bus is used to interface 8-bit video memory configurations, or as the lower byte interface for 16-bit video memory configurations.

The Bank B bus is used as the frame buffer interface when simultaneous display on a CRT and a dual-panel display is required.

When simultaneous display with a dual-panel display is not required, the Bank B bus is used to access the upper byte of 512 Kbyte of video memory organized as 256Kx16, or Bank B memory interface signals can be held static.

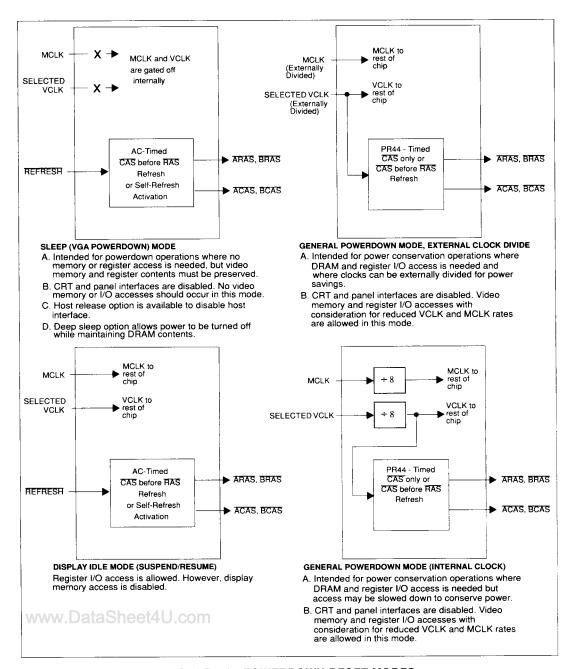

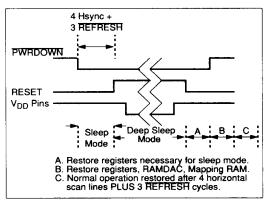

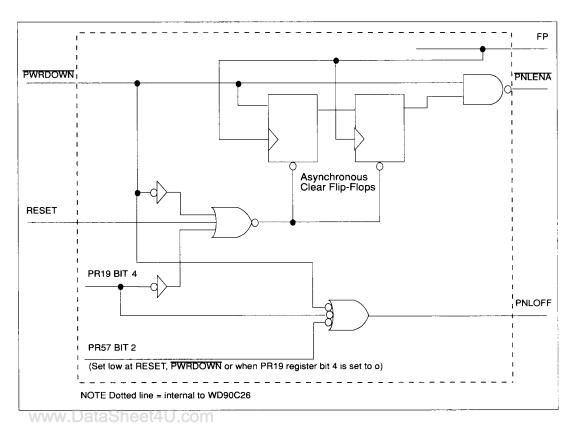

#### 2.9 POWER-DOWN CONTROL

The WD90C26 controller's ability to control power consumption allows it to work successfully in portable applications. Power consumption is managed by the power-down control block, which performs the following functions:

- Turns off clocks to unused portions of the WD90C26

- Provides refresh signals to video memory when normal refresh functions are shut down

- Controls wakeup/sleep cycling

- Reduces chip power during power-down mode

- Sequences chip reset operations

### 3.0 INTERFACES

#### 3.1 INTRODUCTION

This section describes the following WD90C26 interfaces:

- System Interface Allows the WD90C26 to directly interface to ISA bus-based systems or to MicroChannel bus-based systems

- BIOS Support Interface Allows the WD90C26 to provide an enable output for external video BIOS memory

- Video Memory Interface Allows connection of either 2, 3, or 4 256K x 4 DRAMS or one 256Kx16 DRAM

- Video Interface Allows direct connection to most PC-compatible CRTs and to a wide range of industry-standard flat-panel types

- Clock Interface Controls clock oscillators or allows up to four separate frequency inputs

#### 3.2 SYSTEM INTERFACE

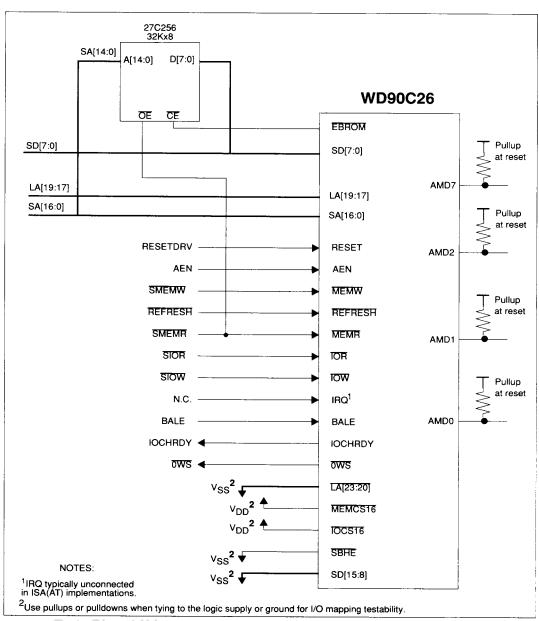

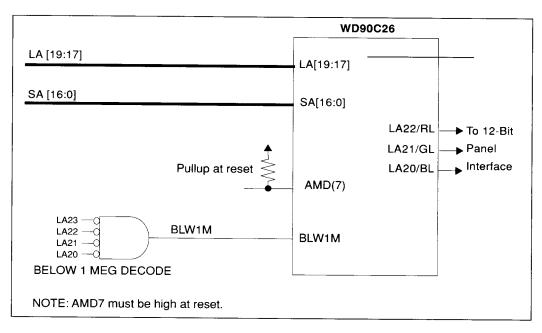

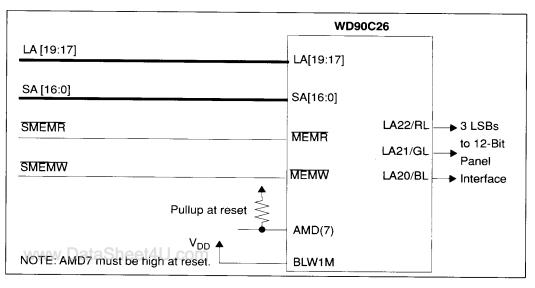

The WD90C26 is designed to directly interface to ISA bus based or MicroChannel based systems.

System interface selection is done by pulling high or low a video memory data line at time of chip reset. Refer to configuration bits in Section 6 for details on system interface bus selection.

### 3.2.1 Register Map

For both MicroChannel and ISA Bus operations, the WD90C26 is mapped into the system I/O address space as the standard set of VGA I/O registers.

Extended indexed "PR" registers at locations 3B5h/3D5h and 3C5h and 3CFh are used to control the vast amount of features beyond those of standard VGA operation.

Refer to Section 5 for specific information about the use of each standard and PR register.

The WD90C26 has a 1-1/2 word write buffer which operates as a 2-cycle write buffer. This allows the WD90C26 to operate with a very high percentage of true zero wait state performance.

### 3.2.2 Power Conserving Bus Drivers

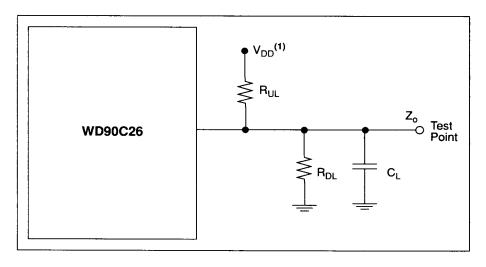

The WD90C26 is designed to be a portable computing device where driving a large capacitive bus, such as found in traditional PCs, is not a factor. To reduce power consumption, the WD90C26 controller's system interface has been designed to drive typical loads found in laptop applications where bus devices are fewer and closely grouped. For additional information on power consumption, refer to the Electrical Specifications in Section 9.

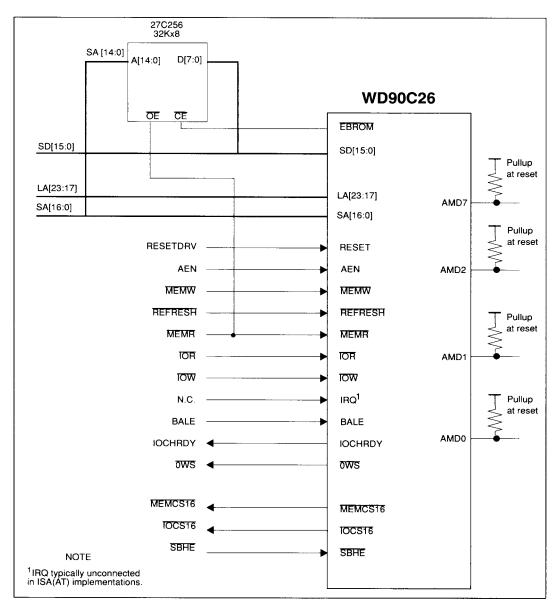

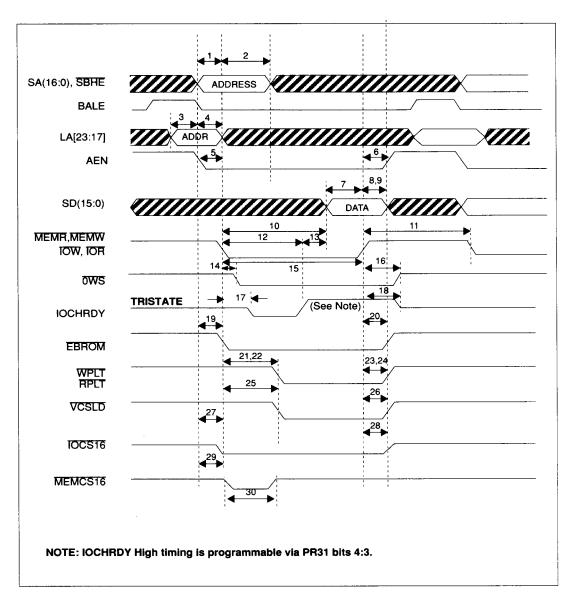

### 3.2.3 ISA Bus Interface Signals

The WD90C26 interfaces to an ISA bus at bus clock rates of up to 12.5 MHz. The WD90C26 supports full 16-bit memory and I/O transfers. Support of 16-bit memory transfers is independent of whether the WD90C26 has an 8-bit or 16-bit video memory path, although increased performance occurs when a 16-bit video memory is available.

The following ISA Bus signals are directly supported by the WD90C26:

| LA[23:17] | IOW        |

|-----------|------------|

| SA [16:0] | MEMCS16    |

| BALE      | IOCS16     |

| SBHE      | IOCHRDY    |

| AEN       | ŌWS (SRDY) |

| SD[15:0]  | REFRESH    |

| MEMR      | RESET      |

| MEMW      | IRQ        |

| IOR       |            |

LA(23:17) addresses are latched internal to the WD90C26 by the BALE signal to eliminate bus timing problems in some common system implementations.

8/16-bit I/0 and 8/16 bit memory operation may be separately enabled by selectively enabling IOCS16 and MEMCS16 bus interface signals.

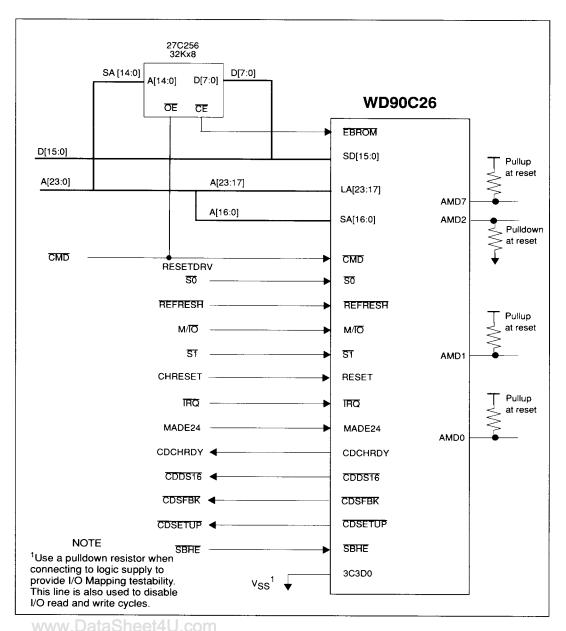

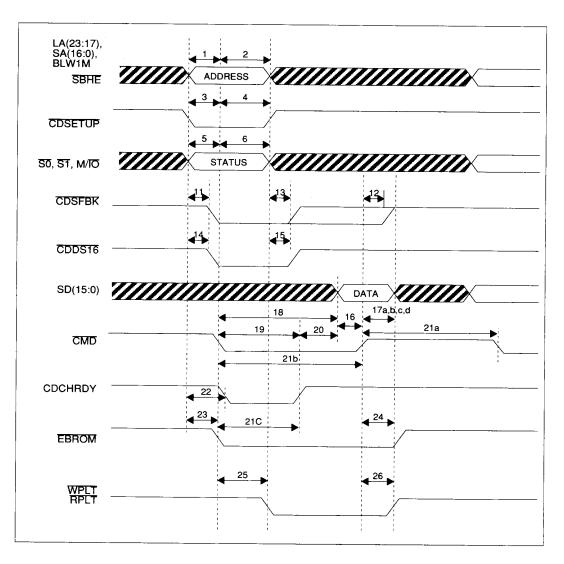

# 3.2.4 MicroChannel Interface Signals

The WD90C26 directly supports the following MicroChannel interface signals:

| A[23:0] | SBHE           |

|---------|----------------|

| CDSFBK  | <del>S</del> 0 |

| M/IO    | <del>ছ</del> 1 |

| D[15:0] | TRQ            |

| CDDS16  | CDSETUP        |

| CDCHRDY | CHRESET        |

| CMD     | REFRESH        |

| MADE24  |                |

In addition, the WD90C26 supports both an internal and external decode of I/O address 3C3 bit 0 as a video memory and I/O decode enable.

For full MicroChannel compatibility, only the lower 16 bits of system address bus are decoded for I/O accesses.

### 3.3 BIOS SUPPORT INTERFACE

The WD90C26 can be configured to provide an enable output for an external 8-bit video BIOS

PROM. The WD90C26 can be configured to automatically map this external BIOS in to the system memory map at time of reset, and then selectively map it in or out thereafter. Decodes are provided for the 32K of VGA video BIOS address space as defined in the VGA architecture. The WD90C26 also supports the ability to dynamically map out the highest 2K of the 32K VGA BIOS space.

Refer to *Using Features* in Section 6, for information on how to configure the WD90C26 for video BIOS support.

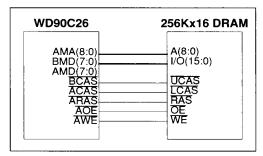

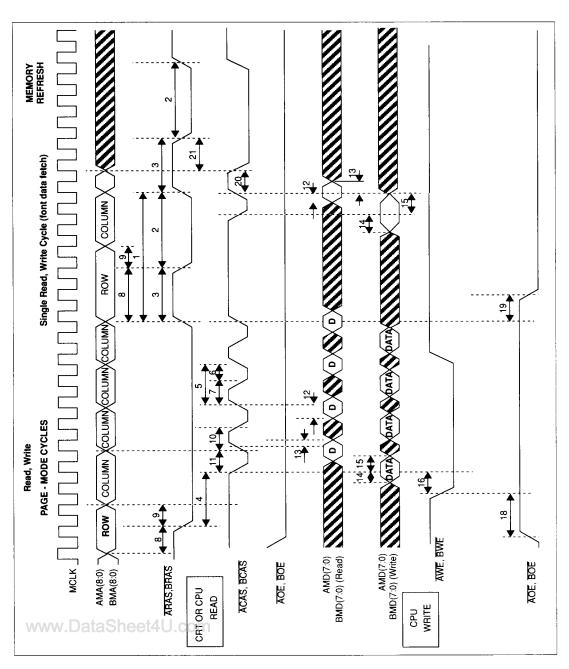

### 3.4 VIDEO MEMORY INTERFACE

The WD90C26 is designed to operate with either 2, 3, or 4 256Kx4 DRAMs or a single 256Kx16 DRAM, with a variety of performance available at each step.

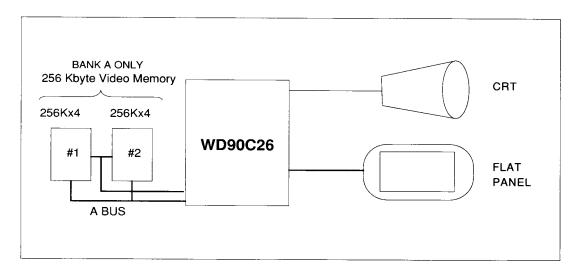

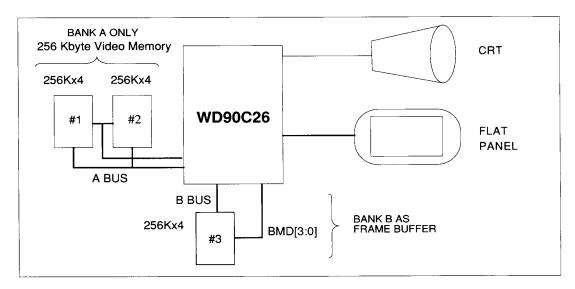

Table 3-1 matches the display modes with Figures 3-1 through 3-4 which are provided on the following pages.

| FIGURE       | FUNCTIONS SUPPORTED                                                                                                                                                                                          | DRAMS        |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 3-1          | Simultaneous display on a CRT and any non-dual-panel flat-panel display     Non-simultaneous display with dual-panel multiplexed LCD or mono display                                                         | 2<br>256Kx4  |

| 3-2          | Simultaneous display of a CRT and dual panel multiplexed LCD display.                                                                                                                                        | 3<br>256Kx4  |

| 3-3          | <ul> <li>Use of 16-bit 256 Kbyte video RAM except when dual-panel multiplexed display and CRT are used simultaneously.</li> <li>Supports 256 color mode on 640x400 and 640x480 resolution display</li> </ul> | 4<br>256Kx4  |

| 3-4<br>WWW.I | Simultaneous display operation with all flat panel types except dual-<br>panel LCDs     Supports 256 color mode on 640x400 and 640x480 resolution<br>displays                                                | 1<br>256Kx16 |

TABLE 3-1 SUMMARY OF DISPLAY CAPABILITIES AND REQUIRED DRAM

# 3.4.1 2 DRAM Implementation

FIGURE 3-1 2 DRAM IMPLEMENTATION

In this 2 DRAM implementation, the WD90C26 can support the following:

- simultaneous display on a CRT and any nondual-panel flat-panel display such as active matrix (TFT), multiplexed (STN) color, plasma, and EL.

- non-simultaneous display with a monochrome dual-panel multiplexed (STN) LCD.

This memory configuration provides for the lowest active power utilization since only two external DRAMs are active.

# 3.4.2 3 DRAM Implementation

FIGURE 3-2 3 DRAM IMPLEMENTATION

When 3 DRAMs are used, the WD90C26 can additionally support the following:

simultaneous display of a CRT and a monochrome dual-panel LCD display. DRAM #3 may be disabled under firmware control when this simultaneous display feature is not needed, allowing power savings when the two displays are not simultaneously connected or when the flat-panel is not a dual-panel type.

### 3.4.3 4 DRAM Implementation

FIGURE 3-3 4 DRAM IMPLEMENTATION

In addition to the features of the 2 DRAM and 3 DRAM modes, the following features are supported when 4 256Kx4 DRAMs are used:

- the ability to use 512K video RAM except in those occasional times when a dual panel multiplexed display and a CRT are used simultaneously.

- support of 640x400x256 and 640x480x256 color modes

Bank B of DRAM may also be disabled by firmware for power reduction, and as before DRAM #3 may be used alone for simultaneous display support of a dual panel display and CRT, while DRAM #4 is disabled.

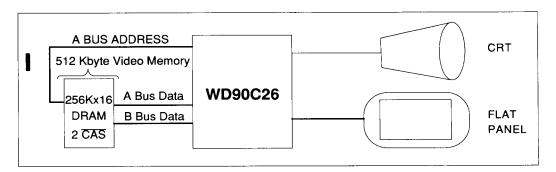

# 3.4.4 Single 256K x 16 DRAM Implementation

FIGURE 3-4 SINGLE 256K x 16 DRAM IMPLEMENTATION

The WD90C26 may be used with a single 2 CAS 256Kx16 DRAMS, providing 512 Kbytes of video memory and 16-bit memory performance. The following features are supported:

- Simultaneous display operation with all flatpanel types except dual-panel LCDs is allowed

- support of 640x400x256 and 640x480x256 color modes

CLOCK INTERFACE

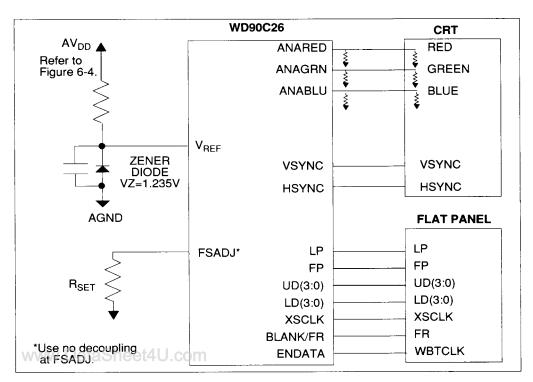

### 3.5 VIDEO INTERFACES

The WD90C26 supports a number of video interfaces allowing it to directly connect to most PC compatible CRTs and to a wide range of industry-standard flat-panel types. This support is achieved through configurable CRT and flat-panel interfaces.

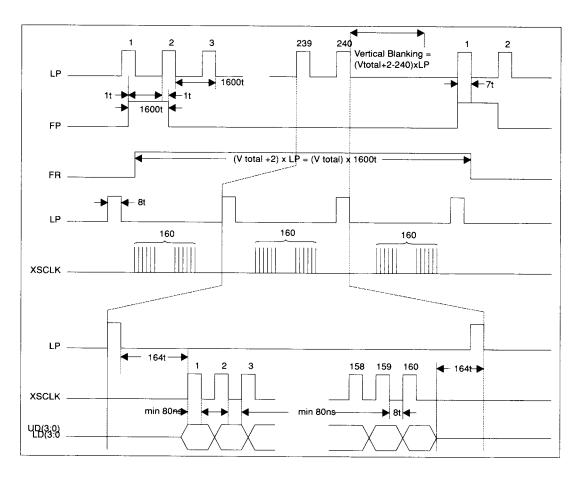

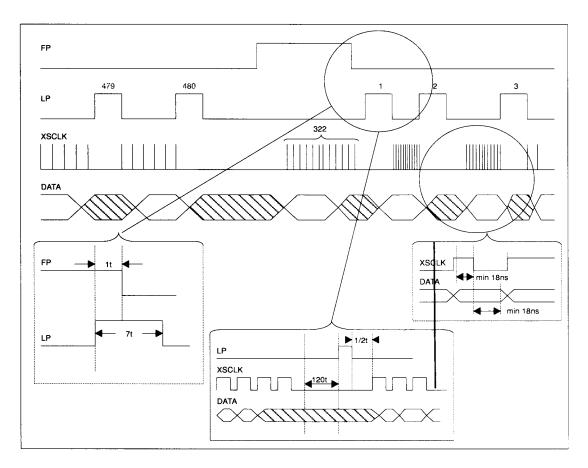

#### 3.5.1 Flat Panel Interface

One of the key features of the WD90C26 is a configurable video output port designed for support of a number of flat-panel technologies. This port is designed to directly support a number of panel types without requiring external interface formatting circuitry. Refer to *Panel Interfacing* in Section 6 for a description of the different panel interfaces available and the methods for configuring the WD90C26 for each type of interface.

Programmable flat-panel timing signals allow wide degrees of flexibility in configuring panel interfaces, making the WD90C26 usable with most popular flat-panel designs for PC applications.

The flat panel interface may also be programmed to interface with the WD90C55 VGA Color LCD Interface for certain color multiplexed STN LCD panels with special interface requirements.

# 3.5.2 Analog CRT Interface

The WD90C26 includes a complete VGA compatible CRT interface with on-board 256 x 18-bit RAMDAC, which can directly drive analog VGA compatible color or monochrome displays.

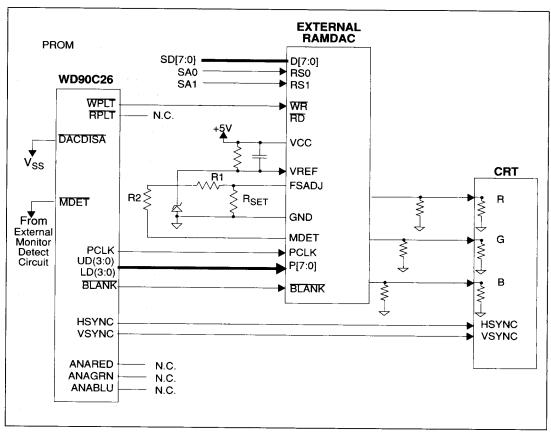

#### 3.5.3 External RAMDAC Interface

For applications where use of an external RAM-DAC or equivalent external function is desired, the WD90C26 flat-panel interface can be configured as an industry-standard RAMDAC interface instead of flat-panel pixel data. This allows the WD90C26 to be used in special applications where a 24-bit RAMDAC is needed or where special panel pixillization techniques are required.

#### 3.5.4 Video Modes

The WD90C26 supports a number of video modes including standard IBM modes, VESA defined extended modes, and Western Digital/Paradise Video modes. All VGA and most VE modes are supported on both a panel and a CRT. Modes with higher resolution than that of the attached panel are supported in CRT only modes of operation.

Refer to Section 7 for information about screen characteristics.

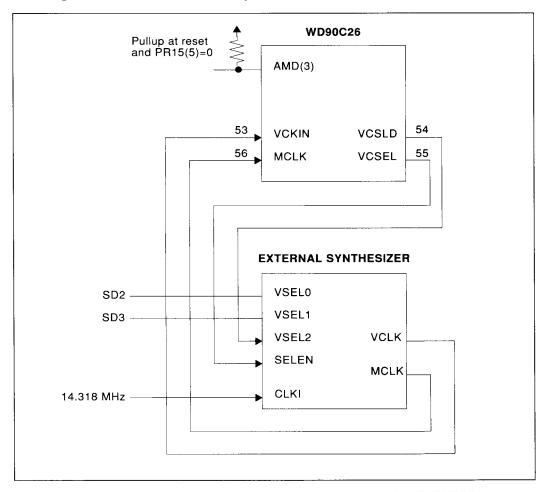

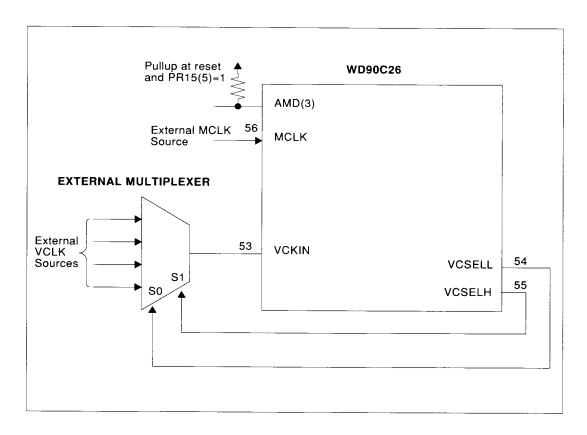

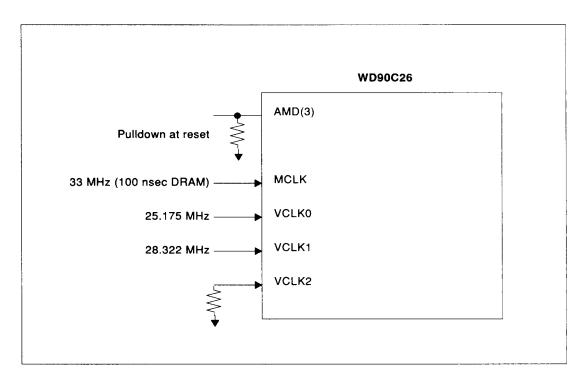

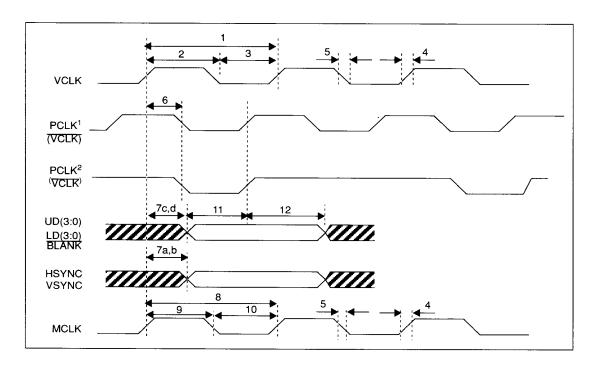

#### 3.6 CLOCK INTERFACE

The WD90C26 has four clock input signal pins:

- VCLK0

- VCLK1

- VCLK2

- MCLK

Three of these (VCLK 2, 1, and 0) are normally connected to pixel rate oscillators. VCLK1 and VCLK2 may alternately be configured to control an external clock multiplexer or clock generator. In this configuration, VCLK0 becomes the clock input while VCLK1 and VCLK2 become outputs used to drive the multiplexor select inputs.

The memory clock input, MCLK, is used by the internal logic to generate all memory timing and may be up to 44.3 MHz for 70 nsec DRAMs.

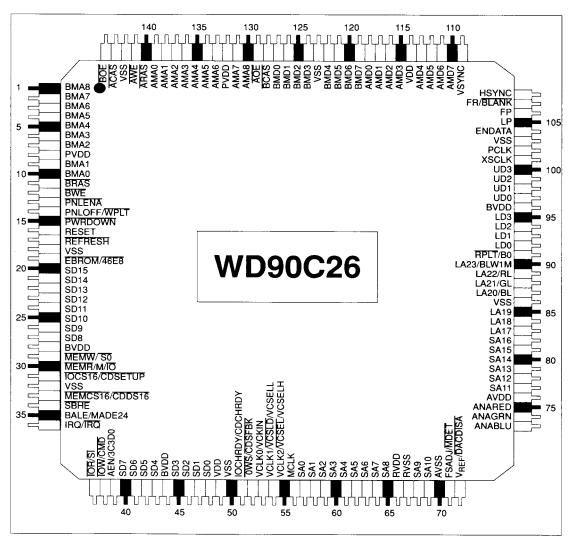

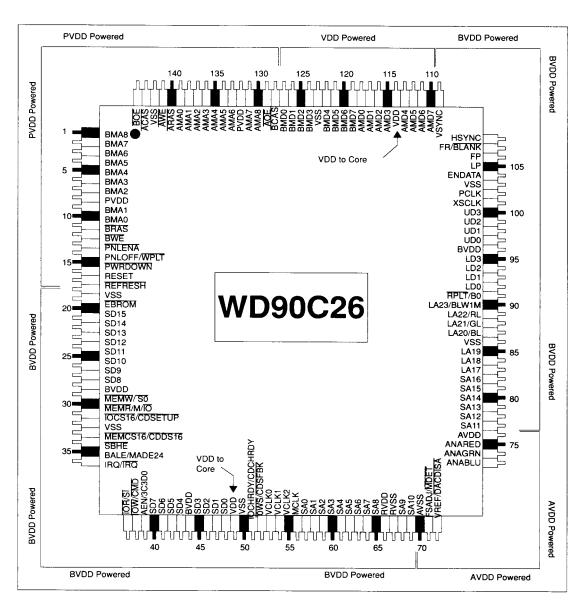

# 4.0 SIGNAL DESCRIPTIONS

### 4.1 INTRODUCTION

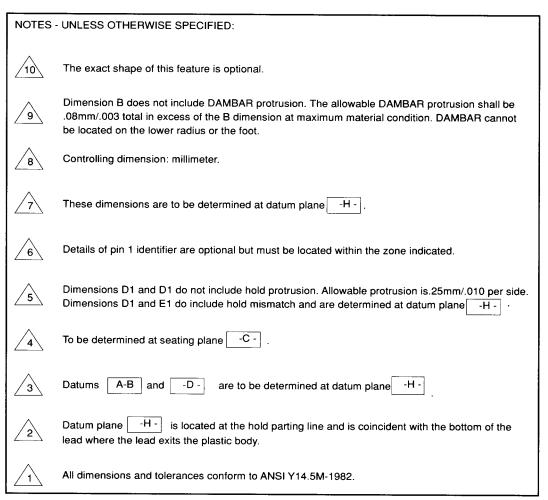

This section contains a pin diagram, a pin out table, and a signal description summary for the following groups of pins:

### **System Interface Pins**

RESET REFRESH EBROM/46E8 MEMW/SO MEMR/M/IO IOCS16/CDSETUP MEMCS16/CDDS16 SBHE BALE/MADE24 IRQ/IRQ IOR/S1 IOW/CMD AEN/3C3D0 IOCHRDY/CDCHRDY OWS/CDSFBK SD[15:0] SA[16:0] LA[19:17] LA20/BL LA21/GL LA22/RL LA23/BLW1M

### **Display Buffer Memory Interface Pins**

AMD[7:0] AMA[8:0] ACAS AOE ARAS AWE BMD[7:0] BMA[8:0] BCAS BOE BRAS

BWE

MANAY DataSheet4II com

### Internal DAC/CRT Interface Pins

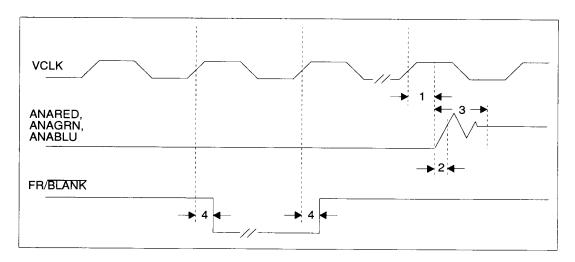

ANARED ANAGRN ANABLU V<sub>REF</sub>/DACDISA FSADJ/MDET HSYNC VSYNC

### **Clock Generation Interface Pins**

VCLK0/VCKIN VCLK1/VCSLD/VCSELL VCLK2/VCSEL/VCSELH MCLK

### **Panel Interface Pins**

PNLENA

PNLOFF/WPLT

RPLT/B0

PCLK

FR/BLANK

UD(3:0)

LD(3:0)

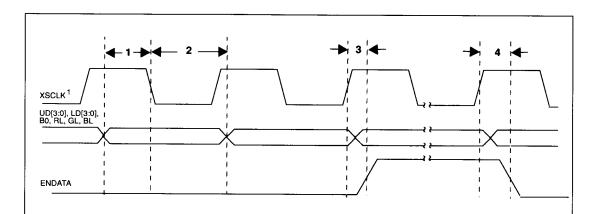

XSCLK

ENDATA

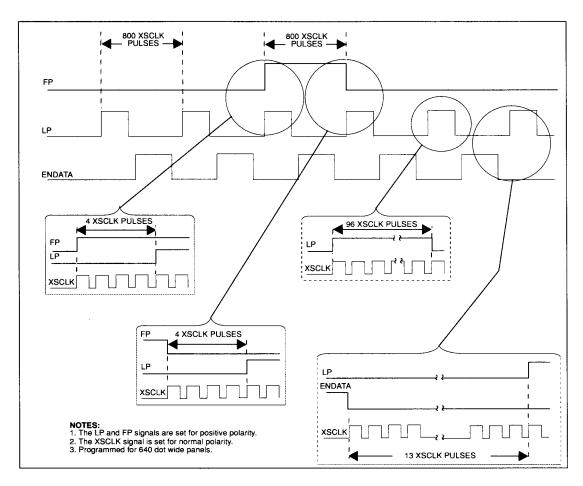

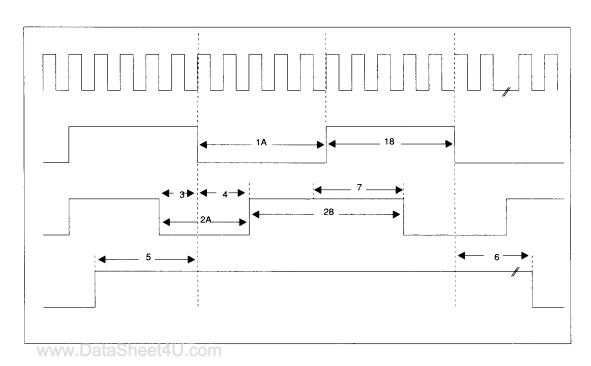

FP

LP

#### **Power Down Control Pins**

**PWRDOWN**

# **Power Pins**

V<sub>DD</sub> RV<sub>DD</sub> AV<sub>DD</sub> BV<sub>DD</sub> PV<sub>DD</sub> V<sub>SS</sub> RV<sub>SS</sub> AV<sub>SS</sub>

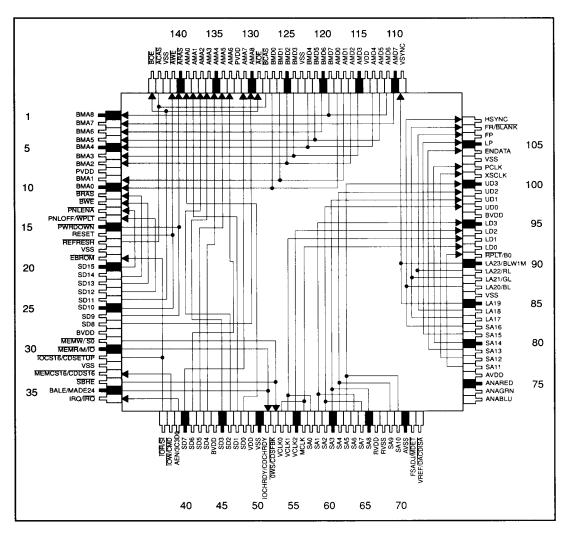

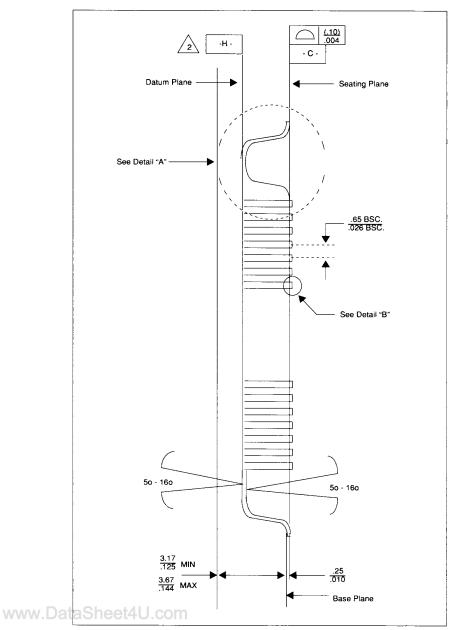

FIGURE 4-1 WD90C26 PIN DIAGRAM, 144 PIN JEDEC MQFP PACKAGE

|     | BMA8             | 30. | MEMR/M/IO                  | 59. | SA2                           | 88.  | LA21/GL          | 117. | AMD1             |

|-----|------------------|-----|----------------------------|-----|-------------------------------|------|------------------|------|------------------|

| 2.  | BMA7             | 31. | IOCS16/<br>CDSETUP         | 60. | SA3                           | 89.  | LA22/RL          | 118. | AMD0             |

| 3.  | ВМА6             | 32. | V <sub>SS</sub>            | 61. | SA4                           | 90.  | LA23/BLW1M       | 119. | BMD7             |

| 4.  | BMA5             | 33. | MEMCS16/<br>CDDS16         | 62. | SA5                           | 91.  | RPLT/B0          | 120. | BMD6             |

| 5.  | BMA4             | 34. | SBHE                       | 63. | SA6                           | 92.  | LD0              | 121. | BMD5             |

| 6.  | ВМАЗ             | 35. | BALE/<br>MADE24            | 64. | SA7                           | 93.  | LD1              | 122. | BMD4             |

| 7.  | BMA2             | 36. | IRQ/IRQ                    | 65. | SA8                           | 94.  | LD2              | 123. | V <sub>SS</sub>  |

| 8.  | PV <sub>DD</sub> | 37. | IOR/SI                     | 66. | RV <sub>DD</sub>              | 95.  | LD3              | 124. | BMD3             |

| 9.  | BMA1             | 38. | IOW/CMD                    | 67. | RV <sub>SS</sub>              | 96.  | BV <sub>DD</sub> | 125. | BMD2             |

| 10. | BMA0             | 39. | AEN/3C3D0                  | 68. | SA9                           | 97.  | UD0              | 126. | BMD1             |

| 11. | BRAS             | 40. | SD7                        | 69. | SA10                          | 98.  | UD1              | 127. | BMD0             |

| 12. | BWE              | 41. | SD6                        | 70. | AVSS                          | 99.  | UD2              | 128. | BCAS             |

| 13. | PNLENA           | 42. | SD5                        | 71. | FSADJ/MDET                    | 100. | UD3              | 129. | AOE              |

| 14. | PNLOFF/<br>WPLT  | 43. | SD4                        | 72. | V <sub>REF</sub> /<br>DACDISA | 101. | XSCLK            | 130. | AMA8             |

| 15. | PWRDOWN          | 44. | BV <sub>DD</sub>           | 73. | ANABLU                        | 102. | PCLK             | 131. | AMA7             |

| 16. | RESET            | 45. | SD3                        | 74. | ANAGRN                        | 103. | V <sub>SS</sub>  | 132. | PV <sub>DD</sub> |

| 17. | REFRESH          | 46. | SD2                        | 75. | ANARED                        | 104. | ENDATA           | 133. | AMA6             |

| 18. | V <sub>SS</sub>  | 47. | SD1                        | 76. | AV <sub>DD</sub>              | 105. | LP               | 134. | AMA5             |

| 19. | EBROM/46E8       | 48. | SD0                        | 77. | SA11                          | 106. | FP               | 135. | AMA4             |

| 20. | SD15             | 49. | v <sub>DD</sub>            | 78. | SA12                          | 107. | FR/BLANK         | 136. | АМАЗ             |

| 21. | SD14             | 50. | V <sub>SS</sub>            | 79. | SA13                          | 108. | HSYNC            | 137. | AMA2             |

| 22. | SD13             | 51. | IOCHRDY/<br>CDCHRDY        | 80. | SA14                          | 109. | VSYNC            | 138. | AMA1             |

| 23. | SD12             | 52. | OWS/<br>CDSBFK             | 81. | SA15                          | 110. | AMD7             | 139. | AMA0             |

| 24. | SD11             | 53. | VCLK0/VCKIN                | 82. | SA16                          | 111. | AMD6             | 140. | ARAS             |

| 25. | SD10             | 54. | VCLK1/<br>VCSLD/<br>VCSELL | 83. | LA17                          | 112. | AMD5             | 141. | AWE              |

| 26. | SD9              | 55. | VCLK2/<br>VCSEL/<br>VCSELH | 84. | LA18                          | 113. | AMD4             | 142. | V <sub>SS</sub>  |

| 27. | SD8              | 56. | MCLK                       | 85. | LA19                          | 114. | v <sub>DD</sub>  | 143. | ACAS             |

| 28. | BV <sub>DD</sub> | 57. | SA0                        | 86. | V <sub>SS</sub>               | 115. | AMD3             | 144. | BOE              |

| 29. | MEMW/SO          | 58. | SA1                        | 87. | LA20/BL                       | 116. | AMD2             | 145. |                  |

### 4.2 SYSTEM INTERFACE PINS

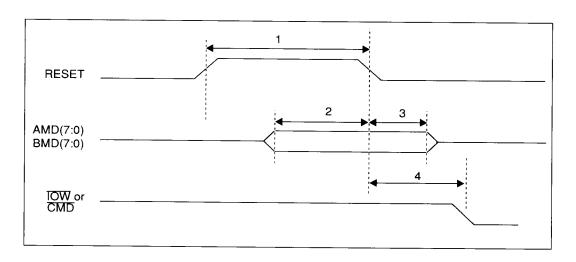

The following table describes each system interface pin on the WD90C26. The WD90C26 system interface can be configured for either ISA bus or MicroChannel interface support by setting CONF/2 high or low by pulling high or low the AMD2 pin at reset. Other configuration options may also be selected by setting configuration bits high or low at reset through pulling memory data lines high or low. The section called "Using Chip Features" contains a complete description of the various configuration options available by setting these configuration bits.

| PIN      | SYMBOL  | TYPE            | DESCRIPTION                                                                                                                                                                                                                                                   |

|----------|---------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16       | RESET   | Input,          | WD90C26 Controller Initialization Signal                                                                                                                                                                                                                      |

|          |         | Active<br>High  | Typical usage in ISA Bus based system: connected to ISA Bus RESET signal.                                                                                                                                                                                     |

|          |         |                 | Typical usage in MicroChannel based system: connected to MicroChannel RESETDRV signal.                                                                                                                                                                        |

| 17       | REFRESH | Input,          | DRAM Refresh                                                                                                                                                                                                                                                  |

|          |         | Active<br>Low   | Active low. The WD90C26 uses this input to initiate refresh operations to its video buffer memory. It also uses this signal as a negative qualifier for memory operations. REFRESH must be inactive high for memory reads or writes to occur.                 |

| 19 EBROM | Output, | Enable BIOS ROM |                                                                                                                                                                                                                                                               |

| :        |         | Active<br>Low   | EBROM if CONF(0)=0, independent of CONF(2) setting.                                                                                                                                                                                                           |

|          |         | Totem-          | In BIOS ROM Map-in mode, where CONF(0)=0 the WD90C26 drives this output low when it decodes system accesses to video BIOS ROM and a memory read operation is requested from an address range identified within the WD90C26 as a video BIOS ROM address.       |

|          |         |                 | This function may be disabled by setting PR1 register bit 0 to 1, which forces CONF(0) to 1 until the next reset operation.                                                                                                                                   |

|          | 46E8    |                 | 46E8 I/O Write                                                                                                                                                                                                                                                |

|          |         | Active<br>Low   | If CONF(2)=1 (ISA Bus Mode) and CONF(0)=1 this pin is an external decode of I/O address 46E8 writes, which can be used as BIOS ROM page select.                                                                                                               |

|          |         | Totem-<br>pole  | In this mode, writes to I/O addresses 46E8, 56E8, 66E8, and 76E8 appear as lows at this pin. This decode of writes to 46E8 is disabled by setting PR16(7) high. Descriptions of internal I/O port registers provide more details on how this feature is used. |

TABLE 4-2 SYSTEM INTERFACE PINS

| PIN       | SYMBOL | TYPE            | DESCRIPTION                                                                                                                                                                                                                                                                 |

|-----------|--------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29        | MEMW   | Input,          | Memory Write                                                                                                                                                                                                                                                                |

|           |        | Active<br>Low   | MEMW if CONF(2)=1 (ISA Bus Mode). Memory write input from ISA bus.                                                                                                                                                                                                          |

|           |        |                 | When the WD90C26 is in ISA Bus Mode, this pin is the industry-standard MEMW bus signal, and indicates to the WD90C26 that a memory write bus cycle is occurring.                                                                                                            |

|           |        |                 | Because MEMW may also be active during refresh cycles, the WD90C26 internally gates MEMW with REFRESH.                                                                                                                                                                      |

| <u>80</u> | Input, | SO Cycle Decode |                                                                                                                                                                                                                                                                             |

|           |        | Active          | S0 if CONF(2)=0 (MicroChannel Mode).                                                                                                                                                                                                                                        |

|           |        | 2011            | When the WD90C26 is in MicroChannel Mode, this pin is the MicroChannel S0 channel status input, which the WD90C26 uses, along with S1, M/IO, and CMD, to decode MicroChannel bus cycles.                                                                                    |

| 30        | MEMR   | Input,          | Memory Read                                                                                                                                                                                                                                                                 |

|           |        | Active<br>Low   | MEMR if CONF(2)=1 (ISA Bus Mode).                                                                                                                                                                                                                                           |

|           |        |                 | When the WD90C26 is in ISA Bus Mode, this pin is the industry-standard MEMR bus signal. This indicates to the WD90C26 that a memory read bus cycle is occurring. Because MEMR may also be active during refresh cycles, the WD90C26 internally gates MEMR with REFRESH.     |

|           | M/TO   | Input,          | Memory/IO Cycle                                                                                                                                                                                                                                                             |

|           |        | Active<br>Low   | M/TO if CONF(2)=0 (MicroChannel Mode)                                                                                                                                                                                                                                       |

|           |        |                 | When the WD90C26 is in MicroChannel Mode, this pin is the M/IO signal from the MicroChannel bus. A high input at this pin is interpreted by the WD90C26 as a MicroChannel Bus Memory cycle. A low signal at this pin indicates a MicroChannel Bus I/O cycle to the WD90C26. |

**TABLE 4-2 SYSTEM INTERFACE PINS**

www.DataSheet4U.com

**//**/

| PIN | SYMBOL                 | TYPE                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31  | IOCS16                 | Input,                  | I/O Chip Select 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |                        | Active<br>Low           | TOCS16 if CONF(2)=1 (ISA Bus Mode). Open Collector.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |                        |                         | Indicates the WD90C26 supports 16-bit I/O operations at the "current" I/O address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |                        |                         | In ISA Bus Mode, pin 31 becoming active low is an indication to the ISA Bus that it supports 16-bit I/O transfers at the I/O address being presented to it. Otherwise this pin is in a high-impedance state. IOCS16 is not gated by any other signals. Its function is independent of other bus control lines, bus modes, or register settings. IOCS16 is not gated by AEN, REFRESH, or PWRDOWN, but it is disabled until wakeup. IOCS16 may also be disabled by host released (PWRDOWN with PR35 bit 5=1). After wakeup, PR31 bits 1 and 2 may be used to disabled IOCS16. |

|     | CDSETUP                | Output,                 | Card Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |                        | Active<br>Low           | CDSETUP if CONF(2)=0 (MicroChannel Mode).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     | 0.0                    | O.C.                    | In MicroChannel mode, this pin is the card setup input indicating to the WD90C26 to perform setup functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 33  | MEMCS16                | Active                  | Memory Chip Select 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | Active<br>Low<br>O. C. |                         | MEMCS16 if CONF(2)=1 (ISA Bus Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |                        |                         | In ISA bus mode, Pin 33 is an indication to the system that the WD90C26 supports 16-bit memory transfers at the system address being presented. If 16-bit transfers are not supported at the address, the WD90C26 tri-states this pin. In ISA Bus applications, pin 33 is typically connected to the ISA Bus MEMCS16 signal.                                                                                                                                                                                                                                                |

|     |                        |                         | MEMCS16 is forced inactive whenever REFRESH or PWRDOWN are active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |                        |                         | MEMCS16 is an open-collector output in ISA bus mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | CDDS16                 | Output,                 | Card Data Size 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |                        | Active<br>Low           | CDDS16 if CONF(2)=0 (MicroChannel Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |                        | Totem-<br>pole          | In MicroChannel applications pin 33 indicates a 16-bit resource available at the address. CDDS16 is a totem-pole type output in MicroChannel mode.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 34  | SBHE                   | Input,                  | System Byte Hi Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ww  | w.DataSh               | Active<br>Low<br>eet4U. | SBHE indicates to the WD90C26 the mapping of bytes into high or low registers on write operations and the ordering of high and low bytes during read operations.                                                                                                                                                                                                                                                                                                                                                                                                            |

**TABLE 4-2 SYSTEM INTERFACE PINS**

| PIN | SYMBOL | TYPE                                                                                                                                                                                                                                                                                                                                                                                         | DESCRIPTION                                                                                                                                                                                                                                                                                                                   |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35  | BALE   | Input,                                                                                                                                                                                                                                                                                                                                                                                       | Address Latch Enable                                                                                                                                                                                                                                                                                                          |

|     |        | Active<br>High                                                                                                                                                                                                                                                                                                                                                                               | BALE if CONF(2)=1 (ISA Bus Mode)                                                                                                                                                                                                                                                                                              |

|     | , ingi | When the WD90C26 is in ISA Bus Mode this pin is the industry standard BALE signal input to the WD90C26. A high level is interpreted by the WD90C26 as an indication that the system address is setting up on its SA bus inputs to be latched on the falling edge of this signal. To ensure compatibility across a variety of platforms, the WD90C26 latches LA17-LA23 with the fall of BALE. |                                                                                                                                                                                                                                                                                                                               |

|     |        |                                                                                                                                                                                                                                                                                                                                                                                              | Typical usage in ISA Bus based system: connected to ISA Bus BALE signal.                                                                                                                                                                                                                                                      |

|     | MADE24 | Input,                                                                                                                                                                                                                                                                                                                                                                                       | Memory Address Enable 24                                                                                                                                                                                                                                                                                                      |

|     |        | Active<br>High                                                                                                                                                                                                                                                                                                                                                                               | MADE24 if CONF(2)=0 (MicroChannel Mode).                                                                                                                                                                                                                                                                                      |

|     |        |                                                                                                                                                                                                                                                                                                                                                                                              | When the WD90C26 is in MicroChannel Mode, this pin is the MicroChannel MADE24 input to the WD90C26 and is used by the WD90C26 as an indication that the system address is in the below-16 Mbyte range.                                                                                                                        |

| 36  | IRQ    | Q Output,<br>Active<br>High<br>Totem-                                                                                                                                                                                                                                                                                                                                                        | Interrupt Request, Active High                                                                                                                                                                                                                                                                                                |

|     |        |                                                                                                                                                                                                                                                                                                                                                                                              | IRQ if CONF(2)=1 (ISA Bus Mode)                                                                                                                                                                                                                                                                                               |

|     |        |                                                                                                                                                                                                                                                                                                                                                                                              | Active high in ISA Bus Mode.                                                                                                                                                                                                                                                                                                  |

|     | Pole/  | )                                                                                                                                                                                                                                                                                                                                                                                            | When bit 5 of the VGA Vertical Retrace End Register (I/O Address 3?5h index 11) is set to 0, this signal is set active at the occurrence of the end of vertical display of a frame of active video. IRQ stays active until cleared by momentarily setting bit 4 of the Vertical Retrace End Register to 0 and then back to 1. |

|     |        |                                                                                                                                                                                                                                                                                                                                                                                              | When bit 5 of the VGA Vertical Retrace End Register is set to 1 the activation of this pin is disabled, forcing its output to be low in ISA Bus Mode or high impedance in MicroChannel Mode.                                                                                                                                  |

|     |        |                                                                                                                                                                                                                                                                                                                                                                                              | NOTE: This pin can only be configured or the interrupt cleared if the Vertical Retrace End Register is unlocked by setting PR3 bit 0 to1.                                                                                                                                                                                     |

|     | TRQ    | Output,                                                                                                                                                                                                                                                                                                                                                                                      | Interrupt Request, Active Low                                                                                                                                                                                                                                                                                                 |

|     |        | Active<br>Low                                                                                                                                                                                                                                                                                                                                                                                | IRQ if CONF(2)=0 (MicroChannel Mode)                                                                                                                                                                                                                                                                                          |

|     |        | O.C.                                                                                                                                                                                                                                                                                                                                                                                         | Open collector in MicroChannel Mode.                                                                                                                                                                                                                                                                                          |

|     |        |                                                                                                                                                                                                                                                                                                                                                                                              | Function is identical as IRQ, described above, except active level is low and the signal is open-collector.                                                                                                                                                                                                                   |

www.DataSheet4TABLE 4-2 SYSTEM INTERFACE PINS

| PIN    | SYMBOL        | TYPE                    | DESCRIPTION                                                                                                                                                                                                                                |

|--------|---------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37     | IOR           | Input,<br>Active<br>Low | I/O Read                                                                                                                                                                                                                                   |

|        |               |                         | TOR if CONF(2)=1 (ISA Bus Mode).                                                                                                                                                                                                           |

|        |               | LOW                     | When the WD90C26 is in ISA Bus Mode, this pin indicates to the WD90C26 that an I/O read bus cycle is to occur. IOR may also be active during DMA cycles and is therefore internally qualified by AEN low.                                  |

|        | S1            | Input,                  | S1 Cycle Decode                                                                                                                                                                                                                            |

|        |               | Active<br>Low           | ST if CONF(2)=0 (MicroChannel Mode).                                                                                                                                                                                                       |

|        |               | LOW                     | When the WD90C26 is in MicroChannel Mode (AMD2 low at reset), this pin is the MicroChannel S1 channel status input, which the WD90C26 uses, along with \$\overline{S0}\$, M/IO, and \$\overline{CMD}\$, to decode MicroChannel bus cycles. |

| 38 IOW | IOW           | Input,                  | I/O Write                                                                                                                                                                                                                                  |

|        | Active<br>Low | 1                       | IOW if CONF(2)=1 (ISA Bus Mode).                                                                                                                                                                                                           |

|        |               | LOW                     | When the WD90C26 is in ISA Bus Mode, this pin indicates to the WD90C26 that an I/O read bus cycle is to occur.                                                                                                                             |

|        |               |                         | The WD90C26 internally qualifies TOW write requests with AEN low.                                                                                                                                                                          |

|        | Active        | Input,                  | Command                                                                                                                                                                                                                                    |

|        |               | Active<br>Low           | CMD if CONF(2)=0 (MicroChannel Mode)                                                                                                                                                                                                       |

|        |               |                         | When the WD90C26 is in MicroChannel Mode, this pin is interpreted by the WD90C26 as the CMD signal from a MicroChannel bus. The WD90C26 uses this signal to properly decode cycle types.                                                   |

| 39     | AEN           | Input,                  | Address Enable                                                                                                                                                                                                                             |

|        |               | Active<br>High          | AEN if CONF(2)=1 (ISA Bus Mode).                                                                                                                                                                                                           |

|        | Tign          |                         | When active high, this signal disables the WD90C26 from performing ISA bus read or write accesses. When low, system accesses to the WD90C26 are enabled.                                                                                   |

|        | 3C3D0         | Input,                  | Video Subsystem Enable Port                                                                                                                                                                                                                |

|        |               | Active                  | 3C3D0 <sup>-</sup> if CONF(2)=0 (MicroChannel Mode).                                                                                                                                                                                       |

|        | Low           |                         | In MicroChannel mode, this input when pulled active high 'wakes up' the WD90C26 in a manner identical to setting the Wakeup register (3C3h) bit 0 to 1.                                                                                    |

TABLE 4-2 SYSTEM INTERFACE PINS www.DataSheet4U.com

| PIN | SYMBOL   | TYPE                   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|----------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 51  | IOCHRDY  | Output,                | I/O Channel Ready Status                                                                                                                                                                                                                                                                                                                                                                                             |

|     |          | Active<br>High         | IOCHRDY if CONF(2)=1 (ISA Bus Mode).                                                                                                                                                                                                                                                                                                                                                                                 |

|     |          | O.C.                   | I/O Channel Ready status when active hi.                                                                                                                                                                                                                                                                                                                                                                             |

|     |          |                        | When the WD90C26 is in ISA Bus Mode pin 51 is the industry-standard IOCHRDY bus signal, and indicates readiness of the WD90C26 in responding to ISA bus read and write cycles. When the WD90C26 cannot complete the desired bus cycle within the standard or 0 wait cycle times, it will de-assert IOCHRDY by pulling it low until it is ready to complete the transfer, otherwise the IOCHRDY output is tri-stated. |

|     | CDCHRDY  | Output,                | Channel Ready                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |          | Active<br>High         | CDCHRDY if CONF(2)=1 (MicroChannel Mode).                                                                                                                                                                                                                                                                                                                                                                            |

|     |          | O.C.                   | When the WD90C26 is in MicroChannel Mode, CONF(2)=0), pin 51 is the CDCHRDY signal to a MicroChannel bus. The WD90C26 drives this pin low when additional cycle time is required.                                                                                                                                                                                                                                    |

|     |          |                        | In MicroChannel mode, CDCHRDY is brought to its high-impedance inactive state by the rising edge of the signal to CMD.                                                                                                                                                                                                                                                                                               |

|     |          |                        | Under typical conditions of video memory speeds and bus rates, the WD90C26 does not cause IOCHRDY or CDCHRDY to go inactive low or cause CDCHRDY to occur later than the minimum requirement, except in certain instances when a write operation results in an internal write data buffer overflow.                                                                                                                  |

| 52  | ōWS      | Output,                | Zero Wait State                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |          | Active<br>Low          | 0WS if CONF(2)=1 (ISA Bus Mode).                                                                                                                                                                                                                                                                                                                                                                                     |