## Wolfson AudioPlus<sup>™</sup> Stereo CODEC with Power Management

## DESCRIPTION

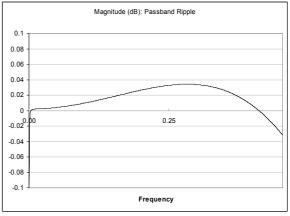

The WM8352 is an integrated audio and power management subsystem which provides a cost effective, single-chip solution for portable audio and multimedia systems.

The integrated audio CODEC provides all the necessary functions for high-quality stereo recording and playback. Programmable on-chip amplifiers allow for the direct connection of headphones and microphones with a minimum of external components. A programmable low-noise bias voltage is available to feed one or more electret microphones. Additional audio features include programmable high-pass filter in the ADC input path.

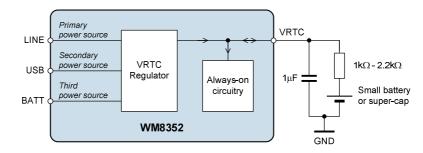

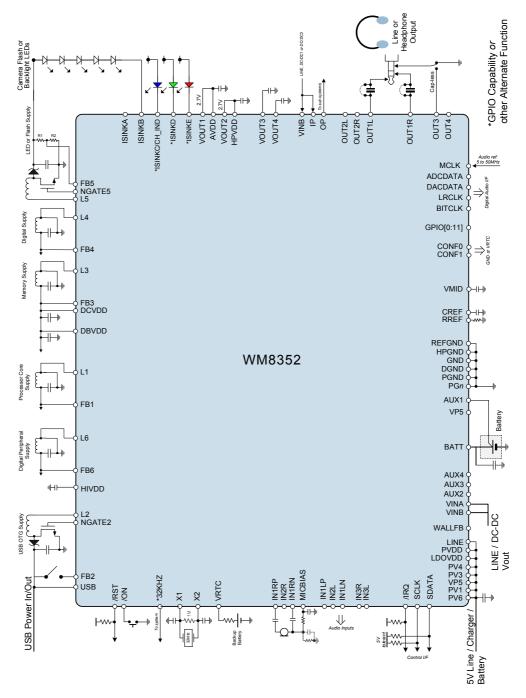

The WM8352 includes six programmable DC-DC converters, four low-dropout (LDO) regulators and a current limit switch to generate suitable supply voltages for each part of the system, including the integrated audio CODEC as well as off-chip components such as a digital core and I/O supplies, and LED lighting. An additional on-chip regulator maintains the backup power for always-on functions. The WM8352 can be powered by a lithium battery, by a wall adaptor or USB.

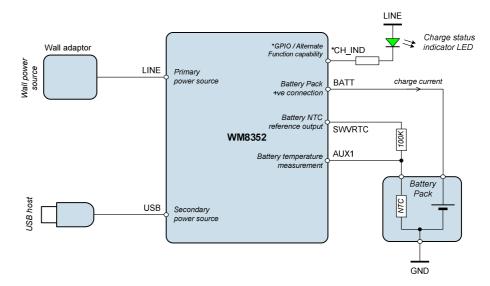

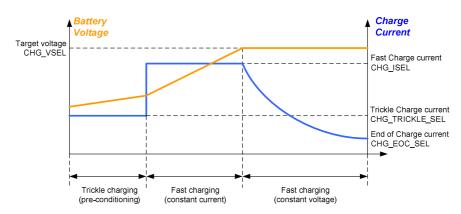

An on-chip battery charger supports both trickle charging and fast (constant current, constant voltage) charging of single-cell lithium batteries. The charge current, termination voltage, and charger time-out are programmable to suit different types of batteries.

Internal power management circuitry controls the start-up and shutdown sequencing of clocks and supply voltages. It also detects and handles conditions such as under-voltage, extreme temperatures, and deeply discharged or defective batteries, with a minimum of software involvement.

Two programmable constant-current sinks are available for driving LED strings, e.g. for display backlights or photo-flash applications, in a highly power-efficient way. Additional RGB LEDs can be driven through GPIO pins.

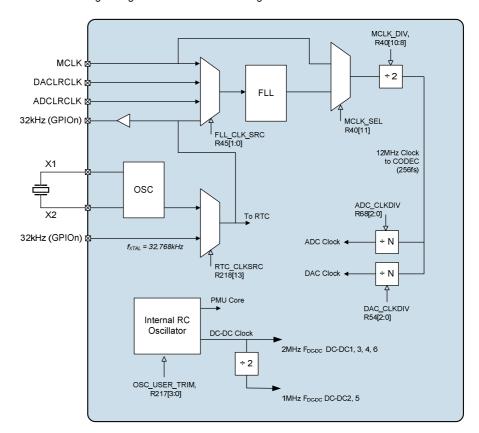

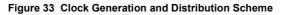

The WM8352 includes a 32.768kHz crystal oscillator, an internal RC oscillator, a real-time clock (RTC) and an alarm function capable of waking up the system. Internal circuitry can generate all clock signals required to start up the device.

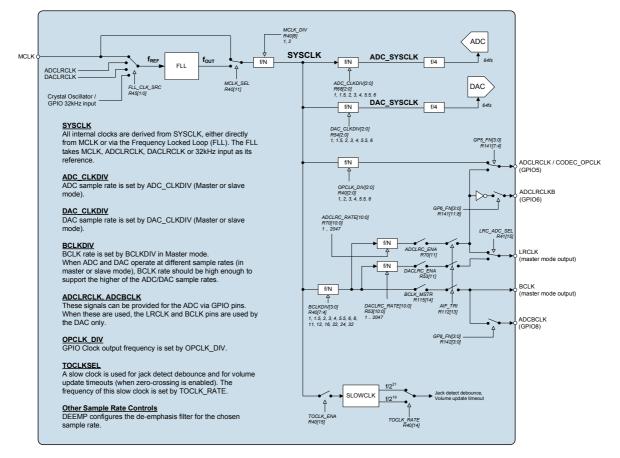

The master clock for the audio CODEC can be input directly, or may be generated internally using an integrated, low power Frequency Locked Loop (FLL).

To extend battery life, fine-grained power management enables each function in the WM8352 to be independently powered down through the control interface. The WM8352 forms part of the Wolfson AudioPlus<sup>TM</sup> series of audio and power management solutions.

## **FEATURES**

### Stereo Hi-Fi CODEC

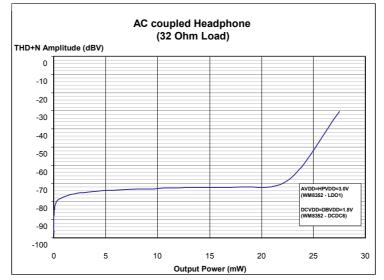

- DAC SNR 95dB ('A' weighted @ 48kHz), THD –81dB

- ADC SNR 95dB ('A' weighted @ 48kHz), THD -83dB

- 40mW on-chip headphone driver with 'capless' option

- 16Ω headphone load: THD -72dB, Po = 20mW

- 2 differential microphone inputs with low-noise bias voltage and programmable preamps

- Programmable high-pass filter for ADC

- Microphone and Headphone detection

- Auxiliary inputs for analogue signals

- Sample rates: 8, 11.025, 16, 22.05, 24, 32, 44.1 or 48kHz

### System Control

- Support for 2-wire or 3-/4-wire Control Interface

- Handles power sequencing, reset signals and fault conditions

- Autonomous power source selection (battery, wall adaptor or USB bus)

- Total current drawn from USB bus is limited to comply with USB 2.0 standard and USB OTG supplement

#### **Supply Generation**

- 2 x DC-DC Buck Converters (0.85V 3.4V, Up to 1A)

- 2 x DC-DC Buck Converters (0.85V 3.4V, Up to 500mA)

- 2 x DC-DC Boost Converters (5V 20V, 40 to 200mA)

- 4 x LDO voltage regulators (0.9V 3.3V, 150mA)

#### LED Drivers

- 2 programmable constant-current sinks, suitable for screen backlight or white LED photo flash

- 3 open-drain outputs for RGB LEDs

#### **Battery Charger**

- Single-cell Li-Ion / Li-Pol battery charger

- Thermal protection for charge control; temperature monitoring available for thermal regulation

- LED outputs to indicate charge status and fault conditions

#### Additional Features

- "Always on" RTC with wake-up alarm

- Watchdog timer

- Up to 13 configurable GPIO pins

- On-chip crystal oscillator and internal RC oscillator

- Low power FLL supporting wide range of input clocks

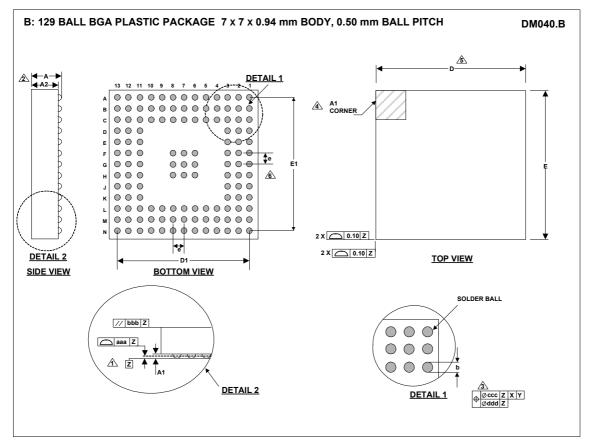

- 7x7mm, 129 BGA package, 0.5mm ball pitch

## **APPLICATIONS**

- Portable Audio and Media players

- Portable Navigation Devices

- Portable systems powered by single-cell lithium batteries

#### WOLFSON MICROELECTRONICS plc

Production Data, March 2010, Rev 4.2

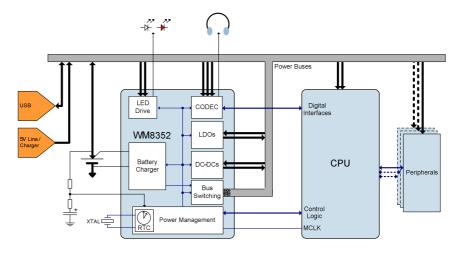

## **TYPICAL APPLICATIONS**

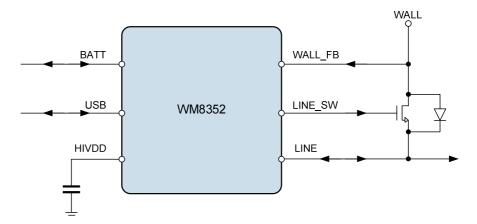

The WM8352 is a complete audio and power management solution for portable media devices. The device incorporates four programmable step-down switching regulators, two step-up switching regulators, a full-featured battery charger, four Low Drop-Out (LDO) voltage regulators which can also serve as hot-swap outputs, a backup supply regulator, two programmable white LED drivers, a Real-Time Clock (RTC) alongside a 32.768kHz (32kHz) oscillator capable of operating from a backup battery, a 12-bit auxiliary ADC for precise measurements, a ROM-programmable power management state machine and numerous protection features all in a single 7x7mm BGA package. When only battery power is available, a battery switch provides power to all switching regulators (and some other internal modules). When external power is applied (eg. from USB or Wall adapter), the WM8352 seamlessly transitions from battery power (a single-cell Lithium battery) to the applicable external supply. The battery charger is then activated, all internal power for the device is drawn from the appropriate external power source and the battery is disconnected from the load. Maximum battery charge current and charge time are programmable. The USB power manager provides accurate current limiting for the USB pin under all conditions. The hot-swap outputs (LDOs in currentlimited 'Switch Mode' operation) are ideal for powering memory cards and other devices that can be inserted while the system is fully powered.

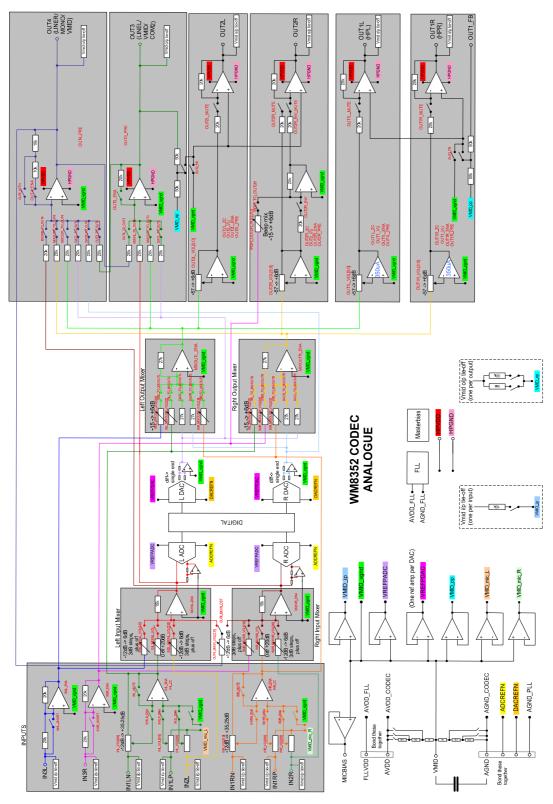

The integrated Hi-Fi stereo CODEC incorporates preamps and a low-noise bias voltage for differential microphones, and flexible pseudo-differential drivers for headphone and differential/singleended line outputs. External component requirements are reduced as no separate microphone or headphone amplifiers are required. Digital filter options are available in the ADC and DAC paths, to cater for application filtering. The WM8352 is capable of operating without any external clock, as it can derive all required clocks from its internal crystal oscillator, RC clock, and Frequency Locked Loop. An external low jitter clock may be required in some applications for high performance audio.

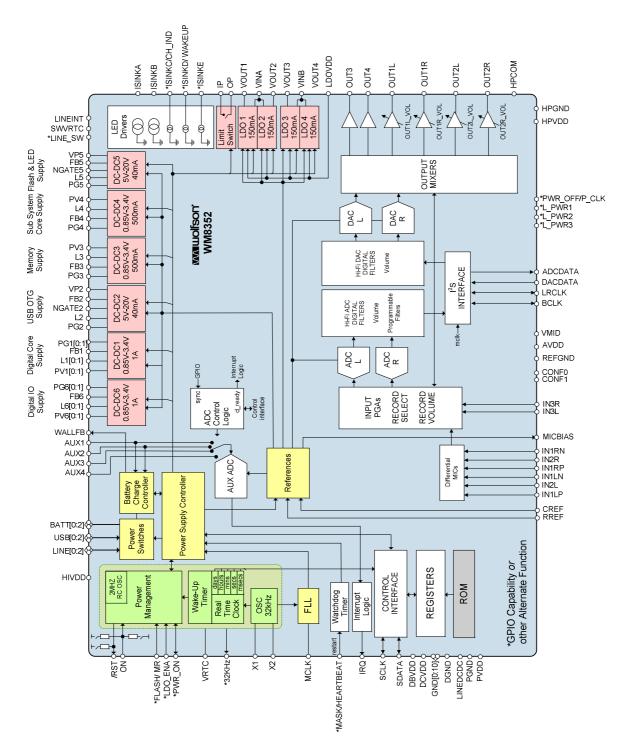

**BLOCK DIAGRAM**

## TABLE OF CONTENTS

| DESCRIPTION                                                                     | 1    |

|---------------------------------------------------------------------------------|------|

| FEATURES                                                                        |      |

| APPLICATIONS                                                                    |      |

| TYPICAL APPLICATIONS                                                            | 2    |

| BLOCK DIAGRAM                                                                   | 3    |

| TABLE OF CONTENTS                                                               | 4    |

| 1 PIN CONFIGURATION                                                             |      |

| 2 ORDERING INFORMATION                                                          |      |

| 3 PIN DESCRIPTION                                                               |      |

| 4 THERMAL CHARACTERISTICS                                                       |      |

| 5 ABSOLUTE MAXIMUM RATINGS                                                      |      |

| 6 RECOMMENDED OPERATING CONDITIONS                                              |      |

| 7 ELECTRICAL CHARACTERISTICS                                                    |      |

| 7.1 HI-FI AUDIO CODEC                                                           |      |

| 7.2 DC-DC STEP UP CONVERTER ELECTRICAL CHARACTERISTICS                          |      |

| 7.3 DC-DC STEP DOWN CONVERTER ELECTRICAL CHARACTERISTICS                        | -    |

| 7.4 LDO REGULATOR ELECTRICAL CHARACTERISTICS                                    | . 21 |

| 7.5 BATTERY CHARGER                                                             |      |

| 7.6 CURRENT LIMIT SWITCH                                                        |      |

| 7.7 LED DRIVERS                                                                 |      |

| 7.8 GENERAL PURPOSE INPUTS / OUTPUTS (GPIO)                                     |      |

| 7.9 DIGITAL INTERFACES                                                          |      |

| 7.10 AUXILIARY ADC                                                              |      |

| 8 TYPICAL POWER CONSUMPTION                                                     |      |

| 9 TYPICAL PERFORMANCE DATA                                                      |      |

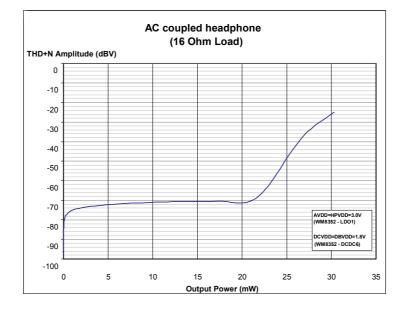

| 9.1 AUDIO CODEC                                                                 |      |

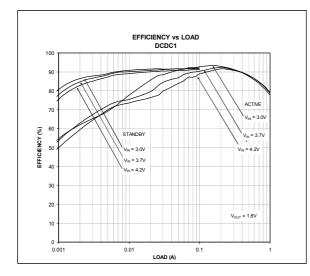

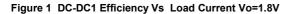

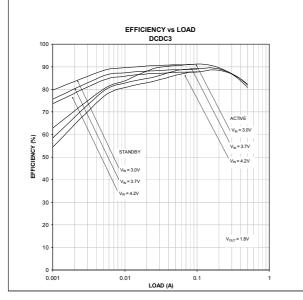

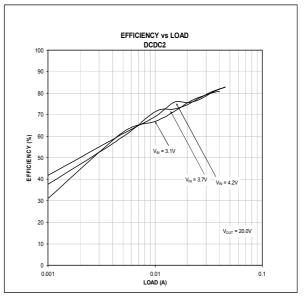

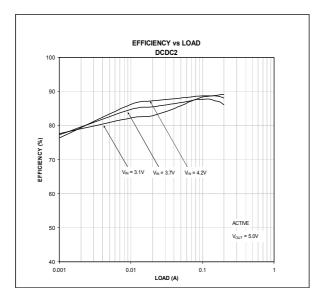

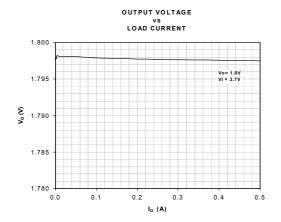

| 9.2 DC-DC CONVERTERS.                                                           |      |

| 9.2.1 POWER EFFICIENCY                                                          |      |

| 9.2.3 DYNAMIC OUTPUT VOLTAGE                                                    |      |

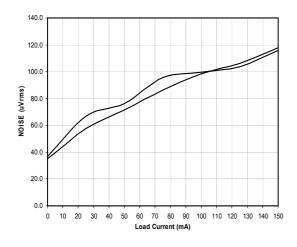

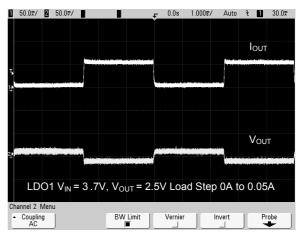

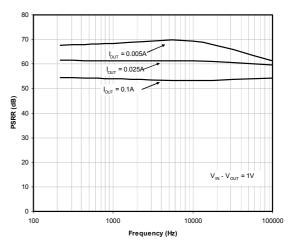

| 9.3 LDO REGULATORS                                                              |      |

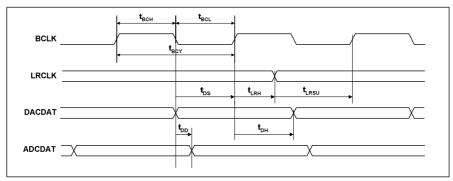

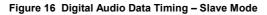

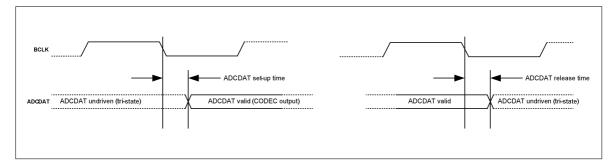

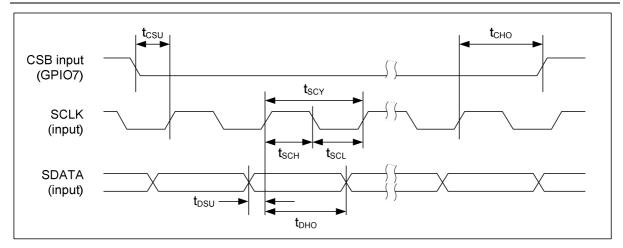

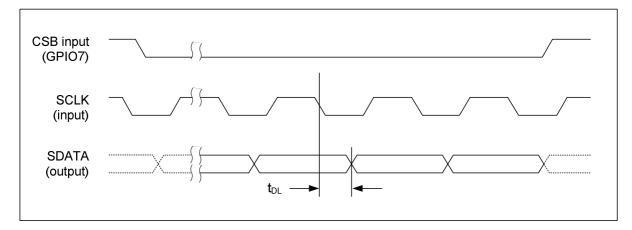

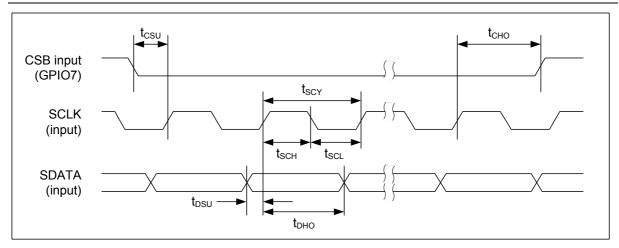

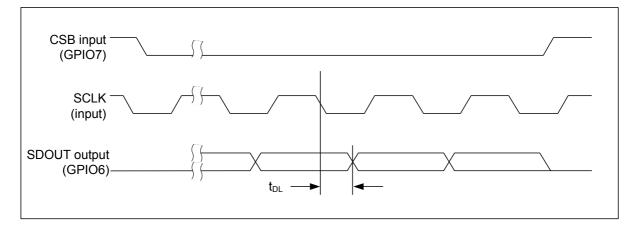

| 10 SIGNAL TIMING REQUIREMENTS                                                   | .32  |

| 10.1 SYSTEM CLOCK TIMING                                                        | . 32 |

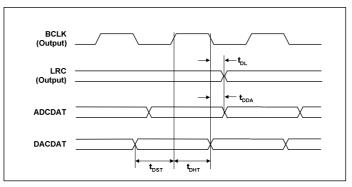

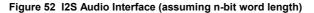

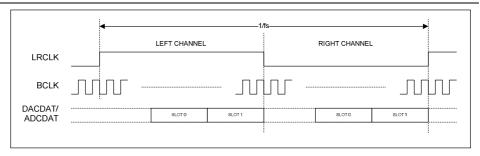

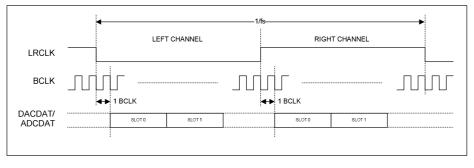

| 10.2 AUDIO INTERFACE TIMING - MASTER MODE                                       |      |

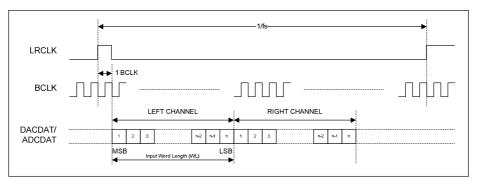

| 10.3 AUDIO INTERFACE TIMING - SLAVE MODE                                        |      |

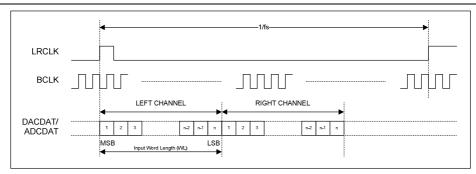

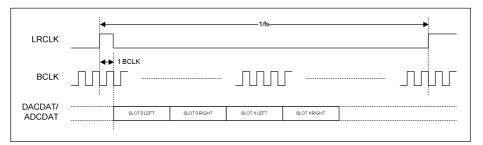

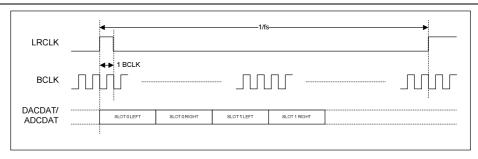

| 10.4 AUDIO INTERFACE TIMING - TDM MODE                                          |      |

| 10.5 CONTROL INTERFACE TIMING                                                   |      |

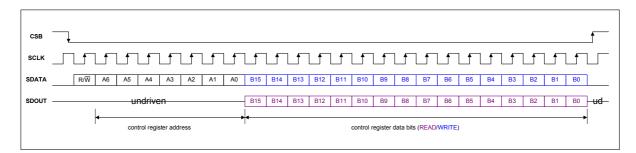

| 11 CONTROL INTERFACE                                                            |      |

| 11.1 GENERAL DESCRIPTION                                                        |      |

| 11.2 CONTROL INTERFACE MODES                                                    |      |

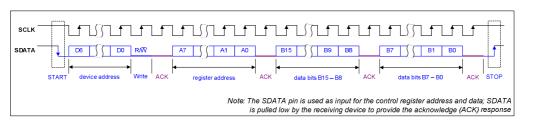

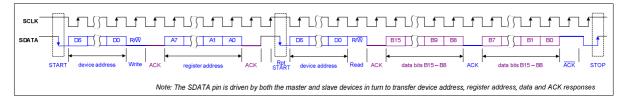

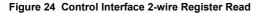

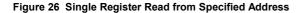

| 11.3 2-WIRE SERIAL CONTROL MODE                                                 |      |

| 11.4 3-WIRE SERIAL CONTROL MODE                                                 |      |

| <ul><li>11.5 4-WIRE SERIAL CONTROL MODE</li><li>11.6 REGISTER LOCKING</li></ul> |      |

| 11.7 SPECIAL REGISTERS                                                          |      |

| 11.7 SPECIAL REGISTERS                                                          |      |

| 11.7.2 DEVICE INFORMATION                                                       |      |

| 12 CLOCKING, TIMING AND SAMPLE RATES                                            | .45  |

| ,                                                                               | -    |

| Production Dat | a                                       | WM |

|----------------|-----------------------------------------|----|

| 12.1 (         | GENERAL DESCRIPTION                     |    |

| 12.1.1         | CLOCKING THE AUDIO CODEC                |    |

| 12.1.2         |                                         |    |

| 12.1.3         |                                         |    |

| 12.2 (         | CRYSTAL OSCILLATOR                      |    |

| 12.3 (         | CLOCKING AND SAMPLE RATES               |    |

| 12.3.1         | SYSCLK CONTROL                          |    |

| 12.3.2         |                                         |    |

| 12.3.3         |                                         |    |

| 12.3.4         |                                         |    |

| 12.3.5         |                                         |    |

| 12.3.6         |                                         |    |

|                |                                         |    |

| 12.4.1         |                                         |    |

| 12.4.2         |                                         |    |

|                | IO CODEC SUBSYSTEM                      |    |

|                | GENERAL DESCRIPTION                     |    |

|                |                                         |    |

|                | AUDIO PATHS<br>ENABLING THE AUDIO CODEC |    |

|                |                                         |    |

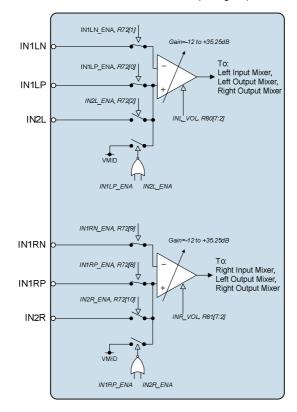

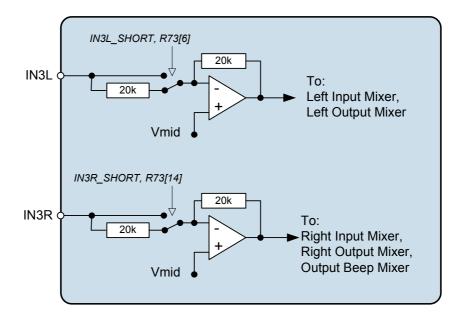

|                | NPUT SIGNAL PATH                        |    |

| 13.4.1         |                                         |    |

| 13.4.2         |                                         |    |

| 13.4.3         |                                         |    |

| 13.4.4         | CONTROLLING THE PRE-AMPLIFIER GAINS     |    |

| 13.4.5         |                                         |    |

| 13.4.6         |                                         |    |

| 13.4.7         |                                         |    |

| 13.5 A         | ANALOGUE TO DIGITAL CONVERTER (ADC)     | 71 |

| 13.5.1         | ADC VOLUME CONTROL                      | 72 |

| 13.5.2         | ADC HIGH-PASS FILTER                    | 72 |

| 13.6 E         | DIGITAL MIXING                          | 73 |

| 13.6.1         | DIGITAL SIDETONE                        | 73 |

| 13.7 E         | DIGITAL TO ANALOGUE CONVERTER (DAC)     | 75 |

| 13.7.1         |                                         |    |

| 13.7.2         | DAC SOFT MUTE AND SOFT UN-MUTE          |    |

| 13.7.3         | DAC DE-EMPHASIS                         | 77 |

| 13.7.4         | DAC OUTPUT PHASE AND MONO MIXING        |    |

| 13.7.5         | DAC STOPBAND ATTENUATION                |    |

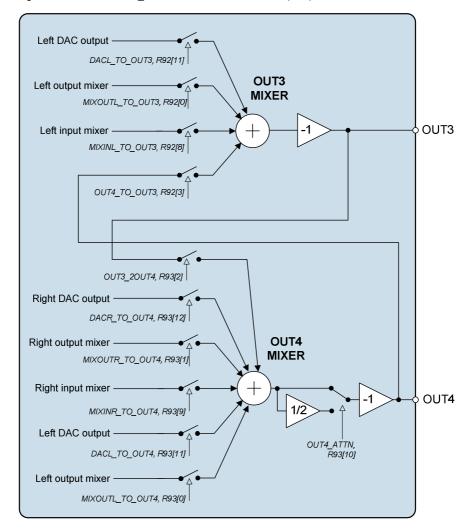

| 13.8 0         | OUTPUT SIGNAL PATH                      | 79 |

| 13.8.1         | ENABLING THE ANALOGUE OUTPUTS           | 79 |

| 13.8.2         |                                         |    |

|                | ANALOGUE OUTPUTS                        |    |

| 13.9.1         |                                         |    |

| 13.9.2         |                                         |    |

| 13.9.3         |                                         |    |

| 13.9.4         |                                         |    |

|                |                                         |    |

| 13.10.         |                                         |    |

| 13.10.         |                                         |    |

| 13.10.         |                                         |    |

| 13.10.         |                                         |    |

|                | 2007BACK                                |    |

|                | ADDITIONAL CODEC FUNCTIONS              |    |

|                |                                         |    |

| 13.12.         | 1 HEADPHONE JACK DETECT                 |    |

| WM8352            |                                                                            | Productio |

|-------------------|----------------------------------------------------------------------------|-----------|

| 13.12.2           | MICROPHONE DETECTION                                                       |           |

| 13.12.3           | MID-RAIL REFERENCE (VMID)                                                  |           |

| 13.12.4           | ANTI-POP CONTROL                                                           |           |

| 13.12.5           | UNUSED ANALOGUE INPUTS/OUTPUTS                                             |           |

| 13.12.6           | ZERO CROSS TIMEOUT                                                         |           |

| 13.12.7           | INTERRUPTS AND FAULT PROTECTION                                            |           |

| 14 POWE           | R MANAGEMENT SUBSYSTEM                                                     | 106       |

|                   | NERAL DESCRIPTION                                                          |           |

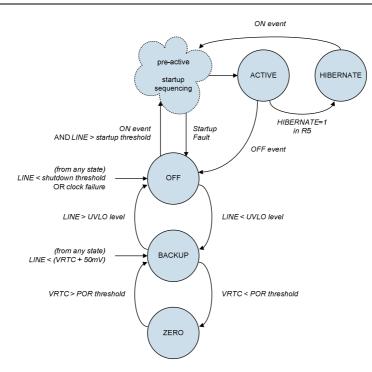

| 14.2 PO           | WER MANAGEMENT OPERATING STATES                                            |           |

| 14.2.1            | HIBERNATE STATE SELECTION                                                  |           |

| 14.3 PO           | WER SEQUENCING AND CONTROL                                                 |           |

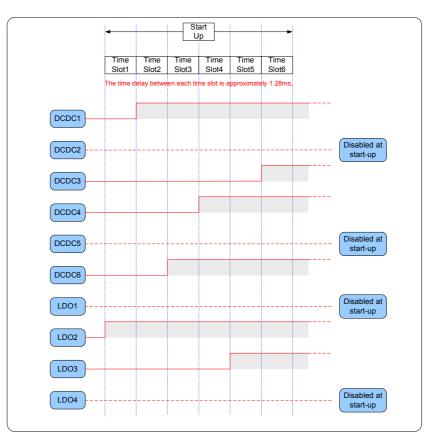

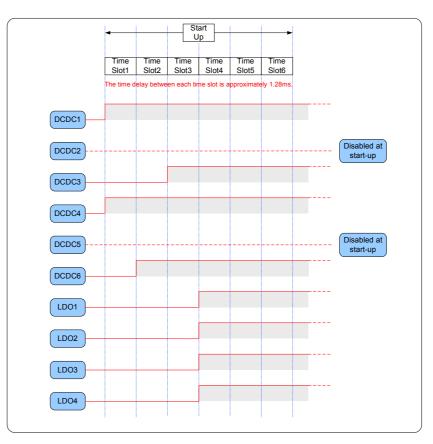

| 14.3.1            | STARTUP                                                                    |           |

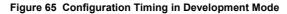

| 14.3.2            | POWER-UP SEQUENCING                                                        |           |

| 14.3.3            | SHUTDOWN                                                                   |           |

| 14.3.4            | POWER CYCLING                                                              |           |

| 14.3.5            | REGISTER RESET                                                             |           |

| 14.3.6            | RESET SIGNALS                                                              |           |

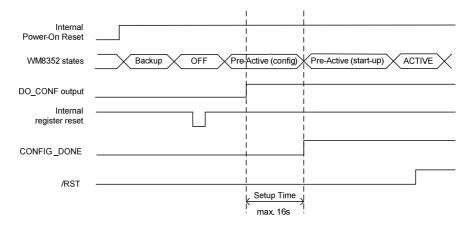

| 14.4 DE           | VELOPMENT MODE                                                             |           |

| 14.4.1            | CONTROL INTERFACE REDIRECTION                                              |           |

| 14.4.2            | STARTING UP IN DEVELOPMENT MODE                                            |           |

| 14.4.3            | CONFIGURING THE WM8352 IN DEVELOPMENT MODE                                 |           |

|                   | STOM MODES                                                                 |           |

| 14.5.1            | CONFIGURATION MODE 01                                                      |           |

| 14.5.2            | CONFIGURATION MODE 10                                                      |           |

| 14.5.3            | CONFIGURATION MODE 11                                                      |           |

|                   | NFIGURING THE DC-DC CONVERTERS                                             |           |

| 14.6.1            | DC-DC CONVERTER ENABLE                                                     |           |

| 14.6.2            |                                                                            |           |

| 14.6.3            | DC-DC BUCK (STEP-DOWN) CONVERTER CONTROL                                   |           |

| 14.6.4            | DC-DC BOOST (STEP-UP) CONVERTER CONTROL<br>INTERRUPTS AND FAULT PROTECTION |           |

| 14.6.5<br>14.7 CO | INTERROPTS AND FAULT PROTECTION                                            |           |

|                   | LDO REGULATOR ENABLE                                                       |           |

| 14.7.1<br>14.7.2  | LDO REGULATOR ENABLE                                                       |           |

| 14.7.2            | INTERRUPTS AND FAULT PROTECTION                                            |           |

| 14.7.4            | ADDITIONAL CONTROL FOR LDO1                                                |           |

|                   | -DC CONVERTER OPERATION                                                    |           |

| 14.8.1            | OVERVIEW                                                                   |           |

| 14.8.2            | DC-DC STEP DOWN CONVERTERS                                                 |           |

| 14.8.3            | DC-DC STEP UP CONVERTERS                                                   |           |

|                   | O REGULATOR OPERATION                                                      |           |

|                   | ENT LIMIT SWITCH                                                           |           |

|                   | NERAL DESCRIPTION                                                          |           |

|                   | NFIGURING THE CURRENT LIMIT SWITCH                                         |           |

| 15.2.1            |                                                                            |           |

| 15.2.2            | CURRENT LIMIT SWITCH BULK DETECTION CONTROL                                |           |

| 15.2.3            | INTERRUPTS AND FAULT PROTECTION                                            |           |

|                   | ENT SINKS (LED DRIVERS)                                                    |           |

|                   | INERAL DESCRIPTION                                                         |           |

|                   | INSTANT-CURRENT SINKS                                                      |           |

| 16.2.1            | ENABLING THE SINK CURRENT                                                  |           |

| 16.2.2            | PROGRAMMING THE SINK CURRENT                                               |           |

| 16.2.3            | FLASH MODE                                                                 |           |

| 16.2.4            | ON/OFF RAMP TIMING                                                         |           |

| 16.2.5            | INTERRUPTS AND FAULT PROTECTION                                            |           |

| Production [      | Data                                                         | WM  |

|-------------------|--------------------------------------------------------------|-----|

| 16.3              | OPEN-DRAIN LED OUTPUTS                                       |     |

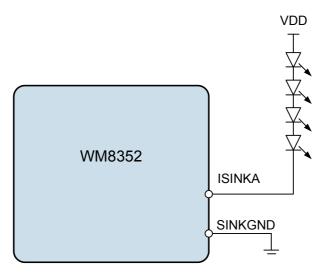

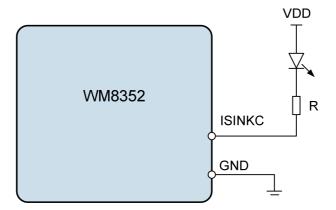

| 16.4              | LED DRIVER CONNECTIONS                                       |     |

| 17 PC             | OWER SUPPLY CONTROL                                          |     |

| 17.1              | GENERAL DESCRIPTION                                          | -   |

| 17.2              | BATTERY POWERED OPERATION                                    |     |

| 17.3              | WALL ADAPTOR (LINE) POWERED OPERATION                        |     |

| 17.4              | USB POWERED OPERATION                                        |     |

| 17.5              | EXTERNAL INTERRUPTS                                          | 156 |

| 17.6              | BACKUP POWER                                                 |     |

| 17.7              | BATTERY CHARGER                                              | 157 |

| 17.7              | .7.1 GENERAL DESCRIPTION                                     |     |

| 17.7              | .7.2 BATTERY CHARGER ENABLE                                  |     |

| 17.7              |                                                              |     |

|                   | .7.4 FAST CHARGING                                           |     |

|                   | .7.5 BATTERY CHARGER TIMEOUT AND TERMINATION                 |     |

| 17.7              | .7.6 BATTERY CHARGER STATUS<br>.7.7 BATTERY FAULT CONDITIONS |     |

| 17.7              |                                                              |     |

|                   | YSTEM MONITORING AND UNDERVOLTAGE LOCKOUT (U                 |     |

|                   |                                                              |     |

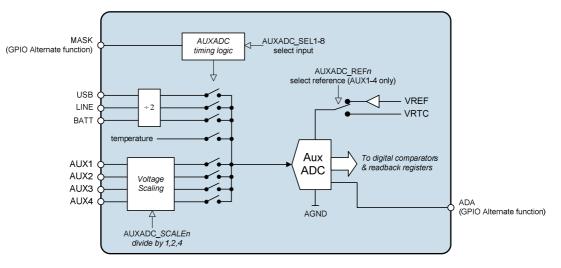

| 19 AU<br>19.1     | GENERAL DESCRIPTION                                          |     |

| 19.1              | INITIATING AUXADC MEASUREMENTS                               |     |

| 19.2              | VOLTAGE SCALING AND REFERENCES                               |     |

| 19.3              | AUXADC READBACK                                              |     |

| 19.5              | CALIBRATION                                                  |     |

| 19.6              | DIGITAL COMPARATORS                                          |     |

| 19.7              | AUXADC INTERRUPTS                                            |     |

| -                 | ENERAL PURPOSE INPUTS / OUTPUTS (GPIO)                       |     |

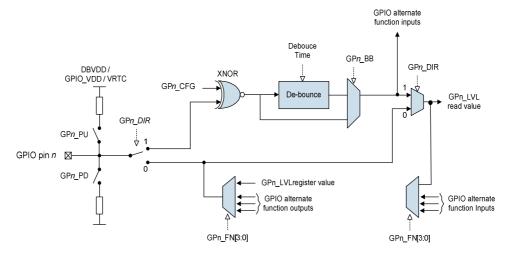

| 20.1              |                                                              |     |

| 20.1              |                                                              |     |

|                   | .1.2 INPUT DE-BOUNCE                                         |     |

| 20.1              |                                                              |     |

| 20.2              | GPIO ALTERNATE FUNCTIONS                                     |     |

| 20.2              |                                                              |     |

|                   | .2.2 SELECTING GPIO ALTERNATE FUNCTIONS                      |     |

| 21 VC             | OLTAGE REFERENCES                                            |     |

| 21.1              | - \ /                                                        |     |

| 21.2              |                                                              |     |

| 22 RE             | EAL-TIME CLOCK (RTC)                                         |     |

| 22.1              | GENERAL DESCRIPTION                                          |     |

| 22.2              |                                                              |     |

|                   | .2.1 MODES OF OPERATION                                      |     |

|                   | .2.2 RTC TIME REGISTERS                                      |     |

|                   | .2.3 SETTING THE TIME                                        |     |

|                   | .2.4 RTC ALARM REGISTERS                                     |     |

| 22.3              |                                                              |     |

| -                 | RTC GPIO OUTPUT                                              |     |

| 22.4              |                                                              |     |

|                   |                                                              |     |

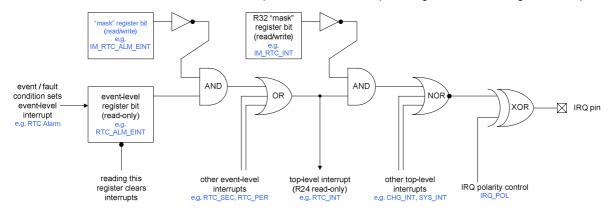

|                   | TERRUPT CONTROLLER                                           |     |

| <b>24</b> IN 24.1 | CONFIGURING THE IRQ PIN                                      |     |

| <b>۲</b> +.۱      |                                                              |     |

| 24.         |                  | ST-LEVEL INTERRUPTS                                         |     |

|-------------|------------------|-------------------------------------------------------------|-----|

| 24.         |                  | COND-LEVEL INTERRUPTS                                       |     |

|             | 24.3.1           | OVERCURRENT INTERRUPT                                       |     |

|             | 24.3.2           | UNDERVOLTAGE INTERRUPTS                                     |     |

|             | 24.3.3           | CURRENT SINK (LED DRIVER) INTERRUPTS                        |     |

|             | 24.3.4           | EXTERNAL INTERRUPTS                                         |     |

|             | 24.3.5           | CODEC INTERRUPTS                                            |     |

|             | 24.3.6           | GPIO INTERRUPTS<br>AUXADC AND DIGITAL COMPARATOR INTERRUPTS |     |

|             | 24.3.7<br>24.3.8 |                                                             |     |

|             | 24.3.8<br>24.3.9 | RTC INTERRUPTS                                              |     |

|             | 24.3.9           | CHARGER INTERRUPTS                                          |     |

|             | 24.3.10          | USB INTERRUPTS                                              |     |

|             | 24.3.12          | WAKE-UP INTERRUPTS                                          |     |

| 25          |                  |                                                             |     |

| 25.         |                  | IP TEMPERATURE MONITORING                                   |     |

| <b>2</b> 5. |                  |                                                             |     |

| 26.         |                  | ERVIEW                                                      |     |

| 20.<br>27   |                  |                                                             |     |

|             |                  |                                                             | -   |

| 28          | -                |                                                             |     |

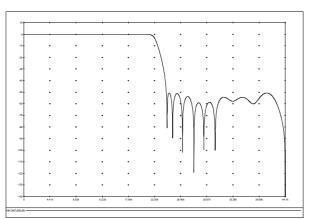

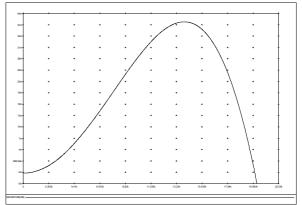

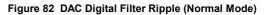

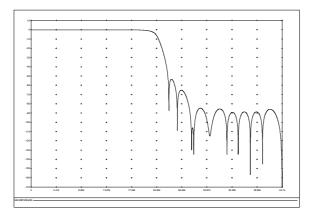

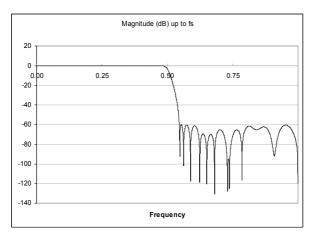

|             | 28.1.1           | DAC FILTER RESPONSES                                        |     |

| ~~          | 28.1.2           |                                                             |     |

| -           |                  |                                                             |     |

| 29.         |                  |                                                             |     |

| 29.         |                  |                                                             |     |

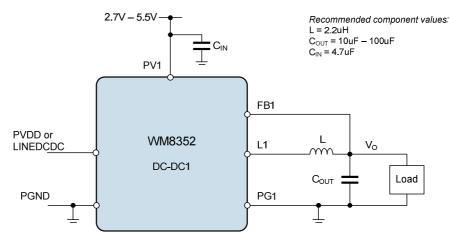

| 29.         |                  | -DC (STEP-DOWN) CONVERTER EXTERNAL COMPONENTS               |     |

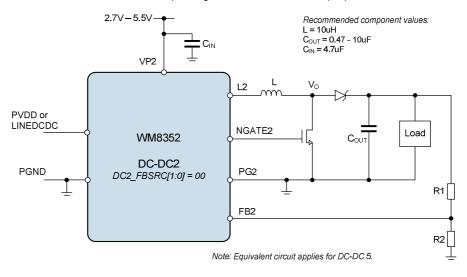

| 29.4        |                  | -DC (STEP-UP) CONVERTER EXTERNAL COMPONENTS                 |     |

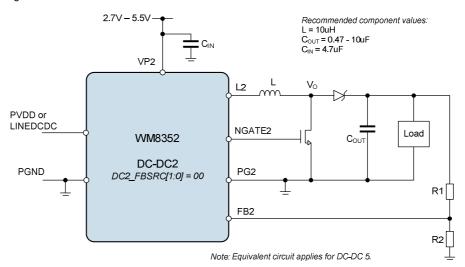

|             | 29.4.1           | DC-DC (STEP-UP) CONVERTERS - CONSTANT VOLTAGE MODE          |     |

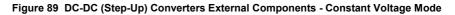

|             | 29.4.2           | DC-DC (STEP-UP) CONVERTERS - CONSTANT CURRENT MODE          |     |

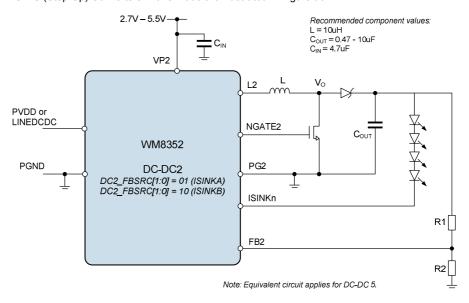

|             | 29.4.3           | DC-DC (STEP-UP) CONVERTERS - USB MODE                       |     |

|             | 29.4.4           | DC-DC (STEP-UP) CONVERTERS RECOMMENDED COMPONENTS           |     |

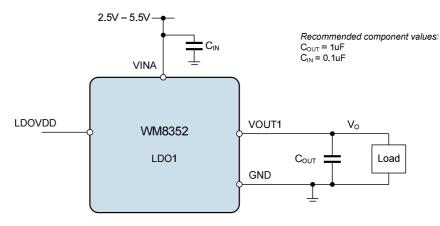

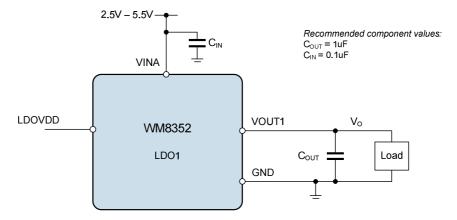

| 29.         |                  | O REGULATOR EXTERNAL COMPONENTS                             |     |

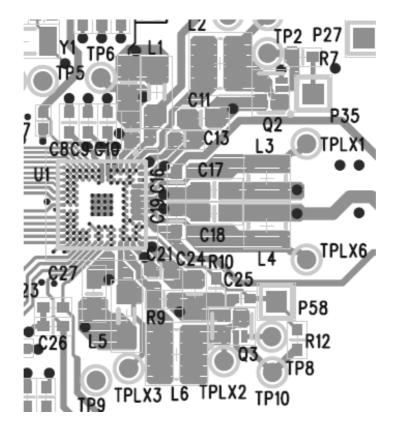

| 29.         |                  | B LAYOUT                                                    |     |

| 30          |                  |                                                             |     |

| 31          | IMPOR            |                                                             | 335 |

## **1 PIN CONFIGURATION**

|   | 1     | 2       | 3      | 4     | 5            | 6     | 7       | 8      | 9     | 10     | 11      | 12     | 13      |

|---|-------|---------|--------|-------|--------------|-------|---------|--------|-------|--------|---------|--------|---------|

| A | VP5   | PG5     | OP     | PV1   | L1           | PG1   | PG6     | L6     | PV6   | FB6    | GPIO12  | FB2    | PG2     |

| в | L5    | NGATE5  | IP     | PV1   | L1           | PG1   | PG6     | L6     | PV6   | PVDD   | GPIO10  | NGATE2 | VP2     |

| с | L4    | PG4     | FB4    | FB5   | LINEDCD<br>C | FB1   | GND     | GND    | AUX4  | GPIO11 | PGND    | PG3    | L2      |

| D | PV4   | BATT    | HIVDD  | N/A   | N/A          | N/A   | N/A     | N/A    | N/A   | N/A    | FB3     | PV3    | L3      |

| E | BATT  | BATT    | WALLFB | N/A   | N/A          | N/A   | N/A     | N/A    | N/A   | N/A    | ISINKA  | ISINKB | SINKGND |

| F | LINE  | LINE    | LINE   | N/A   | N/A          | GND   | GND     | GND    | N/A   | N/A    | VOUT4   | LDOVDD | VINB    |

| G | USB   | USB     | USB    | N/A   | N/A          | GND   | GND     | GND    | N/A   | N/A    | VOUT2   | VOUT3  | VINA    |

| н | VRTC  | LINEINT | CREF   | N/A   | N/A          | GND   | GND     | GND    | N/A   | N/A    | AUX1    | VOUT1  | AUX3    |

| J | CONF0 | X1      | RREF   | N/A   | N/A          | N/A   | N/A     | N/A    | N/A   | N/A    | OUT1R   | HPCOM  | AUX2    |

| к | CONF1 | ON      | X2     | N/A   | N/A          | N/A   | N/A     | N/A    | N/A   | N/A    | OUT1L   | OUT4   | HPVDD   |

| L | GPI00 | /RST    | SWVRTC | IRQ   | GPIO5        | GPIO8 | GPIO9   | BCLK   | LRCLK | IN3L   | IN 1LN  | OUT3   | HPGND   |

| м | GPIO2 | GPIO1   | SDA    | GPIO6 | DGND         | MCLK  | ADCDATA | AVDD   | IN3R  | INL2   | MICBIAS | OUT2R  | OUT2L   |

| N | GPIO3 | SCL     | GPIO4  | GPIO7 | DCVDD        | DBVDD | DACDATA | REFGND | VMID  | IN1LP  | INR2    | IN1RP  | IN1RN   |

#### 7mm x 7mm BGAIZ

Notes: Pin names beginning with a lower-case "n" indicate that the pin is active low. Colour coding indicates function of pins in typical usage:

DC-DC converters LDO voltage regulators Power management functions Analogue pins for audio codec Digital pins for audio codec Quiet ground Others

## 2 ORDERING INFORMATION

| ORDER CODE   | TEMPERATURE<br>RANGE | PACKAGE                                             | MOISTURE SENSITIVITY<br>LEVEL | PEAK SOLDERING<br>TEMPERATURE |

|--------------|----------------------|-----------------------------------------------------|-------------------------------|-------------------------------|

| WM8352GEB/V  | -25°C to +85°C       | 129-ball BGA (7 x 7 mm)<br>(Pb-free)                | MSL3                          | 260°C                         |

| WM8352GEB/RV | -25°C to +85°C       | 129-ball BGA (7 x 7 mm)<br>(Pb-free, tape and reel) | MSL3                          | 260°C                         |

Note:

Reel quantity = 2,200

## **3 PIN DESCRIPTION**

Notes:

Pins are listed in alphabetical order by name.

| NAME    | LOCATION(S)                                        | TYPE            | POWER<br>DOMAIN | DESCRIPTION                                                                                                 |  |  |  |

|---------|----------------------------------------------------|-----------------|-----------------|-------------------------------------------------------------------------------------------------------------|--|--|--|

| ADCDATA | M7                                                 | Digital Output  | DBVDD           | Digital audio output (typically from on-chip audio ADC to external IC)                                      |  |  |  |

| AUX1    | H11                                                | Analogue Input  | LINE            | Auxiliary ADC input AUX1                                                                                    |  |  |  |

|         |                                                    |                 |                 | (Special function for connection to temperature-sensing NTC resistor in battery pack)                       |  |  |  |

| AUX2    | J13                                                | Analogue Input  | LINE            | Auxiliary ADC input AUX2                                                                                    |  |  |  |

| AUX3    | H13                                                | Analogue Input  | LINE            | Auxiliary ADC input AUX3                                                                                    |  |  |  |

| AUX4    | C9                                                 | Analogue Input  | LINE            | Auxiliary ADC input AUX4                                                                                    |  |  |  |

| AVDD    | M8                                                 | Supply          |                 | Analogue supply for audio CODEC                                                                             |  |  |  |

| BATT    | E1, E2, D2                                         | Analogue I/O    |                 | Main battery power connection (can draw power or charge battery)                                            |  |  |  |

| BCLK    | L8                                                 | Digital I/O     | DBVDD           | Bit clock signal for digital audio interface                                                                |  |  |  |

| CREF    | H3                                                 | Analogue Output | VRTC            | Decoupling for VREF reference voltage (connect capacitor here)                                              |  |  |  |

| CONF0   | J1                                                 | Digital Input   | VRTC            | Start-up configuration pin 0                                                                                |  |  |  |

| CONF1   | K1                                                 | Digital Input   | VRTC            | Start-up configuration pin 1                                                                                |  |  |  |

| DACDATA | N7                                                 | Digital Input   | DBVDD           | Digital audio input (typically from external IC to on-chip audio DAC)                                       |  |  |  |

| DCVDD   | N5                                                 | Supply          |                 | Digital core supply; powers digital core of audio CODEC                                                     |  |  |  |

| DBVDD   | N6                                                 | Supply          |                 | Digital I/O buffer supply; powers digital audio interface, control interface and pins GPIO4 to GPIO9        |  |  |  |

| DGND    | M5                                                 | Supply          |                 | Digital ground; return path for DCVDD and DBVDD supplies                                                    |  |  |  |

| FB1     | C6                                                 | Analogue Input  | PV1             | DC-DC1 feedback pin                                                                                         |  |  |  |

| FB2     | A12                                                | Analogue Input  | VP2             | DC-DC2 feedback pin                                                                                         |  |  |  |

| FB3     | D11                                                | Analogue Input  | PV3             | DC-DC3 feedback pin                                                                                         |  |  |  |

| FB4     | C3                                                 | Analogue Input  | PV4             | DC-DC4 feedback pin                                                                                         |  |  |  |

| FB5     | C4                                                 | Analogue Input  | VP5             | DC-DC5 feedback pin                                                                                         |  |  |  |

| FB6     | A10                                                | Analogue Input  | PV6             | DC-DC6 feedback pin                                                                                         |  |  |  |

| GND     | F6, F7, F8,<br>G6,G7, G8,<br>H6, H7, H8,<br>C7, C8 | Supply          |                 | Quiet ground connection for audio CODEC.<br>Note that DC-DC Converters use a separate ground<br>connection. |  |  |  |

| GPIO0   | L1                                                 | Digital I/O     | VRTC            | General Purpose Input/Output pin 0                                                                          |  |  |  |

| GPIO1   | M2                                                 | Digital I/O     | VRTC            | General Purpose Input/Output pin 1                                                                          |  |  |  |

| GPIO2   | M1                                                 | Digital I/O     | VRTC            | General Purpose Input/Output pin 2                                                                          |  |  |  |

| GPIO3   | N1                                                 | Digital I/O     | VRTC            | General Purpose Input/Output pin 3                                                                          |  |  |  |

| GPIO4   | N3                                                 | Digital I/O     | DBVDD           | General Purpose Input/Output pin 4                                                                          |  |  |  |

| GPIO5   | L5                                                 | Digital I/O     | DBVDD           | General Purpose Input/Output pin 5                                                                          |  |  |  |

| GPIO6   | M4                                                 | Digital I/O     | DBVDD           | General Purpose Input/Output pin 6                                                                          |  |  |  |

| GPIO7   | N4                                                 | Digital I/O     | DBVDD           | General Purpose Input/Output pin 7                                                                          |  |  |  |

| GPIO8   | L6                                                 | Digital I/O     | DBVDD           | General Purpose Input/Output pin 8                                                                          |  |  |  |

| GPIO9   | L7                                                 | Digital I/O     | DBVDD           | General Purpose Input/Output pin 9                                                                          |  |  |  |

| GPIO10  | B11                                                | Digital I/O     | LINE            | General Purpose Input/Output pin 10                                                                         |  |  |  |

| GPIO11  | C10                                                | Digital I/O     | LINE            | General Purpose Input/Output pin 11                                                                         |  |  |  |

| GPIO12  | A11                                                | Digital I/O     | LINE            | General Purpose Input/ Output pin 12                                                                        |  |  |  |

| HIVDD   | D3                                                 | Analogue Output |                 | Analogue output from power management unit which determines highest supply from Line, Battery or USB.       |  |  |  |

| HPCOM   | J12                                                | Analogue Input  | HPVDD           | Headphone output amplifier noise compensation input                                                         |  |  |  |

| HPGND   | L13                                                | Supply          | HPVDD           | Headphone ground; return path for HPVDD supply                                                              |  |  |  |

### Production Data

| NAME       | LOCATION(S) | TYPE                         | POWER<br>DOMAIN | DESCRIPTION                                                                                 |

|------------|-------------|------------------------------|-----------------|---------------------------------------------------------------------------------------------|

| HPVDD      | K13         | Supply                       |                 | Headphone supply – powers the analogue outputs<br>OUT1L, OUT1R, OUT2L, OUT2R, OUT3 and OUT4 |

| IN1LN      | L11         | Analogue Input               | AVDD            | Inverting input for left microphone channel                                                 |

| IN1LP      | N10         | Analogue Input               | AVDD            | Non-inverting input 1 for left microphone channel                                           |

| IN1RN      | N13         | Analogue Input               | AVDD            | Inverting input for right microphone channel                                                |

| IN1RP      | N12         | Analogue Input               | AVDD            | Non-inverting input 1 for right microphone channel                                          |

| IN2L       | M10         | Analogue Input               | AVDD            | Non-inverting input 2 for left microphone channel                                           |

| IN2R       | N11         | Analogue Input               | AVDD            | Non-inverting input 2 for right microphone channel                                          |

| IN3L       | L10         | Analogue Input               | AVDD            | Auxiliary input for analogue audio signals (left channel)                                   |

| IN3R       | M9          | Analogue Input               | AVDD            | Auxiliary input for analogue audio signals (right channel)                                  |

| IP         | B3          | Analogue Input               |                 | Power input to current limit switch                                                         |

| IRQ        | L4          | Digital Output<br>open-drain | DBVDD           | Interrupt signal from WM8352 to host processor                                              |

| ISINKA     | E11         | Analogue Output              | LDOVDD          | Constant-current LED driver A                                                               |

| ISINKB     | E12         | Analogue Output              | LDOVDD          | Constant-current LED driver B                                                               |

| L1         | A5, B5      | Analogue I/O                 | PV1             | DC-DC1 inductor connection                                                                  |

| L2         | C13         | Analogue I/O                 | VP2             | DC-DC2 inductor connection                                                                  |

| L3         | D13         | Analogue I/O                 | PV3             | DC-DC3 inductor connection                                                                  |

| L4         | C1          | Analogue I/O                 | PV4             | DC-DC4 inductor connection                                                                  |

| L5         | B1          | Analogue I/O                 | VP5             | DC-DC5 inductor connection                                                                  |

| L6         | A8, B8      | Analogue I/O                 | PV6             | DC-DC6 inductor connection                                                                  |

| LDOVDD     | F12         | Supply                       | -               | LDO amplifier supply voltage                                                                |

| LINEDCDC   | C5          | Supply                       |                 | Supply connection for DC-DC 1, 4 and 5 control circuits                                     |

| LINEINT    | H2          | Supply                       |                 | Supply connection for Internal Reference circuits                                           |

| LINE       | F1, F2, F3  | Supply                       |                 | LINE supply connection                                                                      |

| LRCLK      | L9          | Digital I/O                  | DBVDD           | Word clock (left/right clock) signal for digital audio interface                            |

| MCLK       | M6          | Digital I/O                  | DBVDD           | Master Clock (may be generated internally or externally)                                    |

| MICBIAS    | M11         | Analogue Output              | AVDD            | Low-noise bias voltage for condenser microphones<br>(connect decoupling capacitor here)     |

| NGATE2     | B12         | Analogue Output              | VP2             | DC-DC2 connection to gate of external power FET                                             |

| NGATE5     | B2          | Analogue Output              | VP5             | DC-DC5 connection to gate of external power FET                                             |

| ON         | K2          | Digital Input                | VRTC            | Connection for power-on switch                                                              |

| OP         | A3          | Analogue Output              |                 | Power output from current limit switch                                                      |

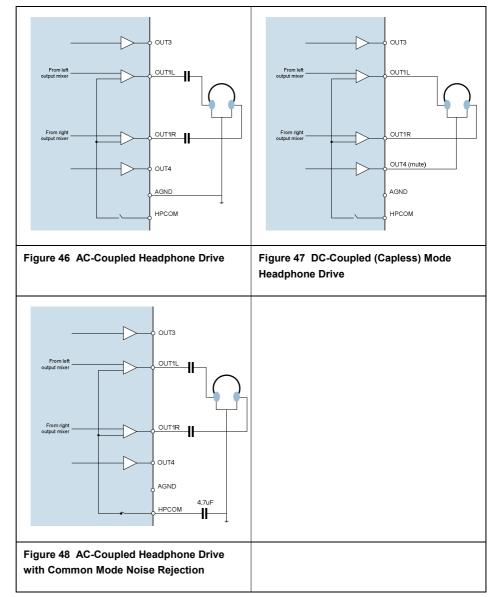

| OUT1L      | K11         | Analogue Output              | AVDD            | Left channel analogue audio output 1                                                        |

| OUT2L      | M13         | Analogue Output              | AVDD            | Left channel analogue audio output 2                                                        |

| OUT1R      | J11         | Analogue Output              | AVDD            | Right channel analogue audio output 1                                                       |

| OUT2R      | M12         | Analogue Output              | AVDD            | Right channel analogue audio output 2                                                       |

| OUT3       | L12         | Analogue Output              | AVDD            | Analogue audio output 3 (or pseudo-ground output for capacitor-less headphone outputs)      |

| OUT4       | K12         | Analogue Output              | AVDD            | Analogue audio output 4                                                                     |

| PG1        | A6, B6      | Supply                       |                 | DC-DC1 power ground                                                                         |

| PG2        | A13         | Supply                       |                 | DC-DC2 power ground                                                                         |

| PG3        | C12         | Supply                       |                 | DC-DC3 power ground                                                                         |

| PG4        | C2          | Supply                       |                 | DC-DC4 power ground                                                                         |

| PG5        | A2          | Supply                       |                 | DC-DC5 power ground                                                                         |

| PG6        | A7, B7      | Supply                       |                 | DC-DC6 power ground                                                                         |

| PGND       | C11         | Supply                       |                 | Ground connection                                                                           |

| PV1        | A4, B4,     | Supply                       |                 | DC-DC1 line or battery power input                                                          |

| PV3        | D12         | Supply                       |                 | DC-DC3 line or battery power input                                                          |

|            | D1          | Supply                       |                 | DC-DC4 line or battery power input                                                          |

| PV4        |             |                              |                 |                                                                                             |

| PV4<br>PV6 | A9, B9      | Supply                       |                 | DC-DC6 power input                                                                          |

Production Data

| NAME    | LOCATION(S) | TYPE                         | POWER<br>DOMAIN | DESCRIPTION                                                                                                                    |  |

|---------|-------------|------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| REFGND  | N8          | Supply                       |                 | Reference ground for audio ADC and DAC                                                                                         |  |

| RREF    | J3          | Analogue Output              |                 | Connection for external 100kΩ current reference resistor                                                                       |  |

| /RST    | L2          | Digital Output<br>open-drain | DBVDD           | System Reset Signal (active low)                                                                                               |  |

| SCLK    | N2          | Digital Input                | DBVDD           | Clock signal for 2-wire serial control interface (5V Tolerant)                                                                 |  |

| SDATA   | M3          | Digital I/O                  | DBVDD           | Data line for 2-wire serial control interface (5V Tolerant)                                                                    |  |

| SINKGND | E13         | Supply                       |                 | Ground connection for ISINKA and ISINKB                                                                                        |  |

| SWVRTC  | L3          | Analogue Output              | VRTC            | Switchable VRTC output. Typically used for battery temperature monitoring                                                      |  |

| USB     | G1, G2, G3  | Supply                       |                 | Connection to USB power rail                                                                                                   |  |

| VINA    | G13         | Supply                       |                 | Input to voltage regulators LDO1 and LDO2                                                                                      |  |

| VINB    | F13         | Supply                       |                 | Input to voltage regulators LDO3 and LDO4                                                                                      |  |

| VMID    | N9          | Analogue I/O                 | AVDD            | Reference voltage (normally AVDD/2) for audio CODEC (connect capacitor here)                                                   |  |

| VOUT1   | H12         | Analogue Output              | VINA            | Output of voltage regulator LDO1                                                                                               |  |

| VOUT2   | G11         | Analogue Output              | VINA            | Output of voltage regulator LDO2                                                                                               |  |

| VOUT3   | G12         | Analogue Output              | VINB            | Output of voltage regulator LDO3                                                                                               |  |

| VOUT4   | F11         | Analogue Output              | VINB            | Output of voltage regulator LDO4                                                                                               |  |

| VP2     | B13         | Supply                       |                 | DC-DC2 power input                                                                                                             |  |

| VP5     | A1          | Supply                       |                 | DC-DC5 power input                                                                                                             |  |

| VRTC    | H1          | Supply                       |                 | Backup power connection (WM8352 can draw power from this pin or re-charge the backup power source)                             |  |

| WALLFB  | E3          | Analogue Input               | LINE            | Connection to Wall feedback                                                                                                    |  |

| X1      | J2          | Analogue Input               | VRTC            | Connection for 32.768kHz crystal (input to oscillator fror crystal) or 32.768kHz external clock input (when not using crystal) |  |

| X2      | КЗ          | Analogue Output              | VRTC            | Connection for 32.768kHz crystal (output from oscillator to crystal)                                                           |  |

## 4 THERMAL CHARACTERISTICS

Thermal analysis must be performed in the intended application to prevent the WM8352 from exceeding maximum junction temperature. Several contributing factors affect thermal performance most notably the physical properties of the mechanical enclosure, location of the device on the PCB in relation to surrounding components and the number of PCB layers. Connecting the nine central GND balls through thermal vias and into a large ground plane will aid heat extraction.

Three main heat transfer paths exist to surrounding air:

- Package top to air (radiation).

- Package bottom to PCB (radiation).

- Package leads to PCB (conduction).

The temperature rise  $T_R$  is given by  $T_R = P_D * \Theta_{JA}$

- P<sub>D</sub> is the power dissipated by the device.

- $\Theta_{JA}$  is the thermal resistance from the junction of the die to the ambient temperature and is therefore a measure of heat transfer from the die to surrounding air.

- For WM8352, Θ<sub>JA</sub> = 32°C/W

The junction temperature  $T_J$  is given by  $T_J = T_A + T_R$

T<sub>A</sub>, is the ambient temperature.

The worst case conditions are when the WM8352 is operating in a high ambient temperature, with low supply voltage, high duty cycle and high output current. Under such conditions, it is possible that the heat dissipated could exceed the maximum junction temperature of the device. Care must be taken to avoid this situation. An example calculation of the junction temperature is given below.

- P<sub>D</sub> = 1W (example figure)

- Θ<sub>JA</sub> = 32°C/W

- $T_R = P_D * \Theta_{JA} = 32^{\circ}C$

- T<sub>A</sub> = 85°C (example figure)

- $T_J = T_A + T_R = 117^{\circ}C$

The minimum and maximum operating junction temperatures for the WM8352 are quoted in Section 5. The maximum junction temperature is 125°C. Therefore, the junction temperature in the above example is within the operating limits of the WM8352.

## 5 ABSOLUTE MAXIMUM RATINGS

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical Characteristics at the test conditions specified.

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage of this device.

Wolfson tests its package types according to IPC/JEDEC J-STD-020B for Moisture Sensitivity to determine acceptable storage conditions prior to surface mount assembly. These levels are:

MSL1 = unlimited floor life at <30°C / 85% Relative Humidity. Not normally stored in moisture barrier bag.

MSL2 = out of bag storage for 1 year at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

MSL3 = out of bag storage for 168 hours at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

The WM8352 has been classified as MSL3.

| CONDITION                                                  | MIN        | МАХ          |

|------------------------------------------------------------|------------|--------------|

| BATT, LINE and USB voltage                                 | -0.3V      | +7V          |

| Input voltage for LDO regulators (pins VINA, VINB)         | -0.3V      | +7V          |

| Analogue supply voltages (AVDD, HPVDD)                     | -0.3V      | +4.5V        |

| Digital supply voltages (DCVDD, DBVDD)                     | -0.3V      | +4.5V        |

| Voltage range for CODEC analogue inputs                    | -0.3V      | AVDD + 0.3V  |

| Voltage range for digital inputs                           | -0.3V      | DBVDD + 0.3V |

| Master Clock Frequency                                     |            | 37MHz        |

| (When MCLK_DIV set to divide by 2)                         |            |              |

| Operating Temperature Range, T <sub>A</sub>                | -25°C      | +85°C        |

| Junction Temperature, T <sub>J</sub>                       | -20°C      | +125°C       |

| Thermal Impedance Junction to Ambient, $\theta_{JA}$       |            | 32°C/W       |

| Storage temperature prior to soldering                     | 30°C max / | 60% RH max   |

| Storage temperature after soldering                        | -65°C      | +150°C       |

| Soldering temperature (10 seconds)                         |            | +260°C       |

| Note: These ratings assume that all ground pins are at 0V. | •          | -            |

## 6 RECOMMENDED OPERATING CONDITIONS

| PARAMETER                     | SYMBOL                                                             | MIN  | ТҮР | MAX  | UNITS |

|-------------------------------|--------------------------------------------------------------------|------|-----|------|-------|

| Digital Supply Range (Core)   | DCVDD                                                              | 1.71 |     | 3.6  | V     |

| Digital Supply Range (Buffer) | DBVDD                                                              | 1.71 |     | 3.6  | V     |

| Headphone Supply Range        | HPVDD                                                              | 2.5  |     | 3.6  | V     |

| Analogue Supply Range         | AVDD                                                               | 2.5  |     | 3.6  | V     |

| Line Input Source             | LINE                                                               | 2.95 |     | 5.5  | V     |

| Battery Input Source          | BATT                                                               | 2.95 |     | 4.2  | V     |

| USB Input Source              | USB                                                                | 4.75 |     | 5.25 | V     |

| LDO Input Source              | VINA, VINB                                                         | 0    |     | 5.5  | V     |

| Ground                        | GND, PGND, DGND, HPGND,<br>REFGND, PG1, PG2, PG3,<br>PG4, PG5, PG6 |      | 0   |      | V     |

## 7 ELECTRICAL CHARACTERISTICS

## 7.1 HI-FI AUDIO CODEC

## **Test Conditions**

DCVDD = 1.8V, AVDD = HPVDD = 3.3V,  $T_A$  = +25°C, 1kHz signal, fs = 48kHz, 24-bit audio data unless otherwise stated.

| PARAMETER                           | SYMBOL                | TEST CONDITIONS                     | MIN         | TYP       | MAX   | UNIT  |

|-------------------------------------|-----------------------|-------------------------------------|-------------|-----------|-------|-------|

| Microphone Preamp Inputs (IN1       | LP, IN1LN, IN         | IRP, IN1RN)                         |             |           |       |       |

| Full-scale Input Signal Level       | VINFS                 |                                     |             | 1         |       | V rms |

| (0dB) – note this changes with AVDD |                       |                                     |             | 0         |       | dBV   |

| Mic preamp equivalent input noise   | At<br>35.25dB<br>gain |                                     |             | 150       |       | μV    |

| Input resistance                    | RMICIN                | Gain set to 35.25dB                 |             | 2.3       |       | kΩ    |

| Input resistance                    | RMICIN                | Gain set to 0dB                     |             | 64        |       | kΩ    |

| Input resistance                    | RMICIN                | Gain set to -12dB                   |             | 101       |       | kΩ    |

| Input Capacitance                   | CMICIN                |                                     |             | 2         |       | pF    |

| Recommended decoupling cap          | CDECOUP               |                                     |             | 0.33      |       | μF    |

| MIC Programmable Gain Amplif        | ier (PGA)             | •                                   |             |           |       |       |

| Programmable Gain                   |                       |                                     | -12         |           | 35.25 | dB    |

| Programmable Gain Step Size         |                       | Monotonic                           |             | 0.75      |       | dB    |

| Mute Attenuation                    |                       |                                     |             | -90       |       | dB    |

| Selectable Input Gain Boost (0/+    | -20dB)                |                                     |             | - I       |       |       |

| Gain Boost                          |                       |                                     | 0           |           | 20    | dB    |

| Auxiliary Analogue Inputs (IN3L,    | IN3R)                 | •                                   |             |           |       |       |

| Full-scale Input Signal Level       | VINFS                 |                                     |             | 1.0       |       | V rms |

| (0dB) – note this changes with AVDD |                       |                                     |             | 0         |       | dBV   |

| PGA gain range to summer            |                       |                                     | -12         |           | +6    | dB    |

| PGA step size to summer             |                       |                                     |             | 3         |       | dB    |

| Input Resistance                    | RAUXIN                |                                     |             | 32        |       | kΩ    |

| Input Capacitance                   | CAUXIN                |                                     |             | 10        |       | pF    |

| Analogue to Digital Converter (A    | ADC)                  |                                     |             |           |       |       |

| Signal to Noise Ratio (Note 1, 2)   |                       | A-weighted, 0dB gain                | 86          | 95        |       | dB    |

| Total Harmonic Distortion           |                       | -2dBV Input                         | -75         | -83       |       | dB    |

| (Note 4)                            |                       |                                     |             |           |       |       |

| Digital to Analogue Converter (D    | AC) to Line-          | Out (OUT1L, OUT1R with <sup>·</sup> | 10kΩ / 50pF | load)     |       |       |

| Full-scale output                   |                       | PGA gains set to 0dB                |             | HPVDD/3.3 |       | V rms |

| Signal to Noise Ratio (Note 1, 2)   | SNR                   | A-weighted                          | 90          | 95        |       | dB    |

| Total Harmonic Distortion           | THD+N                 | $R_L = 10k\Omega$                   | -75         | -81       |       | dB    |

| (Note 3)                            |                       | full-scale signal                   |             |           |       |       |

| Channel Separation (Note 4)         |                       | 1kHz signal                         |             | 89        |       | dB    |

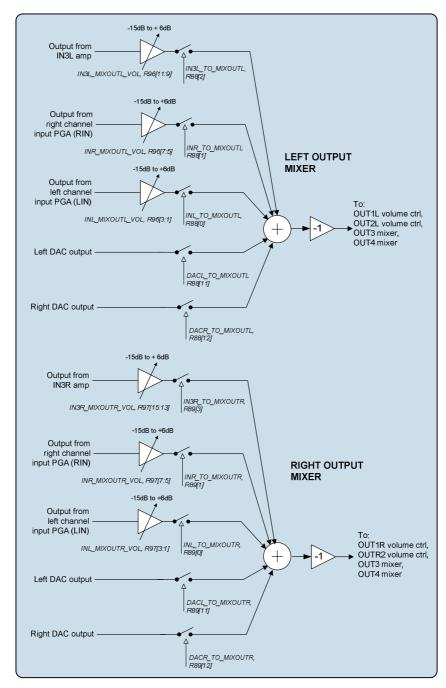

| Output Mixers                       |                       |                                     |             |           |       |       |

| PGA gain range into mixer           |                       |                                     | -15         | 0         | +6    | dB    |

| PGA gain step into mixer            |                       |                                     |             | 3         |       | dB    |

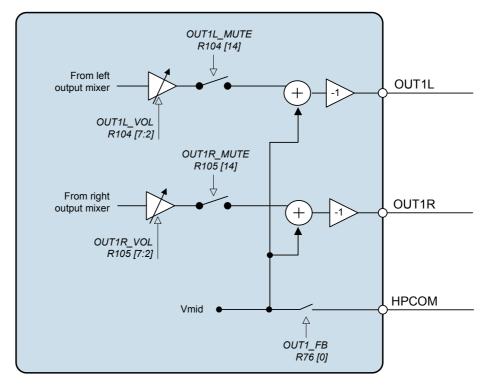

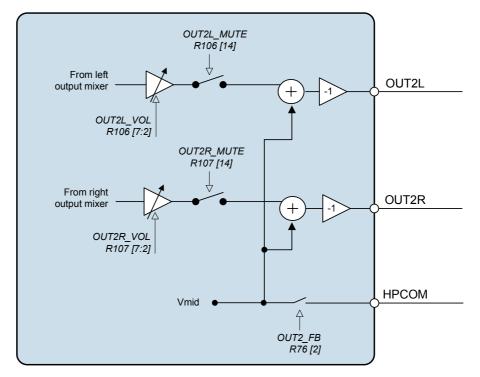

| Analogue Output PGAs (OUT1L,        | OUT1R, OUT            | 12L, OUT2R)                         |             |           |       |       |

| Programmable Gain range             |                       |                                     | -57         | 0         | +6    | dB    |

| Programmable Gain step size         |                       | Monotonic                           |             | 1         |       | dB    |

| Mute attenuation                    |                       | 1KHz, full scale<br>signal          |             | 78        |       | dB    |

Production Data

| PARAMETER                            | SYMBOL               | TEST CONDITIONS               | MIN       | TYP       | MAX       | UNIT   |

|--------------------------------------|----------------------|-------------------------------|-----------|-----------|-----------|--------|

| Headphone Output (OUT1L, OUT         | T1R, OUT2L,          | OUT2R)                        | •         | •         |           |        |

| 0dB full scale output voltage        |                      |                               |           | HPVDD/3.3 |           | Vrms   |

| Signal to Noise Ratio                | SNR                  | A-weighted                    | 87        | 96        |           | dB     |

| Total Harmonic Distortion            | THD+N                | R <sub>L</sub> = 16Ω, Po=20mW | -65       | -72       |           | dB     |

| (Note 3)                             |                      | HPVDD=3.3V                    |           |           |           |        |

|                                      |                      | R <sub>L</sub> = 32Ω, Po=20mW |           | -71       |           | dB     |

|                                      |                      | HPVDD=3.3V                    |           |           |           |        |

| OUT3/OUT4 outputs (with 10k $\Omega$ | / 50pF load)         |                               |           |           |           |        |

| Full-scale output                    |                      |                               |           | HPVDD/3.3 |           | V rms  |

| Signal to Noise Ratio (Note 1, 2)    | SNR                  | A-weighted                    | 90        | 97        |           | dB     |

| Total Harmonic Distortion            | THD                  | $R_L = 10k\Omega$             | -77       | -83       |           | dB     |

| (Note 3)                             |                      | full-scale signal             |           |           |           |        |

| Channel Separation (Note 4)          |                      | 5KHz signal                   |           | 80        |           | dB     |

| Microphone Bias                      |                      |                               |           |           |           |        |

| Bias Voltage                         | V <sub>MICBIAS</sub> | MBVSEL=0                      |           | 0.9*AVDD  |           | V      |

|                                      |                      | MBVSEL=1                      |           | 0.75*AVDD |           | V      |

| Bias Current Source                  | IMICBIAS             |                               |           | 3         |           | mA     |

| Output Noise Voltage                 | Vn                   | 1kHz to 20kHz                 |           | 24        |           | nV/√Hz |

| Digital Input / Output               |                      |                               |           |           |           |        |

| Input HIGH Level                     | VIH                  |                               | 0.7×DBVDD |           |           | V      |

| Input LOW Level                      | VIL                  |                               |           |           | 0.3×DBVDD | V      |

| Output HIGH Level                    | V <sub>OH</sub>      | I <sub>OL</sub> =1mA          | 0.9×DBVDD |           |           | V      |

| Output LOW Level                     | Vol                  | I <sub>OH</sub> -1mA          |           |           | 0.1xDBVDD | V      |

| Frequency Locked Loop (FLL)          |                      |                               |           |           |           |        |

| Reference clock frequency            | F <sub>REF</sub>     |                               | 0.032     |           | 22        | MHz    |

| Jack Detect                          |                      |                               |           |           |           |        |

| Detection switch threshold           | VIH                  |                               | 0.7xAVDD  |           |           | V      |

|                                      | VIL                  |                               |           |           | 0.3xAVDD  | V      |

| НРСОМ                                |                      |                               |           |           |           |        |

| Ground noise rejection               | VIH                  |                               |           | 40        |           | dB     |

|                                      | VIL                  |                               |           | 40        |           | dB     |

## TERMINOLOGY

- 1. Signal-to-noise ratio (dB) = SNR is a measure of the difference in level between the full scale output and the output with no signal applied. (No Auto-zero or Automute function is employed in achieving these results).

- Dynamic range (dB) = DR is a measure of the difference between the highest and lowest portions of a signal. Normally a THD+N measurement at 60dB below full scale. The measured signal is then corrected by adding the 60dB to it. (E.g. THD+N @ -60dB= -32dB, DR= 92dB).

- 3. THD+N (dB) = THD+N is a ratio, of the rms values, of (Noise + Distortion)/Signal.

- 4. Channel Separation (dB) = Also known as Cross-Talk. This is a measure of the amount one channel is isolated from the other. Normally measured by sending a full scale signal down one channel and measuring the other.

## 7.2 DC-DC STEP UP CONVERTER ELECTRICAL CHARACTERISTICS

#### **Test Conditions**

| PARAMETER                 | SYMBOL               | CONDITIONS                                                             | MIN             | TYP  | МАХ   | UNITS |

|---------------------------|----------------------|------------------------------------------------------------------------|-----------------|------|-------|-------|

| DC-DC2 and DC-D           | C5                   |                                                                        |                 |      |       |       |

| Input voltage             | V                    | when used as converter                                                 | 2.7             | 2.7  |       | V     |

| range                     | V <sub>IN</sub>      | when used as switch                                                    | 1.2             | 3.7  | 5.5   | V     |

| Output voltage            | Vout                 | by default                                                             | V <sub>IN</sub> |      | 20    | v     |

| range                     | V001                 | (needs external component configuration)                               | V IN            |      | (30)  | v     |

| USB OTG output<br>voltage | V <sub>OUT,USB</sub> | V <sub>IN</sub> <4.5V; I <sub>OUT</sub> <100mA;<br>DCn_FBSRC [1:0]=11  |                 | 5.0  |       | v     |

| Voltage                   |                      | V <sub>OUT</sub> =30V                                                  |                 |      | 25    |       |

|                           |                      | V <sub>OUT</sub> =20V                                                  |                 |      | 40    | -     |

| Output current            | lout                 | (DCn_ILIM_=1)                                                          | 0               |      | (18)  | mA    |

|                           |                      | V <sub>OUT</sub> =5.0V                                                 |                 |      | 170   |       |

|                           |                      | (DCn_ILIM_=1)                                                          |                 |      | (100) |       |

|                           |                      | V <sub>IN</sub> =3.3V; V <sub>OUT</sub> =3.2V; +25°C                   |                 | 0.26 |       | -     |

| Switch resistance         | R <sub>ON</sub>      | V <sub>IN</sub> =1.8V; V <sub>OUT</sub> =1.7V; +25°C                   |                 | 0.41 |       | Ω     |

|                           |                      | V <sub>IN</sub> =1.2V; V <sub>OUT</sub> =1.1V; +25°C                   |                 | 0.84 |       |       |

| Maximum switch<br>current | I <sub>SW,MAX</sub>  |                                                                        |                 |      | 700   | mA    |

| Switching                 | f                    |                                                                        |                 | 1.0  |       |       |

| frequency                 | f <sub>CLK</sub>     |                                                                        |                 |      |       | MHz   |

| Maximum duty<br>cycle     | D <sub>MAX</sub>     | V <sub>IN</sub> =3V; f <sub>CLK</sub> =1.0MHz                          |                 | 90   |       | %     |

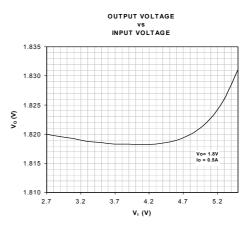

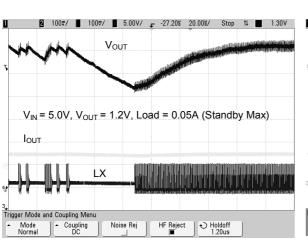

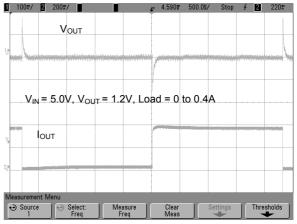

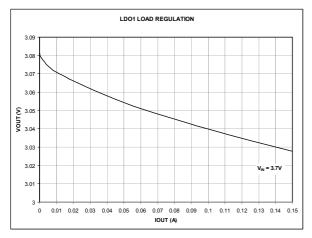

| Efficiency                |                      | V <sub>IN</sub> =3.8V; V <sub>OUT</sub> =20V; I <sub>OUT</sub> =20mA   |                 | 75   |       | 0/    |