## M5M82C51AP/FP/J

#### CMOS PROGRAMMABLE COMMUNICATION INTERFACE

#### DESCRIPTION

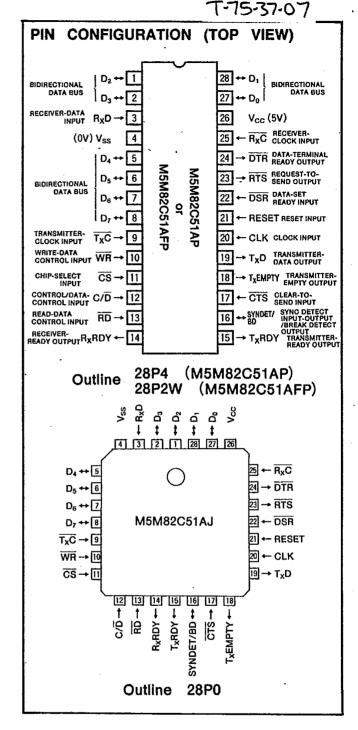

The M5M82C51AP is a universal synchronous/asynchronous receiver/transmitter (USART) IC chip designed for data communications use. It is produced using the silicon-gate CMOS process and is mainly used in combination with 8-bit microprocessors. It is housed in a 28-pin plastic molded DIP.

And preparatory for surface equipment M5M82C51AFP (SOP) and M5M82C51AJ(PLCC).

#### **FEATURES**

- Single 5V supply voltage

- TTL compatible

- Synchronous and asynchronous operation

Synchronous:

5~8-bit characters

Internal or external synchronization

**Automatic SYNC character insertion**

Asynchronous system:

5~8-bit characters

Clock rate-1, 16 or 64 times the baud rate

$1, 1\frac{1}{2}$ , or 2 stop bits

False-start-bit detection

Automatic break-state detection

- Baud rate: DC~64K-baud

- Full duplex, double-buffered transmitter/receiver

- Error detection: parity, overrun, and framing

#### **APPLICATION**

Modem control of data communications using microcomputers

Control of CRT, TTY and other terminal equipment

#### **FUNCTION**

The M5M82C51AP is used in the peripheral circuits of a CPU. It permits assignments, by means of software, of operations in all the currently used serial-data transfer systems.

The M5M82C51AP receives parallel-format data from the CPU, converts it into a serial format, and then transmits via the  $T_XD$  pin. It also receives data sent in via the  $R_XD$  pin from the external circuit, and converts it into a parallel format for sending to the CPU. On receipt of parallel-format data for transmission from the CPU or serial data for the CPU from external devices, the M5M82C51AP informs the CPU using the  $T_XRDY$  or  $R_XRDY$  pin. In addition, the CPU can read the M5M82C51AP status at any time. The M5M82C51AP can detect the data received for errors and inform the CPU of the presence of errors as status information. Errors include parity, overrun and frame errors.

#### **OPERATION**

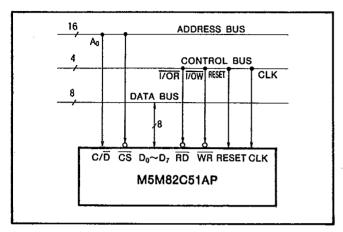

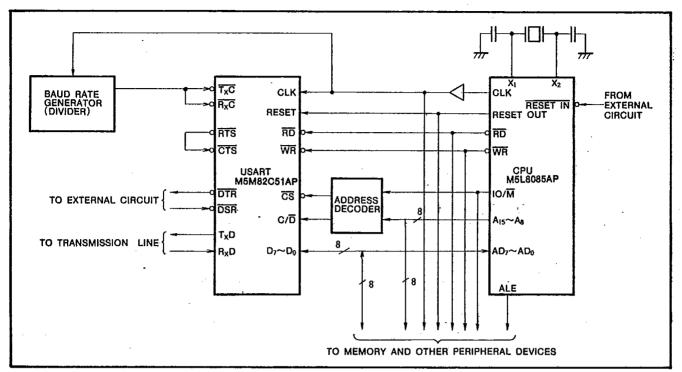

The M5M82C51AP interfaces with the system bus as shown in Fig.1, positioned between the CPU and the modem or terminal equipment, and offers all the functions required for data communication.

Fig. 1 M5M82C51AP interface to CPU system bus

When using the M5M82C51AP, it is necessary to program, as the initial setting, assignments for synchronous/asynchronous mode selection, baud rate, character length, parity check, and even/odd parity selection in accordance with the communication system used. Once programming is completed, functions appropriate to the communication system can be carried out continuously.

When initial setting of the USART is completed, data communication becomes possible. Though the receiver is always in the enable state, the transmitter is placed in the transmitter-enable state (T<sub>x</sub>EN) by a command instruction, and the application of a low-level signal to the CTS pin prompts data-transfer start-up. Until this condition is satisfied, transmission is not executed. On receiving data, the receiver informs the CPU that reading for the receiver data in the USART by the CPU has become possible (the R<sub>x</sub>RDY terminal has turned to high-level). Since data reception and the entry of the CPU into the data-readable state are output as status information, the CPU can access USART status without accessing the R<sub>x</sub>RDY terminal.

During receiving operation, the USART checks errors and gives out status information. There are three types of errors: parity, overrun, and frame. Even though an error occurs, the USART continues its operations, and the error state is retained until error reset (ER) is effected by a command instruction. The M5M82C51AP access methods are listed in Table 1.

Table 1 M5M82C51AP Access Methods

| C/D | RD | WR | CS | Function                 |

|-----|----|----|----|--------------------------|

| L   | L  | Н  | ٦  | Data bus ← Data in USART |

| L   | Н  | L  | L  | USART ← Data bus         |

| Н   | L  | Н  | L  | Data bus ← Status        |

| Н   | H  | L  | L  | Control ← Data bus       |

| Х   | Н  | Н  | L  | 3-State ← Data bus       |

| Х   | Х  | х  | Н  | 3-State ← Data bus       |

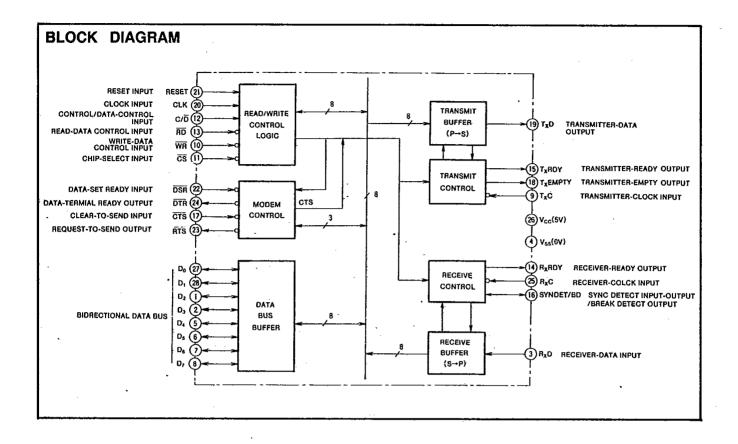

#### Read/Write Control Logic

This logic consists of a control word register and command word register. It receives signals from the CPU control bus and generates internal-control signals for the elements.

#### **Modem Control Circuit**

This is a general-purpose control-signal circuit designed to simplify the interface to the modem. Four types of control signal are available: output signals  $\overline{\text{DTR}}$  and  $\overline{\text{RTS}}$  are controlled by command instructions, input signal  $\overline{\text{DSR}}$  is given to the CPU as status information and input signal  $\overline{\text{CTS}}$  controls direct transmission.

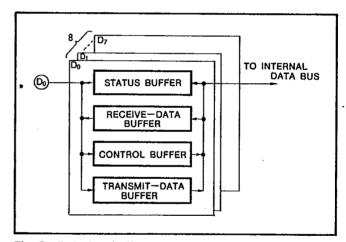

#### **Data-Bus Buffer**

This is an 8-bit 3-state bidirectional bus through which control words, command words, status information, and transfer data are transferred. Fig. 2 shows the structure of the databus buffer.

Fig. 2 Data-bus buffer structure

#### **Transmit Buffer**

This buffer converts parallel-format data given to the databus buffer in to serial data with addition of a start bit, stop bits and a parity bit, and sends out the converted data through the  $T_XD$  pin based on the control signal.

#### **Transmit-Control Circuit**

This circuit carries out all the controls required for serial data transmission. It controls transmitter data and outputs the signals required by external devices in accordance with the instructions of the read/write control logic.

## CMOS PROGRAMMABLE COMMUNICATION INTERFACE

#### **Receive Control Circuit**

This circuit offers all the controls required for normal reception of the input serial data. It controls receiver data and outputs signals for the external devices in accordace with the instructions of the read/write control logic.

#### **Receive Buffer**

This buffer converts serial data given via the R<sub>X</sub>D pin into a parallel format, checks the bits and characters in accordance with the communication format designated by mode setting, and transfers the assembled characters to the CPU via the data-bus buffer.

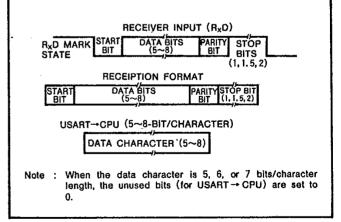

## Receiver-Data Input (R<sub>x</sub>D)

Serial characters sent from another device are input to this pln and converted to a parallel-character format to serve as data for the CPU. Unless the high-level state is detected after a chip-master reset procedure (this resetting is carried out to prevent spurious operation such as that due to faulty connection of the  $R_XD$  to the line in a break state), the serial characters are not received. This applies to only the asynchronous mode. When the  $R_XD$  line enters the low-level state instantaneously because of noise, etc, the misstart prevention function starts working. That is, the start bit is detected by its falling edge but in order to make sure that it is the correct start bit, the  $R_XD$  line is strobed at the middle of the start bit to reconfirm the low-level state. If it is found to be high-level a faulty-start judgment is made.

### Transmitter-Clock Input (T<sub>X</sub>C)

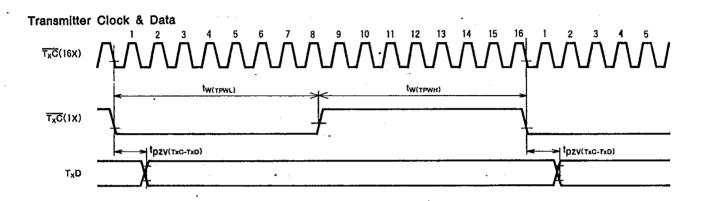

This clock controls the baud rate for character transmission from the  $T_XD$  pin. Serial data is shifted by the falling edge of the  $\overline{T_XC}$  signal. In the synchronous mode, the  $\overline{T_XC}$  frequency is equal to the actual baud rate. In the asynchronous mode, the frequency is specified as 1, 16, or 64 times the baud rate by the mode setting.

Example When the baud rate is 110 bauds:

$T_xC=110Hz(1X)$

$\overline{T_XC}=1.76kHz(16X)$

$T_xC=7.04kHz(64X)$

#### Write-Data Control Input (WR)

Data and control words output from the CPU by the low-level input are written in the M5M82C51AP. This terminal is usually used in a form connected with the control bus I/OW of the CPU.

#### Chip-Select Input (CS)

This is a device-select signal that enables the USART by a low-level input. Usually, it is connected to the address bus directly or via the decoder. When this signal is in the high-level state, the M5M82C51AP is disabled.

#### Control/Data Control Input (C/D)

This signal shows whether the information on the USART data bus is in the form of data characters or control words, or in the form of status information, in accordance with the RD and WR inputs while the CPU is accessing the M5M82C51AP. The high-level identifies control words or status information, and the low-level, data characters.

www.DataSheet4U.com

#### Read-Data Control Input (RD)

Receiver data and status information are output from the CPU by a low-level input for the CPU data bus.

#### Receiver-Ready Output (RxRDY)

This signal indicates that the received characters have entered the receiver buffer, and further, the receiver-data buffer in the data-bus buffer shown in Fig. 2. It is possible to confirm the  $R_XRDY$  status by using this signal as an interruption signal for the CPU or by allowing the CPU to read the  $D_1$  bit of the status information by polling. The  $R_XRDY$  is automatically reset when a character is read by the CPU. Even in the break state in which the  $R_XD$  line is held at low-level, the  $R_XRDY$  remains active. It can be masked by making the  $R_XE(D_2)$  of the command instruction 0.

#### Transmitter-Ready Output (TyRDY)

This signal shows that the data is ready for transmission. It is possible to confirm the status of serial-data transmission by using it as an interruption signal for the CPU or by allowing the CPU to read the  $D_0$  bit of the status information by polling. Since the  $T_xRDY$  signal shows that the data buffer is empty, it is automatically reset when a transmission character is loaded by the CPU. The  $T_xRDY$  bit of the status information means that the transmit-data buffer shown in Fig. 2 has become empty, while the  $T_xRDY$  pin enters the highlevel state only when the transmit-data buffer is empty,  $T_xEN$  equals 1, and a low-level input has been applied to the  $\overline{CTS}$  pin.

Status (D<sub>0</sub>): When transmit-data buffer (TDB) is empty, it becomes 1.

$T_xRDY$  terminal: When (TDB is empty)  $\cdot$  ( $T_xEN=1$ )  $\cdot$  (CTS="L")="H" or resetting, it becomes active.

## Sync Detect Input-Output/Break Detect Output (SYNDET/BD)

In the synchronous mode this pin is used for input and output operations. When it is specified for the internal synchronous mode by mode setting, this pin works as an output terminal. It enters the high-level state when a SYNC character is received through the R<sub>x</sub>D pin. If the M5M82C51AP has been programmed for double SYNC characters (bisync), a high-level is entered in the middle of the last bit of the second SYNC character. This signal is automatically reset by reading the status information.

On designation of the M5M82C51AP to the external synchronous mode, this pin begins to serve for input operations. Applying a high-level signal to this pin prompts the M5M82C51AP to begin assembling data characters at the next rising edge of the  $\overline{R_XC}$ . For the width of a high-level signal to be input, a minimum  $\overline{R_XC}$  period is required.

Designation of the asynchronous mode causes this pin to function as a BD (output) pin. When the start, data, and parity bits and stop bits are all 0 for two characters period, a high-level is entered. The BD (break detect) signal can also be read as the  $D_6$  bit of the status information. This signal is reset by resetting the chip master or by the  $R_{\rm X}D$  line's recovering the high-level state.

M5M82C51AP/FP/J

# MITSUBISHI(MICMPTR/MIPRC)

T-75-37-07

## CMOS PROGRAMMABLE COMMUNICATION INTERFACE

### Clear-To-Send Input (CTS)

When the  $T_XEN$  bit  $(D_0)$  of the command instruction has been set to 1 and the  $\overline{CTS}$  input is low-level serial data is sent out from the  $T_XD$  pin. Usually this is used as a clear-to-send signal for the modem.

Note: CTS indicates the modern status as follows:

ON means data transmission is possible;

OFF means data transmission is impossible.

## Transmitter-Empty Output (T<sub>X</sub>EMPTY)

When no transmisison characters are left in the transmit buffer, this pin enters the high-level state. In the asynchronous mode, the following transmission character is shifted to the transmit buffer when it is loaded from the CPU. Thus, it is automatically reset. In the synchronous mode, a SYNC character is loaded automatically on the transmit buffer when no transfer-data characters are left. In this case, however, the TxEMPTY does not enter the low-level state when a SYNC character has been sent out, since TxEMPTY = "H" denotes the state in which there is no transfer character and one or two SYNC characters are being transferred or the state in which a SYNC character is being transferred as a filler. TxEMPTY is unrelated to the TxEN bit of the command instruction.

## Transmission-Data Output (T<sub>X</sub>D)

Parallel-format transmission characters loaded on the M5M82C51AP by the CPU are assembled into the format designated by the mode instruction and sent in serial-data form via the  $T_xD$  pin. Data is output, however, only in cases where the  $D_0$  bit ( $T_xEN$ ) of the command instruction is 1 and the  $\overline{CTS}$  terminal is in the low-level state. Once reset, this pin is kept at the mark status (high-level) until the first character is sent.

#### Clock Input (CLK)

This system-clock input is required for internal-timing generation and is usually connected to the clock-output (CLK) pin of the M5L8085AP. Although there is no direct relation with the data-transfer baud rate, the clock-input (CLK) frequency is more than 30 times the  $\overline{T_XC}$  or  $\overline{R_XC}$  input frequency in the case of the synchronous system and more than 4.5 times in the case of the asynchronous system.

## Reset Input (RESET)

Once the USART is shifted to the idle mode by a high-level input, this state continues until a new control word is set. Since this is a master reset, it is always necessary to load a control word following the reset process. The reset input requires a minimum 6-clock pulse width.

## Data-Set Ready Input (DSR)

This is a general-purpose input signal, but is usually used as a data-set ready signal to test modem status. Its status can be known from the status reading process. The D<sub>7</sub> bit of the status information equals 1 when the DSR pin is in the low-level state, and 0 when in the high-level state.

DSR="L"→D<sub>7</sub> bit of status information=1

DSR="H"→D<sub>7</sub> bit of status information=0

Note: DSR indicates modern status as follows:

ON means the modem can transmit and receive; OFF means it cannot.

## Request-To-Send Output (RTS)

This is a general-purpose output signal but is used as a request-to-send signal for the modem. The  $\overline{RTS}$  terminal is controlled by the  $D_5$  bit of the command instruction. When  $D_5$  is equal to 1,  $\overline{RTS}$ ="L", and when  $D_5$  is 0,  $\overline{RTS}$ ="H".

Command register  $D_5=1\rightarrow \overline{RTS}="L"$ Command register  $D_5=0\rightarrow \overline{RTS}="H"$

Note: RTS controls the modern transmission carrier as follows:

ON means carrier dispatch;

OFF means carrier stop.

## Data-Terminal Ready Output (DTR)

This is a general-purpose output signal, but is usually used as a data-terminal ready or rate-select signal to the modern. The  $\overline{DTR}$  pin is controlled by the  $D_1$  bit of the command instruction; if  $D_1=1$ ,  $\overline{DTR}="L"$ , and if  $D_1=0$ ,  $\overline{DTR}="H"$ .

$D_1$  of the command register=1 $\rightarrow \overline{DTR}$ ="L"

D₁ of the command register=0→DTR="H"

## Receiver-Clock Input (RxC)

This clock signal controls the baud rate for the sending in of characters via the  $\overline{R}_XD$  pin. The data is shifted in by the rising edge of the  $\overline{R}_XC$  signal. In the synchronous mode, the  $\overline{R}_XC$  frequency is equal to the actual baud rate. In the asynchronous mode, the frequency is specified as 1, 16, or 64 times the baud rate by mode setting. This relationship is parallel to that of  $\overline{T}_XC$ , and in usual communication-line systems the transmission and reception baud rates are equal. The  $\overline{T}_XC$  and  $\overline{R}_XC$  terminals are, therefore, used connected to the same baud-rate generator.

## **PROGRAMMING**

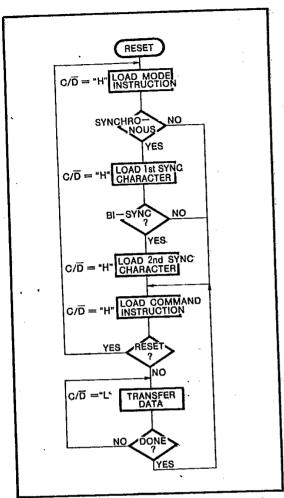

It is necessary for the M5M82C51AP to have the control word loaded by the CPU prior to data transfer. This must always be done following any resetting operation (by external RESET pin or command instruction IR). There are two types of control words: mode instructions specifying general operations required for communications and command instructions to control the M5M82C51AP actual operations. Following the resetting operation, a mode instruction must be set first. This instruction neats the second

be set first. This instruction sets the synchronous or asynchronous system to be used. In the sysnchronous system, a SYNC character is loaded from the CPU. In the case of the bi-sync system, however, a second SYNC character must be loaded in succession.

Loading a command instruction makes data transfer possible. This operation after resetting must be carried out for initializing the M5M82C51AP. The USART command instruction contains an internal-reset IR instruction ( $D_6bit$ ) that makes it possible to return the M5M82C51AP to its reset state. The initialization flowchart is shown in Fig. 3 and the mode-instruction and command-instruction formats are shown in Figs. 4 and 5.

Fig. 3 initialization flow chart

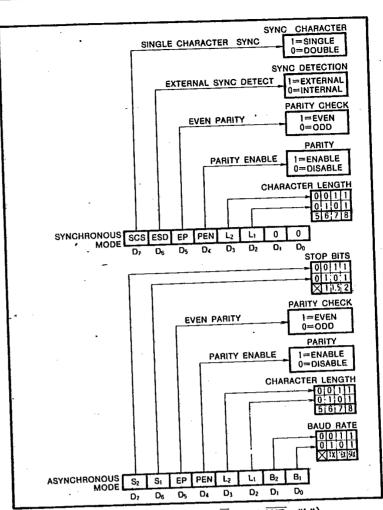

Fig. 4 Mode-instruction format  $(C/\overline{D}="H" \overline{WR}="L")$

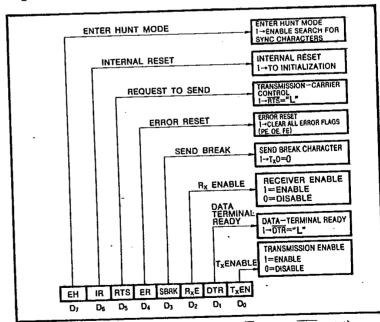

Fig. 5 Command-Instruction format (C/D="H" WR="L")

#### **Asynchronous Transmission Mode**

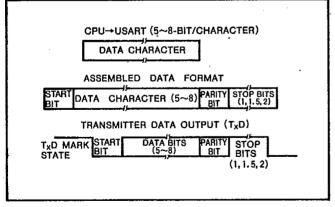

When data characters are loaded on the M5M82C51AP after initial setting, the USART automatically adds a start bit (0), an odd or even parity bit specified by the mode instruction during initialization, and a specified number of stop bits (1). After that, the assembled data characters are transferred as serial data via the  $T_xD$  pin, if transfer is enabled ( $T_xEN=1\cdot\overline{CTS}="L"$ ). In this case, the transfer data (baud rate) is shifted by the mode instruction at a rate of 1X, 1/16X, or 1/64X the  $\overline{T_xC}$  period.

If the data characters are not loaded on the M5M82C51AP, the  $T_xD$  pin enters a mark state ("H"). When SBRK is programmed by the command instruction, break characters (0) are output continuously through the  $T_xD$  pin.

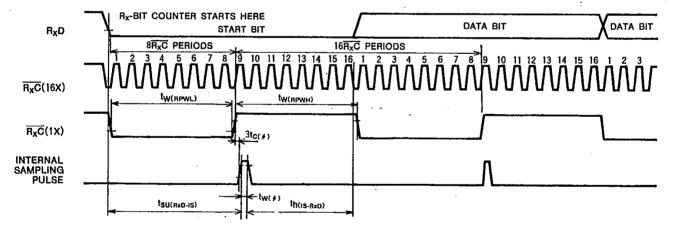

#### Asynchronous Reception Mode

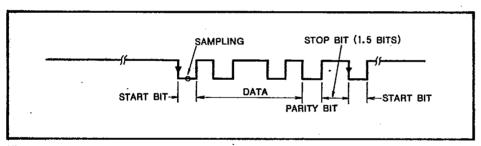

The R<sub>x</sub>D line usually starts operations in a mark state ("H"), triggered by the falling edge of a low-level pulse when it comes to this line. This signal is again strobe at the middle of the bit to confirm that it is a perfect start bit. The detection of a second low-level indicates the validity of the start bit (again strobe is carried out only in the case of 16X and 64X). After that, the bit counter inside the M5M82C51AP starts operating; each bit of the serial information on the  $R_{\rm x}D$  line is shifted in by the rising edge of  $\overline{R_{\rm x}C}$ , and the data bit, parity bit (when necessary), and stop bit are sampled at the middle position.

The occurrence of a parity error causes the setting of a parity-error flag. If the stop bit is 0, a frame error flag is set. Attention should be paid to the fact that the receiver requires only one stop bit even though the program has designated 1.5 or 2 stop bits.

Reception up to the stop bit means reception of a complete character. This character is then transferred to the receiver-data buffer shown in Fig.2, and the R<sub>x</sub>RDY becomes active. In cases where this character is not read by the CPU and where the next character is transferred to the receiver-

data buffer, the preceding character is destroyed and an overrun-error flag is set.

These error flags can be read as the M5M82C51AP status information. The occurrence of an error does not stop USART operations. The error flags are cleared by the ER ( $D_4$  bit) of the command instruction.

The asynchronous-system transfer formats are shown in Figs. 6 and 7.

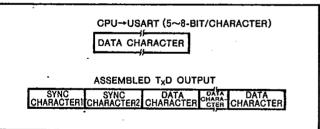

#### **Synchronous Transmission Mode**

In this mode the  $T_XD$  pin remains in the high-level state until initial setting by the CPU is completed. After initialization, the state of  $\overline{CTS}$ ="L" and  $T_XEN$  =1 enables serial transmission of characters through the  $T_XD$  pin. Then, data characters are sent out and shifted by the falling edge of the  $\overline{T_XD}$  signal. The transmission rate equals the  $\overline{T_XD}$  rate.

Thus, once data-character transfer starts, it must continue through the  $T_{x}D$  pin at the same rate as that of  $\overline{T_{x}C}$ . Unless data characters are provided from the CPU before the transmitter buffer becomes empty, one or two SYNC characters are automatically output from the  $T_{x}D$  pin. In this case, it should be noted that the  $T_{x}EMPTY$  pin enters the high-level state when there are no data characters left in the M5M82C51AP to be transferred, and that the low-level state is not entered until the USART is provided with the next data character from the CPU. Care should also be taken over the fact that merely setting a command instruction does not effect SYNC character insertion, because the SYNC character insertion is enabled after sending out the first data character.

In this mode, too, break characters are sent out in succession from the  $T_XD$  pin when SBRK is designated ( $D_3=1$ ) by a command instruction.

Fig. 6 Asynchronous transmission format I (transmission)

Fig. 7 Asynchronous transmission format II (reception)

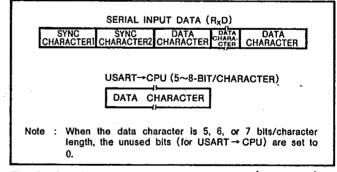

#### **Synchronous Reception Mode**

Character synchronization in this mode is carried out internally or externally by initial-setting designation.

Programming in the internal synchronous mode requires that an EH instruction (D<sub>7</sub>=1, enter hunt mode) is included in the first command instruction. Data on the RxD pin is sampled by the rising RxC signal, and the receiver-buffer contents are compared with the SYNC character each time a bit is input. Comparison continues until an agreement is reached. When the M5M82C51AP has been programmed in the bi-sync mode, data received in further succession is compared. The detection of two SYNC characters in succession makes the USART end the hunt mode, setting the SYNDET pin to the high-level state. This reset operation is prompted by the reading of the status information. When the parity has been programmed, SYNDET is not set in the middle of the last data bit but in the middle of the parity bit. In the external synchronous mode, the M5M82C51AP gets out of the hunt mode when a high-level synchronization signal is given to the SYNDET pin. The high-level signal requires a minimum duration of one RxC cycle. In the asynchronous mode, however, the EH signal does not affect the operation at all.

Parity and overrun errors are checked in the same way as in the asynchronous system. During hunt-mode operations the parity bit is not checked, but parity checking is carried out even when the receiver is disabled.

The CPU can command the receiver to enter the hunt mode, if synchronization is lost. This prevents the SYNC character from erroneously becoming equal to the received data when all the data in the receiver buffer is set to 1 Attention should be paid to the fact that the SYNDET F/F is reset each time status information is read irrespective of the synchronous mode's being internal or external. This,

however, does not return the M5M82C51AP to the hunt mode. Synchronism detection is carried out even though it is not the hunt mode. The synchronous transfer formats are shown in Figs. 8 and 9.

#### **Command Instruction**

This instruction defines actual operations in the communication mode designated by mode setting. Command instructions include transmitter/receiver enable error-reset, internal-reset, modem-control, enter-hunt and break transmission instructions.

The mode is set following the reset operation. A SYNC character is set as required, and the writing of high-level signals on the control/data pin  $(C/\overline{D})$  that follows it is regarded as a command instruction. When the mode is set all over again from the beginning, the M5M82C51AP can be reset by using inputting via the reset terminal or by internal resetting based on the command instruction.

- Note 1: The command error reset (ER), internal reset (IR) and enter-hunt-mode (EH) operations are only effective when the command instruction is loaded, so that these bits need not be returned to 0.

- 2: When a break character is sent out by a command, the T<sub>x</sub>D set to 0 immediately irrespective of whether or not the USART has sent out data.

- 3: Operations of the USART's receiver section which is always in the enable state cannot be inhibited. The command instruction R<sub>x</sub>E = 0 does not mean that data reception via the R<sub>x</sub>D pin is inhibited; it means that the R<sub>x</sub>RDY is masked and error flags are inhibited.

Fig. 8 Synchronous transmission format (transmission)

Fig. 9 Synchronous transmission format II (reception)

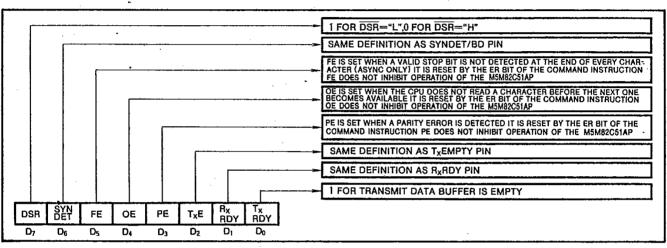

#### Status Information

The CPU can always read USART status by setting the C/D to high-level and RD to low-level.

The status information format is shown in Fig. 10. In this format RxRDY, TxEMPTY and SYNDET have the same definitions as those of the pins. This means that these three pieces of status information become high-level when each pin is 1. The other status information is defined as follows:

When the DSR pin is in the low-level state, status DSR:

Information DSR becomes 1.

FE: The occurrence of a frame error in the receiver section makes the status information FE=1.

OE: The occurrence of an overrun error in the receiver section makes the status information OE=1.

PE: The occurrence of a parity error in the receiver section makes this status information PE=1.

TxRDY: This information becomes 1 when the transmit

data buffer is empty. Be careful because this has a different meaning from the TxRDY pin that enters the high-level state only when the transmitter buffer is empty, when the CTS pin is in the low-

level state, and when TxEN is 1.

Flg. 10 Status information C/D="H", RD="L")

#### APPLICATION EXAMPLES

Fig. 11 shows an application example for the M5M82C51AP in the asynchronous mode. When the port addresses of the M5M82C51AP are assumed to be 00 # and 01 # in this figure, initial setting in the asynchronous mode is carried out in the following manner:

A, B6# MVI Mode setting

OUT 01#

A, 27# MVI Command instruction

OUT 01#

In this case, the following are set by mode setting:

Asynchronous mode

6-bit/character

Parity enable (even)

1.5 stop bits

Baud rate: 16X

Command instructions set the following

RTS=1→RTS pin="L"

$R_x = 1$

DTR=1→DTR pin="L"

TxEN=1

When the initial setting is complete, transfer operations are allowed. The RTS pin is initially set to the low-level by setting RTS to 1, and this serves as a CTS input with TxEN

being equal to 1. For this reason the same definition applies to the status and pin of TxRDY, and 1 is assigned when the transmit-data buffer is empty. Actual transfer of data is carried out in the following way:

IN 01# Status read

The IN instruction prompts the CPU to read the USART's status. The result is; if the TxRDY equals 1 transmitter data is sent from the CPU and written on the M5M82C51AP. Transmitter data is written in the M5M82C51AP in the following manner:

MVI A, 2D# 2D<sub>16</sub> is an example of transmitter data.

OUT 00# USART←(A)

Receiver data is read in the following manner:

IN 00# (A)←USART

In the above example, the status information is read and as a result, the transmitter data is written and read. Interruption processing by using the TxRDY and RxRDY pins is also possible.

Fig. 12 shows the status of the T<sub>x</sub>D pin when data written in the USART is transferred from the CPU. When the data shown in Fig.12 enters the R<sub>X</sub>D pin, data sent from the M5M82C51AP to the CPU becomes 2D<sub>16</sub> and bits D<sub>6</sub> and D<sub>7</sub> are treated as 0.

Fig. 11 Example of circuit using the asynchronous mode

Fig. 12 Example of data transmission

## M5M82C51AP/FP/J

## MITSUBISHI(MICMPTR/MIPRC)

T-75-37-07

## CMOS PROGRAMMABLE COMMUNICATION INTERFACE

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol             | Parameter                            | Conditions                                                       | Ratings                   | Unit |

|--------------------|--------------------------------------|------------------------------------------------------------------|---------------------------|------|

| Vcc                | Power-supply voltage                 |                                                                  | −0.3~7                    | V    |

| V <sub>I</sub>     | Input voltage                        | With respect to Vss                                              | -0.3~V <sub>cc</sub> +0.3 | ٧    |

| Vo                 | Oulput voitage                       |                                                                  | -0.3~Vco+0.3              | ٧    |

| Industry           | MAX "H"                              | All output and I/O pins output                                   | -500                      | μA   |

|                    | Output current                       | "H" level and force same current.                                |                           |      |

| I <sub>OLMAX</sub> | MAX "L" Output current               | All output and I/O pins output "L" level and force same current. | 2.5                       | mA   |

| Topr               | Operating free-air temperature range |                                                                  | -20~75                    | ဗ    |

| Tstg               | Storage temperature range            |                                                                  | <b>−65~150</b>            | C    |

## RECOMMENDED OPERATING CONDITIONS (Ta=-20~75°C unless otherwise noted)

| Symbol |                            |     | Unit |     |     |

|--------|----------------------------|-----|------|-----|-----|

|        | Parameter                  | Min | Nom  | Max | Onk |

| Voc    | Supply voltage             | 4.5 | 5    | 5.5 | ٧   |

| Vss    | Power-supply voltage (GND) |     | 0    |     | V   |

## ELECTRICAL CHARACTERISTICS (Ta=-20~75°C, V<sub>CC</sub>=5V±10%, V<sub>SS</sub>=0V unless otherwise noted)

| Symbol            | Parameter                         | Test conditions                                                                       | Limits |     |                      |            |

|-------------------|-----------------------------------|---------------------------------------------------------------------------------------|--------|-----|----------------------|------------|

|                   | - Fai alliefel                    |                                                                                       | Min    | Тур | Max                  | Unit       |

| V <sub>IH</sub>   | High-level input voltage          | •                                                                                     | 2.0    |     | V <sub>cc</sub> +0.3 | V          |

| VIL               | Low-level input voltage           |                                                                                       | -0.3   |     | 0.8                  | V          |

| VoH               | High-level output voltage         | I <sub>OH</sub> =-400μA                                                               | 2.4    |     |                      | <b>V</b> . |

| <b>VOH</b>        | High-level output voltage         | $I_{OH} = -20\mu A$                                                                   | 4.4    |     |                      |            |

| VoL               | Low-level output voltage          | I <sub>OL</sub> =2.2mA                                                                |        |     | 0.45                 | V          |

| loc               | Supply current from Voc           | All outputs are high-level                                                            |        |     | 5                    | mA         |

| liH               | High-level Input current          | V <sub>I</sub> =V <sub>GG</sub>                                                       | -10    |     | 10                   | μА         |

| I <sub>IL</sub> . | Low-level input current           | V <sub>1</sub> =0V                                                                    | -10    |     | 10                   | μΑ         |

| loz               | Off-state input current           | V <sub>o</sub> =0V~V <sub>cc</sub>                                                    | -10    |     | 10                   | μΑ         |

| Cı                | Input terminal capacitance        | Vcc=Vss, f=1MHz, 25mVrms, Ta=25°C                                                     |        |     | 10                   | pF         |

| Civo              | Input/output terminal capacitance | V <sub>CC</sub> =V <sub>SS</sub> , f=1MHz, 25mV <sub>rms</sub> , T <sub>a</sub> =25°C |        |     | 20                   | pF         |

www.DataSheet4U.com

M5M82C51AP/FP/J

## CMOS PROGRAMMABLE COMMUNICATION INTERFACE

#### TIMING REQUIREMENTS (Ta=-20~75°C, Vcc=5V±10%, Vss=0V unless otherwise noted)

| Symbol            | Parameter                                    |                     | Test conditions | Limits    |             |                       | 11-14              |

|-------------------|----------------------------------------------|---------------------|-----------------|-----------|-------------|-----------------------|--------------------|

|                   |                                              |                     |                 | Min       | Тур         | Max                   | Unit               |

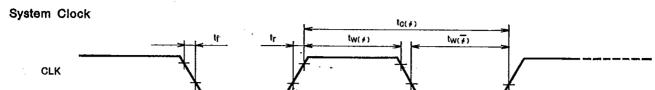

| t <sub>C(≠)</sub> | Clock cycle time (Notes4, 5)                 |                     |                 | 320       |             | 1350                  | ne                 |

| tw(+)             | Clock high pulse width                       | <u></u>             |                 | 120       |             | t <sub>C(#)</sub> -90 | វាន                |

| tw(F)             | Clock low pulse width                        |                     | <u> </u>        | - 90      |             |                       | ns                 |

| tr                | Clock rise time                              |                     |                 |           |             | 20                    | ns                 |

| tg.               | Clock fall time                              |                     |                 | ,         |             | 20                    | ns                 |

| •                 | Transmitter input clock                      | 1X baud rate        |                 | DC        |             | 64                    |                    |

| ftx               | frequency                                    | 16X baud rate       | ·               | DC        |             | 310                   | kHz                |

|                   | Troquency                                    | 64X baud rate       |                 | DC        |             | 615                   |                    |

| tw(TPWL)          | Transmitter input clock low                  | 1X baud rate        |                 | 12        |             |                       | †g(≠)              |

| -W(IPWL)          | pulse width                                  | 16X, 64X baud rate  |                 | 1         |             |                       | t <sub>G</sub> (#) |

| tw(TPWH)          | Transmitter input clock high                 | 1X baud rate        |                 | 15        |             | -                     | t <sub>G(≠)</sub>  |

| W(IPWH)           | pulse width                                  | 16X, 64X baud rate  |                 | 3         |             |                       | to(+)              |

|                   | Receiver Input clock                         | 1X baud rate        | • •             | DC        | -           | 64                    | kHz                |

| fex.              | frequency                                    | 16X baud rate       |                 | DC        |             | 310                   |                    |

|                   |                                              | 64X baud rate       |                 | DC        |             | 615                   |                    |

|                   | Receiver input clock low                     | 1X baud rate        |                 | 12        |             |                       | t <sub>G(≠)</sub>  |

| tW(HPWL)          | pulse width                                  | 16X, 64X baud rate  |                 | 1         |             |                       |                    |

| tw(RPWH)          | Receiver Input clock high                    | 1X baud rate        |                 | 15        |             |                       | t <sub>a(≠)</sub>  |

| W(RPWH)           | pulse width                                  | 16X, 64X baud rate  |                 | 3         |             |                       |                    |

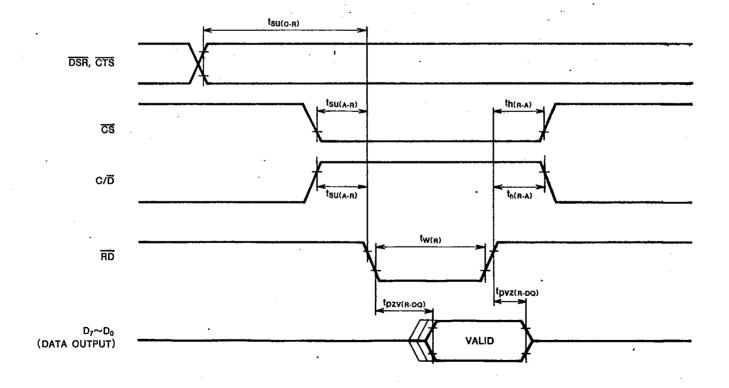

| tsu(A-R)          | Address setup time before rea                | d (CS, C/D) (Note6) |                 | 0         | _           |                       | ns                 |

| th(R—A)           | Address hold time after read (               | CS, C/D) (Note6)    |                 | 0         | กร          |                       |                    |

| t <sub>W(R)</sub> | Read pulse width                             |                     | - ·             | 250 (200) |             |                       | ns                 |

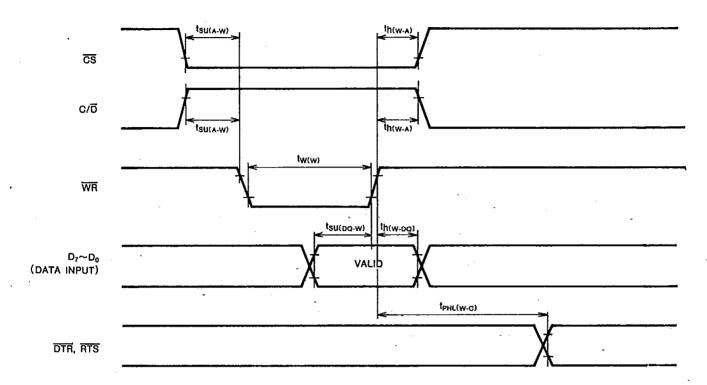

| tsu(A-W)          | Address setup time before wri                | le                  |                 | 0         |             |                       | ns                 |

| th(w-A)           | Address hold time after write                |                     |                 | 0         |             |                       | ns                 |

| tw(w)             | Write pulse width                            |                     |                 | 250 (200) |             |                       | ns                 |

| tsu(pa-w)         | Data setup time before write                 |                     |                 | 150(100)  |             |                       | ns                 |

| th(w-pa)          |                                              |                     |                 | 20(0)     |             |                       | กร                 |

| SI(ESD-RxC)       | E-SYNDET setup time before R <sub>x</sub> C  |                     |                 | 18        |             | - +                   | t <sub>G(#)</sub>  |

| tsu(o-n)          | Control setup time before read               |                     |                 | 20        |             | - · ·                 | t <sub>C(+)</sub>  |

| tav               | Write recovery time between writes (Note7)   |                     |                 | 6         | _           | <del></del>           | tc(+)              |

| tsu(Axo—is)       |                                              |                     |                 | 2         | • •         |                       | μs                 |

| h(IS-FuD)         | R <sub>X</sub> D hold time after internal sa | noting pulse        | -               | 2         | · - · · · · |                       | μS                 |

Note 4: The T<sub>x</sub>C and R<sub>x</sub>C frequencies have the following limitations with respect to CLK. For 1X baud rate f<sub>TX</sub>, f<sub>nx</sub>≤1/(30t<sub>C(#)</sub>). For 16X, 64X baud rate f<sub>TX</sub>, f<sub>nx</sub>≤1/(4.5t<sub>C(#)</sub>) 5: Reset pulse width=6t<sub>C(#)</sub> minimum. System clock must be running during reset. 6: CS, C/D are considered as address.

This recovery time is for mode initialization only. Write data is allowed only when  $T_XRDY=1$ . Recovery time between writes for asynchronous mode is  $8t_{C(\phi)}$ , and that for synchronous mode is  $16t_{C(\phi)}$ .

## CMOS PROGRAMMABLE COMMUNICATION INTERFACE

## SWITCHING CHARACTERISTICS ( $T_8 = -20 \sim 75\%$ , $V_{cc} = 5V \pm 10\%$ , $V_{ss} = 0V$ unless otherwise noted)

| Symbol                  | Parameter                                                              | Test conditions       |     | Limits |          |                    |

|-------------------------|------------------------------------------------------------------------|-----------------------|-----|--------|----------|--------------------|

|                         |                                                                        |                       | Min | Тур    | Max      | Unit               |

| tpzv(RDQ)               | Output data enable time after read (Note8)                             | C <sub>L</sub> =150pF |     |        | 200(170) | ns                 |

| t <sub>P</sub> vz(n-pq) | Output data disable time after read                                    |                       | 10  |        | 100      | ns.                |

| PZV(TxC-TxD)            | T <sub>XD</sub> enable time after falling edge of T <sub>X</sub> C     |                       |     |        | 1        | μЗ                 |

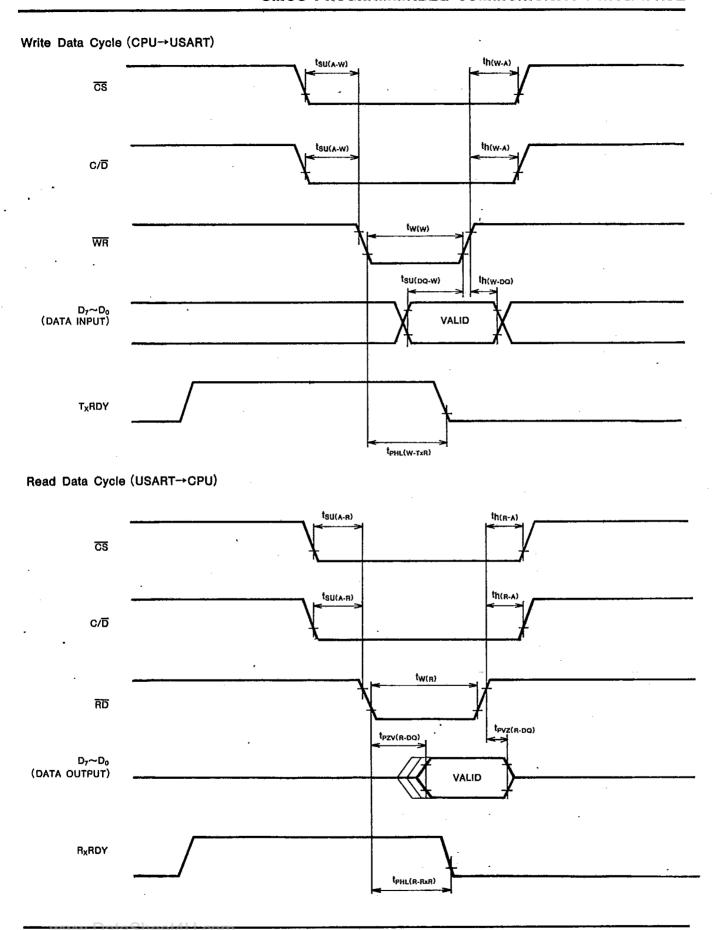

| PLH(CLB-TxR)            | Propagation time from center of last bit to TxRDY (Note9)              |                       |     |        | 8        | t <sub>O</sub> (≠) |

| PHL(W-TxR)              | Propagation time from write data to T <sub>X</sub> RDY clear (Note9)   |                       |     |        | 400      | ns                 |

| PLH(CLB-RxR)            | Propagation time from center of last bit to R <sub>X</sub> RDY (Note9) |                       |     |        | 26       | <sup>†</sup> G(≠)  |

| tphL(R-RxR)             | Propagation time from read data to R <sub>X</sub> RDY clear (Note9)    |                       |     |        | 400      | ns                 |

| (RxC-SYD)               | Propagation time from rising edge of RxC to internal SYNDET (Note9)    |                       |     |        | 26       | t <sub>c(≠)</sub>  |

| PLH(CLB-TxE)            | Propagation time from center of last bit to TxEMPTY (Note9)            |                       |     |        | 20       | t <sub>c(+)</sub>  |

| tehr(M-c)               | Propagation time from rising edge of WR to control (Note9)             |                       |     |        | 8        | t <sub>C(+)</sub>  |

Note 8: Assumes that address is valid before falling edge of RD.

9: Status-up data can have a maximum delay of 28 clock periods from the event affecting the status.

10: Input pulse level 0, 45~2, 4V Reference level Input V<sub>IH</sub>=2V, V<sub>IL</sub>=0, 8V Input pulse rise time 10ns Output V<sub>OH</sub>=2V, V<sub>OL</sub>=0.8V Input pulse fall time 10ns

11: M5M82C51AP is also invested with the extended specification showed in the brackets.

## **CMOS PROGRAMMABLE COMMUNICATION INTERFACE**

## TIMING DIAGRAMS

#### Receiver Clock & Data

## Write Control Cycle (CPU→USART)

## Read Control Cycle (USART→CPU)

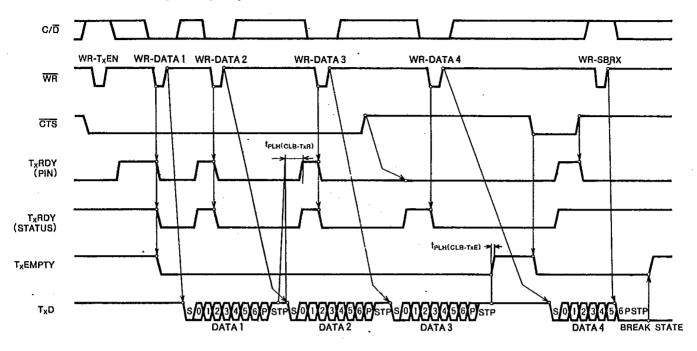

## Transmitter Control & Flag Timing (Async Mode)

Note 12: Example format= 7 bits/character with parity & 2 stop bits 13:  $T_XRDY(pin)="H"\leftarrow (Transmit-data buffer is empty) \cdot (T_XEN=1) \cdot (CTS="L")$  14:  $T_XRDY(status)=1 \leftarrow (Transmit-data buffer is empty)$

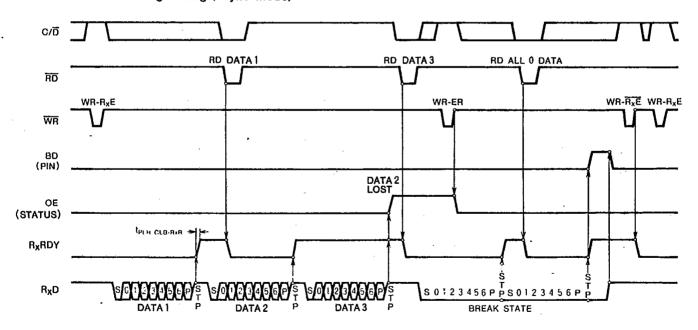

## Receiver Control & Flag Timing (Async Mode)

Note 15: Example format= 7 bits/character with parity & 2 stop bits

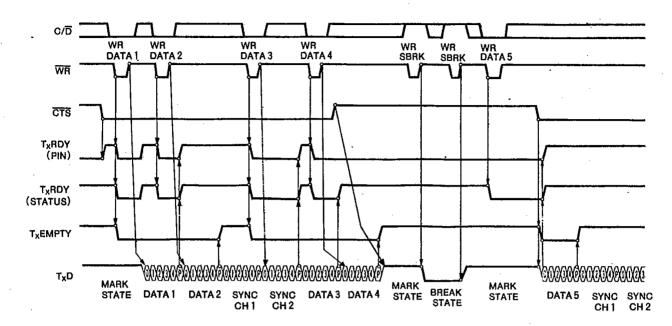

#### Transmitter Control & Flag Timing (Sync mode)

Note 16: Example format= 5 bits/character with parity, bi-sync characters.

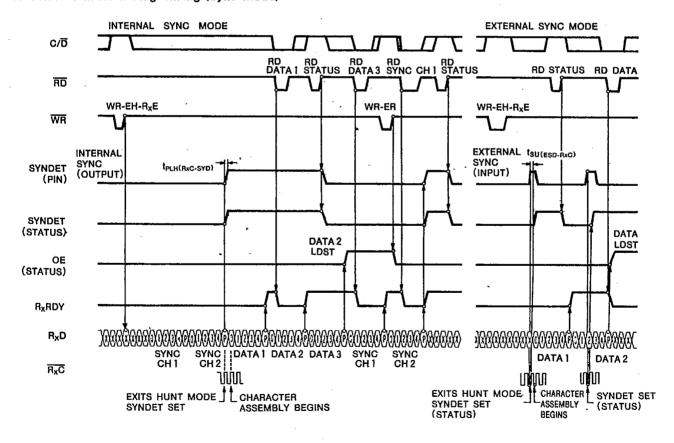

#### Receiver Control & Flag Timing (Sync Mode)

Note 17: Example format= 5 bits/character with parity, bi-sync characters.