## KS0119 Data Sheet

#### **MULTIMEDIA VIDEO**

#### **VIDEO ENCODER**

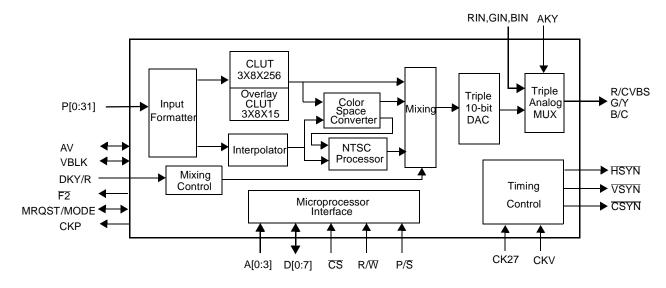

The KS0119 combines NTSC encoding with conventional RAM-DAC functions so that digitized video or computer generated graphics can be displayed on either NTSC or PC monitors. There are two data input channels which allow mixing. Provision is also made for analog mixing at the output. Operation modes can be programmed under host control. The KS0119 can be used with other members of the Samsung multimedia chip set in a typical desktop multimedia environment.

#### FEATURES

- Accepts true color; high color; color indexed; CCIR 601 4:4:4, 4:2:2, 4:1:1, or 2:1:1 formatted video inputs

- Supports analog NTSC CVBS, S-VIDEO, or RGB display

- Fully programmable timing generation; supports CGA, VGA, SVGA display up to 45 MHz pixel clock rate (with 100 pin package)

- · Accepts up to 2 input channels for digital mixing

- · Operate as slave or master in timing generation

- Supports alpha, chroma, and window keying for digital mixing

- · Provides an analog RGB mixing function

- Contains 3 256X8 color palette tables and 3 15X8 overlay color look up tables

- Contains 3 10-bit video grade DACs

- Provides a parallel microprocessor or a 3-wire serial interface

- Contains a two way color space converter: RGB -> NTSC, YCbCr -> RGB

- Supports power down mode

#### **BLOCK DIAGRAM**

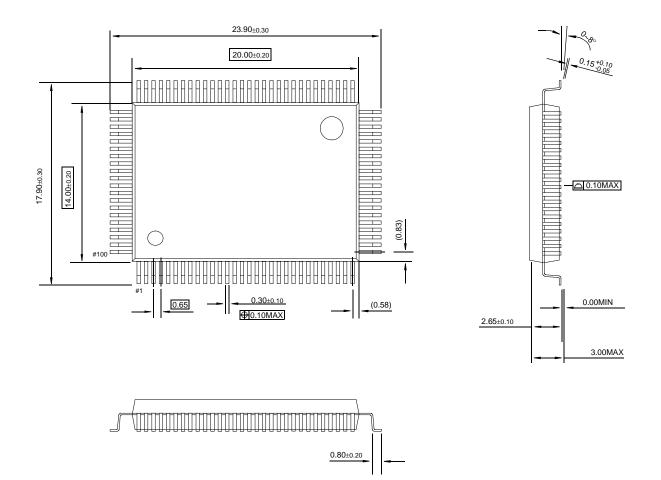

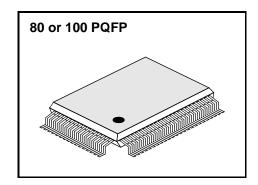

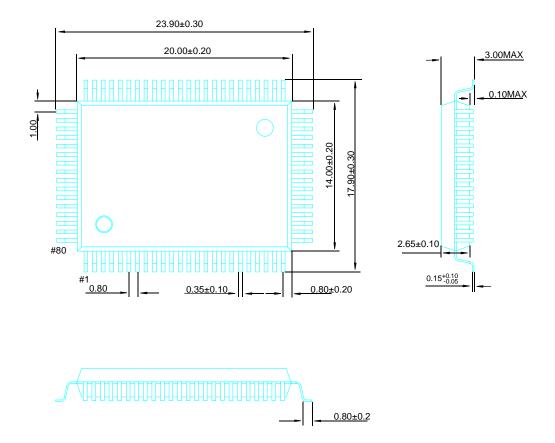

#### **ORDERING INFORMATION**

| Device   | Package | Temp. Range | Max. CKV |

|----------|---------|-------------|----------|

| KS0119   | 80-QFP  | 0° ∼ +65°C  | 32 MHz   |

| KS0119Q2 | 100-QFP | 0° ∼ +65°C  | 45 MHz   |

#### **APPLICATIONS**

- PC Video

- RAM DAC, Gamma Correction

- YUV DAC for MPEG, JPEG Play Back

- NTSC Video Encoder

#### **RELATED PRODUCT**

KS0122 MULTISTANDARD VIDEO DECODER

## **KS0119** Data Sheet

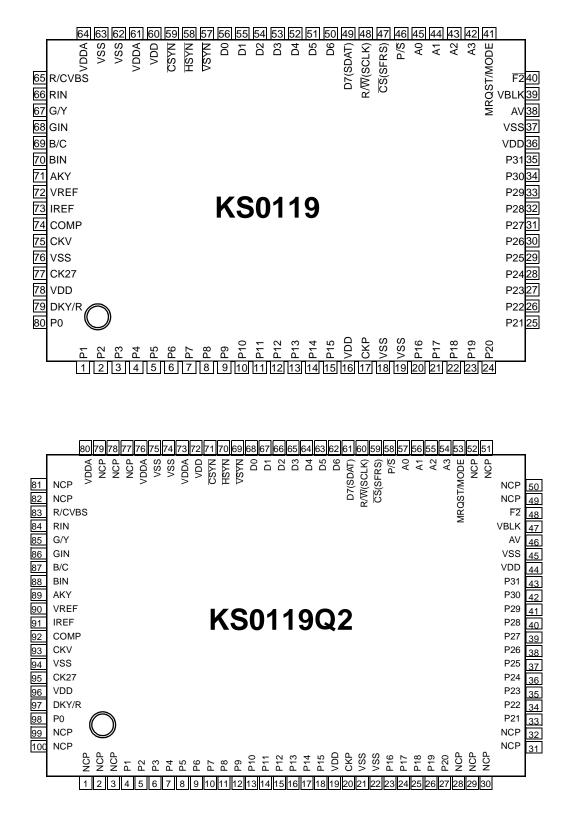

#### **PIN ASSIGNMENT**

## **TYPICAL APPLICATIONS**

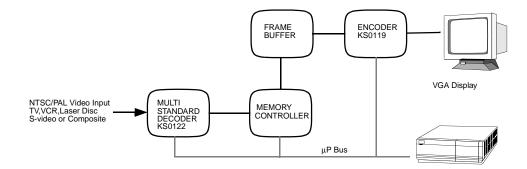

The KS0119 is shown in a VGA overlay application with the KS0122 Multistandard Video Decoder in Figure 1.

Figure 1. VGA Overlay

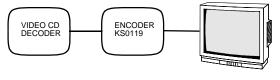

Figure 2 shows a video CD playback system using the KS0119 as a video encoder.

NTSC Display

Figure 2. Video CD Playback

### **PIN DESCRIPTION**

| Pin Name       | Pin #<br>(80)       | Pin #<br>(100)           | Туре | Description                                                                                                                                                                                                                                                                                                                                  |

|----------------|---------------------|--------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VIDEO BL       | JFFER INT           | ERFACE                   |      |                                                                                                                                                                                                                                                                                                                                              |

| P0 - P31       | 80,1-15,<br>20 - 35 | 98,4-18, 23-<br>27,33-43 | I    | Digital video input bus.                                                                                                                                                                                                                                                                                                                     |

| F2             | 40                  | 48                       | 0    | Field 2 indicator. Active low signal.                                                                                                                                                                                                                                                                                                        |

| MRQST<br>/MODE | 41                  | 53                       | I/O  | Dual function pin. During power-on, it is an input and its logic state determines whether the chip operates in NTSC mode or VGA pass through mode. A 4.7 K pull-up resistor sets the chip in VGA pass through mode. Otherwise it defaults to NTSC mode. After power-on this pin becomes an output and is high during active lines' sync tip. |

| AV             | 38                  | 46                       | I/O  | Active video indicator. Input in slave mode; output in master mode.                                                                                                                                                                                                                                                                          |

| VBLK           | 39                  | 47                       | I/O  | Vertical blank. Input in slave mode; output in master mode.                                                                                                                                                                                                                                                                                  |

| СКР            | 17                  | 20                       | 0    | Pixel clock output.                                                                                                                                                                                                                                                                                                                          |

| DKY/R          | 79                  | 97                       | I    | Dual function input pin. Configured by the <b>CMD</b> register bit 2. It can be used as either digital mixing or hardware RUN input. Please refer to the command register description for more detail.                                                                                                                                       |

| ANALOG         | MULTIPLE            | XER INPUT                |      |                                                                                                                                                                                                                                                                                                                                              |

| RIN            | 66                  | 84                       | I    | Analog R input to the analog mixing multiplexer.                                                                                                                                                                                                                                                                                             |

| GIN            | 68                  | 86                       | I    | Analog G input to the analog mixing multiplexer.                                                                                                                                                                                                                                                                                             |

| BIN            | 70                  | 88                       | I    | Analog B input to the analog mixing multiplexer.                                                                                                                                                                                                                                                                                             |

| AKY            | 71                  | 89                       | I    | Analog multiplexer control. A logic '0' connects analog RGB inputs to the output pins. A '1' connects DACs' outputs to the output pins.                                                                                                                                                                                                      |

| VIDEO OL       | JTPUT PO            | RT                       |      |                                                                                                                                                                                                                                                                                                                                              |

| HSYN           | 58                  | 70                       | 0    | Horizontal Sync. Active low, TTL signal for monitor. In the pass through mode HSYN is the inverted AV (pin 38).                                                                                                                                                                                                                              |

| VSYN           | 57                  | 69                       | 0    | Vertical Sync. Active low, TTL signal for monitor. In the pass through mode VSYN is the inverted VBLK (pin 39)                                                                                                                                                                                                                               |

| CSYN           | 59                  | 71                       | 0    | Composite Sync. Active low, TTL signal for monitor.                                                                                                                                                                                                                                                                                          |

| R/CVBS         | 65                  | 83                       | 0    | Either an analog R or Composite output, controlled by <b>CMD</b> bits 5 and 1. It can drive a 37.5 $\Omega$ load (doubly terminated 75 $\Omega$ load).                                                                                                                                                                                       |

| G/Y            | 67                  | 85                       | 0    | Either an analog G or S-video Y output, controlled by <b>CMD</b> bits 5 and 1. It can drive a 37.5 $\Omega$ load.                                                                                                                                                                                                                            |

| B/C            | 69                  | 87                       | 0    | Either an analog B or S-video C output, controlled by <b>CMD</b> bits 5 and 1. It can drive a 37.5 $\Omega$ load.                                                                                                                                                                                                                            |

## **PIN DESCRIPTION (Continued)**

| Pin Name      | Pin #<br>(80) | Pin #<br>(100) | Туре | Description                                                                                                                                                                                          |

|---------------|---------------|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFEREN       | NCE AND (     | COMPENSATIO    | ON   |                                                                                                                                                                                                      |

| VREF          | 72            | 90             | I/O  | Voltage reference. It has an internal voltage reference circuit, but may be overridden by an external voltage reference input. A 0.1 $\mu$ F ceramic capacitor is required between this pin and GND. |

| IREF          | 73            | 91             | I    | A resistor is connected between this pin and GND to control the DAC output current.                                                                                                                  |

| COMP          | 74            | 92             | I    | Compensation capacitor for the DAC internal reference amplifier. A 0.1 $\mu$ F ceramic capacitor is required between this pin and VDDA.                                                              |

| HOST INT      | ERFACE        |                |      |                                                                                                                                                                                                      |

| P/S           | 46            | 58             | Ι    | Microprocessor interface configuration control. Tie to VDD to select parallel mode. Tie to VSS to select serial mode.                                                                                |

| CS<br>(SFRS)  | 47            | 59             | I    | Chip select strobe in parallel mode (Frame Sync in serial mode).                                                                                                                                     |

| R/W<br>(SCLK) | 48            | 60             | I    | Read/write in parallel mode (Serial clock in serial mode).                                                                                                                                           |

| D7<br>(SDAT)  | 49            | 61             | I/O  | Data bus msb in parallel mode (Serial data in serial mode).                                                                                                                                          |

| D0 - D6       | 56-50         | 68-62          | I/O  | Parallel data bus bit 0 to 6.                                                                                                                                                                        |

| A0 - A3       | 45-42         | 57-54          | I    | Address bus for parallel interface.                                                                                                                                                                  |

| CLOCK IN      | NPUT          |                | •    |                                                                                                                                                                                                      |

| CKV           | 75            | 93             | I    | Clock input used to generate pixel clock for VGA display.                                                                                                                                            |

|               |               | 1              | 1    |                                                                                                                                                                                                      |

#### POWER AND GROUND

77

95

L

| VDD  | 16,36,<br>60,78           | 19,44,72,96           | +5V | Digital power supply. |

|------|---------------------------|-----------------------|-----|-----------------------|

| VSS  | 18,19,<br>37,62,<br>63,76 | 21,22,45,74,<br>75,94 | GND | Digital ground.       |

| VDDA | 61,64                     | 76,80                 | +5V | Analog power supply.  |

27 MHz clock input, required for NTSC display.

NCP

CK27

| NCP | N/A | 1-3,28-32,<br>49-52,77-<br>79,81,82,99,<br>100 | - | These pins are directly connected to the die substrate. They are<br>intended as heat dissipation points. It is recommended that each<br>corner set of NCP pins be connected to as large as possible solid<br>metal plane on the PCB component surface side. If electrical connect<br>is desired (not required) only connection to VDDA is allowed. |

|-----|-----|------------------------------------------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-----|-----|------------------------------------------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

## PIN CROSS REFERENCE (Numerical Order by Pin Number):

### 80-PQFP

| Pin # | Pin Name | Pin # | Pin Name | Pin # | Pin Name   | Pin # | Pin Name |

|-------|----------|-------|----------|-------|------------|-------|----------|

| 1     | P1       | 21    | P17      | 41    | MRQST/MODE | 61    | VDDA     |

| 2     | P2       | 22    | P18      | 42    | A3         | 62    | VSS      |

| 3     | P3       | 23    | P19      | 43    | A2         | 63    | VSS      |

| 4     | P4       | 24    | P20      | 44    | A1         | 64    | VDDA     |

| 5     | P5       | 25    | P21      | 45    | A0         | 65    | R/CVBS   |

| 6     | P6       | 26    | P22      | 46    | P/S        | 66    | RIN      |

| 7     | P7       | 27    | P23      | 47    | CS(SFRS)   | 67    | G/Y      |

| 8     | P8       | 28    | P24      | 48    | R/W(SCLK)  | 68    | GIN      |

| 9     | P9       | 29    | P25      | 49    | D7(SDAT)   | 69    | B/C      |

| 10    | P10      | 30    | P26      | 50    | D6         | 70    | BIN      |

| 11    | P11      | 31    | P27      | 51    | D5         | 71    | AKY      |

| 12    | P12      | 32    | P28      | 52    | D4         | 72    | VREF     |

| 13    | P13      | 33    | P29      | 53    | D3         | 73    | IREF     |

| 14    | P14      | 34    | P30      | 54    | D2         | 74    | COMP     |

| 15    | P15      | 35    | P31      | 55    | D1         | 75    | CKV      |

| 16    | VDD      | 36    | VDD      | 56    | D0         | 76    | VSS      |

| 17    | СКР      | 37    | VSS      | 57    | VSYN       | 77    | CK27     |

| 18    | VSS      | 38    | AV       | 58    | HSYN       | 78    | VDD      |

| 19    | VSS      | 39    | VBLK     | 59    | CSYN       | 79    | DKY/R    |

| 20    | P16      | 40    | F2       | 60    | VDD        | 80    | P0       |

# KS0119 Data Sheet

# PIN CROSS REFERENCE (Continued):

100-PQFP

| Pin # | Pin Name | Pin # | Pin Name | Pin # | Pin Name   | Pin # | Pin Name |

|-------|----------|-------|----------|-------|------------|-------|----------|

| 1     | NCP      | 26    | P19      | 51    | NCP        | 76    | VDDA     |

| 2     | NCP      | 27    | P20      | 52    | NCP        | 77    | NCP      |

| 3     | NCP      | 28    | NCP      | 53    | MRQST/MODE | 78    | NCP      |

| 4     | P1       | 29    | NCP      | 54    | A3         | 79    | NCP      |

| 5     | P2       | 30    | NCP      | 55    | A2         | 80    | VDDA     |

| 6     | P3       | 31    | NCP      | 56    | A1         | 81    | NCP      |

| 7     | P4       | 32    | NCP      | 57    | A0         | 82    | NCP      |

| 8     | P5       | 33    | P21      | 58    | P/S        | 83    | R/CVBS   |

| 9     | P6       | 34    | P22      | 59    | CS(SFRS)   | 84    | RIN      |

| 10    | P7       | 35    | P23      | 60    | R/W(SCLK)  | 85    | G/Y      |

| 11    | P8       | 36    | P24      | 61    | D7(SDAT)   | 86    | GIN      |

| 12    | P9       | 37    | P25      | 62    | D6         | 87    | B/C      |

| 13    | P10      | 38    | P26      | 63    | D5         | 88    | BIN      |

| 14    | P11      | 39    | P27      | 64    | D4         | 89    | AKY      |

| 15    | P12      | 40    | P28      | 65    | D3         | 90    | VREF     |

| 16    | P13      | 41    | P29      | 66    | D2         | 91    | IREF     |

| 17    | P14      | 42    | P30      | 67    | D1         | 92    | COMP     |

| 18    | P15      | 43    | P31      | 68    | D0         | 93    | CKV      |

| 19    | VDD      | 44    | VDD      | 69    | VSYN       | 94    | VSS      |

| 20    | CKP      | 45    | VSS      | 70    | HSYN       | 95    | CK27     |

| 21    | VSS      | 46    | AV       | 71    | CSYN       | 96    | VDD      |

| 22    | VSS      | 47    | VBLK     | 72    | VDD        | 97    | DKY/R    |

| 23    | P16      | 48    | F2       | 73    | VDDA       | 98    | P0       |

| 24    | P17      | 49    | NCP      | 74    | VSS        | 99    | NCP      |

| 25    | P18      | 50    | NCP      | 75    | VSS        | 100   | NCP      |

#### **1. GENERAL DESCRIPTION**

The KS0119 is a digital NTSC encoder combined with basic RAM-DAC functions. It is designed to be a high performance, cost effective NTSC or PC display driver. The chip consists of a two way Color Space Converter, which is capable of supporting almost all the popular input formats pertaining to PC video, graphics, or image compression/decompression. The chip contains signal processing blocks to enhance image quality and reduce artifacts due to sampling. It provides image manipulation facilities such as masking, mixing, hue control, and color lookup tables to create special effects. It includes a programmable Timing Generator to generate the synchronization signals and color burst for different display monitors.

### 1.1. Application

The KS0119 is a versatile chip, which can be used for many application such as NTSC encoding, YUV DAC, RAM DAC, Gamma correction, mixing, and VGA overlay. CK27 must be used for NTSC encoder, whereas CKV must be used for the others. It is recommended that the unused clock input pin be tied to a static state.

#### **1.2. Power On Default**

The KS0119 can be configured for two power-on default states: one for NTSC video encoding and the other for VGA overlay application. For the latter the MRQST/MODE pin must be pulled up so the KS0119 defaults to *sync pass through* mode and Channel A is set to support 8-bit pseudo color format after power up. In this mode, the KS0119 functions as a RAM-DAC. The internal video timing generator is disabled; the horizontal and vertical syncs are delay compensated for the video path delay and passed to the sync output pins. The sync pass through mode is recommended for VGA overlay application.

| Power On MRQST/MODE Pin State | Operations    | Channel A Input Format | SYNCPT | Clock Source |

|-------------------------------|---------------|------------------------|--------|--------------|

| 0                             | NTSC encoding | 4:2:2 YCbCr            | 0      | CK27         |

| 1                             | VGA overlay   | 8 bit pseudo color     | 1      | CKV          |

Table 1: Power On Default State

### 1.3. Operation Mode

The KS0119 can be configured to operate either in master mode or slave mode. In the master mode the encoder uses the parameter stored in the CRT control registers to generate all the video timings and outputs synchronizing signals (refer to "VIDEO OPERATIONAL TIMING" on page 18). In the slave mode the encoder synchronize the internal pixel counter on the falling edge of AV, and line counter on the rising edge or VBLK. The sync outputs, HSYN and  $\nabla$ SYN, waveform can be modified if sync pass through is disabled (SYNCPT=0). Table 2 shows the registers related to the sync generation.

Table 2: Sync Output Generation

|                                    |                         | •                                     |                  |

|------------------------------------|-------------------------|---------------------------------------|------------------|

|                                    | MASTER                  | SLA                                   | AVE              |

| Control Registers                  | MSTR=1                  | MSTR=0, SYNCPT=1                      | MSTR=0, SYNCPT=0 |

| HSYN, VSYN                         | Internally generated    | Pass through                          | Regenerated      |

| Video Output Port Sync<br>Polarity | Active low              | Inverted AV and VBLK                  | Active low       |

| Input Sync Polarity Control        | N/A                     | VSP, HSP                              |                  |

| CRT Control Registers              | Index Registers 70 - 79 | 1                                     |                  |

| Comments                           |                         | Recommend for VGA overlay application |                  |

#### 1.4. Power Down Mode

The KS0119 supports power down mode; the DAC outputs can be put into high impedance state by turning off the current source to conserve power.

#### 1.5. Digital Video Input Format

The digital video input is a 32 bit port. This port can be used as a single channel or logically divided into two channels: A and B. Channel A's input can be true color, color indexed, or CCIR 601 formats. Channel B's input is restricted to CCIR 601 formats. The supported formats and their bit assignments are shown in Table 3 and Table 4.

The KS0119 accepts certain input combinations from Channel A and B. However the following rules must be observed when both channels are selected (their format registers contain valid numbers):

- 1. Channel B's input is ignored if mixing is not enabled.

- 2. If mixing is enabled, channel A is the foreground and will be displayed if the mixing key is false.

- 3. In YC/YC mixing, both channels must have the same format (e.g. Channel A's format is 4:1:1A, Channel B's format must be 4:1:1A. See Table 3 and Table 4).

|           |    |    |    |      |      |    | FOF | MAT  | REGI    | STER   | R (BIT | 7 - 4) |     |     |     |      |     |    |

|-----------|----|----|----|------|------|----|-----|------|---------|--------|--------|--------|-----|-----|-----|------|-----|----|

| VALUE     | 1  | 2  | 3  | 4    | 5    | 6  | 9   | 9    | 4       | 4      |        | E      | 3   |     |     | (    | )   |    |

| TYPE      |    |    |    | RGB  |      |    | 4:2 | 2:2  | 2:1:    | 1 A    |        | 4:1:   | 1 A |     |     | 4:1: | 1 B |    |

| # of Bits | 24 | 16 | 16 | 15   | 12   | 8  | 1   | 6    | 1       | 6      |        | 1      | 2   |     |     | 1    | 6   |    |

| Pixel Bus |    |    |    |      |      |    | •   | Pixe | el Byte | e Sequ | lence  |        |     |     |     |      |     |    |

| FIXEI DUS | Ν  | Ν  | Ν  | Ν    | Ν    | Ν  | 2N  | +1   | 2N      | +1     | 4N     | +1     | +2  | +3  | 4N  | +1   | +2  | +3 |

| P0        | B0 | B0 | B0 | B0   | P0   | P0 | Cb0 | Cr0  | Cb0     | Cr0    |        |        |     |     | Cb0 |      | Cr0 |    |

| P1        | B1 | B1 | B1 | B1   | P1   | P1 | Cb1 | Cr1  | Cb1     | Cr1    |        |        |     |     | Cb1 |      | Cr1 |    |

| P2        | B2 | B2 | B2 | B2   | P2   | P2 | Cb2 | Cr2  | Cb2     | Cr2    |        |        |     |     | Cb2 |      | Cr2 |    |

| P3        | B3 | B3 | B3 | B3   | P3   | P3 | Cb3 | Cr3  | Cb3     | Cr3    |        |        |     |     | Cb3 |      | Cr3 |    |

| P4        | Β4 | B4 | G0 | B4   | P4   | Ρ4 | Cb4 | Cr4  | Cb4     | Cr4    | Cr6    | Cr4    | Cr2 | Cr0 | Cb4 |      | Cr4 |    |

| P5        | B5 | G0 | G1 | G0   | P5   | P5 | Cb5 | Cr5  | Cb5     | Cr5    | Cr7    | Cr5    | Cr3 | Cr1 | Cb5 |      | Cr5 |    |

| P6        | B6 | G1 | G2 | G1   | P6   | P6 | Cb6 | Cr6  | Cb6     | Cr6    | Cb6    | Cb4    | Cb2 | Cb0 | Cb6 |      | Cr6 |    |

| P7        | B7 | G2 | G3 | G2   | P7   | P7 | Cb7 | Cr7  | Cb7     | Cr7    | Cb7    | Cb5    | Cb3 | Cb1 | Cb7 |      | Cr7 |    |

| P8        | G0 | G3 | G4 | G3   | OVL0 |    | Y0  | Y0   | Y0      | Y0     | Y0     | Y0     | Y0  | Y0  | Y0  | Y0   | Y0  | Y0 |

| P9        | G1 | G4 | G5 | G4   | OVL1 |    | Y1  | Y1   | Y1      | Y1     | Y1     | Y1     | Y1  | Y1  | Y1  | Y1   | Y1  | Y1 |

| P10       | G2 | G5 | R0 | R0   | OVL2 |    | Y2  | Y2   | Y2      | Y2     | Y2     | Y2     | Y2  | Y2  | Y2  | Y2   | Y2  | Y2 |

| P11       | G3 | R0 | R1 | R1   | OVL3 |    | Y3  | Y3   | Y3      | Y3     | Y3     | Y3     | Y3  | Y3  | Y3  | Y3   | Y3  | Y3 |

| P12       | G4 | R1 | R2 | R2   |      |    | Y4  | Y4   | Y4      | Y4     | Y4     | Y4     | Y4  | Y4  | Y4  | Y4   | Y4  | Y4 |

| P13       | G5 | R2 | R3 | R3   |      |    | Y5  | Y5   | Y5      | Y5     | Y5     | Y5     | Y5  | Y5  | Y5  | Y5   | Y5  | Y5 |

| P14       | G6 | R3 | R4 | R4   |      |    | Y6  | Y6   | Y6      | Y6     | Y6     | Y6     | Y6  | Y6  | Y6  | Y6   | Y6  | Y6 |

| P15       | G7 | R4 | R5 | TKEY |      |    | Y7  | Y7   | Y7      | Y7     | Y7     | Y7     | Y7  | Y7  | Y7  | Y7   | Y7  | Y7 |

| P16       | R0 |    |    |      |      |    |     |      |         |        |        |        |     |     |     |      |     |    |

| P17       | R1 |    |    |      |      |    |     |      |         |        |        |        |     |     |     |      |     |    |

| P18       | R2 |    |    |      |      |    |     |      |         |        |        |        |     |     |     |      |     |    |

| P19       | R3 |    |    |      |      |    |     |      |         |        |        |        |     |     |     |      |     |    |

| P20       | R4 |    |    |      |      |    |     |      |         |        |        |        |     |     |     |      |     |    |

| P21       | R5 |    |    |      |      |    |     |      |         |        |        |        |     |     |     |      |     |    |

| P22       | R6 |    |    |      |      |    |     |      |         |        |        |        |     |     |     |      |     |    |

| P23       | R7 |    |    |      |      |    |     |      |         |        |        |        |     |     |     |      |     |    |

Table 3: Channel A Input Format

|           |       |      |     |      |     |      | FOF | RMAT | REG     | ISTER | R (BIT | 3 - 0 | )   |     |      |     |    |       |

|-----------|-------|------|-----|------|-----|------|-----|------|---------|-------|--------|-------|-----|-----|------|-----|----|-------|

| VALUE     | 1     | 2    | 2   | 3    | 3   | 4    | 1   | Ę    | 5       |       | (      | 6     |     |     | 7    | 7   |    | 9     |

| TYPE      | 4:4:4 | 4:2: | 2 A | 4:2: | 2 B | 2:1: | 1 A | 2:1: | 1 B     |       | 4:1:   | 1 A   |     |     | 4:1: | 1 B |    | 4:4:4 |

| # of Bits | 24    | 1    | 6   | 2    | 4   | 1    | 6   | 2    | 4       |       | 1      | 2     |     |     | 1    | 6   |    | 24    |

| Pixel     |       | 1    |     |      |     |      |     | Pixe | el Byte | e Seq | uence  | ;     |     | 1   |      |     |    |       |

| Bus       | Ν     | 2N   | +1  | 2N   | +1  | 2N   | +1  | 2N   | +1      | 4N    | +1     | +2    | +3  | 4N  | +1   | +2  | +3 | Ν     |

| P0        |       |      |     |      |     |      |     |      |         |       |        |       |     |     |      |     |    | Cr0   |

| P1        |       |      |     |      |     |      |     |      |         |       |        |       |     |     |      |     |    | Cr1   |

| P2        |       |      |     |      |     |      |     |      |         |       |        |       |     |     |      |     |    | Cr2   |

| P3        |       |      |     |      |     |      |     |      |         |       |        |       |     |     |      |     |    | Cr3   |

| P4        |       |      |     |      |     |      |     |      |         |       |        |       |     |     |      |     |    | Cr4   |

| P5        |       |      |     |      |     |      |     |      |         |       |        |       |     |     |      |     |    | Cr5   |

| P6        |       |      |     |      |     |      |     |      |         |       |        |       |     |     |      |     |    | Cr6   |

| P7        |       |      |     |      |     |      |     |      |         |       |        |       |     |     |      |     |    | Cr7   |

| P8        | Cr0   |      |     | Cr0  |     |      |     | Cr0  |         |       |        |       |     |     |      |     |    |       |

| P9        | Cr1   |      |     | Cr1  |     |      |     | Cr1  |         |       |        |       |     |     |      |     |    |       |

| P10       | Cr2   |      |     | Cr2  |     |      |     | Cr2  |         |       |        |       |     |     |      |     |    |       |

| P11       | Cr3   |      |     | Cr3  |     |      |     | Cr3  |         |       |        |       |     |     |      |     |    |       |

| P12       | Cr4   |      |     | Cr4  |     |      |     | Cr4  |         |       |        |       |     |     |      |     |    |       |

| P13       | Cr5   |      |     | Cr5  |     |      |     | Cr5  |         |       |        |       |     |     |      |     |    |       |

| P14       | Cr6   |      |     | Cr6  |     |      |     | Cr6  |         |       |        |       |     |     |      |     |    |       |

| P15       | Cr7   |      |     | Cr7  |     |      |     | Cr7  |         |       |        |       |     |     |      |     |    |       |

| P16       | Cb0   | Cb0  | Cr0 | Cb0  |     | Cb0  | Cr0 | Cb0  |         |       |        |       |     | Cb0 |      | Cr0 |    | Cb0   |

| P17       | Cb1   | Cb1  | Cr1 | Cb1  |     | Cb1  | Cr1 | Cb1  |         |       |        |       |     | Cb1 |      | Cr1 |    | Cb1   |

| P18       | Cb2   | Cb2  | Cr2 | Cb2  |     | Cb2  | Cr2 | Cb2  |         |       |        |       |     | Cb2 |      | Cr2 |    | Cb2   |

| P19       | Cb3   | Cb3  | Cr3 | Cb3  |     | Cb3  | Cr3 | Cb3  |         |       |        |       |     | Cb3 |      | Cr3 |    | Cb3   |

| P20       | Cb4   | Cb4  | Cr4 | Cb4  |     | Cb4  | Cr4 | Cb4  |         | Cr6   | Cr4    | Cr2   | Cr0 | Cb4 |      | Cr4 |    | Cb4   |

| P21       | Cb5   | Cb5  | Cr5 | Cb5  |     | Cb5  | Cr5 | Cb5  |         | Cr7   | Cr5    | Cr3   | Cr1 | Cb5 |      | Cr5 |    | Cb5   |

| P22       | Cb6   | Cb6  | Cr6 | Cb6  |     | Cb6  | Cr6 | Cb6  |         | Cb6   | Cb4    | Cb2   | Cb0 | Cb6 |      | Cr6 |    | Cb6   |

| P23       | Cb7   | Cb7  | Cr7 | Cb7  |     | Cb7  | Cr7 | Cb7  |         | Cb7   | Cb5    | Cb3   | Cb1 | Cb7 |      | Cr7 |    | Cb7   |

| P24       | Y0    | Y0   | Y0  | Y0   | Y0  | Y0   | Y0  | Y0   | Y0      | Y0    | Y0     | Y0    | Y0  | Y0  | Y0   | Y0  | Y0 | Y0    |

| P25       | Y1    | Y1   | Y1  | Y1   | Y1  | Y1   | Y1  | Y1   | Y1      | Y1    | Y1     | Y1    | Y1  | Y1  | Y1   | Y1  | Y1 | Y1    |

| P26       | Y2    | Y2   | Y2  | Y2   | Y2  | Y2   | Y2  | Y2   | Y2      | Y2    | Y2     | Y2    | Y2  | Y2  | Y2   | Y2  | Y2 | Y2    |

| P27       | Y3    | Y3   | Y3  | Y3   | Y3  | Y3   | Y3  | Y3   | Y3      | Y3    | Y3     | Y3    | Y3  | Y3  | Y3   | Y3  | Y3 | Y3    |

| P28       | Y4    | Y4   | Y4  | Y4   | Y4  | Y4   | Y4  | Y4   | Y4      | Y4    | Y4     | Y4    | Y4  | Y4  | Y4   | Y4  | Y4 | Y4    |

| P29       | Y5    | Y5   | Y5  | Y5   | Y5  | Y5   | Y5  | Y5   | Y5      | Y5    | Y5     | Y5    | Y5  | Y5  | Y5   | Y5  | Y5 | Y5    |

| P30       | Y6    | Y6   | Y6  | Y6   | Y6  | Y6   | Y6  | Y6   | Y6      | Y6    | Y6     | Y6    | Y6  | Y6  | Y6   | Y6  | Y6 | Y6    |

| P31       | Y7    | Y7   | Y7  | Y7   | Y7  | Y7   | Y7  | Y7   | Y7      | Y7    | Y7     | Y7    | Y7  | Y7  | Y7   | Y7  | Y7 | Y7    |

#### Table 4: Channel B Input Format

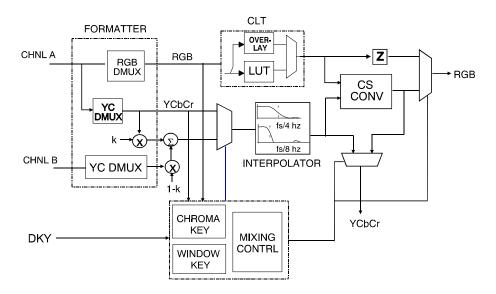

### 2. DIGITAL MIXING

The KS0119 supports digital mixing between the two input channels. Digital mixing is the process of replacing a selected area in the foreground (Channel A) with the corresponding area in the background (Channel B) according to the output of the keying function. The result is that the foreground objects appear situated in front of the background's. Mixing is an indispensable tool to create special effects, such as animation, picture in picture, and video overlay. The ability to select a small area to display can be used to reduce or hide the image download time during presentations. The digital mixing is controlled by the Mixing Control Register (**MXCTR**) and control registers 05h to 0Dh.

Figure 3. Digital Mixer Signal Flow Diagram

### 2.1. Mixing Methods

The KS0119 supports two types of mixing: RGB/YC and YC/YC.

#### 2.1.1. RGB/YC Mixing

RGB/YC mixing is automatically selected if channel A's format is either high color or pseudo color. The process simply replaces channel A's video with Channel B's when the output of the Keying function is 1.

#### 2.1.2. YC/YC Mixing

If channel A's input is YCbCr formatted (format register value greater than 7), then YC/YC mixing is selected. In YC/ YC mixing, when the output of the Keying function is 1, the Channel A's chrominance components are replaced with Channel B's, while the luminance signals are linearly blended according to the equation

$$Yout = \frac{1}{8} \cdot [K \cdot Ya + (1 - K) \cdot Yb]$$

where K is a programmable value, from 0 to 7, stored in the **Mixing Control** register (**MXCTR**). Linear Mixing preserves the shadows inside the keyed area.

### 2.2. Keying Methods

The KS0119 supports Window Keying, Index Keying, Chroma Keying, Alpha Keying, External Keying, and certain combinations of them. These are described in detail below.

#### 2.2.1. Index Keying

If channel A's input format is 2, 3, 4, 5, or 6, Index Keying can be used for mixing. Channel A's inputs are first compared with the contents in the two 8 bit **TEMPLATE** registers (**TMPLB**,**TMPLA**). The results are then filtered by the **MASK** registers (**MSKB**, **MSKA**) and ANDed together to generate the key signal. If the input is 8 or 15 bits wide, the unused bits are automatically masked out. Figure 4 shows the logic operation involved in Index Keying.

Figure 4. Index Keying Generation

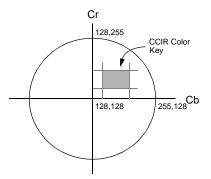

#### 2.2.2. Chroma Keying

If channel A's input is YCbCr format, Chroma Keying can be used for mixing. A rectangular area is specified in the Cb-Cr space (Figure 5). If Channel A's Cb/Cr values fall within this area, Channel B's video will be displayed. In this mode, **TMPLA** and **TMPLB** specify the lower and upper Cb, respectively, and **MSKA** and **MSKB** specify the lower and upper Cr, respectively, in the Cb-Cr space. Note that Cb and Cr are binary offset numbers with 128 corresponding to zero intensity, 0 and 255 corresponding to maximum intensity.

Figure 5. Cb-Cr Chroma Keying

#### 2.2.3. Window Keying

A rectangular key window is specified in X-Y coordinates in the active display area. If window mixing is enabled and the **OUTSD** bit of the **Mixing Control** register is 0, Channel B is displayed inside the window, and Channel A is outside the window. The converse is true if the **OUTSD** bit is 1. If both the Chroma and Window Keyings are enabled, the **OUTSD** bit specifies where the Chroma Keying will be applied: 0 inside the window and 1 outside the window.

The 8 msb's of the four 10 bit coordinate registers, Window Horizontal Start Address, Window Horizontal End Address, Window Vertical Start Address and Window Vertical End Address, are stored in the **WHS**, **WHE**, **WVS** and **WVE** registers, respectively, while the 2 lsb bits are stored in the **WHV** register. The four msb registers are double clocked, and synchronized to the **WVE** write. A write to the **WVE** register will transfer the four msb registers' contents, concatenated with their corresponding lsb's, to the respective final address registers. Modifying the msb

## **KS0119 Data Sheet**

register without writing to the **WVE** register will have no effect on the final address register. For multiplexed YCbCr video inputs, it is recommended that the horizontal window boundaries equal integer multiples of the block size.

#### 2.2.4. Alpha Keying

If Channel A's input is only 15 bits (format 4, RGB 5:5:5), bit 15 of the input can be used as a mixing key.

#### 2.2.5. External Key

Pin DKY/R can be used as a mixing key if the **DKF** bit of the **Command** register (**CMD**) configures this pin as an external key input.

### **3. SIGNAL PROCESSING**

### 3.1. Y/C Interpolation Filters

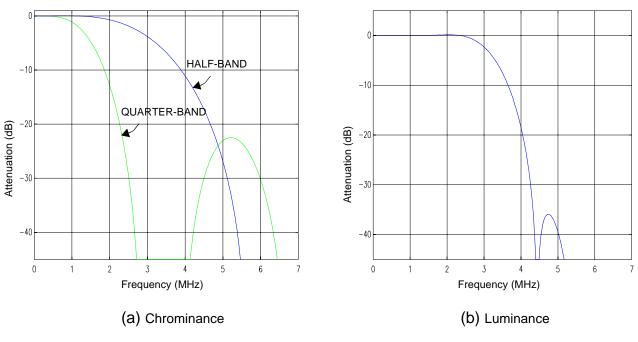

The incoming YCbCr signals are processed by the Interpolation Unit to increase the data rates to 13.5 MHz. (4:4:4 format). The multiplexed chroma signals are up sampled first, and then pass through either a 6th-order half-band or an 8th-order quarter-band filter. The reconstruction filters have flat 0 to 0.6 MHz frequency response as shown in Figure 6-(a). The received half-sampled luminance component (MPEG decoder output, 360 samples/line), which has a bandwidth less than 3 MHz, after being up sampled, will pass through a 14th-order smooth filter whose frequency response characteristic is shown in Figure 6-(b). These filters ensure the preservation of base band signals as well as the elimination of attendant high frequency aliasing components due to up sampling.

### 3.2. Band-limit Filter

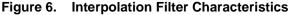

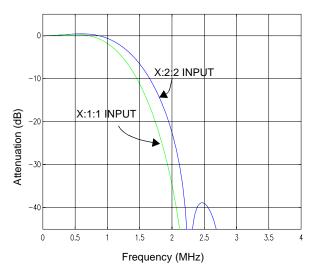

The NTSC Encoder Unit consists of a 4 MHz luminance low pass filter and two equal bandwidth 1.2 MHz chrominance low pass filters. The functions of these filters are to limit the frequency contents of the computer generated image, to reduce the cross-luminance/chrominance distortion due to the mixing processes, and to enhance the resolutions. The digital filters are designed to have faster roll-off than the analog counterparts so that the quantization noise, which is monotonic decreasing along the frequency axis, are removed as soon as they pass the band of interest. Figure 7 shows the overall filter characteristics (interpolation cascaded with band-limit) for X:1:1 and X:2:2 formatted data. Also shown in Figure 8 are the luminance band-limit characteristics with and without the chroma filter.

At the filters' outputs, each pixel is represented by 3 10-bit numbers, which are maintained until the DAC inputs. Hence the block effects due to the limited quantization levels are reduced.

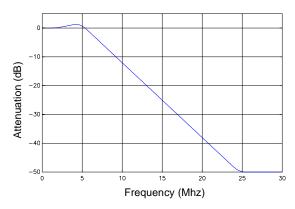

Figure 7. Chrominance Filter Characteristics

Figure 8. Luminance Band-limit Filter Characteristics

### 3.3. SINC (Sinx/x) Function Effect

The digital-to-analog converter exhibits a high frequency roll-off SINC filter characteristic owing to the zeroth order sample and hold process. The roll-off is a function of the DAC's conversion rate. The NTSC Encoder Unit also incorporates a 6th-order interpolation filter to raise the data rate to 27 MHz. The roll-off at 4 MHz is reduced from -1 dB (sampled at 13.5 MHz) to -0.2 dB. The up sampling also pushes the high frequency "image" beyond 23 MHz, greatly reducing the analog reconstruction filter requirement at the DAC's outputs.

## 4. SIGNAL MANIPULATION FUNCTIONS

The NTSC Encoder Unit provides the facilities for the user to control the contrast, hue, color killer and the vertical blanking period by programming the **Command Register B** (**CMDB**) and **Hue Control** register(**HUE**).

### 4.1. Hue Control

The chromaticity can be changed by modifying the modulation angle. The entire 360° hue range is divided into 264 equal units. To move the hue angle by k units the congruent 83\*k MOD 264 should be loaded into the **HUE** register and bit 7 of **CMDB** register. The **HUE** register will not be transferred to the final **Hue Control** register until a write to the **CMDB** register occurs. Therefore, when changing the hue angle, the **HUE** register must be loaded first followed by a write to the **CMDB** register. The following examples show the value to be programmed into the HUE register for +5 and -5 degree hue angle:

Examples:

+5 degree Hue angle

$k = \left\lfloor \frac{5}{360} \times 264 \right\rfloor = 3$ HUE = mod(k \cdot 83, 264) = mod(249, 264) = 249

-5 degree Hue angle

$$k = \left\lfloor \frac{355}{360} \times 264 \right\rfloor = 260$$

HUE = mod(260 \cdot 83, 264) = mod(264 \cdot 81 + 196, 264) = 196

## 4.2. Chroma Trap Filter

The luminance path includes a Chroma Trap filter. When this filter is enabled (**CMDB**[4] = 1), the effective bandwidth is reduced to 2.8 MHz, resulting in a softer picture.

### 4.3. Color Killer

When bit 3 of the **CMDB** register is set to 1, the chroma data will be removed and the picture will be displayed as black and white.

### 4.4. Vertical Blanking

Normally, line 1 to line 9 in field 1 and the second half of line 263 to 272 in field 2 are blanked automatically. However, if bit 2 of **CMDB** register is 1, the blanking period is extended to the line specified in the **VBLK** register.

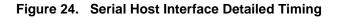

#### 5. VIDEO OPERATIONAL TIMING

The KS0119 can operate in either slave or master mode. In slave mode, the chip uses two external input signals, active video (AV) and vertical blank (VBLK), to synchronize the internal operation. In master mode, however, the chip outputs these two signals. The chip generates two additional signals: Memory Transfer Request (MRQST) and field two indicator ( $\overline{F2}$ ), which can be used to simplify the interface to an external frame buffer controller. Figure 9 shows the timing waveform for the NTSC output mode.

|            |        |             |     |     |     |     | FIRST | FIEL   | D   |     |     |                  |               |        |             |

|------------|--------|-------------|-----|-----|-----|-----|-------|--------|-----|-----|-----|------------------|---------------|--------|-------------|

|            | 525    | 1           | 2   | 3   | 4   | 5   | 6     | 7      | 8   | 9   | 10  | 11               | 20            | 21     |             |

| CVBS       | ┟╹     |             |     |     |     |     |       |        |     |     | ╢┛  | ╜┛               | ╶╢╋┦╵╌╢╋──    | ╶╢┛──  | -           |

| AV         |        |             |     |     |     |     |       |        |     |     |     |                  |               |        | ٦           |

| VBLK       |        |             |     |     |     |     |       |        |     |     | 1   |                  |               |        | _           |

| F2         |        |             |     |     |     |     |       |        |     |     |     |                  |               |        |             |

| MRQST(E    | BLKALL | =0)         |     |     |     |     |       |        |     |     |     |                  |               |        | _           |

| MRQST(E    | BLKALL | =1)         |     |     |     |     |       |        |     |     |     |                  | /T            |        | _           |

|            |        |             |     |     |     | S   | ECON  | ID FIE | LD  |     |     |                  |               |        |             |

|            | 263    | 264         | 265 | 266 | 267 | 268 | 269   | 270    | 271 | 272 | 273 | 274              | 283           | 284    |             |

| CVBS       | ∣ſ∎⊣┌  |             |     |     | пп  | пп  | n nr  |        |     |     |     | ─ <b>╷┌</b> ╋─── | ╶┐ӷ╉╌╱└─┐ӷ╉── |        | _           |

|            |        | υu          | υυ  |     |     |     |       | υu     | υu  | UU  | Ц   | Ц                |               | ╶╢╋─── |             |

| AV         |        |             |     |     |     |     |       |        |     |     |     |                  |               |        | ٦           |

| AV<br>VBLK |        |             |     |     |     |     |       |        |     |     |     |                  |               |        | ٦<br>_      |

|            |        |             |     |     |     |     |       |        |     |     |     |                  |               |        | Т<br>-<br>- |

| VBLK       |        | <br><br>=0) |     |     |     |     |       |        |     |     |     |                  |               |        | _<br>_<br>_ |

Figure 9. NTSC Output Timing

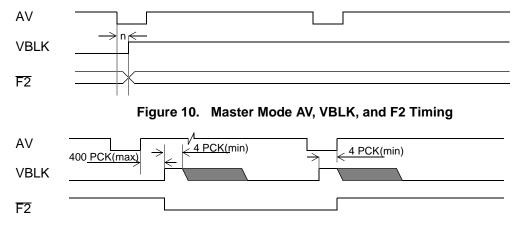

In Master mode, the timing shown in Figure 10 is maintained among AV, VBLK, and F2, where n is the leading pixel number (see Figure 12 for more detail). In Slave mode, the two inputs AV and VBLK must meet the timing requirement as shown in Figure 11 in order for the Encoder to obtain the correct field information.

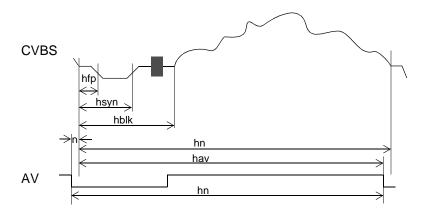

#### 5.1. Horizontal Timing

Each scan line contains hn pixels as shown in Figure 12. Of the hn pixels, only (hn - hblk) pixels are displayed. The AV signal is used to indicate the active portion of the horizontal scan line. The Horizontal Blank portion actually consists of three parts: Horizontal Front Porch, Horizontal Sync, and Horizontal Back Porch. The KS0119 outputs the Horizontal Sync signal to the display monitor.

In Master mode, the NTSC Encoder generates the AV signal. AV can be used by the external frame buffer to control the pixel read out. Because of the memory access latency associated with the external memory subsystem, AV should lead the pixel data by n pixel clocks. This is done by controlling the hav parameter. All horizontal timing parameters are programmable and Table 5 contains the information on how to calculate the line timing control register values for both NTSC and RGB displays.

Figure 12. Horizontal Timing

| Register | Parameter                 | NTSC Value | RGB Value   |

|----------|---------------------------|------------|-------------|

| HFP      | Horizontal Front Porch    | 11         | Thfp + 1    |

| HSYN     | Horizontal Sync Tip       | 184*       | Thsyn + 1   |

| HBLK     | Horizontal Blanking       | 135        | Thblk - 3   |

| HN       | Number of Pixels per Line | 856        | Thn - 2     |

| HAV      | End of Active Video       | 854 - n    | Thn - 4 - n |

| Table 5: | Line | Timing | Register | Values |

|----------|------|--------|----------|--------|

|----------|------|--------|----------|--------|

\*: This number is not used to control the Horizontal Sync Tip in NTSC mode.

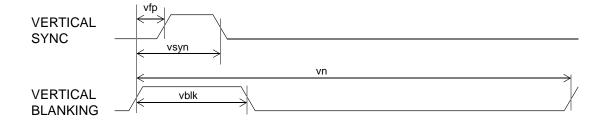

### 5.2. Vertical Timing

Each field contains the active line and vertical blank portions. The vertical blank portion is further divided into Vertical Front Porch, Verical Sync, and Vertical Back Porch. There are four parameters that control the vertical timing: VFP, VSYN, VBLK, and VN. They are specified in terms of lines. Figure 13 shows the timing related to the four parameters. For NTSC output, these parameters are fixed and the power on default values should be used. However, if the **BLKALL** bit in the **Command Register** is set to 1, the **VBLK** value will be used instead. Table 6 provides information on how to program these parameters.

## KS0119 Data Sheet

## **MULTIMEDIA VIDEO**

In Master mode, the NTSC Encoder outputs the VBLK signal. This signal can be used to synchronize the external frame buffer controller's line counter. In Slave mode, VBLK is an input and is used to synchronize the chip's internal operation.

Figure 13. Vertical Timing

| Register | Parameter                 | Value      |

|----------|---------------------------|------------|

| VFP      | Vertical Front Porch      | Tvfp - 1.  |

| VSYN     | Vertical Sync Tip         | Tvsyn - 1. |

| VBLK     | Vertical Blanking         | Tvblk - 1. |

| VN       | Number of Lines per Frame | Tvn - 1.   |

Table 6: Frame Timing Register Value

### 5.3. MRQST/MODE and F2

MRQST/MODE is output during AV low for the active lines. This signal can be used to transfer video data from DRAM to shift registers in the VRAM.  $\overline{F2}$  can be used by the external frame buffer controller for interlaced display.

### 6. COLOR PALETTE RAM, OVERLAY LOOKUP TABLE, AND PIXEL MASK REGISTER

The KS0119 contains a Color Palette RAM, an Overlay Lookup Table, and a Pixel Mask Register. They can be accessed through the host interface.

### 6.1. Accessing the Color Palette RAM

The Color Palette RAM is organized as 3 256x8 arrays. From the programmer's point of view, there are 256 entries; each entry has 3 bytes. To write to the Color Palette RAM, the entry offset is written to the Color Palette Write Index register, then three bytes, in the order of R, G, and B, are written to the Color Palette Data register. If consecutive entries are to be written, only the first offset address needs to be written to the Color Palette Write Index register. It is important to note that writing to the Color Palette Data register should always consist of multiples of three bytes. Unpredictable result will occur if this is not strictly followed.

Reading the Color Palette RAM is similar to writing the Color Palette RAM except the entry offset is written to the Color Palette Read Index register.

The Color Palette RAM is located at the center of the RGB path. There is no bypass path. Consequently, for 24-bit true color inputs even though the translations are not required the Color Palette RAM still needs to be loaded.

### 6.2. 6-Bit Color Palette Mode

The KS0119 also supports 6-bit color palette mode. When this mode is selected by setting **Command Register** bit 3 to 0, only the 6 LSB's for each color entry are loaded into the corresponding color palette register. Internally, the 6 LSB's are shifted to the MSB positions with the 2 LSB's padded with 0's. When reading from the palette RAM, the two MSB's must be ignored.

### 6.3. High Color and Pseudo Color Input Lookup Address.

The high color and pseudo color inputs pass through a formatter, which expands the inputs to a full 24 bits according to Table 7. For inputs with R, G, and B components less than 8 bits, the LSB's are padded with 0's. The outputs of the formatter, after passing through the pixel mask filter, become the color palette table addresses.

| Mode    | Video Input<br><msbisb></msbisb> | Color Lookup Table Input<br><msblsb></msblsb> |           |            |  |  |

|---------|----------------------------------|-----------------------------------------------|-----------|------------|--|--|

|         |                                  | Byte 2                                        | Byte 1    | Byte 0     |  |  |

| 1       | R<7:0>:G<7:0>:B<7:0>             | R<7:0>                                        | G<7:0>    | B<7:0>     |  |  |

| 2       | R<4:0>:G<5:0>:B<4:0>             | R<4:0>000                                     | G<5:0>00  | B<4:0>000  |  |  |

| 3       | R<5:0>:G<5:0>:B<3:0>             | R<5:0>00                                      | G<5:0>00  | B<3:0>0000 |  |  |

| 4       | R<4:0>:G<4:0>:B<4:0>             | R<4:0>000                                     | G<4:0>000 | B<4:0>000  |  |  |

| 5 and 6 | P<7:0>                           | P<7:0>                                        | P<7:0>    | P<7:0>     |  |  |

| Table 7: | <b>RGB Input Formatter Conversion Table</b> |

|----------|---------------------------------------------|

|----------|---------------------------------------------|

### 6.4. Overlay Lookup Table

Four overlay input bits address the Overlay Lookup Table. If the overlay input is non-zero, overlay data will be displayed. The Overlay Look Up Table contains 15 entries, and each entry has three bytes, in the order of R, G, and B. The entry offset starts from 1 instead of 0. The access method for the Overlay Lookup Table is the same as that for the Color Palette RAM.

## 6.5. Pixel Mask Register

The Pixel Mask Register is used to filter the pixel data coming out from the RGB Input Formatter. Each R, G, B pixel byte is bit-wise ANDed with the pixel mask register. Special effects can be created by selectively masking out certain bits. This register needs to be initialized after power up.

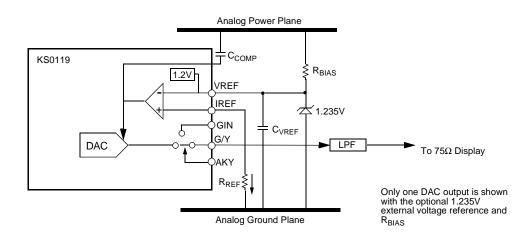

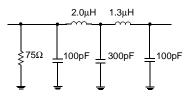

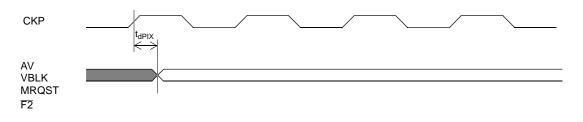

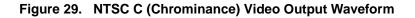

## 7. DAC AND EXTERNAL RECONSTRUCTION FILTER

The three DACs on the chip are identical; they are video grade 10 bit current DACs. Figure 14 shows a typical configuration for the DAC portion of the chip.  $R_{REF}$  is connected to IREF to adjust the DAC output full scale. The DAC output is designed to drive a doubly terminated 75  $\Omega$  load. A 105  $\Omega$  resistor connected to  $R_{REF}$  can be used to set the output voltage peak to the RS-170A standard of 1 V. The built-in voltage reference has a large variation due to manufacturing technology limitations. For precise control of the DAC, an external voltage reference can be used. A variable resistor may also be used for  $R_{REF}$  to adjust the full scale DAC output current. The recommended analog filter circuit and its characteristic are shown in Figure 15 and Figure 16, respectively.

Figure 14. DAC Reference Circuit and Termination

Figure 15. DAC Output Analog Reconstruction Filter

Figure 16. DAC Output Analog Reconstruction Filter Response

#### 8. HOST INTERFACE

The KS0119 contains a conventional parallel microprocessor interface and a proprietary serial interface. The parallel microprocessor interface consists of 11 pins, some of which are shared by the three pin serial bus. The logic sense of the P/S control pin defines the host interface mode, parallel or serial. Three of the interface pins serve a dual purpose depending upon the mode selected. The  $\overline{CS}$ , R/W, and D7 pins in parallel mode become SFRS, SCLK, and SDAT pins in serial mode, respectively.

#### 8.1. Microprocessor Address Map

The KS0119 contains three groups of registers. The first group is the control registers. The control registers are used for feature/option selection. The second group is the color palette RAM. The third group is the overlay color look up table. Table 8 shows the microprocessor address map for the KS0119.

| Address<br>(Hex) | Description               |

|------------------|---------------------------|

| 00               | Color Palette Write Index |

| 01               | Color Palette Data        |

| 02               | Pixel Mask Register       |

| 03               | Color Palette Read Index  |

| 04               | Overlay CLUT Write Index  |

| 05               | Overlay CLUT Data         |

| 06               | Reserved                  |

| 07               | Overlay CLUT Read Index   |

| 08               | Control Register Index    |

| 09               | Control Register Data     |

Table 8: Microprocessor Address Map

### 8.2. Transfer Mode

Both the read and write cycles require that the index be written to the KS0119 first. The index is written to location ADDR = 08. The index is the internal address location for each register. The internal address is indicated by the register number associated with each register. Once the index is written, the selected register can have data read from or written to location ADDR = 09. Non-sequential internal registers are accessed individually by writing an index and then reading or writing one byte of data. Sequential locations can be accessed by writing the index for the first register and then reading or writing multiple bytes of data. The index auto-increments internally by one for each successive byte of data accessed while ADDE = 09. This mode is useful when initializing the device or when accessing word wide or blocks of registers.

The color palette and overlay CLUT operate in a similar fashion, except that separate index locations exist for read and write operations. The color palette write index is written to ADDR=00, and palette data is written to ADDR=01. For read operation, the index is written to ADDR=03. The color palette and overlay exhibit the same auto-increment capability as the control registers. This simplifies loading the color palette.

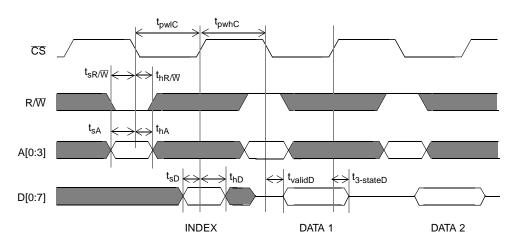

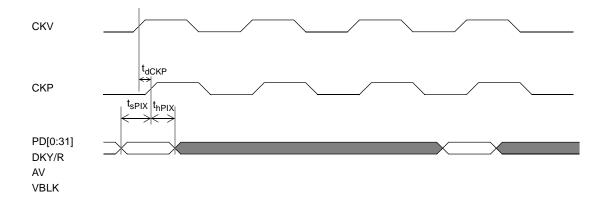

#### 8.3. Serial Host Interface

The serial interface is selected by connecting the  $P/\overline{S}$  pin to ground. This interface uses three signals: SFRS, SDAT,

## KS0119 Data Sheet

and SCLK. The SFRS indicates a valid data transfer. Serial data is carried through the SDAT and clocked in or out with the SCLK. The data protocol sends each byte as msb first.

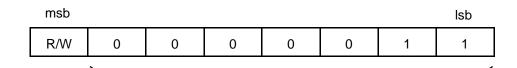

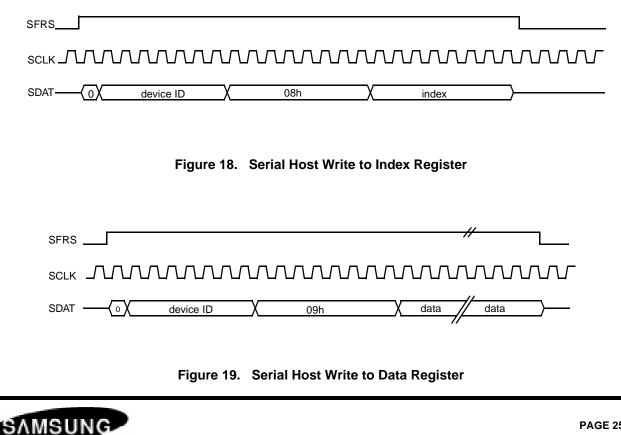

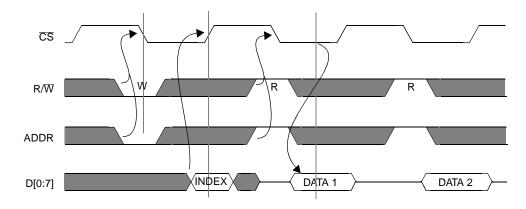

#### 8.3.1. Serial Host Write/Read to KS0119

Each data transfer cycle is called a frame. A valid frame is indicated by a HIGH on the SFRS signal. A frame consists at least three bytes: the first byte contains a 7-bit slave device ID and a R/W bit (bit assignment shown in Figure 17): the second byte indicates the internal address of register the data transfer is intended for (see Table 8); and the third and consequent byte(s) are the data to be transferred to/from the register. If the data transfer is to/ from the index register, three bytes are needed each frame. Since the KS0119 features an auto index increment function, consecutive data transfer to/from the data registers can be completed within the same frame.

slave device ID

Figure 18 shows an example of a write to the index register. Each bit is latched into the device by the rising edge of the SCLK. A write to the data register is similar to a write to the index register except the second byte is 01h and the third and so on byte(s) are the data to be written (Figure 19). When the data is read from the device, the KS0119 outputs each bit is after the falling edge of the SCLK.

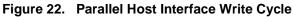

### 8.4. Parallel Host Interface

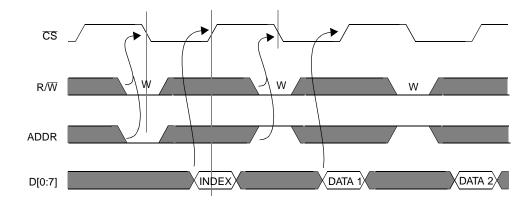

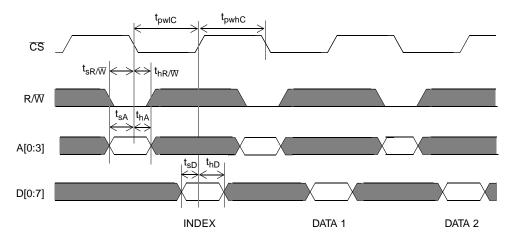

Figure 20 shows the timing relation for a parallel read cycle. Figure 21 shows the timing for a parallel write cycle. The address ADDR and read/write R/W are stable before the  $\overline{CS}$  signal is lowered. Data written to the KS0119 must be stable before  $\overline{CS}$  goes high. Data is read from the KS0119 when  $\overline{CS}$  is low.

Figure 20. Parallel Host Interface Read Cycle

Figure 21. Parallel Host Interface Write Cycle

## 9. DETAILED CONTROL REGISTER DESCRIPTION

This section contains the detailed description of the control registers. The control registers can be categorized into three functional groups: indexes 60h to 63h are general control registers; indexes 64h to 6Dh are mixing control registers; indexes 70h to 79h are CRT control registers. Table 9 is a register summary, followed by the individual register description. Default values are noted with an asterisk (\*) after the value description.

| Index | Mnemonic | Default | Description                      |

|-------|----------|---------|----------------------------------|

| 60h   | CMD      | 12h/A2h | Command Register                 |

| 61h   | FMT      | 90h/60h | Input Format                     |

| 62h   | CMDB     | 02h     | Second Command Register          |

| 63h   | HUE      | 00h     | Chroma Phase Offset Bits 70      |

| 64h   | MXCTR    | 00h     | Mixing Control                   |

| 65h   | WHS      | 00h     | Window Row Start Address         |

| 66h   | WHE      | 00h     | Window Row End Address           |

| 67h   | WVS      | 00h     | Window Column Start Address      |

| 68h   | WVE      | 00h     | Window Column End Address        |

| 69h   | WHV      | 00h     | Window Overflow Address(Isbs)    |

| 6Ah   | TMPLA    | 00h     | Chroma Key TMPLATE Byte 0        |

| 6Bh   | TMPLB    | 00h     | Chroma Key TMPLATE Byte 1        |

| 6Ch   | MSKA     | 00h     | Chroma Key MASK Byte 0           |

| 6Dh   | MSKB     | 00h     | Chroma Key MASK Byte 1           |

| 70h   | HAVN     | 33h/B3h | HN and HAV Overflow Bits         |

| 71h   | HAV      | 54h     | Master Mode's AVout Lead Control |

| 72h   | HN       | 58h     | Number of Pixels per Line        |

| 73h   | HFP      | 0Bh     | Horizontal Front Porch           |

| 74h   | HSYN     | B8h     | End of Horizontal Sync           |

| 75h   | HBLK     | 87h     | End of Horizontal Blanking       |

| 76h   | VN       | 00h     | Number of Lines per Field        |

| 77h   | VFP      | 83h     | Vertical Front Porch             |

| 78h   | VSYN     | 06h     | End of Vertical Sync             |

| 79h   | VBLK     | 14h     | End of Vertical Blanking         |

Note:

Some registers have two default values. The first number is for **MRQST/MOED** pin pulled low. The second number is for **MRQST/MODE** pin pulled high.

| Command Register |          |                                                                                                                                                                        |               |              |              |              |               |              |         |

|------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------|--------------|--------------|---------------|--------------|---------|

| Index            | Mnemonic | bit 7                                                                                                                                                                  | bit 6         | bit 5        | bit 4        | bit 3        | bit 2         | bit 1        | bit 0   |

| 60h              | CMD      | RUN                                                                                                                                                                    | MSTR          | RGB          | CKSL         | 8/6*         | DKF           | CVBS         | YC      |

|                  |          |                                                                                                                                                                        |               |              |              |              |               |              |         |

|                  |          |                                                                                                                                                                        |               |              |              |              |               |              |         |

| RUN              |          | Software RL                                                                                                                                                            |               |              | al state mac | hine is con  | trolled by th | ne logically | ORed    |

|                  | 1        |                                                                                                                                                                        | ware run e    |              | 5.           |              |               |              |         |

|                  | Ċ        |                                                                                                                                                                        | ware run d    |              |              |              |               |              |         |

|                  | -        |                                                                                                                                                                        |               |              | DE is latche | ed into this | bit durina p  | ower-on.     |         |

| MSTR             |          | -                                                                                                                                                                      |               |              | ode select.  |              | 51            |              |         |

|                  | 1        | Mas                                                                                                                                                                    | ster.         |              |              |              |               |              |         |

|                  | C        | ) Slav                                                                                                                                                                 | /e.*          |              |              |              |               |              |         |

| RGB              | A        | Analog outp                                                                                                                                                            | ut format s   | elect.       |              |              |               |              |         |

|                  | 1        | RG                                                                                                                                                                     | З.            |              |              |              |               |              |         |

|                  | C        | ) Con                                                                                                                                                                  | nposite and   | I Super vide | eo.          |              |               |              |         |

|                  | Т        | The logic sta                                                                                                                                                          | ate of the N  | IRQST/MO     | DE is latche | ed into this | bit during p  | ower-on.     |         |

| CKSL             | C        | Clock input                                                                                                                                                            | •             |              |              |              |               |              |         |

|                  | 1        |                                                                                                                                                                        |               | •            | el clock CK  |              | . ,           |              |         |

|                  | -        | 0 CKV is selected as the source, and CKP has the same rate as the clock input.<br>The inverted logic state of the MRQST/MODE is latched into this bit during power-on. |               |              |              |              |               |              |         |

| 0.40*            |          |                                                                                                                                                                        | •             | e of the MR  | QST/MODE     | s latched    | into this bit | during pov   | /er-on. |

| 8/6*             |          | 6 bit paleti<br>אלי                                                                                                                                                    |               |              |              |              |               |              |         |

|                  | 1<br>C   |                                                                                                                                                                        | t palette.    |              |              |              |               |              |         |

| DKF              | -        | DKY/R pin c                                                                                                                                                            | •             | n control    |              |              |               |              |         |

| DI               | 1        | •                                                                                                                                                                      | •             | key for digi | ital mixing  |              |               |              |         |

|                  | C        |                                                                                                                                                                        | •             | ware RUN i   | •            |              |               |              |         |

| CVBS             |          |                                                                                                                                                                        |               |              | ontrols R/C  | VBS DAC.     |               |              |         |

|                  | 1        |                                                                                                                                                                        | VBS DAC i     |              |              |              |               |              |         |

|                  | C        | R/C                                                                                                                                                                    | VBS DAC i     | s in the pov | ver down st  | ate.         |               |              |         |

| YC               | lí       | f bit 5 of this                                                                                                                                                        | s register is | 0 this bit c | ontrols G/Y  | and B/C D    | ACs.          |              |         |

|                  | 1        | G/Y                                                                                                                                                                    | and B/C D     | ACs are on   | ı.           |              |               |              |         |

|                  | C        | ) G/Y                                                                                                                                                                  | and B/C D     | ACs are in   | power dow    | n state.*    |               |              |         |

| Input Format Register |          |       |       |       |       |       |       |       |       |

|-----------------------|----------|-------|-------|-------|-------|-------|-------|-------|-------|

| Index                 | Mnemonic | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

| 61h                   | FMT      | FMTA3 | FMTA2 | FMTA1 | FMTA0 | FMTB3 | FMTB2 | FMTB1 | FMTB0 |

FMTA Channel A input format. See Table 3 for supported format on Channel A. The power-on default is 6 if there is an external pull-up resistor on the MRQST/MODE pin, or 9 otherwise.

FMTB Channel B input format. See Table 4 for supported format on Channel B.

| Command Register B |          |       |       |       |       |       |        |       |       |

|--------------------|----------|-------|-------|-------|-------|-------|--------|-------|-------|

| Index              | Mnemonic | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2  | bit 1 | bit 0 |

| 62h                | CMDB     | HUE8  | VSP   | HSP   | CTRAP | MONO  | BLKALL | SLT1  | SLT0  |

| VSP      | Vertica | al sync input (VBLK) polarity control.                                                                                                                            |

|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1       | vertical sync input is active low.                                                                                                                                |

|          | 0       | vertical sync input is active high.*                                                                                                                              |

| HSP      | Horizo  | ontal sync input (AV) polarity control.                                                                                                                           |

|          | 1       | horizontal sync input is active high.                                                                                                                             |

|          | 0       | horizontal sync input is active low.*                                                                                                                             |

| CTRAP    |         | na trap filter control. When enabled, the high frequency luminance signals near the subcarrier are filtered out. This function is available for NTSC output only. |

|          | 1       | enables filtering.                                                                                                                                                |

|          | 0       | disables filtering.*                                                                                                                                              |

| MONO     |         | Killer control. When enabled, the chrominance signal is suppressed. This function is ble for NTSC output only.                                                    |

|          | 1       | Color Killer enable.                                                                                                                                              |

|          | 0       | Color Killer disable.*                                                                                                                                            |

| BLKALL   | When    | set, the output from line 1 to the line set by the VBLK register is blanked.                                                                                      |