#### 4096-BIT DYNAMIC RANDOM ACCESS MEMORY

The MCM6605A is a 4096-bit high-speed dynamic Random Access Memory designed for high-performance, low-cost applications in mainframe and buffer memories and peripheral storage. Organized as 4096 one-bit words, these memories are fabricated using selective oxidation N-channel silicon gate technology to optimize device speed, power and density tradeoffs.

All address and control inputs are TTL compatible except for a single high-level clock (Chip Enable). Complete address decoding is done on chip and address latches are incorporated for ease of use. Refresh of the entire memory can be accomplished by sequentially cycling through addresses A0-A4 (32 cycles) a maximum of every 2.0 milliseconds.

The MCM6605A uses a three-transistor memory cell to simplify internal sense amplifier requirements. Output data is inverted with respect to input data. The outputs are 3-state TTL configuration and require no external sense amplifier. Outputs are in the high impedance (floating) state when either the Chip Enable is in the low state or the Chip Select is in the high state.

• Organized as 4096 Words of 1 Bit

|                            | LI, PI   | L2,P2     | L, F   |

|----------------------------|----------|-----------|--------|

| Maximum Access Time =      | 150 ns   | 200 ns    | 300 ns |

| Minimum Read Cycle Time =  | 290 ns   | 360 ns    | 470 ns |

| Minimum Write Cycle Time = | 390 ns   | 490 ns    | 590 ns |

| Minimum Read Modify Write  | Da       | taSheet4L | J.com  |

| Cycle Time =               | 390 ns . | 490 ns    | 590 ns |

- Low Power Dissipation

335 mW Typical (Active)

2.6 mW Typical (Standby with Refresh)

- Easy Refresh Only 32 Cycles Every 2.0 ms

- TTL Compatible

- 3-State Output

- Address Latches On Chip

- Power Supply Pins on Package Corners for Layout Simplification

- Typical Applications:

Main Memory

Buffer Memory

Peripheral Storage

# MOS

(N-CHANNEL, SILICON-GATE)

4096-BIT DYNAMIC RANDOM ACCESS MEMORY

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields, however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedance circuit.

#### ABSOLUTE MAXIMUM RATINGS (See Note 1)

| Rating                             | Symbol                             | Value       | Unit |

|------------------------------------|------------------------------------|-------------|------|

| Voltage on Any Pin Relative to VBB | V <sub>in</sub> , V <sub>out</sub> | -0.3 to +20 | Vdc  |

| Operating Temperature Range        | TA                                 | 0 to +70    | °C   |

| Storage Temperature Range          | T <sub>stg</sub>                   | -65 to +150 | °C   |

NOTE 1: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to RECOMMENDED OPERATING CONDITIONS. Exposure to higher than recommended voltages for extended periods of time could affect device reliability.

ataSheet4U.com

# 9

# DC OPERATING CONDITIONS AND CHARACTERISTICS

(Full operating voltage and temperature range unless otherwise noted.)

# RECOMMENDED DC OPERATING CONDITIONS (Referenced to VSS).

| Parameter                                                                                | Symbol          | Min                   | Nom  | Max                   | Unit |

|------------------------------------------------------------------------------------------|-----------------|-----------------------|------|-----------------------|------|

| Supply Voltage                                                                           | V <sub>DD</sub> | 11.4                  | 12   | 12.6                  | Vdc  |

|                                                                                          | Vcc             | 4.5                   | 5.0  | 5.5                   | Vdc  |

|                                                                                          | Vss             | 0                     | 0    | 0                     | Vdd  |

| _                                                                                        | V <sub>BB</sub> | -5.25                 | -5.0 | -4.75                 | Vdd  |

| Logic Levels Input High Voltage (A <sub>n</sub> , D <sub>in</sub> , R/W, <del>CS</del> ) | ViH             | 3.0                   | -    | V <sub>DD</sub> + 0.6 | Vde  |

| Input Low Voltage (A <sub>B</sub> , D <sub>iB</sub> , R/W, <del>CS</del> )               | VIL             | -1.0                  |      | 0.8                   | Vd   |

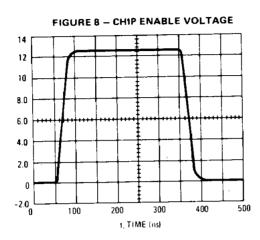

| Chip Enable High Voltage                                                                 | VCEH            | V <sub>DD</sub> - 0.6 |      | V <sub>DD</sub> + 0.6 | Vd   |

| Chip Enable Low Voltage                                                                  | VCEL            | -1.0                  | _    | 0.8                   | Vd   |

#### DC CHARACTERISTICS

et4U.c

| Characteristic                                                                                                                     | Symbol                 | Min | Тур  | Max  | Unit |

|------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|------|------|------|

| Input Current (A <sub>n</sub> , D <sub>in</sub> , R/W, <del>CS</del> , Preset)<br>(V <sub>in</sub> = 0 to V <sub>DD</sub> + 1.0 V) | lin                    | -   | _    | 10   | μА   |

| Input Chip Enable Current (V <sub>in</sub> = 0 to V <sub>DD</sub> + 1.0 V)                                                         | lice<br>DataSheet4U.co | m   | -    | 10   | μА   |

| Output High Voltage<br>(I <sub>O</sub> = -100 μA)                                                                                  | VQH                    | 2.4 | -    | Vcc  | Vdc  |

| Output Low Voltage (IO = 2.0 mA)                                                                                                   | VoL                    | ٧ss | -    | 0.45 | Vdc  |

| Output Leakage Current (VO = 0.45 V to VCC, CE = VCEL, or CS = V(H)                                                                | lLO                    |     | _    | 10   | μА   |

| Average Supply Current, Active Mode                                                                                                | <sup>I</sup> DDA       | -   | 28   | 36   | mA   |

| (Tcyc(W) = min)                                                                                                                    | CCA                    |     | 0.05 | 1.0  | mA   |

| -, -, -, -, -, -, -, -, -, -, -, -, -, -                                                                                           | <sup>1</sup> BBA       | -   | -    | 100  | μА   |

| Supply Current, Standby Mode                                                                                                       | DDS                    |     | 1.0  | 20   | Aπ   |

| (CE = 0.45 V)                                                                                                                      | ccs                    |     | -    | 10   | μА   |

|                                                                                                                                    | BBS                    |     | 1,0  | 20   | μА   |

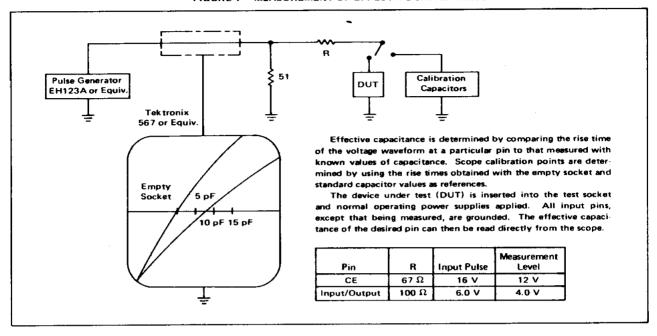

# EFFECTIVE CAPACITANCE (Test Circuit of Figure 1, full operating voltage and temperature range, periodically sampled rather than 100% tested.)

| Characteristic                               | Symbol                | Min | Тур | Max_ | Unit |

|----------------------------------------------|-----------------------|-----|-----|------|------|

| Input Capacitance (An, Din, R/W, CS, Preset) | C <sub>in(EFF)</sub>  | _   | 4.0 | 5.0  | ρF   |

| Chip Enable Capacitance                      | C <sub>CE(EFF)</sub>  |     | 25  | 30   | рF   |

| Output Capacitance                           | C <sub>out(EFF)</sub> |     | 4.0 | 5.0  | ρF   |

et4U.com

#### FIGURE 1 - MEASUREMENT OF EFFECTIVE CAPACITANCE

# AC OPERATING CONDITIONS AND CHARACTERISTICS

(Full operating voltage and temperature unless otherwise noted.)

# **OPERATING MODES**

| Mode                      | Contro | Output |                  |

|---------------------------|--------|--------|------------------|

|                           | R/W    | cs     |                  |

| Active (CE = High)        |        |        |                  |

| Read Only                 | н      | L      | Valid            |

| Read/Write                | H→L    | L      | Valid            |

| Write Only                | L      | Ļ      | Valid            |

| Read Refresh              | H→L    | L→H    | Valid → Floating |

| Refresh Only              | L      | н      | Floating         |

| Chip Disable (Unselected) | н      | н      | Floating         |

| Standby (CE = Low)        | X      | Х      | Floating         |

X = Don't Care

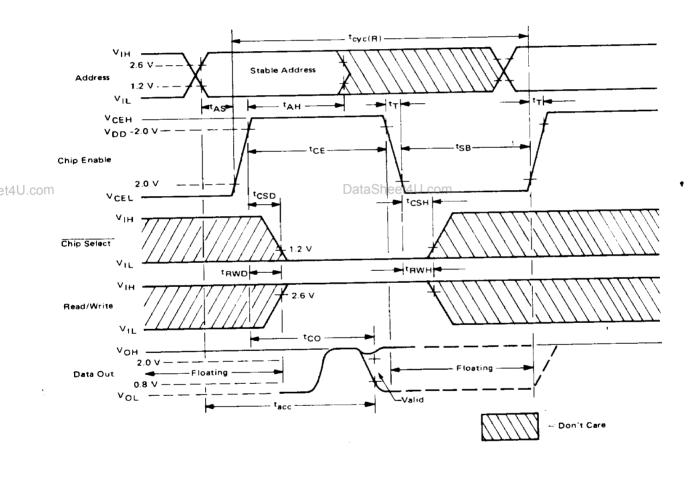

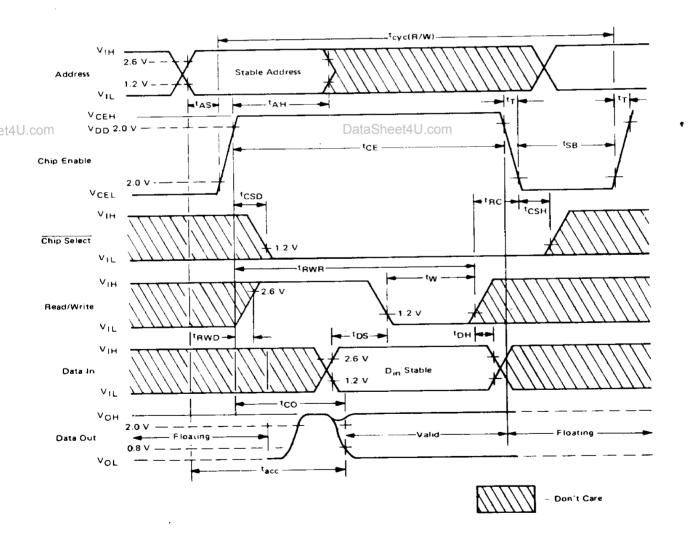

#### RECOMMENDED AC OPERATING CONDITIONS (Read, Write, and Read Modify Write Cycles)

|                         | Parameter         | Symbol           | Min | Max | Unit |

|-------------------------|-------------------|------------------|-----|-----|------|

| Address Setup Time      |                   | t <sub>AS</sub>  | 0   | -   | ns   |

| Address Hold Time       |                   | tAH              | 60  |     | ns   |

| CE Pulse Transition Tir | ne                | tŢ               | 10  | 100 | ns   |

| CE Off Time             | MCM6605AL,P/L2,P2 | tSB              | 120 | -   | ns   |

|                         | MCM6605AL1,P1     |                  | 90  |     |      |

| Chip Select Delay Time  | :                 | tCSD             |     | 70  | ns   |

| Chip Select Hold Time   |                   | <sup>t</sup> CSH | 0   | -   | ns   |

| Read Write Delay Time   |                   | tRWD             |     | 70  | ns   |

| Read Write Hold Time    |                   | tRWH.            | 0   |     | ns   |

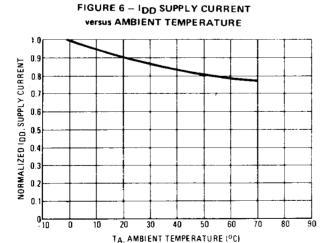

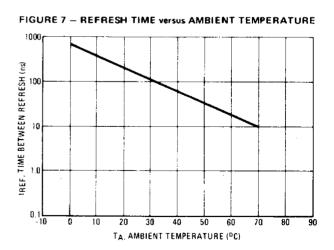

| Time Between Refresh    |                   | tREF             | I - | 2.0 | ms   |

DataSha

DataSheet4U.com

#

READ CYCLE (R/W = VIH, CS = VIL)

|                             |                     | MCM6605AL,P  |      | MCM66        | D5AL1,P1 | MCM66       | )5AL2,P2 |      |

|-----------------------------|---------------------|--------------|------|--------------|----------|-------------|----------|------|

| Characteristic              | Symbol              | Min          | Max  | Min          | Max      | Min         | Max      | Unit |

|                             | t <sub>cvc(R)</sub> | 470          | -    | 290          | _        | 360         |          | ns   |

| Read Cycle Time             | tCE                 | 310          | 2000 | 160          | 2000     | 200         | 2000     | ns   |

| Chip Enable On Time         |                     | +            | 280  | <del> </del> | 130      | -           | 180      | กร   |

| Chip Enable to Output Delay | tco_                | <del> </del> | 300  | +            | 150      | <del></del> | 200      | ns   |

| Read Access Time            | tacc t              | l            | 300  |              | 1 .50    | <u> </u>    |          | L    |

# READ CYCLE TIMING

2

DataShe

et4U.com

WRITE CYCLE (R/W =  $V_{IL}$ ,  $\overline{CS}$  =  $V_{IL}$ ) REFRESH CYCLE (R/W =  $V_{IL}$ ,  $\overline{CS}$  =  $V_{IH}$ )

|                                           | Symbol              | MCM6605AL,P |      | MCM6605AL1,P1 |      | MCM6605AL2,P2 |       |      |

|-------------------------------------------|---------------------|-------------|------|---------------|------|---------------|-------|------|

| Characteristic                            |                     | Min         | Max  | Min           | Max  | Min           | Mex   | Unit |

| Write Cycle Time                          | <sup>†</sup> cyc(W) | 590         | -    | 390           | _    | 490           | -     | ns   |

| Chip Enable On Time                       | †CE                 | 430         | 2000 | 260           | 2000 | 330           | 2000  | ns   |

| Read-Write Release Time                   | <sup>t</sup> RWR    | 410         | 2000 | 240           | 2000 | 310           | 2000  | ns   |

| Write Pulse Width                         | tw                  | 210         |      | 160           |      | 160           | 1 - 1 | ns   |

| Read-Write to Chip Enable Separation Time | <sup>t</sup> RC     | 0           | _    | 0             | _    | 0             | 1 - 1 | ns   |

| Data Delay Time*                          | tDD                 |             | 70   | _             | 70   | _             | 70    | ns   |

| Data Hold Time                            | HQ†                 | 50          | 1 -  | 20            | -    | 50            | -     | ns   |

<sup>\*</sup>If a write pulse (tw) is employed on the R/W line during a write cycle, then the input data setup time is measured from the leading edge of the write pulse. The tos time is the same as that of the read-modify-write cycle.

#### WRITE AND REFRESH CYCLE TIMING

Address V<sub>DD</sub>-2.0 V Chip Enable VCEL tCSH (Refresh) Chip Select 1.2 V VIL TRWR TRC -Read. Write **⊢**t<sub>DD</sub> ►  $^{t}DH$ Z 26 V D<sub>in</sub> Stable

DataShe

DataSheet4U.com

Read Access Time

# READ-MODIFY-WRITE (R/W = VIH→VIL, CS = VIL)

**READ REFRESH (See Note 1)** MCM6605AL,P MCM6605AL1,P1 MCM6605AL2,P2 Max Min Min Max Unit Min Symbol Characteristic 590 390 490 nş t<sub>cyc</sub>(R/W) Read-Modify-Write Cycle Time 430 2000 260 2000 330 2000 ns <sup>t</sup>CE Chip Enable On Time 410 2000 240 2000 310 2000 ns Read-Write Release Time <sup>t</sup>RWR 160 160 пs 210 tw Write Pulse Width 0 ns n 0 Data Setup Time <sup>t</sup>DS 50 20 50 <sup>t</sup>DH Data Hold Time 0 ns 0 Read-Write to Chip Enable Separation Time 0 <sup>t</sup>RC 130 180 ns 280 Chip Enable to Output Delay tco

tacc

Note 1: A read refresh cycle is possible by bringing ES high after output data is valid and then bringing R/W low to the write position.

#### READ MODIFY WRITE TIMING

300

150

200

ns

2

DataShe

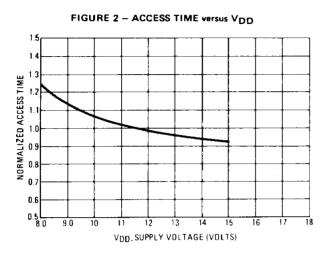

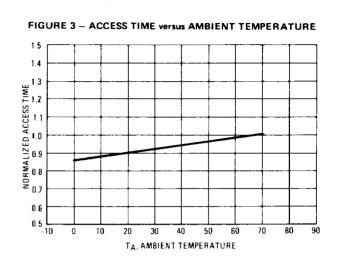

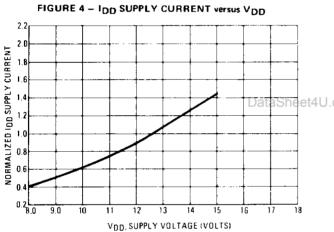

# TYPICAL CHARACTERISTICS CURVES

2

et4U.com

www.DataSheet4U.com

DataShe

DataSheet4U.com

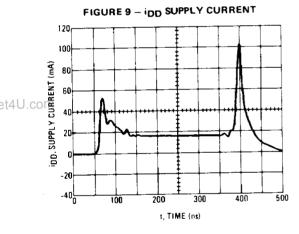

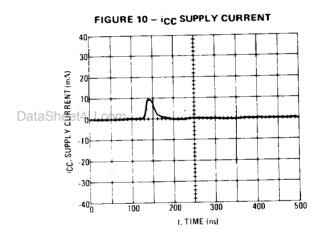

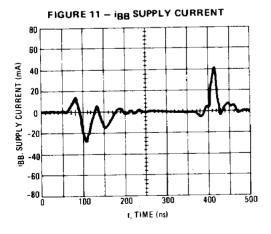

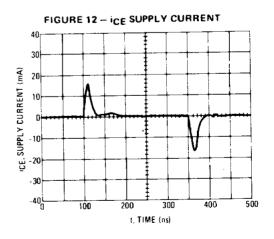

# TYPICAL SUPPLY CURRENT TRANSIENT WAVEFORMS

L

DataShe

DataSheet4U.com

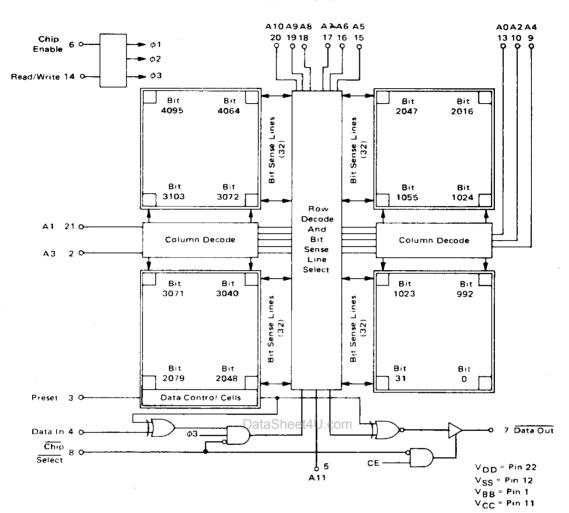

#### **BLOCK DIAGRAM**

t4U.com

DataShe

# **FUNCTIONAL DESCRIPTION**

The MCM6605A 4096-bit dynamic RAM uses a three transistor storage cell in an inverting cell configuration. The single high-level clock (Chip Enable) starts an internal three-phase clock generator which controls the read and write functions of the device. The  $\phi1$  signal, which is high when CE is low (standby mode), preconditions the nodes in the dynamic RAM in preparation for a memory cycle. The  $\phi2$  signal, which comes on as CE goes high, is the read control and transfers data from storage onto bit sense lines. The  $\phi3$  signal, which comes after  $\phi2$  only during a write or refresh cycle, transfers data from the bit sense lines back into storage. The  $\phi3$  signal occurs only if the R/W input is low.

To perform a read cycle, CE is brought high to initiate a  $\phi 2$  signal and latch the input addresses. The column decoders select one column in each of the four storage quadrants (see the block diagram) and transfers data from storage onto the 128 bit sense lines. The row

decoder selects one of these 128 bit sense lines for read and write operations. During the  $\phi 2$  signal, the data on this selected bit sense line is Exclusive ORed with the state of the appropriate data control cell to supply the correct output data. After this data is received by the external system, CE may be brought low to the standby position. This assumes that the R/W signal is held high to prevent an internal  $\phi 3$  being generated.

To perform a write or refresh operation, CE is brought high and everything is identical to a read operation up until the 128 bit sense lines are charged with the selected columns of stored data. When R/W is brought low (if it is not already there), a  $\phi$ 3 signal is generated after  $\phi$ 2 is over. The  $\phi$ 3 signal takes the data from the 128 bit sense lines and returns it to the 128 storage locations it came from. Because of the design of the memory array, this  $\phi$ 2- $\phi$ 3, read-write operation inverts the data. Therefore, one extra row of memory cells, called data control cells, is used to

DataShe

## MCM6605A

keep track of the polarity of stored data in order to be able to correctly recover it. During the write operation, the input data is Exclusive ORed with these control cells before being stored in the array. A refresh cycle does not modify any of the bit sense lines, but simply returns the data (now inverted) into storage.

All timing signals for the MCM6605A are specified around these operations. The following is a brief description of the input pins and relevant timing requirements.

Chip Enable - CE is a single high level clock which initiates all memory cycles. CE can remain low as long as desired for specific applications as long as the 2.0 ms refresh requirements are met.

Chip Select - This signal controls only the I/O buffers. When CS is high, the input is disconnected and the output is in the 3-state high-impedance state. A refresh cycle is, therefore, a write cycle with  $\overline{\text{CS}}$  high.  $\overline{\text{CS}}$  has no critical timing with respect to any other signal except that there is a finite delay between activation and data out.

Read/Write - When high, R/W inhibits the internal  $\phi$ 3 signal, thereby keeping the memory from writing. When R/W is low, a  $\phi$ 3 will occur soon after  $\phi$ 2 is finished. For a read cycle, R/W should be high within tRWD of CE to insure that a \$\phi 3\$ does not start. The only timing requirement on the R/W input for writing is a minimum write pulse defined as the overlap of CS, CE, and R/W. Refresh cycles require that  $\overline{\text{CS}}$  be high to inhibit the input buffer before a \$\phi 3 occurs. Thus \$\overline{CS}\$ should be high within tCSD for a refresh cycle, or before R/W goes low for a readrefresh cycle.

et4U.co Data In – The input data must be valid for a sufficient DataS time to override the data stored on the selected bit sense line. It must remain valid for the "write pulse" defined under Read/Write. Signals on the Din pin are ignored when either CS or R/W is high, or CE is low.

> Data Out - Output data is inverted from input data and is valid tacc after CE goes high. The data will remain valid as long as CE is high and CS remains low. With either CE low or  $\overline{CS}$  high, the output is in a high-impedance state. The data output is initially precharged high when CE goes high and is then either discharged to ground or left high depending on the stored data. This precharging followed by valid data occurs regardless of the state of the R/W input, making the write cycle actually a read-write cycle. The output will also try to precharge during a refresh cycle but will be kept at high impedance by the CS being high. If  $\overline{CS}$  is originally low and is then brought high (within the tCSD specification) the output may start to precharge before being cut off and returned to high impedance.

> Addresses - The addresses are latched when CE goes high, and may be removed after an appropriate hold time.

Vss - Circuit ground.

VBB - The reverse bias substrate supply. Forward biasing this supply with respect to VSS will destroy the memory

**VDD** - Positive supply voltage.

VCC - Output buffer supply. This supply goes only to the data output buffer and draws current only when driving an output load high.

Preset - This pin should be tied to ground. During device testing Preset can be used to preset the data control cells to a logic zero. One 200 ns, 12 V pulse will set all 32 cells simultaneously. Preset has no system use; its only purpose is to ensure a good logic level in the control cells after first power up. In system use, this good logic level will come naturally after the first few refresh cycles.

#### APPLICATIONS INFORMATION

#### **Power Supplies**

The MCM6605A is a dynamic RAM which has essentially zero power drain when in the standby (CE low) mode. When operating, the VDD supply may experience transients in the order of 100 mA for a short time (Figure 9). The VBB supply, which has very low dc drain while operating. may see transients of about 40 mA during the edges of CE. Therefore, appropriate bypassing of both supplies is recommended. This bypassing has been simplified by the location of the power supply pins on the corners of the package.

The VCC line supplies only the input leakage of a TTL load on Data Out and should never exceed about 100 µA, presenting little bypassing requirement.

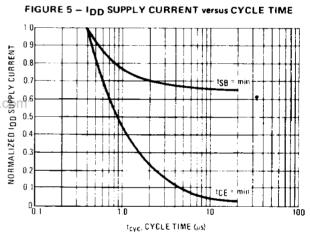

Power dissipation for a system of N chips is much lower than N times the 335 mW typical dissipation for a full speed operating chip. This is because the unselected rows in a memory array card are operating in the standby mode of near zero dissipation. This zero standby power is actually unachievable because of the requirements for Therefore, power dissipation for an array of N X M chips operating at t1 cycle time, tREF refresh increment, and maximum CE down time between cycles is:

$$P_D \approx M \left( \frac{490 \text{ ns}}{t_1 \text{ ns}} \right) 335 \text{ mW} + (N-1) (M) \left( \frac{15.7}{t_R EF \mu s} \right) 335 \text{ mW}$$

For a 550-ns-cycle-time, 64 k by 16 system (16 by 16 chip array) with refresh at 2.0 ms, the approximate power

$$P_D \approx 16 \left(\frac{490}{550}\right) 335 + (15) (16) \left(\frac{15.7}{2000}\right) 335$$

$$\approx 4775 \text{ mW} + 630 \text{ mW} = 5.4 \text{ W}$$

A similar one megabyte system, eight bytes wide, would have a dissipation of only 24 W. If the low standby power capability were not used, over 600 W would be dissipated.

#### Refresh

The MCM6605A is refreshed by performing a refresh (or write) cycle on each of the 32 combinations of the least significant address bits (A0-A4) within a 2.0 ms time period. (A5-A11 must remain constant at proper logic levels.) This refresh can be done in a burst mode (32 cycles starting every 2.0 ms) or in a distributed mode where one cycle is done every 62.5 µs.

A refresh abort can be accomplished by treating a refresh cycle as a read-modify-write cycle with  $\overline{CS}$  high. This type of cycle can be aborted any time until the R/W signal has been brought low to allow a  $\phi 3$  clock to begin.

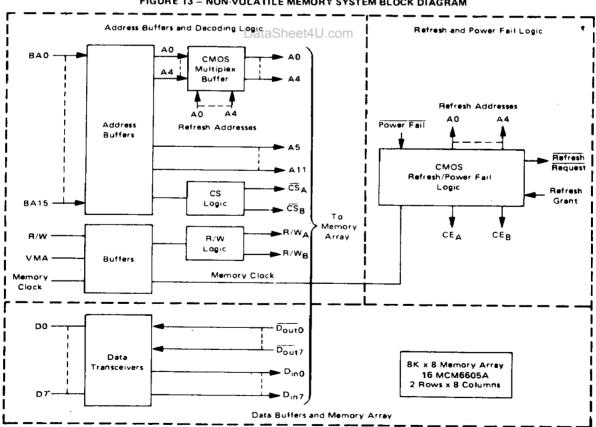

#### Non-Volatile Storage

In many digital systems, it is extremely important to retain data during emergencies such as power failure. Unfortunately, however, most random access read/write semiconductor memories such as the MCM6605A are volatile. That is, if power is removed from the semiconductor memory, stored information is lost. Therefore, non-volatility for a specified period of time becomes highly desirable — as a necessity to maintain irreplaceable information or as a convenience to avoid the time consuming and troublesome task of having to reload the memory.

The extremely low standby power dissipation of the MCM6605A makes it ideal for main memory applications requiring battery backup for non-volatility. For example, the MCM6605A can be employed in an 8K byte non-volatile main memory system application for microprocessors. The memory system can be partitioned into three major sections as illustrated in Figure 13. The first section contains the address buffers and the Read/Write and Chip Select decoding logic. The second section consists of the

data bus buffering transceivers and the memory array (which consists of 16 MCM6605As) organized into two rows of 4K bytes each.

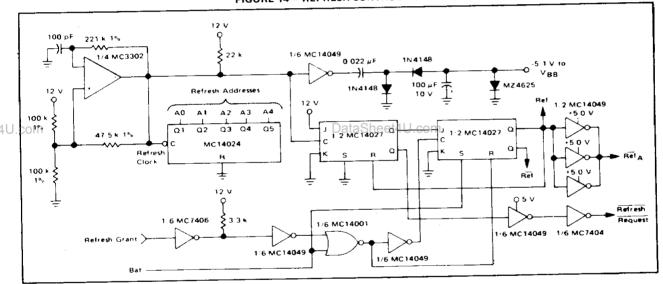

The third section of the block diagram comprises refresh and control logic for the memory system. This logic interfaces the timing of the refresh handshaking with the microprocessor (MPU) clock circuitry. It handles requests for refresh, the generation of refresh addresses, the synchronization of a Power Fail signal, the multiplexing of the external Memory Clock with the internal clock (used during standby), and the generation of a -5 V supply on the board using a charge-pump method.

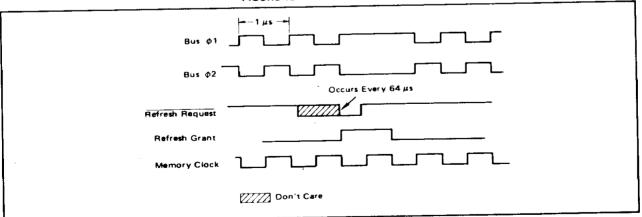

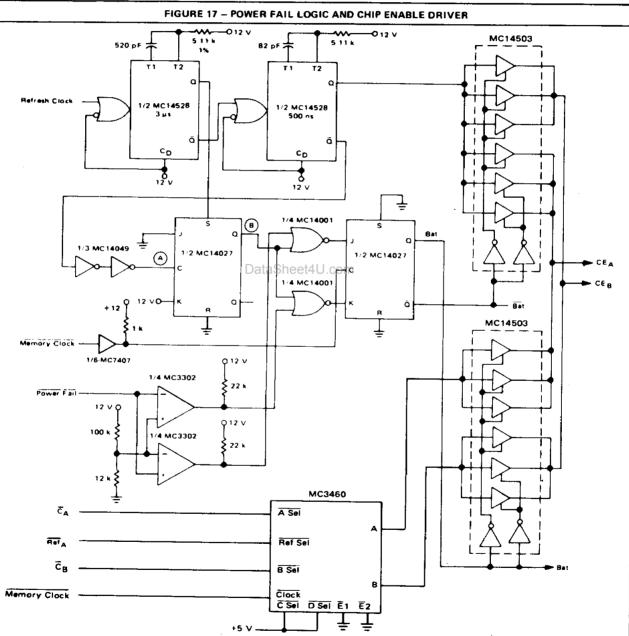

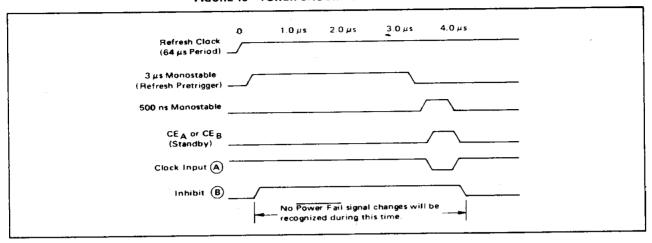

The refresh control logic is illustrated in Figure 14. It handles the refreshing of the memory during both operating and standby modes. The timing for this logic is given in Figure 15. Figure 16 gives the memory timing for the standby mode only. Decoding of the memory clock (CEA and CEB) and the circuitry to synchronize the Power Fail signal are shown in Figure 17, with the timing given in Figure 18.

The memory device clock (CEA and CEB) during standby is created by a monostable multivibrator (MC14528) and buffered from the memory array by three MC14503 buffers in parallel. This clock is multiplexed with the Memory Clock by use of the three-state feature of the

FIGURE 13 - NON-VOLATILE MEMORY SYSTEM BLOCK DIAGRAM

2

MC14503. The Memory Clock (used during normal operation) is translated to 12 V levels by use of an MC3460 Clock Driver. Decoding of the CEA and CEB signals (i.e., clocking only the memory bank addressed) to conserve power is accomplished by the logic within the MC3460.

Since the Power Fail signal will occur asynchronously with both the Memory Clock and the refreshing operation (Refresh Clock), it is necessary to synchronize the Power Fail signal to the rest of the system in order to avoid aborting a memory access cycle or a refresh cycle. An MC14027 dual flip-flop is used as the basic synchronization device. The leading edge of the Refresh Clock triggers a 3 µs monostable multivibrator which is used as a refresh pretrigger. The trailing edge of this pretrigger triggers a 500 ns monostable which creates the CE pulse during standby operation. The 3 µs pretrigger signal is used to set half of the MC14027 flip-flop, the output of which, (B), then inhibits a changeover from the standby to the operating modes (or vice versa). This logic prevents the system from aborting a refresh cycle should the Power

Fail signal change states just prior to or during a refresh cycle. The trailing edge of the 500 ns monostable clears the MC14027flip-flop, enabling the second flip-flop in the package. The state of Power Fail and Power Fail is applied to the K and J inputs of this second flip-flop and is synchronized by clocking with Memory Clock. The outputs of this flip-flop, labeled Bat and Bat, lock the system into the refresh mode and multiplex in the internal clock for standby operation when Bat = "1". The voltage to logic not required for the refresh only mode of operation is removed to conserve power.

By using CMOS for the refresh logic and capacitance drivers, and a low current refresh oscillator, the standby current required for the 8K byte system is extremely small, as noted in Table 1. This low standby current requirement can be easily supplied for several days with standard type +12 V batteries. For more detailed information on this sytem and a large mainframe memory system, see Application Notes AN-732 and AN-740.

FIGURE 14 - REFRESH CONTROL LOGIC

FIGURE 15 - REFRESH TIMING

FIGURE 16 – MEMORY TIMING IN STANDBY MODE

0 32 µs 64 µs

Refresh Clock

A = First 4K Byte

B = Second 4K Byte

CE<sub>A</sub>, CE<sub>B</sub>

Refresh Address Counter Incremented

CS<sub>A</sub>, CS<sub>B</sub> "1"

R/W<sub>A</sub>, R/W<sub>B</sub> "0"

et4U.com

www.DataSheet4U.com

DataShe

FIGURE 18 - POWER UP/DOWN SYNCHRONIZATION

TABLE 1 - STANDBY MODE CURRENT ALLOCATION

| Circuit Section                       | Typical Current |

|---------------------------------------|-----------------|

| +12 V Current (VDD) for 16 MCM6605A's | 5 mA            |

| Charge Pump                           | 3 mA            |

| Comparator                            | 2 mA            |

| Capacitance Drivers                   | 4 mA            |

| Total                                 | 14 mA           |

Circuit diagrams utilizing Motorola products are included as a means of illustrating typical semiconductor applications, consequently, complete information sufficient for construction purposes is not necessarily given. The information has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described any license under the patent rights of Motorola Inc. or others.

et4U.com

DataSheet4U.com