HIGH-OUTPUT-CURRENT OPERATIONAL AMPLIFIER  $|A_{VCL} \ge 5|$

# Precision Monolithics Inc

## **FEATURES**

| • | Open-Loop Gain              | 10,000. | 000V/V Min |

|---|-----------------------------|---------|------------|

|   | Low Input Offset Voltage    |         |            |

| • | Low Input Bias Current      |         | 5nA Max    |

|   | Excellent TCV <sub>OS</sub> |         |            |

|   | High CMRR                   |         |            |

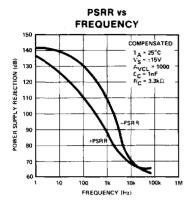

|   | High PSRR                   |         |            |

|   | Low Noise 5.5n\             |         |            |

|   | 4.5n\                       |         |            |

| • | High Output Current         |         | ±50mA      |

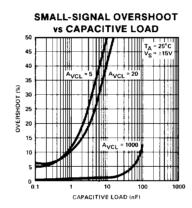

- Drives Capacitive Loads up to 10nF

- On-Board Thermal Shutdown Circuit

- Available in Die Form

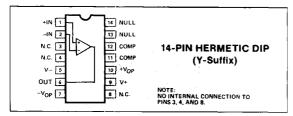

## **PIN CONNECTIONS**

## ORDERING INFORMATION†

| T <sub>A</sub> = 25°C       | PACKAGE          | OPERATING            |

|-----------------------------|------------------|----------------------|

| V <sub>OS</sub> MAX<br>(μV) | CERDIP<br>14-PIN | TEMPERATURE<br>RANGE |

| 25                          | OP-50AY*         | MIL                  |

| 100                         | OP-50BY*         | MIL                  |

| 25                          | OP-50EY          | IND                  |

| 100                         | OP-50FY          | IND                  |

- For devices processed in total compliance to MIL-STD-883, add /883 after part number. Consult factory for 883 data sheet.

- Burn-in is available on commercial and industrial temperature range parts in CerDIP, plastic DIP, and TO-can packages. For ordering information, see 1990/91 Data Book, Section 2.

## **GENERAL DESCRIPTION**

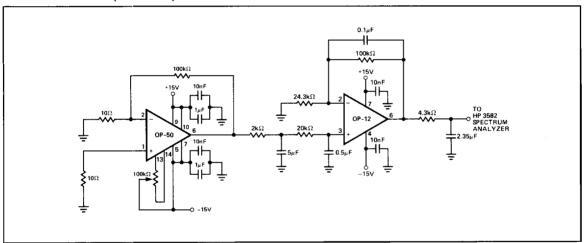

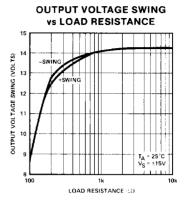

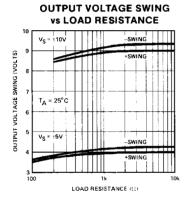

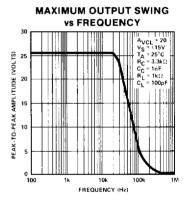

The OP-50 eliminates the need for an output buffer in applications which require high load-driving capability coupled with premium amplifier performance. The output stage can drive  $\pm 50 \text{mA}$  into  $50 \Omega$  loads. In addition, the output is stable with capacitive loads of up to 10nF. This load driving ability makes the OP-50 ideal for amplifying small signals for transmission through long cables. The amplifier features open-loop voltage gain of over 10 million with common-mode rejection and power supply rejection of greater than 126dB (A/E grades).

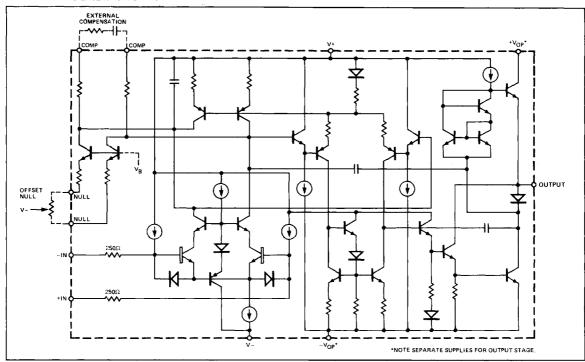

## SIMPLIFIED SCHEMATIC

OPERATIONAL AMPLIFIERS/BUFFERS

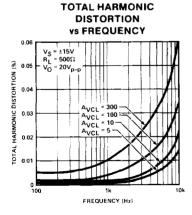

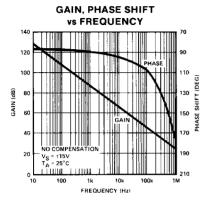

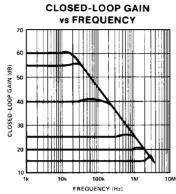

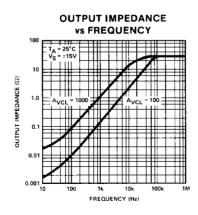

The OP-50 is stable for closed-loop gains above 50, and can be externally compensated for closed-loop gains in the range of 5 to 50. The amplifier is designed for use in high-gain and/or high-output-current applications. For example, an OP-07 coupled with an output buffer can be replaced by a single OP-50 amplifier.

Ion-implanted superbeta transistors, combined with a patented input bias current cancellation circuit, provide an input bias current of only 5nA and input offset current of 1nA. Over the full military temperature range, input bias current and input offset current for an A-grade device does not exceed 8nA and 3nA, respectively. Input offset voltages are trimmed to a maximum of 25µV (A/E grades) and 100µV (B/F grades) using PMI's zener-zapping technique. This low offset eliminates the need for an offset trimpot in most applications.

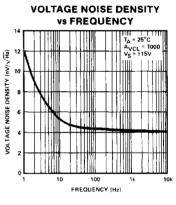

Low voltage-noise, typically 4.5nV/ $\sqrt{\text{Hz}}$  at 1kHz, is achieved in the OP-50 with minimum sacrifice of input protection. Overload protection is provided by input resistors of 250 $\Omega$  and emitter-base diodes. The input resistors provide current limit protection against differential inputs of up to  $\pm$ 10V; and the diodes prevent avalanche breakdown which could degrade the I<sub>B</sub>, I<sub>OS</sub>, and matching of the input stage transistors. External resistors can be added to the input to guard against higher input voltages; however, the added resistors will degrade noise voltage performance. When minimum noise voltage is required, source resistance should be kept below a few hundred ohms.

Separate output-stage power supply pins are provided on the OP-50 to allow control of device power dissipation and output voltage swing. The maximum voltage which may be applied across the power supply pins is ±18V. The guaranteed specifications are based on operating both stages at ±15V; however, there is minimal effect on DC performance when the main amplifier is operated at ±15V and the output stage is operated at a reduced voltage. When operating both the main amplifier and the output stage at the same voltages, the corresponding power supply pins may be tied together. Decoupling capacitors are recommended between the power supply pins and analog ground. It is necessary to use decoupling capacitors on each power supply pin when operating the output stage at supply voltages less than the amplifier supply voltage. Do not operate the output-stage negative power supply pin at a more negative voltage than the negative supply pin (V-).

A thermally-symmetric die layout, which differs from other op amp designs by the positioning of more devices along the center line, provides the OP-50 with a thermal drift of less than  $0.3\mu\text{V}/^{\circ}\text{C}$ . This layout feature is critical to the maintenance of high open-loop gain when driving large-current loads and dissipating hundreds of milliwatts in the device. The use of a heatsink is recommended to reduce internal temperature rise when operating at high output power levels. The use of standard dual-in-line package heatsinks will help to dissipate heat to the environment. Other techniques, such as the use of external voltage-dropping resistors, allow heat to be dissipated **outside** of the package. See Figure 5, "Driving 50 $\Omega$  Loads", in the applications section.

A thermal-shutdown circuit protects the OP-50 from overdissipation. When the die temperature reaches approximately 165°C, the output stage automatically shuts down. The amplifier input stage remains fully operational, thereby protecting the signal source from any loading changes caused by a complete shutdown.

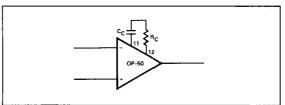

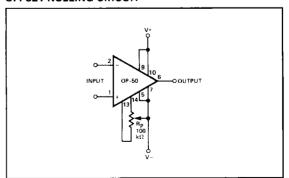

#### **COMPENSATION FOR GAINS BETWEEN 5 AND 50**

The OP-50 can be compensated for inverting gains between 5 and 50 using a series resistor and capacitor. These values can be adjusted to minimize overshoot for a given application. The recommended compensation is:

| GAIN RANGE                | R <sub>C</sub>           | c <sub>c</sub> |  |  |

|---------------------------|--------------------------|----------------|--|--|

| 5 ≤ A <sub>VCL</sub> ≤ 20 | 560Ω                     | 4.7nF          |  |  |

| $20 \le A_{VCL} \le 50$   | 3.3kΩ                    | 1nF            |  |  |

| A <sub>VCL</sub> ≥ 50     | No compensation required |                |  |  |

### COMPENSATION

#### **ABSOLUTE MAXIMUM RATINGS (Note 1)**

| Supply Voltage (Note 2)    |                          |                 | ±18V       |

|----------------------------|--------------------------|-----------------|------------|

| Input Voltage              |                          | Supp            | ly Voltage |

| Differential Input Voltage |                          |                 |            |

| Differential Input Curren  |                          |                 |            |

| Output Short-Circuit Du    |                          |                 |            |

| Storage Temperature R      |                          |                 |            |

| Operating Temperature      | _                        |                 |            |

| OP-50A, B                  |                          | 55°C            | to +125°C  |

| OP-50E, F                  |                          |                 |            |

| Lead Temperature (Solo     | dering, 60 sec)          |                 | 300°C      |

| Junction Temperature (     | •                        |                 |            |

| PACKAGE TYPE               | Θ <sub>JA</sub> (NOTE 4) | e <sub>ic</sub> | UNITS      |

| 14-Pin Hermetic DIP (Y)    | 99                       | 12              | °C/W       |

#### NOTES:

- Absolute ratings apply to both DICE and packaged parts, unless otherwise noted.

- Supply voltage rating applies to all power supply pins. No device pins should be connected to a voltage more negative than the supply to V-, pin 5.

- The OP-50's inputs are protected by 250Ω series resistors and protection diodes. If the differential input voltage exceeds ±10V, the input current must be limited to ±20mA.

- Θ<sub>|A</sub> is specified for worst case mounting conditions, i.e., Θ<sub>|A</sub> is specified for device in socket for CerDIP package.

**ELECTRICAL CHARACTERISTICS** at V+ =  $+V_{OP}$  = +15V,  $V- = -V_{OP}$  = -15V,  $T_A$  =  $25^{\circ}C$ , no compensation, unless otherwise noted.

|                                       |                   |                                                                                     |              | P-50A/        | E                |                                        | P-50B         | 'F         |                   |

|---------------------------------------|-------------------|-------------------------------------------------------------------------------------|--------------|---------------|------------------|----------------------------------------|---------------|------------|-------------------|

| PARAMETER                             | SYMBOL            | CONDITIONS                                                                          | MIN          | TYP           | MAX              | MIN                                    | TYP           | MAX        | UNITS             |

| Input Offset Voltage                  | V <sub>OS</sub>   |                                                                                     |              | 10            | 25               | _                                      | 50            | 100        | μ۷                |

| Input Bias Current                    | I <sub>B</sub>    |                                                                                     |              | ±1            | ±5               |                                        | ±1            | ±10        | nA                |

| Input Offset Current                  | los               |                                                                                     | _            | 0.1           | 1                | rae.                                   | 0.1           | 3          | nA                |

| Input Voltage Range                   | IVR               | CMRR ≥ 100dB                                                                        | ±12          |               | -                | ±12                                    |               |            | V                 |

| Output Voltage Swing                  | v <sub>o</sub>    | $R_L \ge 500\Omega$<br>$R_L \ge 50\Omega$ (Note 1)                                  | ±13<br>=2.5  | ±13.4<br>±4.0 | -                | ±13<br>±2.5                            | ±13.4<br>±4.0 |            | V                 |

| Output Voltage Swing                  | v <sub>o</sub>    | $V + = +V_{OP} = +5V,$ $V - = -V_{OP} = -5V$ $R_{L} = 500\Omega$ $R_{L} = 50\Omega$ | ±3.5<br>±2.5 | ±3.8<br>±2.8  |                  | ±3.5<br>±2.5                           | ±3.8<br>±2.8  | -          | V                 |

| Slew Rate                             | SR                | $R_L \ge 2k\Omega$ $R_C = 560\Omega$ $C_C = 4.7nF$                                  | 2.5          | 3.0           |                  | 2.5                                    | 3.0           | -          | V/μs              |

| Common-Mode<br>Rejection Ratio        | CMRR              | V <sub>CM</sub> = ±10V                                                              | 126          | 140           | -                | 110                                    | 120           | . —        | dB                |

| Power Supply Rejection Ratio          | PSRR              | V <sub>S</sub> = ±5V to ±15V                                                        | _            | 0.1           | 0.5              | *-                                     | 0.5           | 1          | μV/V              |

| Large-Signal<br>Voltage Gain          | A <sub>vo</sub>   | $V_C = \pm 10V$ , $R_L \approx 1k\Omega$                                            | 10           | 50            | _                | 7.5                                    | 15            | ener.      | V/μV              |

| Gain-Bandwidth Product                | GBW               | A <sub>VCL</sub> = 50 (Note 2)                                                      | 15           | 25            | -                | 15                                     | 25            |            | MHz               |

| Offset Voltage<br>Range Adjust        |                   | $R_{\rm P}$ = 100k $\Omega$                                                         | ±1.0         | ±2.5          |                  | ≡1.0                                   | ±2.5          |            | mV                |

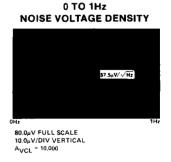

| Input Noise Voltage                   | e <sub>np-p</sub> | f = 0.1Hz to 10Hz                                                                   | _            | 0.12          | -                | _                                      | 0.12          |            | μV <sub>p-p</sub> |

| Noise Voltage Density                 | en                | f = 10Hz<br>f = 1kHz (Note 3)                                                       |              | 5.5<br>4.5    | 8.5<br>6.0       | ************************************** | 5.5<br>4.5    | 8.5<br>6.0 | nV/√Hz            |

| Noise Current                         | inp-p             | f = 0.1Hz to 10Hz                                                                   |              | 2             | ~                |                                        | 2             |            | рА <sub>р-р</sub> |

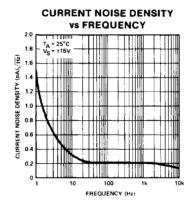

| Noise Current Density                 | in                | f = 100Hz<br>- f = 1kHz                                                             | _            | 0.3<br>0.23   | ~                | _                                      | 0.3<br>0.23   | _          | pA/√Hz            |

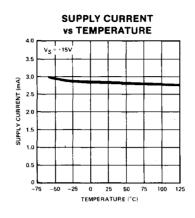

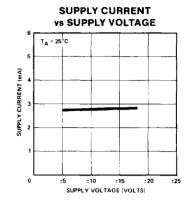

| Quiescent Supply Current              | I <sub>SY</sub>   | No Load                                                                             |              | 2.6           | 3.3              |                                        | 2.6           | 3.3        | mA                |

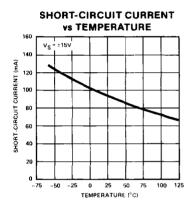

| Positive Current Limit                | +lsc              | Output shorted to Ground                                                            | 60           | 95            | 120              | 60                                     | 95            | 120        | mA                |

| Negative Current Limit                | -I <sub>sc</sub>  | Output shorted to Ground                                                            | 60           | 85            | 120              | 60                                     | 85            | 120        | mA                |

| Differential-Mode<br>Input Resistance | R <sub>IND</sub>  |                                                                                     |              | 2             | w <sub>e</sub> . | _                                      | 2             | _          | МΩ                |

| Common-Mode<br>Input Resistance       | R <sub>INOM</sub> |                                                                                     |              | 20            | -                | _                                      | 20            |            | Gn                |

| Capacitive Load Capability            | CL                | $A_{VCL} \ge 5$<br>$R_C = 560\Omega$ (Note 2)<br>$C_C = 4.7nF$                      | 10           | _             |                  | 10                                     |               |            | nF                |

| Settling-Time                         | ts                | Settling to 0.01%, $V_O = 20V_{p-p}$<br>$A_{VCL} = 500$<br>$A_{VCL} = 1000$         | _            | 30<br>60      | ~                | -                                      | 30<br>60      | _          | μs                |

#### NOTES:

- 1. Guaranteed by current limit tests.

- 2. Guaranteed by design.

- 3. Sample tested.

**ELECTRICAL CHARACTERISTICS** at V+ = +V $_{OP}$  = +15V, V- = -V $_{OP}$  = -15V, -25°C  $\leq$  T $_{A}$   $\leq$  +85°C, no compensation, unless otherwise noted.

|                                 |                 |                                                    |       | OP-50E |      | -:    | OP-50 |      |            |

|---------------------------------|-----------------|----------------------------------------------------|-------|--------|------|-------|-------|------|------------|

| PARAMETER                       | SYMBOL          | CONDITIONS                                         | MIN   | TYP    | MAX  | MIN   | TYP   | MAX  | UNITS      |

| Input Offset Voltage            | Vos             |                                                    | _     | 20     | 45   |       | 50    | 150  | μV         |

| Input Offset<br>Voltage Drift   | TCVos           | (Note 1)                                           | _     | 0.15   | 0.3  |       | 0.3   | 1    | μV/°C      |

| Input Bias Current              | I <sub>B</sub>  |                                                    | _     | ±2     | ±7   |       | ±:2   | ±25  | nA         |

| Input Offset Current            | los             |                                                    |       | 0.2    | 2.5  | ****  | 0.2   | 20   | n <b>A</b> |

| Input Offset<br>Current Drift   | TCIos           |                                                    |       | 3      |      | _     | 5     |      | pA/°C      |

| Input Bias<br>Current Drift     | TCIB            |                                                    |       | 20     | _    |       | 50    | _    | pA/°C      |

| Input Voltage Range             | IVR             | CMRR ≥ 100dB                                       | ±11.5 |        |      | ±11.5 | _     |      | V          |

| Output Voltage Swing            | V <sub>O</sub>  | R <sub>L</sub> ≥ 500Ω                              | ±12   | ±13.4  | -    | ±12   | ±13.4 |      | V          |

| Common-Mode<br>Rejection Ratio  | CMRR            | V <sub>CM</sub> = ±10V                             | 120   | 130    |      | 105   | 120   | · _  | dB         |

| Power Supply<br>Rejection Ratio | PSRR            | V <sub>S</sub> = ±5V to ±15V                       |       | 0.5    | 1.25 |       | 0.5   | 1.25 | μV/V       |

| Quiescent Supply<br>Current     | I <sub>SY</sub> | No Load                                            | _     | 2.8    | 4    |       | 2.8   | 4    | mA         |

| Open-Loop Gain                  | Avo             | $V_{OUT} = \pm 10V$ , (Note 2)<br>$R_L = 1k\Omega$ | 4     | 15     | _    | 4     | 15    | _    | V/μV       |

#### NOTES:

**ELECTRICAL CHARACTERISTICS** at V+ = +V<sub>OP</sub> = +15V, V- = -V<sub>OP</sub> = -15V, -55°C  $\leq$  T<sub>A</sub>  $\leq$  +125°C, no compensation, unless otherwise noted.

|                                 |                   |                                                |       | OP-50/ | \    |       | OP-50E | }    |        |

|---------------------------------|-------------------|------------------------------------------------|-------|--------|------|-------|--------|------|--------|

| PARAMETER                       | SYMBOL            | CONDITIONS                                     | MIN   | TYP    | MAX  | MIN   | TYP    | MAX  | UNITS  |

| Input Offset Voltage            | V <sub>OS</sub>   |                                                | _     | 20     | 55   | _     | 50     | 200  | μV     |

| Input Offset<br>Voltage Drift   | TCV <sub>OS</sub> |                                                | _     | 0.15   | 0.3  |       | 0.3    | 1    | μV/°C  |

| Input Bias Current              | l <sub>B</sub>    |                                                | _     | ±2     | ±8   | _     | ±.2    | ±20  | nA     |

| Input Offset Current            | los               |                                                | _     | 0.5    | 3    |       | 0.5    | 12   | nA     |

| Input Offset<br>Current Drift   | TCIOS             |                                                | _     | 3      | _    |       | 5      |      | pA/°C  |

| Input Blas<br>Current Drift     | TCIB              |                                                | _     | 20     | _    | _     | 50     |      | pA/°C  |

| Input Voltage Range             | IVR               | CMRR ≥ 100dB                                   | ±11.5 |        |      | ±11.5 | _      |      | V      |

| Output Voltage Swing            | v <sub>o</sub>    | $R_L \ge 500\Omega$                            | ±12   | ±13.2  | -    | ±12   | ±13.2  |      | V      |

| Common-Mode<br>Rejection Ratio  | CMRR              | V <sub>CM</sub> = ±10V                         | 120   | 130    | _    | 105   | 120    | _    | dB     |

| Power Supply<br>Rejection Ratio | PSRR              | V <sub>S</sub> = ±5V to ±15V                   | _     | 0.5    | 1.25 |       | 0.5    | 1.25 | μV/V   |

| Quiescent Supply<br>Current     | I <sub>SY</sub>   | No Load                                        | _     | 2.8    | 4    |       | 2.8    | 4    | mA     |

| Open-Loop Gain                  | A <sub>vo</sub>   | $V_0 = \pm 10V$ ,<br>$R_L = 1k\Omega$ (Note 1) | 4     | 10     | _    | 4     | 10     |      | · V/μV |

#### NOTE:

<sup>1.</sup>  $TCV_{OS}$  tested on E grade, guaranteed by design on F grade specification

<sup>2.</sup> Guaranteed by design.

<sup>1.</sup> Tested at +125°C, guaranteed by design at -55°C.

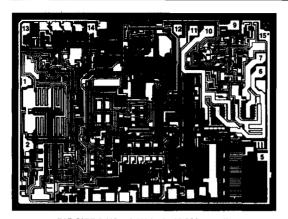

## **DICE CHARACTERISTICS**

DIE SIZE 0.149  $\times$  0.111 inch, 16,539 sq. mils (3.78  $\times$  2.82 mm, 10.66 sq. mm)

- 1. NONINVERTING INPUT

- 2. INVERTING INPUT

- 5. V-

- 6. OUTPUT

- 7. -V<sub>OP</sub> 9. V+

- 10. +V<sub>OP</sub>

- 11. COMPENSATION

- 12. COMPENSATION

- 13. NULL

- 14. NULL

- 15. V- (OPTIONAL BONDING PAD)\*

For additional DICE ordering information, refer to 1990/91 Data Book, Section 2.

**WAFER TEST LIMITS** at  $V+=+V_{OP}=+15V$ ,  $V-=-V_{OP}=-15V$ ,  $T_A=25^{\circ}C$ , no compensation, unless otherwise noted.

| PARAMETER                       | SYMBOL           | CONDITIONS                                                       | OP-50G       | UNITS    |

|---------------------------------|------------------|------------------------------------------------------------------|--------------|----------|

| Input Offset Voltage            | v <sub>os</sub>  |                                                                  | 100          | μV MAX   |

| Input Bias Current              | I <sub>B</sub>   |                                                                  | +10          | nA MAX   |

| Input Offset Current            | los              |                                                                  | 3            | nA MAX   |

| Output Voltage Swing            | v <sub>o</sub>   | $R_L \geq 500\Omega$                                             | ±13          | V MIN    |

| Output Voltage Swing            | $v_{o}$          | $V+=+V_{OP}=+5V,\ V-=-V_{OP}=-5V$ $R_L=500\Omega$ $R_L=50\Omega$ | ±3.5<br>±2.5 | VMIN     |

| Common-Mode<br>Rejection Ratio  | CMRR             | V <sub>CM</sub> = ±10V                                           | 110          | dB MIN   |

| Power Supply<br>Rejection Ratio | PSRR             | V <sub>S</sub> = ±5V to ±15V                                     | 1            | μV/V MAX |

| Large-Signal<br>Voltage Gain    | A <sub>VO</sub>  | $V_O = \pm 10V$ , $R_L = 1\kappa\Omega$                          | 7.5          | V/μV MIN |

| Positive Current Limit          | +I <sub>sc</sub> | Output shorted to Ground                                         | 60           | mA MIN   |

| Negative Current Limit          | -I <sub>SC</sub> | Output shorted to Ground                                         | 60           | mA MIN   |

| Quiescent Supply Current        | I <sub>SY</sub>  | No Load                                                          | 3.3          | mA MAX   |

#### NOTE:

Electrical tests are performed at wafer probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after packaging is not guaranteed for standard product dice. Consult factory to negotiate specifications based on dice lot qualification through sample lot assembly and testing.

**TYPICAL ELECTRICAL CHARACTERISTICS** at  $V+=+V_{OP}=+15V$ ,  $V-=-V_{OP}=-15V$ ,  $T_A=25^{\circ}C$ , no compensation, unless otherwise noted.

| PARAMETER                  | SYMBOL            | CONDITIONS                                                              | OP-50G<br>TYPICAL | UNITS             |

|----------------------------|-------------------|-------------------------------------------------------------------------|-------------------|-------------------|

| Slew Rate                  | SR                | R <sub>L</sub> ≥ 2kΩ<br>R <sub>C</sub> = 560Ω<br>C <sub>C</sub> = 4.7nF | 3                 | V/µs              |

| Noise Voltage Density      | €n                | f = 10Hz<br>f = 1kHz                                                    | 5.5<br>4.5        | nV/√Hz            |

| Input Noise Voltage        | € <sub>np-p</sub> | f = 0.1Hz to 10Hz                                                       | 0.12              | μV <sub>p-p</sub> |

| Noise Current Density      | İŋ                | f = 10Hz<br>f = 1kHz                                                    | 0.2<br>0.15       | pA/√Hz            |

| Capacitive Load Capability | CL                | $A_{VCL} \ge 5$ $R_C = 560\Omega$ $C_C = 4.7nF$                         | 10                | nF                |

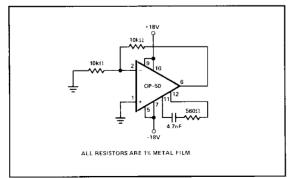

## NOISE TEST CIRCUIT (0.1 TO 10Hz)

## **BURN-IN CIRCUIT**

## OFFSET NULLING CIRCUIT

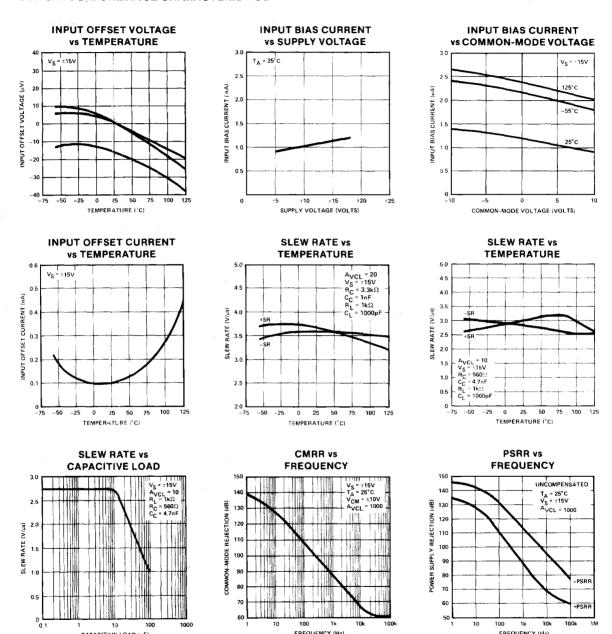

## TYPICAL PERFORMANCE CHARACTERISTICS

NOTE:

The symbol  $\pm V_S$  is used to indicate the supply voltages when the main amplifier and the output stage are being operated at the same voltages.

10

CAPACITIVE LOAD (nF)

FREQUENCY (Hz)

FREQUENCY (Hz)

## TYPICAL PERFORMANCE CHARACTERISTICS

## TYPICAL PERFORMANCE CHARACTERISTICS

## TCVOS TEST CIRCUIT

#### **APPLICATIONS INFORMATION**

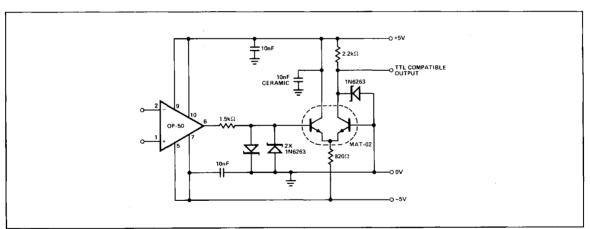

#### HIGH-SENSITIVITY VOLTAGE COMPARATOR

A comparator capable of resolving a submicrovolt difference signal is shown in Figure 1. The OP-50, operating without feedback, drives a second gain stage which generates a TTL-compatible output signal Schottky-clamp diodes prevent

overdriving of the long-tailed transistor pair and stop saturation of the output transistor. Power supply voltage is set to ±5V to lower the quiescent power dissipation and minimize thermal feedback due to output stage dissipation. Operating from ±5V supplies also reduces the OP-50 rise and fall times as the output slews over a reduced voltage range. This, in turn, reduces the output response time.

It is common practice with voltage comparators to ground one input terminal and to use a single-ended input. The historic reason is poor common-mode rejection on the input stage. In contrast, the OP-50 has very high common-mode rejection and is capable of detecting microvolt level differences in the presence of large common-mode signals.

The comparator is not fast, but it is very sensitive and can detect signal differences as low as  $0.3\mu V$ . With large input overdrives, the circuit responds in approximately  $3\mu s$ . If sharp transitions are needed, the use of a TTL Schmitt-trigger input is recommended. A table of Response Time vs. Input Overdrive is shown below.

| INPUT OVERDRIVE       | 100mV | 10mV | 1mV  | 100μV | 10μ <b>V</b> |

|-----------------------|-------|------|------|-------|--------------|

| Positive Output Delay | 3.2µs | 5μs  | 40μs | 340µs | 2.4ms        |

| Negative Output Delay | 1.8µs | 5µs  | 50µs | 380µs | 4.5ms        |

FIGURE 1: HIGH-SENSITIVITY VOLTAGE COMPARATOR

## INTEGRATOR AND UNITY-GAIN BUFFER

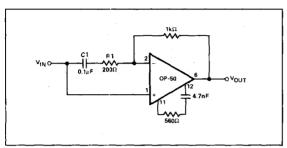

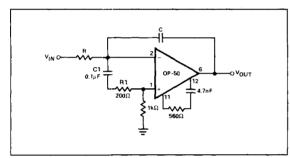

Figure 2 shows a method of obtaining unity-gain in a buffer configuration. The R1 and C1 network provides input compensation to circumvent the minimum gain requirement. Figure 3 shows the same technique applied in the inverting mode to form a high precision integrator.

FIGURE 2: UNITY GAIN BUFFER

FIGURE 3: INTEGRATOR

## 20mA CURRENT SOURCE

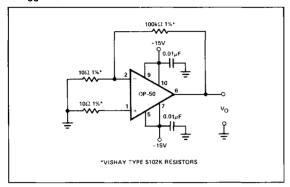

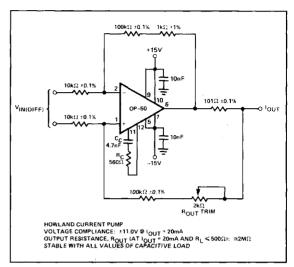

The 20mA current source exploits the high output current and high linearity capabilities of the OP-50. Five precision resistors and a trim potentiometer are required in this circuit configuration, known as the Howland Current Pump. The trim potentiometer is used to balance the resistive feedback dividers. This maximizes the current-source output impedance. Compensation is selected for a voltage gain of 10.

Compliance is better than  $\pm 11V$  at an output current of 20mA and the trimmed output resistance is typically 2M $\Omega$  with  $R_L \leq 500\Omega.$  The transfer function is given by:

$$I_{OUT} = \frac{V_{IN (DIFF)} \times 10.1}{101} \text{ Amps}$$

$V_{IN\ (DIFF)}$  is the differential input voltage. For the resistor values shown in Figure 4, the maximum  $V_{IN\ (DIFF)}$  is 200mV.

FIGURE 4: 20mA CURRENT SOURCE

#### DRIVING 50Ω LOADS

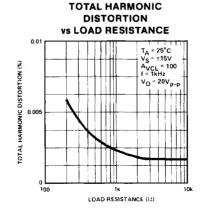

The OP-50 can provide up to 50mA into a 50 $\Omega$  load and up to 26mA into a 500 $\Omega$  load. The output is stable driving capacitive loads of up to 10nF.

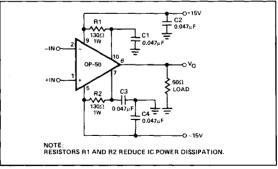

Applications that make use of the high output current capability of the OP-50 will cause increased power dissipation in the amplifier. To reduce internal dissipation in these applications, external voltage dropping resistors can be connected in series with the output-stage power supply pins. As shown in Figure 5, 130 $\Omega$  resistors can be attached to pin 7 (-V<sub>OP</sub>) and to pin 10 (+V<sub>OP</sub>). To maintain stability and specified performance levels,  $0.047\mu F$  decoupling capacitors should be used as indicated from pin 7 and pin 10 to ground.

FIGURE 5: DRIVING 500 LOADS