# Military CMOS Programmable Gate Array Logic Cell™ Array M2064/M2018

Conforms to MIL-STD-883, Class B\*

## **Features**

#### **CMOS**

- Low power

- TTL or CMOS input threshold levels

## PROGRAMABLE

- Programmable Logic functions

- Programmable I/O blocks

- Programmable interconnects

#### STATIC RAM BASED

- Reprogrammable

- Reconfigurable

## SECURITY

- User selectable Security

Mode

- Verification feature

# **Benefits**

- Reduced power supply

- · Higher board densitles

- Complete user control of design

- Instant prototyping

- Replaces SSI and MSI devices

- · Easy design modification

- Selectable configuration modes

- 100% testable

- Protects proprietary designs

- · Eases design debug

# **Description**

The Military CMOS Logic Cell Array bridges the gap between Programmable Logic Devices (PLDs) and gate arrays. This high-density, low-power Logic Cell Array device provides designers with both the density benefits of gate arrays and the programmability benefits of user-configurable devices.

The flexible architecture of the LCA is similar to that of a gate array, with an interior matrix of programmable logic blocks called Configurable Logic Blocks (CLBs), a surrounding ring of programmable I/O blocks (IOBs) and programmable interconects used to define the overall device structure. Unlike gate arrays, LCA functionality is user defined by loading the internal

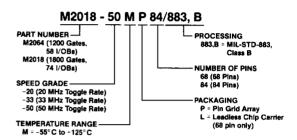

## **Ordering Information**

writable storage cells with the configuration data. The reprogrammability of the SRAM-based LCA allows instant design modification on the bench and on the board. Due to the SRAM-based architecture of the LCA, the radiation tolerance data for the M2064 is similar to industry SRAMs which display Total Dose levels from 10<sup>4</sup> to 10<sup>6</sup> rads (Si).

Applications for the LCA cover a wide spectrum of uses. With its high gate density and low-power CMOS technology, the LCA is an ideal low-cost gate array good for prototyping as well as production. The LCA's SRAM-based architecture allows it to be used in applications that take advantage of its reconfigurability. Ground systems (radar) can use the LCA as reconfigurable hardware replacing several devices and saving board space. The SRAM-based logic of the LCA allows for pattern security of sensitive designs when the device is removed from its board. When a different mode backup device is needed the LCA provides excellent redundancy. In short, the LCA offers the total ASIC solution.

## Silicon Menu

| MMI<br>PART | ORGAN-<br>IZATION | EQUIVA-<br>LENT<br>GATE<br>COUNT | CONFIGU-<br>RABLE<br>LOGIC<br>BLOCKS | USER<br>I/Os | CONFIGU-<br>RATION<br>PROGRAM<br>BITS | MAX<br>STANDBY<br>CURRENT<br>(CMOS<br>INPUTS) | MAX<br>STANDBY<br>CURRENT<br>(TTL<br>INPUTS) | PACKAGES        | MAX<br>TOGGLE<br>RATE<br>BETWEEN<br>CLBs |

|-------------|-------------------|----------------------------------|--------------------------------------|--------------|---------------------------------------|-----------------------------------------------|----------------------------------------------|-----------------|------------------------------------------|

| M2064-20    | 8x8               | 1200                             | 64                                   | 58           | 12040                                 | 5 mA                                          | 10 mA                                        | 68LCC,<br>68PGA | 20 MHz                                   |

| M2064-33    | 8x8               | 1200                             | 64                                   | 58           | 12040                                 | 5 mA                                          | 10 mA                                        | 68LCC,<br>68PGA | 33 MHz                                   |

| M2064-50    | 8x8               | 1200                             | 64                                   | 58           | 12040                                 | 5 mA                                          | 10 mA                                        | 68LCC,<br>68PGA | 50 MHz                                   |

<sup>\*</sup> Latest revision.

10331A JANUARY 1988

## Software/Hardware Menu

| MMI PARTS |                                                    |

|-----------|----------------------------------------------------|

| LCA-MDS21 | LCA Development System                             |

| LCA-MSC21 | LCA Development System<br>Annual Support Agreement |

| LCA-MDS22 | LCA Simulator (P-SILOS**)                          |

| LCA-MDS23 | LCA Automatic Placement and<br>Routing Program     |

| LCA-MDS24 | LCA In-Circuit Emulator                            |

| MMI PARTS   |                                  |

|-------------|----------------------------------|

| LCA-MDS28   | LCA Universal Pod                |

| LCA-MDS27XX | LCA Package Specific Pod Headers |

| LCA-MDS31   | LCA Futurenet® Interface         |

| LCA-MDS33   | LCA Daisy Interface              |

| LCA-MDS34   | LCA Mentor Interface             |

| LCA-MDSXX   | LCA/OrCAD™ Package               |

| LCA-MEK01   | LCA Evaluation Kit               |

# **Absolute Maximum Ratings**

| Supply voltage, VCC                                                         | -0.5 V to 7.0 V |

|-----------------------------------------------------------------------------|-----------------|

| Power down, V <sub>CC</sub>                                                 |                 |

| Input voltage range                                                         |                 |

| Voltage applied to three-state output                                       | -0.5 V to 5.5 V |

| Storage temperature -65                                                     |                 |

| Terminal temperature, Leadless Chip Carrier package (Soldering, 10 seconds) | 240°C           |

| Thermal resistance, junction to case flower and junction to ambient flower  |                 |

Thermal resistance, junction to case,  $heta_{

m jcmax}$ , and junction to ambient,  $heta_{

m jamax}$

| Package                   | $\theta$ jcmax | $\theta_{jamax}$ (Still air) |

|---------------------------|----------------|------------------------------|

| (L) Leadless Chip Carrier | 1.5°C/W        | 32° C/W                      |

| (P) Pin Grid Array        | 3°C/W          | 45° C/W                      |

|                           |                |                              |

Maximum power dissipation

See Table 2

Maximum junction temperature

175°C

Maximum current density

Contact factory

# **Operating Conditions**

| SYMBOL           | PARAMETER                                                | MIN TYP MAX                         | UNIT |

|------------------|----------------------------------------------------------|-------------------------------------|------|

| v <sub>CC</sub>  | Supply voltage relative to GND                           | 4.5 5.5                             | V    |

| VIHT             | High level input voltage—TTL configuration               | 2.0 V <sub>CC</sub>                 | V    |

| V <sub>IHC</sub> | High level input voltage—CMOS configuration              | 0.7 V <sub>CC</sub> V <sub>CC</sub> | ٧    |

| VILT             | Low level input voltage—TTL configuration                | 0 0.8                               | V    |

| V <sub>ILC</sub> | Low level input voltage—CMOS configuration               | 0 0.2 V <sub>CC</sub>               | V    |

| ΙΤ               | Input leakage current—TTL configuration                  | ±1                                  | μА   |

| lic              | Input leakage current—CMOS configuration                 | ±1                                  | μА   |

| loz              | Three-state output off current (V <sub>CC</sub> = 5.5 V) | ±10                                 | μА   |

| <sup>t</sup> OP  | Operating free-air temperature                           | -55 +125                            | °C   |

# **Electrical Characteristics** Over Operating Conditions

Conforms to MIL-STD-883 Group A Subgroups 1, 2 and 3

| SYMBOL | PARAM                    | ETER        | TEST C                  | MIN TYP                   | MAX | UNIT |    |

|--------|--------------------------|-------------|-------------------------|---------------------------|-----|------|----|

| Vон    | High level output volta  | ge          | V <sub>CC</sub> = MIN   | I <sub>OH</sub> = -4.0 mA | 3.7 |      | V  |

| VOL    | Low level output voltage | ge          | V <sub>CC</sub> = MIN   | I <sub>OL</sub> = 4.0 mA  |     | 0.4  | ٧  |

| le     | Quiescent operating      | CMOS inputs | V <sub>CC</sub> = 5.0 V |                           |     | 5    | mA |

| lcco   | power supply current     | TTL inputs  | V <sub>CC</sub> = 5.0 V |                           |     | 10   | mA |

| CCPD   | Power down supply cu     | irrent      | V <sub>CC</sub> = 2.0 V |                           |     | 0.5  | mA |

G

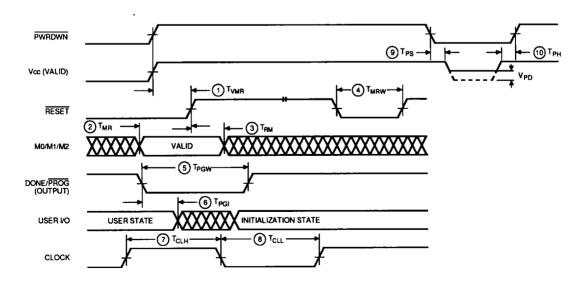

# **Power On Timing**

The LCAs contain on-chip reset timing logic for power-up operation. To insure proper master mode system operation, VCC must rise from 2.0 V to minimum specification level in 10 ms or less. For other modes, initiation of configuration must be

delayed for 60 ms after VCC reaches the minimum specified level.

## **Test Conditions**

Outputs loaded with rated DC current and 50-pF capacitance to GND

# **Switching Characteristics — General**

Conforms to MiL-STD-883 Group A Subgroups 9, 10 and 11\*

| SYMBOL                         | DESCRIPTION        |                               | -:  | -20 |     | -33 |     | -50 |      |

|--------------------------------|--------------------|-------------------------------|-----|-----|-----|-----|-----|-----|------|

| STMBOL                         |                    |                               | MIN | MAX | MIN | MAX | MIN | MAX | UNIT |

| t <sub>VMR</sub> ①             |                    | V <sub>CC</sub> setup (2.0 V) | 250 |     | 150 |     | 150 |     | ns   |

| t <sub>MR</sub> ②              | RESET <sup>2</sup> | M2, M1, M0 setup              | 100 |     | 60  |     | 60  |     | ns   |

| t <sub>RM</sub> ①              | nese:              | M2, M1, M0 hold               | 100 | •   | 60  |     | 60  |     | ns   |

| t <sub>MRW</sub> ①             |                    | Width (LOW)                   | 250 |     | 150 |     | 150 |     | ns   |

| t <sub>PGW</sub> ⑤             | DONE/              | Program width (LOW)           | 6   |     | 6   |     | 6   |     | μS   |

| t <sub>PGI</sub> ®             | PROG               | Initialization                |     | 7   |     | 7   |     | 7   | μS   |

| tCLH ⑦                         | CLOCK              | Clock (HIGH)                  | 20  |     | 12  |     | 8   |     | ns   |

| t <sub>CLL</sub> ③             | CLOCK              | Clock (LOW)                   | 20  |     | 12  |     | 8   |     | ns   |

| t <sub>PS</sub> ⑨              | PWR DWN            | Setup to V <sub>CC</sub>      | 0   |     | 0   |     | 0   |     | ns   |

| t <sub>PH</sub> <sup>(j)</sup> |                    | Hold from V <sub>CC</sub>     | 0   |     | 0   |     | 0   |     | ns   |

| V <sub>PD</sub>                |                    | Power Down                    | 2.0 |     | 2.0 |     | 2.0 |     | ٧    |

Notes: 1. V<sub>CC</sub> must rise from 2.0 Volts to V<sub>CC</sub> minimum in lest than 10 ms for master mode

- 2. RESET timing relative to power-on and valid mode lines (M0, M1, M2) is relevant only when RESET is used to delay configuration.

- 3. Minimum CLOCK widths for the auxiliary buffer are 1.25 times the t<sub>CLH</sub>, t<sub>CLL</sub>.

- \* Contact factory for test macros.

# 7

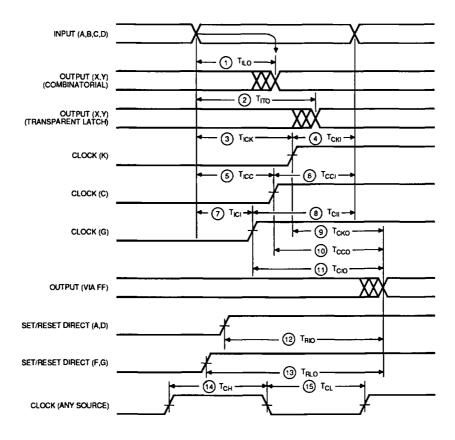

# **Switching Characteristics — CLB**

| SYMBOL               | DESCRIPTION               |                                        | -   | 20  | -33 |     |     | -50 | UNIT |

|----------------------|---------------------------|----------------------------------------|-----|-----|-----|-----|-----|-----|------|

| SIMBOL               | DESCI                     | RIPHON                                 | MIN | MAX | MIN | MAX | MIN | MAX | UNII |

| t <sub>ILO</sub> ①   |                           | Combinatorial                          |     | 35  |     | 20  |     | 15  | ns   |

| t <sub>ITO</sub> ②   | Logic input               | Transparent latch                      |     | 45  |     | 25  |     | 20  | ns   |

| <sup>t</sup> QLO     | to output                 | Additional for Q through F or G to out |     | 30  |     | 13  |     | 8   | ns   |

| tско                 |                           | To output                              |     | 35  |     | 20  |     | 15  | ns   |

| t <sub>ICK</sub> ③   | K Clock                   | Logic-input setup                      | 22  |     | 12  |     | 8   |     | ns   |

| t <sub>CKI</sub> ⊙   |                           | Logic-input hold                       | 0   |     | 0   |     | 0   |     | ns   |

| © 000±               |                           | To output                              |     | 45  |     | 25  |     | 19  | ns   |

| t <sub>ICC</sub> ⑤   | C Clock                   | Logic-input setup                      | 18  |     | 12  |     | 9   |     | ns   |

| tCCI ®               |                           | Logic-input hold                       | 10  |     | 6   |     | 0   |     | ns   |

| OIO <sup>‡</sup>     |                           | To output                              |     | 65  |     | 37  |     | 27  | nş   |

| t <sub>ICI</sub> ①   | Logic input<br>to G Clock | Logic-input setup                      | 10  |     | 6   |     | 4   |     | ns   |

| tCII ®               |                           | Logic-input hold                       | 15  |     | 9   |     | 5   |     | пѕ   |

| t <sub>RIO ®</sub>   |                           | Input A or D to out                    |     | 45  |     | 25  |     | 22  | ns   |

| t <sub>RLO (1)</sub> |                           | Through F or G to out                  |     | 65  |     | 37  |     | 28  | ns   |

| <sup>t</sup> MRQ     | Set/reset direct          | Master Reset pin to out                |     | 60  |     | 35  |     | 25  | ns   |

| <sup>t</sup> RS      |                           | Separation of set/reset                | 30  |     | 17  |     | 9   |     | ns   |

| tRPW                 |                           | Set/reset pulse-width                  | 20  |     | 12  |     | 9   |     | ns   |

| FCLK                 | Flip-flop toggle rate     | Q through F to flip-flop               | 20  |     | 33  |     | 50  |     | MHz  |

| t <sub>CH</sub> (6   | Clock                     | Clock HIGH                             | 20  |     | 12  |     | 8   |     | ns   |

| t <sub>CL</sub> (§   | CIOCK                     | Clock LOW                              | 20  |     | 12  |     | 8   | _   | ns   |

Note: All switching characteristics apply to all valid combinations of process, temperature and supply

# Military Case Outlines\*

| PACKAGE OUTLINE<br>LETTER | CONFORMS TO<br>MIL-M-38510<br>APPENDIX C CASE |

|---------------------------|-----------------------------------------------|

| L                         | C-7                                           |

| Р                         | P-BC                                          |

<sup>\*</sup> Refer to MIL-M-38510. Appendix C for the appropriate package drawings

# **Switching Characteristics CLB**

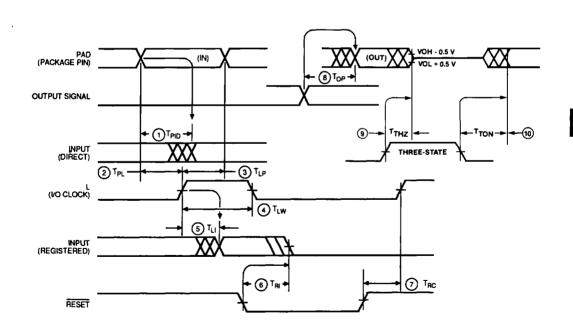

# Switching Characteristics — IOB

| SYMBOL             | DESCRIPTION                         |     | -20 |     | -33 |     | -50 |      |

|--------------------|-------------------------------------|-----|-----|-----|-----|-----|-----|------|

|                    | DESCRIPTION                         | MIN | MAX | MIN | MAX | MIN | MAX | TINU |

| t <sub>PID</sub> ① | Pad (package pin) to input (direct) |     | 20  |     | 12  |     | 8   | ns   |

| t <sub>LI</sub> ①  | I/O Clock to input (storage)        |     | 30  |     | 20  |     | 15  | ns   |

| tpL ②              | /O Clock to pad-input setup         | 20  |     | 12  |     | 8   |     | п\$  |

| tլթ (3             | I/O Clock to pad-input hold         | 0   |     | 0   |     | 0   |     | ns   |

| , ,                | I/O Clock pulse width               | 20  |     | 12  |     | 9   |     | nsp  |

| t <sub>LW</sub>    | I/O Clock frequency                 |     | 20  |     | 33  |     | 50  | MHz  |

| t <sub>OP</sub> ①  | Output to pad (output enabled)      |     | 25  |     | 15  |     | 12  | пѕ   |

| t <sub>THZ</sub> ⑨ | Three-state to pad begin hi-Z       |     | 35  |     | 25  |     | 20  | ns   |

| tTON ®             | Three-state to pad end hi-Z         |     | 40  |     | 25  |     | 20  | ns   |

| t <sub>RI</sub> ®  | RESET to input (storage)            |     | 50  |     | 40  |     | 30  | ns   |

| t <sub>RC</sub> ①  | RESET to input clock                |     | 35  |     | 35  |     | 25  | ns   |

Note Timing is measured at 0.5 V<sub>CC</sub> levels with 50-pF output load.

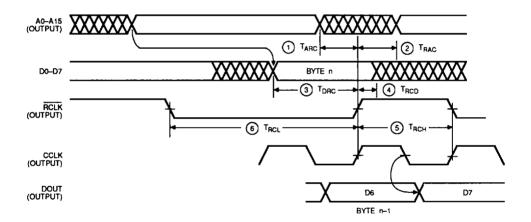

# Switching Characteristics — Programming — Master Mode

| SYMBOL             | DESCRIPTION |                      |     | -20 |     | -33 |     | -50 |      |

|--------------------|-------------|----------------------|-----|-----|-----|-----|-----|-----|------|

|                    |             | DESCRIPTION          |     | MAX | MIN | MAX | MIN | MAX | UNIT |

| tARC ①             |             | From address invalid |     | 0   |     | 0   |     | 0   | ns   |

| t <sub>RAC</sub> ② |             | To address valid     |     | 300 |     | 200 |     | 200 | ns   |

| tDRC ①             | RCLK        | To data setup        | 100 |     | 60  |     | 60  |     | กร   |

| t <sub>RCD</sub> ① | HOLK        | To data hold         | 0   |     | 0   |     | 0   |     | ns   |

| t <sub>RCH</sub> ⑤ |             | RCLK HIGH            | 600 |     | 600 |     | 600 |     | ns   |

| t <sub>RCL</sub> © |             | RCLK LOW             | 4.0 |     | 4.0 |     | 4.0 |     | μS   |

Notes 1. CCLK and DOUT timing are the same as for slave mode

<sup>2</sup> At power up, V<sub>CC</sub> must rise from 2.0 V to V<sub>CC</sub> minimum in less than 10 ms

# 5

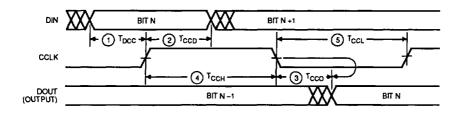

# Switching Characteristics — Programming — Slave Mode

| SYMBOL                    | DESCRIPTION    | -20  |      | -33  |     | -50  |     |      |

|---------------------------|----------------|------|------|------|-----|------|-----|------|

|                           |                | MIN  | MAX  | MIN  | MAX | MIN  | MAX | UNIT |

| tcco ①                    | CCLK to DOUT   |      | 100  |      | 65  |      | 65  | ns   |

| tDCC ①                    | CCLK DIN setup | 50   |      | 25   |     | 0    |     | ns   |

| tCCD ②                    | CCLK DIN hold  | 75   |      |      | 40  |      | 40  | ns   |

| <sup>t</sup> CCH <b>①</b> | CCLK HIGH time | 0.50 |      | 0.30 |     | 0.25 |     | μS   |

| tCCL ③                    | CCLK LOW time  | 0.30 | 10.0 | 0.25 | 5.0 | 0.25 | 5.0 | μS   |

| FCC                       | CCLK frequency |      | 1    |      | 2   |      | 2   | MHz  |

Note. Configuration must be delayed at least 40 ms after  $V_{\mbox{\footnotesize{CC}}}$  minimum.

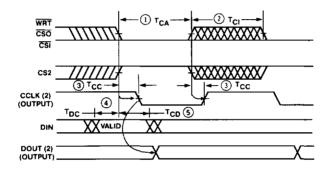

# Switching Characteristics — Programming — Peripheral Mode

| SYMBOL             | DESCRIPTION                         |                                                |      | -20  |      | -33 |      | -50 |    |

|--------------------|-------------------------------------|------------------------------------------------|------|------|------|-----|------|-----|----|

| J                  |                                     | MIN                                            | MAX  | MIN  | MAX  | MIN | MAX  | X   |    |

| t <sub>CA</sub> ①  | -                                   | Active (last active input to first inactive)   | 0.30 | 10.0 | 0.25 | 5.0 | 0.25 | 5.0 | μS |

| t <sub>Cl</sub> ②  | Controls <sup>1</sup><br>(CS0, CS1, | Inactive (first inactive input to last active) | 0.25 |      | 0.25 |     | 0.25 |     | μS |

| t <sub>CCC</sub> ① | CS2, WRT)                           | CCLK <sup>2</sup>                              |      | 100  |      | 75  |      | 75  | ns |

| t <sub>DC</sub>    |                                     | DIN setup                                      | 50   |      | 35   |     | 35   |     | ns |

| t <sub>CD</sub> ③  |                                     | DIN hold                                       | 10   |      | 5    |     | 5    |     | ns |

Notes: 1 Peripheral mode timing determined from last control signal of the logical AND of (CSO, CS1, CS2, WRT) to transition to active or inactive state

- 2. CCLK and DOUT timing are the same as for slave mode

- 3. Configuration must be delayed at least 40 ms after V<sub>CC</sub> minimum.

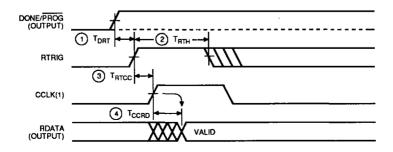

# **Switching Characteristics — Program Readback**

| SYMBOL             | DESCRIPTION |             | _   | -20 |     | -33 |     | -50 |      |

|--------------------|-------------|-------------|-----|-----|-----|-----|-----|-----|------|

| SIMBOL             |             |             | MIN | MAX | MIN | MAX | MIN | MAX | UNIT |

| t <sub>DRT</sub> ① | RTRIG       | PROG setup  | 300 |     | 300 |     | 300 |     | ns   |

| t <sub>RTH</sub> ② | ninia       | RTRIG HIGH  | 250 |     | 250 |     | 250 |     | ns   |

| tRTCC ③            | CCLK        | RTRIG setup | 100 |     | 100 |     | 100 |     | ns   |

| tCCRD ①            | CCLK        | RDATA delay |     | 100 |     | 100 |     | 100 | ns   |

Notes: 1. CCLK and DOUT timing are the same as for slave mode.

2. DONE/PROG output/input must be HIGH (device programmed) prior to a positive transition of RTRIG (M0).

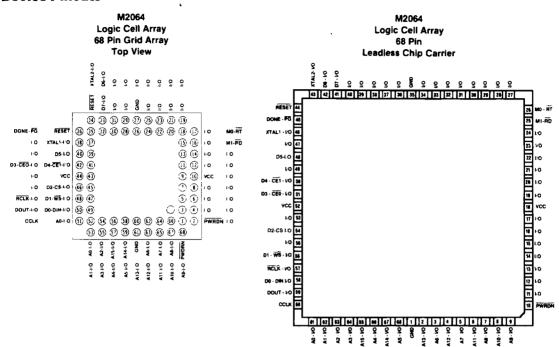

## **Device Pinouts\***

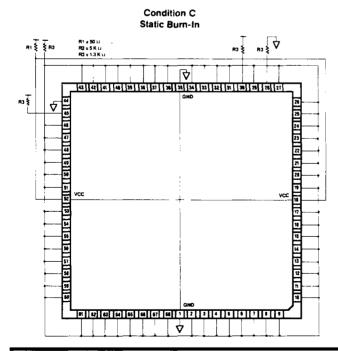

# **Burn-In Circuitry\***

Condition D

Dynamic Burn-In

Contact factory

# Military M2064/M2018

# Configuration Pin Assignments\*

| 00 DIN        | 20 500        | С                | ONFIGURATION I        | MODE: ≪M2: M1: M       | 0≫                    |                   |  |  |

|---------------|---------------|------------------|-----------------------|------------------------|-----------------------|-------------------|--|--|

| 68-PIN<br>LCC | 68-PIN<br>PGA | SLAVE<br><1:1:1> | PERIPHERAL<br><1:0:1> | MASTER-HIGH<br><1:1:0> | MASTER-LOW<br><1:0:0> | USER<br>OPERATION |  |  |

| 1             | B6            |                  | GND                   |                        |                       |                   |  |  |

| 2             | A6            |                  |                       | A13                    | (O)                   |                   |  |  |

| 3             | B5            | 1                |                       | A6                     | (O)                   | 1                 |  |  |

| 4             | A5            | 1                |                       | A12                    | (O)                   |                   |  |  |

| 5             | B4            |                  | ≪HIGH≫ A7 (O)         |                        |                       | 1/0               |  |  |

| 6             | A4            | ] ""             | GI IS                 | A11                    | "                     |                   |  |  |

| 7             | B3            | 1                |                       | A8                     | (O)                   | 1                 |  |  |

| 8             | A3            | 1                |                       | A10                    | A10 (O)               |                   |  |  |

| 9             | A2            | 1                | A9 (O)                |                        |                       |                   |  |  |

| 10            | B2            |                  | PWR                   | OWN (I)                |                       |                   |  |  |

| 11            | B1            |                  |                       |                        |                       |                   |  |  |

| 12            | C2            | 1                |                       |                        |                       |                   |  |  |

| 13            | C1            | 1                |                       |                        |                       | 1/0               |  |  |

| 14            | D2            | 1                | ≪HI                   | GH≫                    |                       |                   |  |  |

| 15            | D1            |                  |                       |                        |                       |                   |  |  |

| 16            | . E2          | 1                |                       |                        |                       |                   |  |  |

| 17            | E1            |                  |                       |                        |                       |                   |  |  |

| 18            | F2            |                  | VCC                   |                        |                       |                   |  |  |

| 19            | F1            |                  |                       |                        |                       |                   |  |  |

| 20            | G2            |                  |                       |                        |                       |                   |  |  |

| 21            | G1            |                  | ≪н                    | GH≫                    |                       | 1/0               |  |  |

| 22            | H2            | 1                | ×111                  |                        |                       |                   |  |  |

| 23            | H1            |                  |                       |                        |                       |                   |  |  |

| 24            | J2            |                  |                       |                        |                       |                   |  |  |

| 25            | J1            | M1 (HIGH)        | M1 (LOW)              | M1 (HIGH) M1 (LOW)     |                       | RDATA (O)         |  |  |

| 26            | K1            | M0 (HIGH)        | M0 (HIGH)             | M0 (LOW)               | M0 (LOW)              | RTRIG (I)         |  |  |

| 27            | K2            |                  | M2 (                  | HIGH)                  |                       |                   |  |  |

| 28            | L2            |                  | HDC (HIGH)            |                        |                       |                   |  |  |

| 29            | К3            |                  | ]                     |                        |                       |                   |  |  |

| 30            | L3            |                  | ]                     |                        |                       |                   |  |  |

| 31            | K4            |                  |                       |                        |                       | 1/0               |  |  |

| 32            | L4            | ≪HIGH≫           |                       |                        |                       |                   |  |  |

| 33            | K5            |                  |                       |                        |                       |                   |  |  |

| 34            | L5            |                  |                       |                        |                       |                   |  |  |

≪HIGH≫ is high impedance with a 20 to 50-KΩ internal pull-up resistor during configuration

Table 1. M2064 Pin Assignments (continued on next page)

# **Configuration Pin Assignments\***

| 68-PIN | 68-PIN | C                | LICER                 |                        |                       |                                                  |  |  |

|--------|--------|------------------|-----------------------|------------------------|-----------------------|--------------------------------------------------|--|--|

| LCC    | PGA    | SLAVE<br><1:1:1> | PERIPHERAL<br><1:0:1> | MASTER-HIGH<br><1:1:0> | MASTER-LOW<br><1:0:0> | USER<br>OPERATION                                |  |  |

| 35     | K6     |                  |                       |                        |                       |                                                  |  |  |

| 36     | L6     |                  |                       |                        |                       | <del>                                     </del> |  |  |

| 37     | K7     |                  |                       |                        |                       |                                                  |  |  |

| 38     | L7     | 7                | ≪H                    | IGH≫                   |                       |                                                  |  |  |

| 39     | K8     | 7                |                       |                        |                       | 1/0                                              |  |  |

| 40     | L8     | 7                |                       |                        |                       |                                                  |  |  |

| 41     | К9     | 7                |                       | D7                     | (1)                   |                                                  |  |  |

| 42     | L9     | 7                |                       | D6                     |                       |                                                  |  |  |

| 43     | L10    | 7                |                       |                        |                       | XTL2 or I/O                                      |  |  |

| 44     | K10    |                  | RES                   | ET (I)                 | · · · · -             | <del>1</del>                                     |  |  |

| 45     | K11    |                  | <del></del>           | NE (O)                 |                       | PROG (I)                                         |  |  |

| 46     | J10    |                  |                       |                        |                       | XTL1 or I/O                                      |  |  |

| 47     | J11    | ≪H               | IGH≫                  |                        |                       |                                                  |  |  |

| 48     | H10    | 7                |                       | D5                     | (1)                   | 1                                                |  |  |

| 49     | H11    | 7                |                       |                        |                       | 1/0                                              |  |  |

| 50     | G10    | 1                | CS0 (I)               | D4                     | (1)                   | 1                                                |  |  |

| 51     | G11    | 7                | ČS1 (I)               | D3                     | (I)                   | 1                                                |  |  |

| 52     | F10    |                  | V                     | cc                     |                       | •                                                |  |  |

| 53     | F11    |                  |                       |                        |                       |                                                  |  |  |

| 54     | E10    | 7                | CS2 (I)               | D2                     | (I)                   | -                                                |  |  |

| 55     | E11    | ≪HIGH≫           |                       | <u>'</u>               |                       | -                                                |  |  |

| 56     | D10    |                  | WRT (I)               | D1                     | (1)                   | 1/0                                              |  |  |

| 57     | D11    |                  | <u> </u>              | RC                     | EK                    |                                                  |  |  |

| 58     | C10    | DI               | N (I)                 | DO                     | (1)                   |                                                  |  |  |

| 59     | C11    |                  | DOUT (O)              |                        |                       |                                                  |  |  |

| 60     | B11    | CCLK (I)         | CCL                   | CCLK (O)               |                       | CCLK (I)                                         |  |  |

| 61     | B10    |                  |                       | A0                     | (O)                   |                                                  |  |  |

| 62     | A10    | 7                |                       | A1                     | (O)                   |                                                  |  |  |

| 63     | B9     | 7                |                       | A2                     | (O)                   |                                                  |  |  |

| 64     | A9     |                  | liGH≫                 | A3                     | (O)                   | 1/0                                              |  |  |

| 65     | B8     |                  |                       | A15                    | (0)                   | 1 "                                              |  |  |

| 66     | A8     | 7                |                       | A4                     | (O)                   |                                                  |  |  |

| 67     | B7     | 1                | A14 (O)               |                        |                       |                                                  |  |  |

| 68     | A7     | 7                |                       | A5                     | (O)                   | ]                                                |  |  |

≪HIGH≫ is high impedance with a 20 to 50-KΩ internal pull-up resistor during configuration

Table 1. M2064 Pin Assignments

<sup>\*</sup> Contact factory for M2018 pinout, burn in circuitry and pin assignments.

## Pin Description

#### PWROWN

An active low power-down input stops all internal activity to minimize VCC power and puts all output buffers in a high-impedance state. Configuration is retained, however, internal storage elements are Reset. When the PWRDWN pin returns HIGH, the device returns to operation with the same sequence of reset, buffer enable and DONE, PROGRAM as at the completion of configuration.

#### MO. RTRIG

As Mode 0, this input and M1, M2 are sampled before the start of configuration to establish the configuration mode to be used.

As a read trigger, an input transition to a HIGH, after configuration is complete, will initiate a readback of configuration and storage element data. This operation may be limited to a single request, or be inhibited altogether, by selecting the appropriate readback option when generating the bit stream.

#### M1. RDATA

As Mode 1, this input and M0, M2 are sampled before the start of configuration to establish the configuration mode to be used.

As an active-low read data; after configuration is complete, this pin is the output of the readback data.

#### M<sub>2</sub>

As Mode 2, this input and M0, M1 are sampled before the start of configuration to establish the configuration, mode to be used. After configuration, this pin becomes a user-programmable I/O.

## HDC

High during configuration is held at a HIGH level by the LCA until after configuration. It is intended to be available as a control indication that configuration is not complete. After configuration, this pin is a user I/O.

#### LDC

Low during configuration is held at a LOW level by the LCA until after configuration. It is intended to be available as a control indication that configuration is not completed. It is particularly useful in master mode as a LOW enable for an EPROM. After configuration, this pin is a user I/O. If used as a LOW EPROM enable, it should be programmed as a HIGH after configuration.

## RESET

This is an active-low input which has three functions. Prior to the start of configuration, a LOW input will delay the start of the configuration process. An internal circuit senses the application of power and begins a minimal time-out cycle on the order of 100 ms. When the time-out and RESET are complete, the levels of the "M" mode lines are sampled and configuration begins. If RESET is asserted during a configuration, the LCA is reinitialized and will restart the configuration at the termination of RESET. If RESET is asserted after configuration is complete, it will provide an asynchronous reset of all IOB and CLB storage elements of the LCA.

## DONE, PROG

The DONE open drain output is configurable with or without a pull-up resistor of about 3 K $\Omega$ . At the completion of configuration, the circuitry of the LCA becomes active in a synchronous order and one configuration clock cycle later DONE is asserted. Once configuration is done, a HIGH-to-LOW transition of this program pin will cause an initialization of the LCA and start a reconfiguration if that mode is selected in the current configuration.

#### XTL1

This user I/O pin may be configured to operate as the output of an amplifier usable with an external crystal and bias circuitry to form an oscillator.

#### XTL2

This user I/O pin may be configured to operate as the input of an amplifier usable with an external crystal and bias circuitry to form an oscillator.

#### CCLE

During configuration, configuration clock is an output of an LCA in either master or peripheral mode. LCAs in slave mode use it as a clock input. During a readback operation, it is an input clock for the configuration data being output.

#### DOUT

This user I/O pin is used during configuration to output serial configuration data out for daisy-chained slaves' data in.

#### DIN

This user I/O pin is used as serial data in during slave or peripheral configuration. This pin is D0 in master configuration mode.

## CSO, CS1, CS2, WRT

These four inputs represent a set of signals, three active low and one active high, which are used in the peripheral mode to control configuration data entry. The assertion of all four generates a LOW CCLK and shifts DOUT data. The removal of any assertion clocks in the DIN data present and causes a HIGH CCLK. In master mode, these pins become part of the parallel configuration byte (D4, D3, D2, D1). After configuration is complete, they are user-programmed I/O.

#### **RCLK**

During master mode configuration, this pin represents a read clock of an external memory device. After configuration is complete, this pin becomes a user-programmed I/O.

## D0-D7

This set of eight pins represents the parallel configuration data byte for the master mode. After configuration is complete, they are user-programmed I/O.

## A0-A15

This set of sixteen pins presents an address output for an external configuration memory during master mode. After configuration is complete, they are user-programmed I/O. A12 through A15 are not available in packages with less than sixty-eight pins.

#### I/C

A pin which may be programmed by the user to be input and/or output following configuration. Some of these pins present a high-impedance pull-up or perform other functions before configuration is complete.