# SANYO Semiconductors **DATA SHEET**

# LC74950BG — Silicon gate 40/30MSPS Analog Display I/F LSI

#### Overview

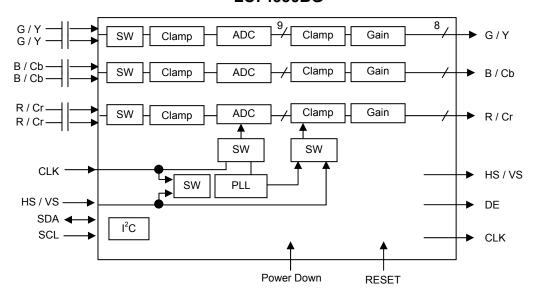

The LC74950BG is an analog display I/F IC that converts analog video signals into equivalent digital video signals. It incorporates 3 channels of ADC and a PLL circuit.

#### **Features**

- Maximum sampling frequency: 40MSPS

- 8-bit output

- Supports self-clamp (bottom/center switching) and digital clamp

- Input signal: 1.0Vp-p maximum

- External clock input

- Low jitter PLL

- Power down mode

- Low power consumption

- Input format: Supports RGB and YCbCr

- Built-in I<sup>2</sup>C bus interface

# **LSI Specifications**

• Supply voltage Core: 1.5±10%

I/O: 3.3V±0.3V (40MHz) or 2.4V to 3.6V (30MHz)

• Maximum operating frequency: 40MHz

• Package: FBGA96

#### **Principal Applications**

• Small-size monitors

- Any and all SANYO Semiconductor Co.,Ltd. products described or contained herein are, with regard to "standard application", intended for the use as general electronics equipment (home appliances, AV equipment, communication device, office equipment, industrial equipment etc.). The products mentioned herein shall not be intended for use for any "special application" (medical equipment whose purpose is to sustain life, aerospace instrument, nuclear control device, burning appliances, transportation machine, traffic signal system, safety equipment etc.) that shall require extremely high level of reliability and can directly threaten human lives in case of failure or malfunction of the product or may cause harm to human bodies, nor shall they grant any guarantee thereof. If you should intend to use our products for applications outside the standard applications of our customer who is considering such use and/or outside the scope of our intended standard applications, please consult with us prior to the intended use. If there is no consultation or inquiry before the intended use, our customer shall be solely responsible for the use.

- Specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

#### **Functions & Overview**

#### 1. Input

All the inputs listed below can be connected to the analog ports. It is also possible to switch between the inputs of two systems and use the one selected.

YCbCr/YPbPr input (480I/576I, 480P/576P): Component input

RGB: RGB input

External clock supported

#### 2. Output

Digital 8-bit/channel output

#### 3. Clamp

Analog clamping and digital clamping supported

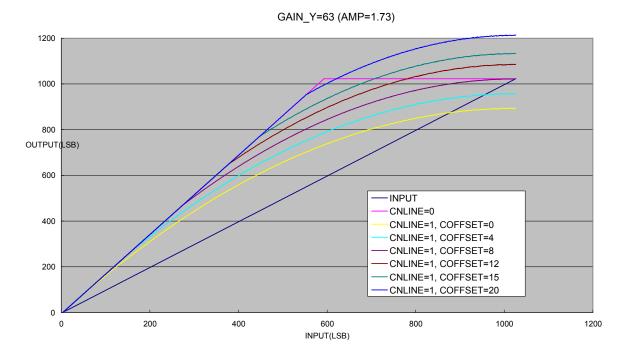

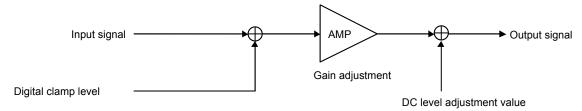

#### 4. Gain

Digital gain adjustment

#### 5. PLL circuit

This circuit can be used as the H lock or frequency-multiplied clock. It is also possible to use the PLL circuit and analog-digital converter (ADC) independently.

H lock PLL circuit: This makes it possible to generate a clock synchronized with the external H sync signal.

Frequency-multiplier PLL circuit: This makes it possible to generate clocks synchronized with an external clock.

#### 6. External interface

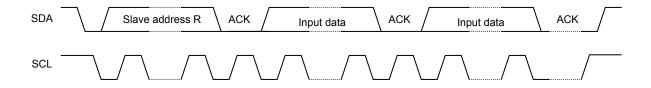

I<sup>2</sup>C: This supports the 100kHz mode. It is possible to select slave addresses by establishing pin settings.

Slave addresses: 0x98, 0x9A

#### 7. PDOWN

Power-down of the whole system can be controlled using the PDOWN pin. Alternatively, the ADC, PLL and other circuits can be powered down separately using register settings. This makes it possible to limit the power as required.

# **Specifications**

# Absolute Maximum Ratings at Ta = 25°C, $DV_{SS} = 0V$ , $AV_{SS} = 0V$

| Parameter                     | Symbol                                     | Conditions | Ratings                         | Unit |

|-------------------------------|--------------------------------------------|------------|---------------------------------|------|

| Maximum supply voltage (I/O)  | DV <sub>DD</sub> 33<br>AV <sub>DD</sub> 33 |            | -0.3 to +3.95                   | ٧    |

| Maximum supply voltage (core) | DV <sub>DD</sub> 15<br>AV <sub>DD</sub> 15 |            | -0.3 to +1.8                    | ٧    |

| Digital input voltage         | VI                                         |            | -0.3 to +5.5                    | V    |

|                               | V <sub>I</sub><br>(when in low voltage)    |            | -0.3 to DV <sub>DD</sub> 33+0.3 | V    |

| Digital output voltage        | VO                                         |            | -0.3 to DV <sub>DD</sub> 33+0.3 | V    |

| Operating temperature         | Topr                                       |            | -30 to +70                      | °C   |

| Storage temperature           | Tstg                                       |            | -55 to +125                     | °C   |

#### Allowable Operating Ranges at $Ta = -30 \text{ to } +70^{\circ}\text{C}$

| Donomotor                                          | Comple at                                  | O subst           |      | Ratings |      |      |  |

|----------------------------------------------------|--------------------------------------------|-------------------|------|---------|------|------|--|

| Parameter                                          | Symbol                                     | Symbol Conditions |      | typ     | max  | unit |  |

| Supply voltage (I/O)                               | AV <sub>DD</sub> 33                        |                   | 3.00 | 3.3     | 3.60 | V    |  |

|                                                    | DV <sub>DD</sub> 33                        | Max 40MHz         | 3.00 | 3.3     | 3.60 | V    |  |

|                                                    |                                            | Max 30MHz         | 2.40 | 3.3     | 3.60 | V    |  |

| Supply voltage (I/O)                               | DV <sub>DD</sub> 15<br>AV <sub>DD</sub> 15 |                   | 1.35 | 1.5     | 1.65 | ٧    |  |

| Input voltage range<br>(5V withstand voltage pin)  | V <sub>IN</sub> 5                          |                   | 0    |         | 5.5  | ٧    |  |

| Input voltage range (non-5V withstand voltage pin) | V <sub>IN</sub>                            |                   | 0    |         | 3.9  | V    |  |

# **DC Characteristics** at Ta = -30 to +70 °C, $DV_{DD}33 = 3.3V \pm 0.3V$ (other than low-voltage support models), $DV_{DD}15 = 1.5 \pm 10\%$

|                                              |                 | 0 1111                                                                   |                        | Ratings |                       |          |

|----------------------------------------------|-----------------|--------------------------------------------------------------------------|------------------------|---------|-----------------------|----------|

| Parameter                                    | Symbol          | Conditions                                                               | min                    | typ     | max                   | unit     |

| Input high-level voltage                     | V <sub>IH</sub> | CMOS level inputs (5V withstand voltage pin)                             | 0.8DV <sub>DD</sub> 33 |         | 5.5                   | ٧        |

|                                              |                 | CMOS level inputs (2.4V to 3.6V or non-5V withstand voltage pin)         | 0.8DV <sub>DD</sub> 33 |         | DV <sub>DD</sub> 33   | ٧        |

|                                              |                 | CMOS level Schmitt inputs (5V withstand voltage pin)                     | 2.0                    |         | 5.5                   | >        |

|                                              |                 | CMOS level Schmitt inputs (2.4V to 3.6V or non-5V withstand voltage pin) | 0.8DV <sub>DD</sub> 33 |         | DV <sub>DD</sub> 33   | >        |

| Input low-level voltage                      | V <sub>IL</sub> | CMOS level inputs                                                        | 0                      |         | 0.2V <sub>DD</sub> 33 | <b>V</b> |

|                                              |                 | CMOS level Schmitt inputs                                                | 0                      |         | 0.2V <sub>DD</sub> 33 | <b>V</b> |

| Input high-level current                     | lн              | $V_I = DV_{DD}$                                                          |                        |         | 10                    | μΑ       |

|                                              |                 | V <sub>I</sub> =DV <sub>DD</sub> , with pull-down resistance             |                        | 100     |                       | μΑ       |

| Input low-level current                      | I <sub>IL</sub> | V <sub>I</sub> =V <sub>SS</sub>                                          | -10                    |         |                       | μА       |

| Output high-level voltage                    | Voн             | CMOS (Pin G/I: I <sub>OH</sub> =-4mA, Pin F: when set to -6mA)           | DV <sub>DD</sub> -0.6  |         |                       | V        |

| Output low-level voltage                     | V <sub>OL</sub> | CMOS                                                                     |                        |         | 0.4                   | V        |

| Output leak current                          | loz             | At output of high-impedance                                              | -10                    |         | 10                    | μΑ       |

| Pull-down resistor                           | R <sub>DN</sub> | 3.0V to 3.6V                                                             |                        | 58      |                       | kΩ       |

|                                              |                 | 2.4V to 3.6V                                                             |                        | 70      |                       | kΩ       |

| Dynamic supply current (DV <sub>DD</sub> 33) | IDDOP           | Outputs open, tck=27MHz<br>natural image, Ta=25°C                        |                        | 13      |                       | mA       |

| Dynamic supply current (DV <sub>DD</sub> 15) |                 | tck=27MHz: natural image, Ta=25°C                                        |                        | 7       |                       | mA       |

| Dynamic supply current (AV <sub>DD</sub> 33) |                 | tck=27MHz: natural image, Ta=25°C                                        |                        | 52      |                       | mA       |

| Dynamic supply current (AV <sub>DD</sub> 15) |                 | tck=27MHz: natural image, Ta=25°C                                        |                        | 0.1     |                       | mA       |

| Static supply current: *1                    | IDDST           | Outputs open, V <sub>I</sub> =V <sub>SS</sub> , Ta=25°C                  |                        | 10      |                       | μΑ       |

<sup>\*1:</sup> There is an input terminal which builds in pull down resistance. Please note that there is no guarantee about static consumption current depending on circuit composition.

# A/D Convertor Characteristics at $Ta=25^{\circ}C,\,DV_{SS}=0V,\,AV_{SS}=0V$

| Parameter                                                           | Symbol/pin       | min | typ  | max | Unit |

|---------------------------------------------------------------------|------------------|-----|------|-----|------|

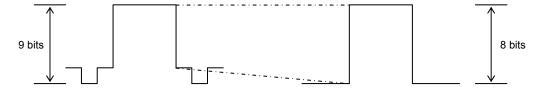

| ADC resolution                                                      |                  |     |      | 9   | bit  |

| Clock frequency                                                     | Fclk             | 5   |      | 40  | MHz  |

| SNR                                                                 |                  |     | 48   |     | dB   |

| DNL                                                                 |                  |     | ±0.5 |     | LSB  |

| INL                                                                 |                  |     | ±1.0 |     | LSB  |

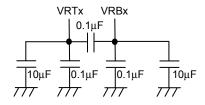

| External capacitance                                                |                  |     |      |     |      |

| Analog input coupling capacitance                                   | Analog video pin |     | 0.1  |     | μF   |

| Top level reference fixed capacitance                               | VRTx pin         |     | 0.01 |     | μF   |

| Bottom level reference capacitance                                  | VRBx pin         |     | 0.01 |     | μF   |

| Analog input frequency                                              | FAIN             |     |      | 10  | MHz  |

| Analog input amplitude                                              |                  |     | 1.0  |     | V    |

| ADC stabilization time (time required to restore from standby mode) |                  |     |      | 500 | ms   |

| PLL lock time                                                       |                  |     |      | 3   | ms   |

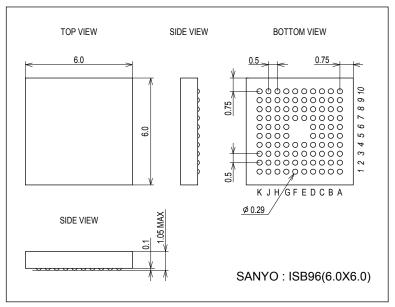

# **Package Dimensions: FBGA96**

unit: mm (typ)

3387

# **Pin Assignment**

LC74950BG

Top view

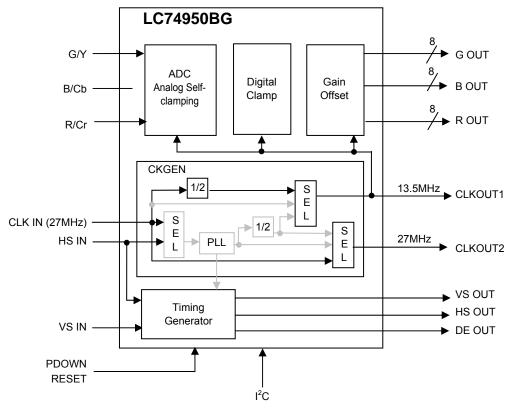

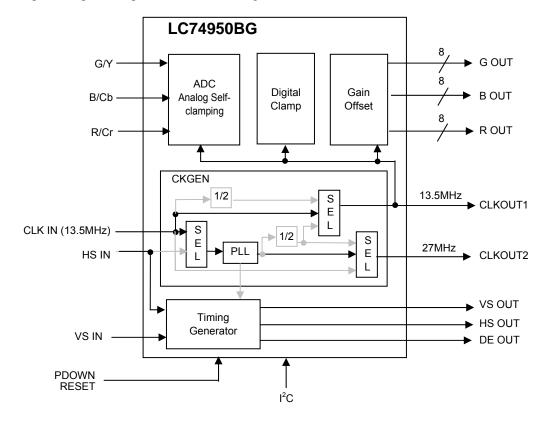

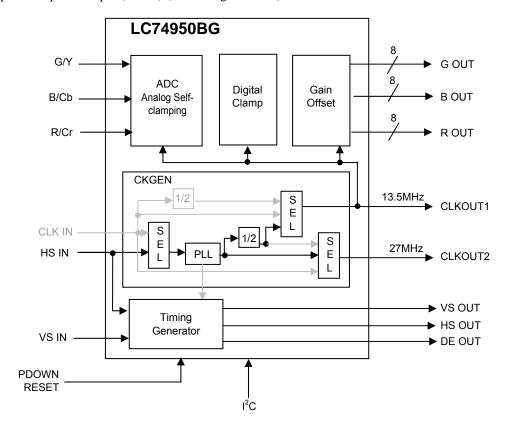

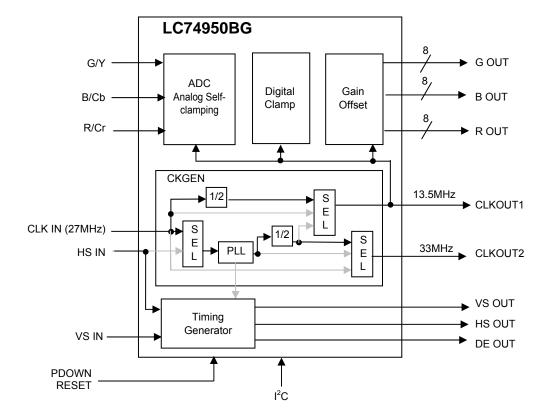

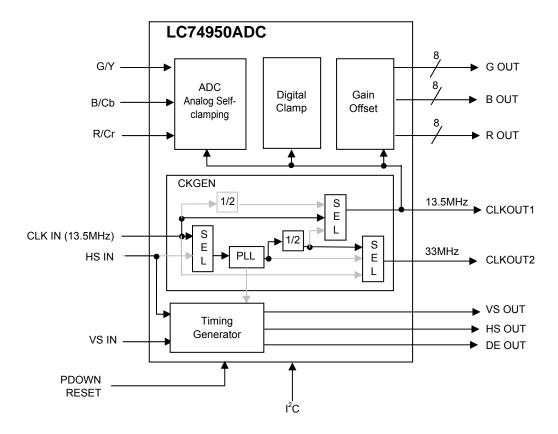

# **Block Diagram**

# LC74950BG

# **Pin Functions**

| Pin No.  | Pin symbol               | In/outpu | ut format | Conn        | ecting  | Remarks                                                |

|----------|--------------------------|----------|-----------|-------------|---------|--------------------------------------------------------|

| FIII NO. | Fill Syllibol            | I/O      | Format    | destination |         | Remains                                                |

| A1       | ADC2AV <sub>SS</sub> 33  | Р        |           | GND         | Analog  | It must be treated in the same way as an NC pin.       |

| A2       | CBOUT0                   | I/O      | I         | 3.3V CMOS   | Digital | Video signal output Cb or B (LSB)                      |

| А3       | CBOUT2                   | I/O      | 1         | 3.3V CMOS   | Digital | Video signal output Cb or B                            |

| A4       | CBOUT4                   | I/O      | - 1       | 3.3V CMOS   | Digital | Video signal output Cb or B                            |

| A5       | CBOUT6                   | I/O      | I         | 3.3V CMOS   | Digital | Video signal output Cb or B                            |

| A6       | PDWN                     | 1        | В         | 3.3V CMOS   | Digital | Power DOWN "L" Power DOWN                              |

| A7       | AV <sub>SS</sub> 33_PLL  | Р        |           | GND         | Analog  |                                                        |

| A8       | CHRGPMP                  | 0        | Α         |             | Analog  | Filter input                                           |

| A9       | AV <sub>DD</sub> 33_PLL  | Р        |           | 3.3V        | Analog  | PLL power supply                                       |

| A10      | DV <sub>DD</sub> 15      | Р        |           | 1.5V        | Digital |                                                        |

| B1       | VRT2                     | 1        | Α         |             | Analog  | Top level reference voltage connection pin for ADC2    |

| B2       | ADC2AV <sub>SS</sub> 33  | Р        |           | GND         | Analog  |                                                        |

| В3       | CBOUT1                   | I/O      | I         | 3.3V CMOS   | Digital | Video signal output Cb or B                            |

| B4       | CBOUT3                   | I/O      | I         | 3.3V CMOS   | Digital | Video signal output Cb or B                            |

| B5       | CBOUT5                   | I/O      | I         | 3.3V CMOS   | Digital | Video signal output Cb or B                            |

| В6       | CBOUT7                   | I/O      | I         | 3.3V CMOS   | Digital | Video signal output Cb or G (MSB)                      |

| В7       | DV <sub>SS</sub>         | Р        |           | GND         | Digital |                                                        |

| В8       | AV <sub>SS</sub> 33_PLL  | Р        |           | GND         | Analog  |                                                        |

| В9       | DV <sub>DD</sub> 15      | Р        |           | 1.5V        | Digital | It must be treated in the same way as an NC pin.       |

| B10      | HSIN                     | 1        | В         | 3.3V CMOS   | Digital | Horizontal synchronizing signal                        |

| C1       | CRIN1                    | 1        | Α         | to 1.0Vp-p  | Analog  | Analog CR or R input (ADC2)                            |

| C2       | VRB2                     | 1        | Α         |             | Analog  | Bottom level reference voltage connection pin for ADC2 |

| C3       | ADC2AV <sub>DD</sub> 33A | Р        |           | 3.3V        | Analog  |                                                        |

| C4       | DV <sub>SS</sub>         | Р        |           | GND         | Digital |                                                        |

| C5       | DV <sub>SS</sub>         | Р        |           | GND         | Digital |                                                        |

| C6       | DV <sub>SS</sub>         | Р        |           | GND         | Digital |                                                        |

| C7       | DV <sub>DD</sub> 15      | Р        |           | 1.5V        | Digital |                                                        |

| C8       | DV <sub>DD</sub> 15      | Р        |           | 1.5V        | Digital |                                                        |

| C9       | VSIN                     | 1        | В         | 3.3V CMOS   | Digital | Vertical synchronizing signal                          |

| C10      | RESET                    | 1        | В         | 3.3V CMOS   | Digital | System reset "L" reset                                 |

Continued on next page.

| Continued | from | preceding | nage  |

|-----------|------|-----------|-------|

| Commuca   | пош  | Dieceume  | Dage. |

| Pin No.   | Pin symbol               | In/outp       | ut format | Conne      | =       | Remarks                                                                      |

|-----------|--------------------------|---------------|-----------|------------|---------|------------------------------------------------------------------------------|

| 1 111110. | T III Symbol             | I/O           | Format    | destir     | nation  | remains                                                                      |

| D1        | VRT1                     | I             | Α         |            |         | Top level reference voltage connection pin for ADC1                          |

| D2        | CRIN0                    | I             | Α         | to 1.0Vp-p | Analog  | Analog CR or R input (ADC2)                                                  |

| D3        | ADC1AV <sub>SS</sub> 33  | Р             |           | GND        | Analog  |                                                                              |

| D4        | DV <sub>SS</sub>         | Р             |           | GND        | Digital |                                                                              |

| D5        | DV <sub>SS</sub>         | Р             |           | GND        | Digital |                                                                              |

| D6        | DV <sub>SS</sub>         | Р             |           | GND        | Digital |                                                                              |

| D7        | DV <sub>DD</sub> 15      | Р             |           | 1.5V       | Digital |                                                                              |

| D8        | DV <sub>DD</sub> 15      | Р             |           | 1.5V       | Digital |                                                                              |

| D9        | CLKOUT2                  | 0             | F         | 3.3V CMOS  | Digital | CLKOUT1×2 output or PLL output                                               |

| D10       | CLKOUT1                  | 0             | F         | 3.3V CMOS  | Digital | Datasynchronization clock output                                             |

| E1        | CBIN1                    | 1             | Α         | to 1.0Vp-p | Analog  | Analog CB or B input (ADC1)                                                  |

| E2        | VRB1                     | I             | Α         |            |         | Bottom level reference voltage connection pin for ADC1                       |

| E3        | ADC1AV <sub>DD</sub> 33A | Р             |           | 3.3V       | Analog  |                                                                              |

| E4        | $DV_SS$                  | Р             |           | GND        | Digital |                                                                              |

| E7        | DV <sub>DD</sub> 15      | Р             |           | 1.5V       | Digital |                                                                              |

| E8        | I <sup>2</sup> CSEL      | I             | С         | 3.3V CMOS  |         | I <sup>2</sup> C slave addresses L=0×98, H=0×9A                              |

| E9        | SCL                      | I             | D         |            | Digital |                                                                              |

| E10       | COAST                    | I             | В         | 3.3V CMOS  | Digital | Connected to GND                                                             |

| F1        | VRT0                     | 1             | Α         |            | Analog  | Top level reference voltage connection pin for ADC0                          |

| F2        | CBIN0                    | I             | Α         | to 1.0Vp-p | Analog  | Analog CB or B input (ADC1)                                                  |

| F3        | ADC0AV <sub>SS</sub> 33  | Р             |           | GND        | Analog  |                                                                              |

| F4        | DV <sub>SS</sub>         | Р             |           | GND        | Digital |                                                                              |

| F7        | DV <sub>DD</sub> 15      | Р             |           | 1.5V       | Digital |                                                                              |

| F8        | TEST                     | I             | Н         | 3.3V CMOS  | Digital | Test pin (normally fixed low)                                                |

| F9        | SDA                      | I/O           | G         |            | Digital |                                                                              |

| F10       | CLKIN                    | 1             | D         | 3.3V CMOS  | Digital | System clock (Must be connected to GND when not to be used)                  |

| G1        | YGIN1                    | I             | Α         | to 1.0Vp-p | Analog  | Analog Y or G input (ADC0)                                                   |

| G2        | VRB0                     | I             | Α         |            | Analog  | Bottom level reference voltage connection pin for ADC0                       |

| G3        | ADC0AV <sub>DD</sub> 33  | Р             |           | 3.3V       | Analog  |                                                                              |

| G4        | SCANEN                   | I             | Н         | 3.3V CMOS  | Digital | Test pin (normally, Lo)                                                      |

| G5        | DV <sub>DD</sub> 33      | Р             |           | 3.3V       | Digital |                                                                              |

| G6        | DV <sub>DD</sub> 33      | Р             |           | 3.3V       | Digital |                                                                              |

| G7        | DV <sub>DD</sub> 33      | Р             |           | 3.3V       | Digital |                                                                              |

| G8        | DV <sub>DD</sub> 33      | Р             |           | 3.3V       | Digital |                                                                              |

| G9        | HSOUT                    | I/O           | I         | 3.3V CMOS  | Digital | Horizontal synchronizing signal                                              |

| G10       | VSOUT                    | I/O           | I         | 3.3V CMOS  | Digital | Vertical synchronizing signal                                                |

| H1        | АТВ                      | 0             | А         |            |         | Analog output for testing the ADC. It must be held open when not to be used. |

| H2        | YGIN0                    | 1             | Α         | to 1.0Vp-p | Analog  | Analog Y or G input (ADC0)                                                   |

| НЗ        | AV <sub>DD</sub> 15_OSC  | Р             |           | 1.5V       | Analog  | Power supply for the RC oscillator                                           |

| H4        | SCANMOD                  | I             | Н         | 3.3V CMOS  | Digital | Test pin (normally, Lo)                                                      |

| H5        | DV <sub>DD</sub> 33      | Р             |           | 3.3V       | Digital |                                                                              |

| H6        | DV <sub>DD</sub> 33      | Р             |           | 3.3V       | Digital |                                                                              |

| H7        | DV <sub>DD</sub> 33      | P             |           | 3.3V       | Digital |                                                                              |

| H8        | DV <sub>DD</sub> 33      | <u>.</u><br>Р |           | 3.3V       | Digital |                                                                              |

| H9        | CROUT7                   | I/O           | 1         | 3.3V CMOS  | Digital | Video signal output Cr or R (MSB)                                            |

| H10       | DEOUT                    | I/O           | i         | 3.3V CMOS  | Digital | Data enable. It must be held open when not to be used.                       |

Continued on next page.

Continued from preceding page.

| from preceding pag    | 36.                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                    |                  |                  |                                                     |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|-----------------------------------------------------|

| Pin symbol            | ·                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                    |                  | J                | Remarks                                             |

|                       | I/O                                                                                                                                                     | Format                                                                                                                                                                                                                                                                                                                                                             | destir           | lation           |                                                     |

| SVO                   | 0                                                                                                                                                       | Α                                                                                                                                                                                                                                                                                                                                                                  | to 1.0Vp-p       | Analog           | Test pin. It must be held open when not to be used. |

| AV <sub>SS</sub> _OSC | Р                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                    | GND              | Analog           |                                                     |

| YGOUT1                | I/O                                                                                                                                                     | I                                                                                                                                                                                                                                                                                                                                                                  | 3.3V CMOS        | Digital          | Video signal output Y or G                          |

| YGOUT7                | I/O                                                                                                                                                     | I                                                                                                                                                                                                                                                                                                                                                                  | 3.3V CMOS        | Digital          | Video signal output Y or G (MSB)                    |

| YGOUT4                | I/O                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                  | 3.3V CMOS        | Digital          | Video signal output Y or G                          |

| CROUT0                | I/O                                                                                                                                                     | I                                                                                                                                                                                                                                                                                                                                                                  | 3.3V CMOS        |                  | Video signal output Cr or R (LSB)                   |

| CROUT3                | I/O                                                                                                                                                     | I                                                                                                                                                                                                                                                                                                                                                                  | 3.3V CMOS        | Digital          | Video signal output Cr or R                         |

| CROUT5                | I/O                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                  | 3.3V CMOS        | Digital          | Video signal output Cr or R                         |

| DV <sub>DD</sub> 33   | Р                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                    | 3.3V             | Digital          |                                                     |

| CROUT6                | I/O                                                                                                                                                     | I                                                                                                                                                                                                                                                                                                                                                                  | 3.3V CMOS        | Digital          | Video signal output Cr or R                         |

| AV <sub>SS</sub> _OSC | Р                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                    | GND              | Analog           | It must be treated in the same way as an NC pin.    |

| YGOUT0                | I/O                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                  | 3.3V CMOS        | Digital          | Video signal output Y or G (LSB)                    |

| YGOUT2                | I/O                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                  | 3.3V CMOS        | Digital          | Video signal output Y or G                          |

| YGOUT3                | I/O                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                  | 3.3V CMOS        | Digital          | Video signal output Y or G                          |

| YGOUT5                | I/O                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                  | 3.3V CMOS        | Digital          | Video signal output Y or G                          |

| YGOUT6                | I/O                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                  | 3.3V CMOS        | Digital          | Video signal output Y or G                          |

| CROUT1                | I/O                                                                                                                                                     | I                                                                                                                                                                                                                                                                                                                                                                  | 3.3V CMOS        |                  | Video signal output Cr or R                         |

| CROUT2                | I/O                                                                                                                                                     | I                                                                                                                                                                                                                                                                                                                                                                  | 3.3V CMOS        | Digital          | Video signal output Cr or R                         |

| CROUT4                | I/O                                                                                                                                                     | ı                                                                                                                                                                                                                                                                                                                                                                  | 3.3V CMOS        | Digital          | Video signal output Cr or R                         |

| DV <sub>DD</sub> 33   | Р                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                    | 3.3V             | Digital          | It must be treated in the same way as an NC pin.    |

|                       | Pin symbol SVO AVSS_OSC YGOUT1 YGOUT7 YGOUT4 CROUT0 CROUT3 CROUT5 DVDD33 CROUT6 AVSS_OSC YGOUT0 YGOUT2 YGOUT3 YGOUT5 YGOUT6 CROUT1 CROUT5 CROUT1 CROUT1 | Pin symbol I/O  SVO O  AVSS_OSC P  YGOUT1 I/O  YGOUT7 I/O  YGOUT4 I/O  CROUT3 I/O  CROUT5 I/O  DVDD33 P  CROUT6 I/O  AVSS_OSC P  YGOUT0 I/O  YGOUT0 I/O  CROUT5 I/O  DVDD33 IP  CROUT6 I/O  AVSS_OSC P  YGOUT0 I/O  YGOUT2 I/O  YGOUT3 I/O  YGOUT3 I/O  CROUT5 I/O  CROUT1 I/O  CROUT1 I/O  CROUT1 I/O  CROUT1 I/O  CROUT2 I/O  CROUT1 I/O  CROUT1 I/O  CROUT2 I/O | In/output format | In/output format | Description                                         |

# Pin Type

| In/Output form | Function                                                         | Equivalent circuit | Application Terminal                                                                                                                                                                                                |

|----------------|------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| А              | Analog input/output                                              | <u></u>            | CHRGPMP, CRIN0, CRIN1, VRT2, VRB2, CBIN0, CBIN1, VRT1, VRB1, YGIN0, YGIN1, VRT0, VRB0, SVO, ATB                                                                                                                     |

| В              | 5V withstand<br>Schmitt trigger<br>CMOS input *                  |                    | HSIN, PDWN, VSIN, COAST, RESET                                                                                                                                                                                      |

| С              | 5V withstand<br>CMOS input with built-in<br>pull-down resistor * |                    | I <sup>2</sup> CSEL                                                                                                                                                                                                 |

| D              | 5V withstand<br>CMOS input *                                     |                    | CLKIN, SCL                                                                                                                                                                                                          |

| F              | 12mA switching<br>3-STATE drive<br>CMOS output                   |                    | CKOUT1, CKOUT2                                                                                                                                                                                                      |

| G              | 8mA 3-STATE drive<br>CMOS input/output *<br>(5V withstand)       |                    | SDA                                                                                                                                                                                                                 |

| Н              | CMOS input with built-in pull-down resistor                      |                    | TEST, SCANEN, SCANMOD                                                                                                                                                                                               |

| I              | 8mA 3-STATE drive<br>CMOS input/output                           |                    | HSOUT, VSOUT, DEOUT, CROUTO, CROUT1, CROUT2, CROUT3, CROUT4, CROUT5, CROUT6, CROUT7, CBOUT4, CBOUT5, CBOUT6, CBOUT7, CBOUT0, CBOUT1, CBOUT2, CBOUT3, YGOUT0, YGOUT1, YGOUT2, YGOUT3, YGOUT4, YGOUT5, YGOUT6, YGOUT7 |

<sup>\*: 5</sup>V Tolerant

#### **Pin Connection**

#### 1) ADC and its peripherals

VRTx: VRT0, VRT1, VRT2 VRBx: VRB0, VRB1, VRB2

YGIN0, YGIN1 CRIN0, CRIN1 CBIN0, CBIN1

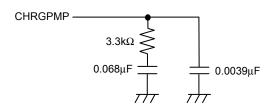

#### 2) PLL and its pereipherals

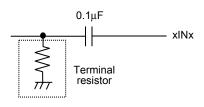

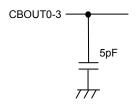

#### 3) Output pin (recommended)

#### 4) Power supplies

The analog A\*\* and digital D\*\* power supplies must be supplied separately without fail. In addition, the power supply for the PLL circuit must also be provided separately as it will affect the jitter characteristics of the PLL circuit. For ADC power supply, it is desirable to provide separate power for each of the ADC channel.

AVDD33\_PLL : Must be separated by L components, etc.

ADC2AV<sub>DD</sub>33A: Separating by L components, etc. recommended ADC1AV<sub>DD</sub>33A: Separating by L components, etc. recommended ADC0AV<sub>DD</sub>33A: Separating by L components, etc. recommended

#### 5) Unused pin treatment

YGIN0, 1/CBIN0, 1/CRIN0, 1: Open

PDWN: Pull up

CHRGPMP: Open (when PLL is not in use)

\*\*\*OUT\* (e.g., YGOUT0): Open

HSIN/VSIN: Must always be configured for input. RESET: Must always be configured for input.

COAST: Must be connected to DVSS. TEST, SCANEN, SCANMOD: DVSS

CLKIN: DVSS

HSOUT, VSOUT, DEOUT: Open

SVO, ATB: Open

\* The specified voltage of power must be applied to each of the power supply pin even if it is not to be used (PLL is not to be used, for example).

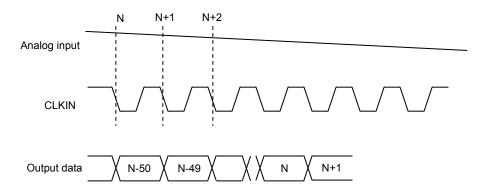

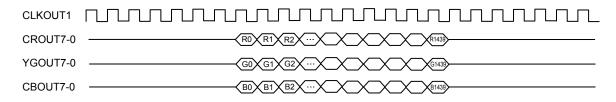

# I/O Data Timing

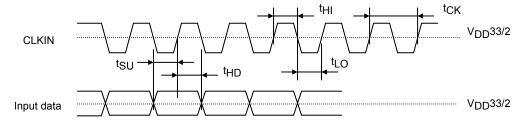

# (1) Input data timing

| Pin name      | Parameter                                               | Symbol          | min | typ | max | unit |

|---------------|---------------------------------------------------------|-----------------|-----|-----|-----|------|

| CLKIN         | Clock cycle                                             | tCK             | 25  |     |     | ns   |

|               | Duty                                                    |                 |     | 50  |     | %    |

|               | Input data setup time (DV <sub>DD</sub> 33=3.0 to 3.6V) | t <sub>SU</sub> | 3.0 |     |     | ns   |

| LICINI VICINI | Input data setup time (DV <sub>DD</sub> 33=2.4 to 3.6V) | t <sub>SU</sub> | 3.0 |     |     | ns   |

| HSIN, VSIN    | Input data hold time (DV <sub>DD</sub> 33=3.0 to 3.6V)  | tHD             | 3.0 |     |     | ns   |

|               | Input data hold time (DV <sub>DD</sub> 33=2.4 to 3.6V)  | t <sub>HD</sub> | 3.0 |     |     | ns   |

<sup>\*:</sup> The recommended duty cycle of input clock is 50%

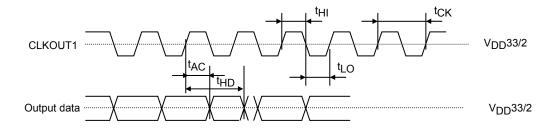

# (2) Output data timing

| Pin name                | Parameter                            | Symbol          | min | typ | max | unit |

|-------------------------|--------------------------------------|-----------------|-----|-----|-----|------|

| CLKOUT1                 | Clock cycle                          | t <sub>CK</sub> | 25  |     |     | ns   |

|                         | Duty                                 |                 |     | 50  |     | %    |

|                         | Output data delay time (3.0 to 3.6V) | <sup>t</sup> AC | 0   |     | 2.0 | ns   |

| YGOUT*, CBOUT*, CROUT*, | Output data delay time (2.4 to 3.6V) | <sup>t</sup> AC | 0   |     | 3.0 | ns   |

| HSOUT ,VSOUT, DEOUT     | Output data hold time (3.0 to 3.6V)  | t <sub>HD</sub> | 3.0 |     |     | ns   |

|                         | Output data hold time (2.4 to 3.6V)  | <sup>t</sup> HD | 3.0 |     |     | ns   |

<sup>\*</sup> When CLKOUT1 is set to the forward rotation output.

# **Timing Chart**

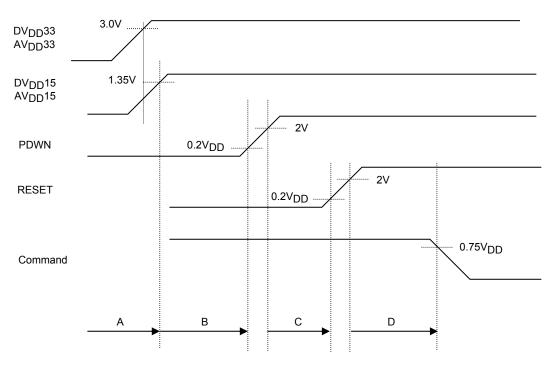

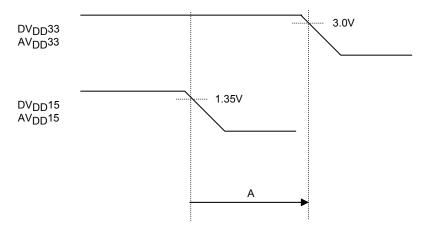

Note: For the initial setting of the registers

#### **Details of the functions**

#### 1. Selection of input pins

Registers related to the selection of input pins

| Name   | Functions                  | Sub address | bit width |

|--------|----------------------------|-------------|-----------|

| AINSEL | Video input select control | 0x22        | 1         |

|        | Analog video input select  |             |           |

|        | 0: YGIN0/CBIN0/CRIN0       |             |           |

|        | 1: YGIN1/CBIN1/CRIN1       |             |           |

#### • Video input selector function

The video input signal used for actual processing can be selected out of the two systems of video input.

AINSEL=0: YGIN0/CBIN0/CRIN0 AINSEL=1: YGIN1/CBIN1/CRIN1

#### 2. Input format

Registers related to the selection of the input format

| Name     | Functions                                                                                  | Sub address | bit width |

|----------|--------------------------------------------------------------------------------------------|-------------|-----------|

| SELYCRGB | This register switches between the YCbCr input and RGB input.                              | 0x14        | 1         |

|          | 0: YCbCr, 1: RGB                                                                           |             |           |

| SYNCON   | For YCbCr input, this register, by cutting off the digitally clamped sync component of the | 0x1B        | 1         |

|          | Y video signal, sets the applicable gain adjustment function to ON or OFF.                 |             |           |

|          | This must be set to 0 for the RGB input (SELYCRGB=1).                                      |             |           |

|          | 0: ON, 1: OFF                                                                              |             |           |

All the inputs listed below can be connected to the analog ports. It is also possible to switch between the inputs of two systems and use the one selected.

YCbCr/YPbPr input (480I/576I, 480P/576P): Component input

RGB: RGB input

# 3. Operating modes

Register related to the selection of operating mode

| Name   | Functions                               | Sub address | bit width |

|--------|-----------------------------------------|-------------|-----------|

| CLKSEL | Operating mode selection                | 0x00        | 3         |

|        | 000: External clock mode (PLL not used) |             |           |

|        | 001: External clock mode (PLL used)     |             |           |

|        | 010: H lock PLL mode                    |             |           |

|        | 011: Panel PLL mode <1>                 |             |           |

|        | 100: Panel PLL mode <2>                 |             |           |

1) External clock mode (PLL not used: CLKOUT1=CLKIN/2, CLKOUT2=CLKIN) Example: Component input (NTSC) (down sample)

2) External clock mode (PLL used: CLKOUT1=CLKIN, CLKOUT2=CLKIN\*2) Example: Component input (NTSC) (2× clock generation)

# 3) H-lock PLL mode (PLL used: CLKOUT1=HS/Divide, CLKOUT2=CLKOUT1\*2) Example: Component input (NTSC) (2× clock generation)

#### 4) ADC/PLL independent mode <1>

(External clock input, PLL configured independently: CLKOUT1=CLKIN/2, CLKOUT2=CLKIN/In-Divide\*Out-Divide)

Example: Component (ADC down sample), PLL: Generation of separate system clock

#### 5) ADC/PLL independent mode <2>

(External clock input, PLL configured separately: CLKOUT1=CLKIN, CLKOUT2=CLKIN/In-Divide\*Out-Divide) Example: Component (ADC down sample), PLL: Generation of separate system clock

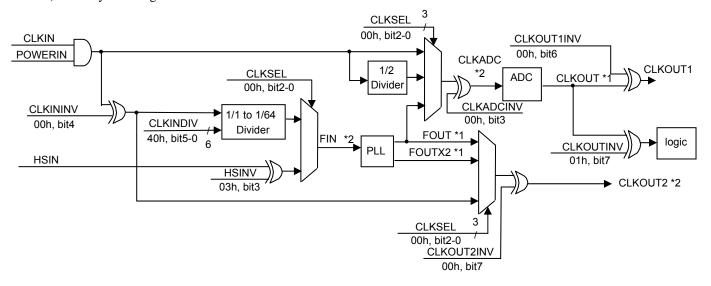

# 4. Clock system

#### 1) Clock system diagram

#### \*1 Explanation of signals

FOUT: A clock generated in the PLL circuit and synchronized with the reference signal (FIN). The frequency of FIN and PLL divider value (HPLDIV, 28h-29h, bits 15-0) determine the frequency of FOUT.

FOUTX2: A clock generated in the PLL circuit and synchronized with the reference signal (FIN). The frequency of

FOUTX2 is two times of the frequency of FOUT.

CLKOUT: A clock generated in the ADC. To output the clock it is necessary to adjust the phase of the sampling clock

(CLKADC) in order that the rising edge of the clock does not occur near the change point of the ADC

sampled data.

Registers related to the control of clock

| Name       | Functions                                                                        | Sub address | bit width |

|------------|----------------------------------------------------------------------------------|-------------|-----------|

| CLKININV   | This register controls the inversion of CLKIN when the CLKIN input is used as a  | 0x00        | 2         |

|            | reference clock to PLL.                                                          |             |           |

|            | 0: Uses CLKIN in its original form                                               |             |           |

|            | 1: Uses CLKIN in its inverted form                                               |             |           |

| HSINV      | This register controls the inversion of HSIN input. The HSIN must be used in its | 0x02        | 1         |

|            | inverted form when the polarity of HSIN input is negative.                       |             |           |

|            | 0: Original form (when HSIN is positive)                                         |             |           |

|            | 1: Inverted form (when HSIN is negative)                                         |             |           |

| CLKINDIV   | This register sets the frequency division ratio of CLKIN to an arbitrary value   | 0x40        | 6         |

|            | (1/1 to1/64) when the CLKIN is used as a reference clock to PLL.                 |             |           |

|            | 1/(CLKINDIV[5:0]+1) division                                                     |             |           |

| CLKSEL     | This register selects the operating mode.                                        | 0x00        | 3         |

|            | 000: (External clock mode (PLL not used)                                         |             |           |

|            | 001: (External clock mode (PLL used)                                             |             |           |

|            | 010: H-lock PLL mode                                                             |             |           |

|            | 011: Panel PLL mode <1>                                                          |             |           |

|            | 100: Panel PLL mode <2>                                                          |             |           |

| CLKADCINV  | This register controls the inversion of the ADC sampling clock (CLKADC).         | 0x00        | 1         |

|            | 0: Uses CLKADC in its original form                                              |             |           |

|            | 1: Uses CLKADC in its inverted form                                              |             |           |

| CLKOUTINV  | This register controls the inversion of the ADC-generated clock. (CLKOUT).       | 0x01        | 1         |

|            | 0: Uses CLKOUT in its original form                                              |             |           |

|            | 1: Uses CLKOUT in its inverted form                                              |             |           |

| CLKOUT1INV | This register controls the inversion of CLKOUT (video clock output).             | 0x00        | 1         |

|            | 0: Original form                                                                 |             |           |

|            | 1: Inverted form                                                                 |             |           |

| CLKOUT2INV | This register controls the inversion of CLKOUT2 (panel clock output).            | 0x00        | 1         |

|            | 0: Original form                                                                 |             |           |

|            | 1: Inverted form                                                                 |             |           |

\*2 Clock control register (CLKSEL, 00h, bits 2-0) specifications

| CLKSEL<br>(bit2-0) | CLKADC*3 (ADC sampling clock) | FIN<br>(PLL reference) | CLKOUT2<br>(Clock output) | Remarks                            |

|--------------------|-------------------------------|------------------------|---------------------------|------------------------------------|

| 000                | CLKIN/2 (13.5MHz)             | L fixed (PLL not used) | CLKIN(27MHz)              | External clock mode (PLL not used) |

| 001                | FOUT (PLL output)             | CLKIN *4               | FOUTX2<br>(PLL output X2) | External clock mode (PLL used)     |

| 010                | FOUT (PLL output)             | HSIN *5                | FOUTX2<br>(PLL output X2) | H-lock PLL mode                    |

| 011                | CLKIN/2                       | CLKIN *4               | FOUT (PLL output)         | Panel PLL mode <1>                 |

| 100                | CLKIN                         | CLKIN *4               | FOUT (PLL output)         | Panel PLL mode <2>                 |

<sup>\*3:</sup> Register CLKADCINV (00h, bit 3) allows for clock inversion.

<sup>\*4:</sup> Register CLKINDIV (40h, bits 5-0) allows for division of clock frequency (1/1 to 1/64).

<sup>\*5:</sup> Register HSINV (03h, bit 3) allows for HSIN inversion.

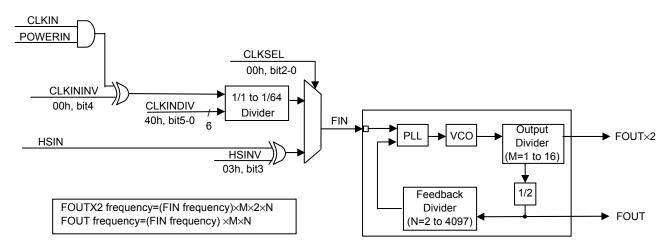

# 2) PLL circuit

This circuit can be used as the H lock or frequency-multiplied clock. It is also possible to use the PLL circuit and analog-digital converter (ADC) independently.

H lock PLL circuit: This makes it possible to generate a clock that is synchronized with the external H sync signal. Frequency-multiplier PLL circuit: This makes it possible to generate clocks that are synchronized with an external clock.

Registers related to the setting of PLL circuit

| Name        | Functions                                                                                | Sub address | bit width |

|-------------|------------------------------------------------------------------------------------------|-------------|-----------|

| CLKININV    | This register controls the inversion of CLKIN when the CLKIN input is used as a          | 0x00        | 2         |

|             | reference clock to PLL.                                                                  |             |           |

|             | 0: Uses CLKIN in its original form                                                       |             |           |

|             | 1: Uses CLKIN in its inverted form                                                       |             |           |

| HSINV       | This register controls the inversion of HSIN input. The HSIN must be used in its         | 0x02        | 1         |

|             | inverted form when the polarity of HSIN input is negative.                               |             |           |

|             | 0: Original form (when HSIN is positive)                                                 |             |           |

|             | 1: Inverted form (when HSIN is negative)                                                 |             |           |

| CLKINDIV    | This register sets the frequency division ratio of CLKIN to an arbitrary value           | 0x40        | 6         |

|             | (1/1 to 1/64) when the CLKIN is used as a reference clock to PLL.                        |             |           |

|             | 1/(CLKINDIV[5:0] 1) division                                                             |             |           |

| CLKSEL      | This register selects the PLL reference input.                                           | 0x00        | 3         |

|             | 000: L fixed (PLL not used)                                                              |             |           |

|             | 001: External clock input (CLKIN)                                                        |             |           |

|             | 010: External Hsync input (HSIN)                                                         |             |           |

|             | 011: External clock input (CLKIN)                                                        |             |           |

|             | 100: External clock input (CLKIN)                                                        |             |           |

| HPLDIV15-12 | This register sets the output divider (M-1, NTSC, 480i=3).                               | 0x28        | 4         |

| HPLDIV11-0  | This register sets the feedback divider (N-2, NTSC, 480i=856).                           | 0x28        | 12        |

|             | H-lock PLL output frequency (1x)=Hsync frequency×N                                       | 0x29        |           |

|             | H-lock PLL output frequency (2x)=Hsync frequency×N×2                                     |             |           |

|             | * After changing the setting, an interval of 3.0ms is required for the H-lock PLL to get |             |           |

|             | stabilized.                                                                              |             |           |

Continued on next page.

Continued from preceding page.

| Name       | Functions                                                                                | Sub address | bit width |

|------------|------------------------------------------------------------------------------------------|-------------|-----------|

| PLLGAIN    | This register switches the setting of Fmin, Fmax, and Gain of the H-lock PLL VCO.        | 0x27        | 3         |

|            | 000: Fmin=60MHz, Fmax=240MHz, Gain=120MHz/V←Standard setting                             |             |           |

|            | 001: Fmin=Standard, Fmax=Standard-20%, Gain=Standard-22.5%                               |             |           |

|            | 010: Fmin=Standard-20%, Fmax=Standard, Gain=Standard+2.5%                                |             |           |

|            | 011: Fmin=Standard-20%, Fmax=Standard-20%, Gain=Standard-20.0%                           |             |           |

|            | 100: Fmin=Standard+20%, Fmax=Standard+10%, Gain=Standard+8.75%                           |             |           |

|            | 101: Fmin=Standard+20%, Fmax=Standard-10%, Gain=Standard-13.75%                          |             |           |

|            | 110: Fmin=Standard, Fmax=Standard+10%, Gain=Standard+11.25%                              |             |           |

|            | 111: Fmin=Standard, Fmax=Standard-10%, Gain=Standard-11.25%                              |             |           |

|            | * After changing the setting, an interval of 3.0ms is required for the H-lock PLL to get |             |           |

|            | stabilized.                                                                              |             |           |

| PLLCTL2    | H-lock PLL power down mode                                                               | 0x27        | 1         |

|            | 0: Normal operation                                                                      |             |           |

|            | 1: H-lock PLL power OFF                                                                  |             |           |

| PLLCTL1    | H-lock PLL Normal Mode FOUT Disable                                                      | 0x27        | 1         |

|            | 0: Normal operation                                                                      |             |           |

|            | 1: H-lock PLL output= L fixed                                                            |             |           |

| CPIS_COAST | These registers set the PLL charge pump constant current                                 | 0x2A        | 4         |

| CPIS_ORG   | (make sure that CPIS_COAST=CPIS_ORG)                                                     |             |           |

|            | 0000: 40μΑ                                                                               |             |           |

|            | 0001: 60μΑ                                                                               |             |           |

|            | 0010: 120μΑ                                                                              |             |           |

|            | 0011: 180μΑ                                                                              |             |           |

|            | 0100: 200μΑ                                                                              |             |           |

|            | 0110: 280μΑ                                                                              |             |           |

|            | 0101: 300μΑ                                                                              |             |           |

|            | 1000: 360μΑ                                                                              |             |           |

|            | 0111: 420μΑ                                                                              |             |           |

|            | 1010: 440μA ←Standard setting                                                            |             |           |

|            | 1100: 520μΑ                                                                              |             |           |

|            | 1001: 540μΑ                                                                              |             |           |

|            | 1110: 600μΑ                                                                              |             |           |

|            | 1011: 660μΑ                                                                              |             |           |

|            | 1101: 780μΑ                                                                              |             |           |

|            | 1111: 900μΑ                                                                              |             |           |

|            | * After changing the setting, an interval of 3.0ms is required for the H-lock PLL to get |             |           |

|            | stabilized.                                                                              |             |           |

PLL setting example (when using as H-lock PLL)

| 3     |        |        | I TOUR I E |        |       |        |       |       | l       |

|-------|--------|--------|------------|--------|-------|--------|-------|-------|---------|

|       | Ref    | CLKSEL | PLLDIV     | PLLDIV | FVCO* | FOUTX2 | FOUT  | CPIS  | PLLGAIN |

|       | [kHz]  | [2:0]  | 15-12      | 11-0   | [MHz] | [MHz]  | [MHz] | [3:0] | [2:0]   |

| NTSC  | 15.734 | 2h     | 3h         | 6B2h   | 216   | (54)   | 27    | Ch    | 0h      |

| NTSC  | 15.734 | 2h     | 7h         | 358h   | 216   | 27     | 13.5  | Ch    | 0h      |

| PAL   | 15.630 | 2h     | 3h         | 6BEh   | 216   | (54)   | 27    | Ch    | 0h      |

| PAL   | 15.630 | 2h     | 7h         | 35Eh   | 216   | 27     | 13.5  | Ch    | 0h      |

| PAL-N | 15.630 | 2h     | 7h         | 35Eh   | 216   | 27     | 13.5  | Ch    | 0h      |

| PAL-M | 15.734 | 2h     | 7h         | 358h   | 216   | 27     | 13.5  | Ch    | 0h      |

| QVGA  | 15.70  | 2h     | Fh         | 1A6h   | 213   | 13.3   | 6.68  | Ch    | 0h      |

| VGA   | 31.5   | 2h     | 3h         | 31Eh   | 201   | (50.4) | 25.2  | Ch    | 0h      |

| WVGA  | 31.0   | 2h     | 3h         | 41Eh   | 262   | (65.4) | 32.7  | Dh    | 0h      |

<sup>\*20</sup>MHz < FVCO < 340MHz

# 5. Timing control

#### 1) DEOUT (enable output) setting

Registers related to the setting of enable

| Name  | Functions                                                                    | Sub address | bit width |

|-------|------------------------------------------------------------------------------|-------------|-----------|

| HBLKS | This register specifies the 1H start position of DEOUT in dot units.         | 0x04        | 12        |

|       | Set value smaller than HBLKE.                                                | 0x05        |           |

| HBLKE | This register specifies the 1H end position of DEOUT in dot units.           | 0x04        | 12        |

|       | Set the value that is larger than HBLKS and does not overlap the next Hsync. | 0x06        |           |

| VBLKS | This register specifies the 1V start position of DEOUT in line units.        | 0x07        | 11        |

|       | Set the value smaller than VBLKE.                                            | 0x08        |           |

| VBLKE | This register specifies the 1V end position of DEOUT in line units.          | 0x07        | 11        |

|       | Set the value that is larger than VBLKS and does not overlap the next Vsync. | 0x09        |           |

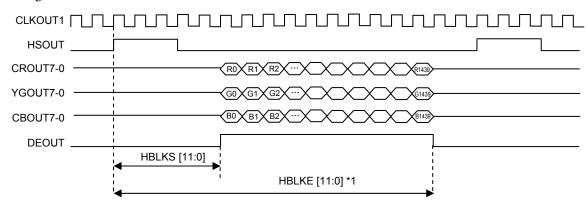

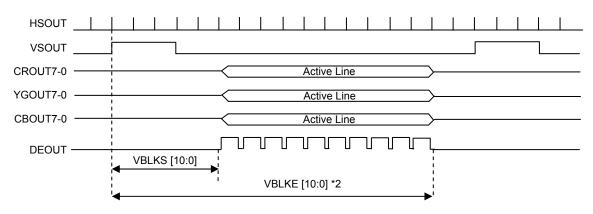

#### • Setting of horizontal enable

\*1: DEOUT is forcibly disabled at the leading edge of the next HSOUT even if HBLKE[11:0] is set with a value larger than the total pixel count of 1H.

#### • Setting of vertical enable

\*2: DEOUT is forced disabled at the leading edge of the next VSOUT even if VBLKE[10:0] is set with a value larger than the total line count of 1V.

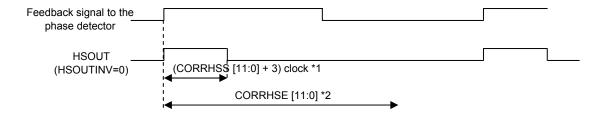

2) SYNC width adjustment (H-lock PLL mode only) of horizontal sync output (HSOUT)

Registers related to SYNC width adjustment of HSOUT

| Name     | Functions                                                                                              | Sub address | bit width |

|----------|--------------------------------------------------------------------------------------------------------|-------------|-----------|

| HSPLLSEL | This register selects the horizontal sync signal (SHOUT) in the H-lock PLL mode.                       | 0x01        | 1         |

|          | 0: HSIN                                                                                                |             |           |

|          | 1: This is the signal that is fed back to the phase detector after dividing the VCO output of the PLL. |             |           |

|          | *: SYNC width adjustment for HSOUT must be turned on when HSPLLSEL is set to 1.                        |             |           |

| CORREN   | This register turns on and off the SYNC width adjustment for HSOUT.                                    | 0x27        | 1         |

|          | 0: OFF, 1: ON                                                                                          |             |           |

| CORRHSS  | SYNC width adjustment register for HSOUT (to be described below)                                       | 0x2B        | 12        |

|          |                                                                                                        | 0x2C        |           |

| CORRHSE  | SYNC width adjustment register for HSOUT (to be described below)                                       | 0x2B        | 12        |

|          |                                                                                                        | 0x2D        |           |

When "1" is set for HSPLLSEL in the H lock PLL mode, the horizontal sync output signal is not HSIN but the signal that is fed back to the phase detector after dividing the VCO output of the PLL. The duty ratio of this signal is 50%, which means when it is to be used as the horizontal sync signal, the sync width must be determined. Furthermore, if "0" is set for HSPLLSEL, the horizontal sync input (HSIN) signal can be output in its original form even in the H lock PLL mode.

- \*1: Clock is expressed in units of CLKOUT1.

- \*2: A value equivalent to about three-fourths of one HSOUT period (640 or so with the NTSC system) must be set as the CORRHSE[11:0] value.

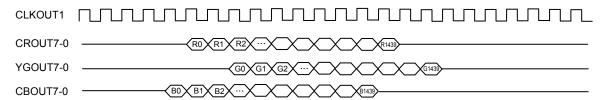

#### 3) Offset adjustment of video output

Registers related to video output offset adjustment

| Name  | Functions                                                                                     | Sub address | bit width |

|-------|-----------------------------------------------------------------------------------------------|-------------|-----------|

| ASYG  | This register adjusts the offset for the Y/G video signal. It is used when the timing between | 0x01        | 3         |

|       | the video signal and sync signals is off.                                                     |             |           |

|       | The Y/G video signal can be shifted by an amount equivalent to (ASYG + 1) locks.              |             |           |

| ASCRR | This register adjusts the offset for the CR/R video signal. It is used when the timing        | 0x02        | 3         |

|       | between the video signal and sync signals is off.                                             |             |           |

|       | The CR/R video signal can be shifted by an amount equivalent to (ASCRR + 1) clocks.           |             |           |

| ASCBB | This register adjusts the offset for the CB/B video signal. It is used when the timing        | 0x02        | 3         |

|       | between the video signal and sync signals is off.                                             |             |           |

|       | The CB/B video signal can be shifted by an amount equivalent to (ASVBBYG + 1) clocks.         |             |           |

| ASVS  | This register adjusts the offset for the VSOUT video signal. It is used when the timing       | 0x03        | 3         |

|       | between the video signal and sync signals is off.                                             |             |           |

|       | The vertical sync signal can be shifted by an amount equivalent to (ASVS + 1) clocks.         |             |           |

| ASHS  | This register adjusts the offset for the HSOUT. It is used when the timing between the        | 0x03        | 3         |

|       | video signal and sync signals is off.                                                         |             |           |

|       | The horizontal sync signal can be shifted by an amount equivalent to (ASHS + 1) clocks.       |             |           |

#### • Offset adjustment method

If the following fluctuations are present between the video outputs when ASYG[2:0] = 000b, ASCRR[2:0] = 000b and ASCBB[2:0] = 000b:

Then, by setting ASYG[2:0] = 010b, ASCRR[2:0] = 000b and ASCBB[2:0] = 011b, the video outputs can be aligned as shown below. The maximum shift width of the video signals is 8 clocks. If the ASVS[2:0] and ASHS[2:0] registers are used in line with the video signal shift, the sync signals (VSOUT and HSOUT) can also be shifted in line with the video signals. (DEOUT is also shifted following HSOUT.)

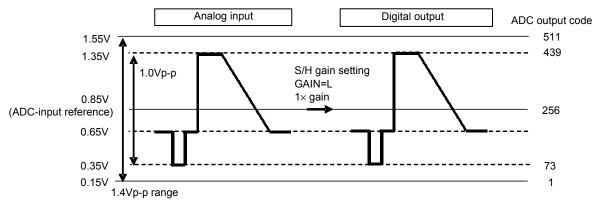

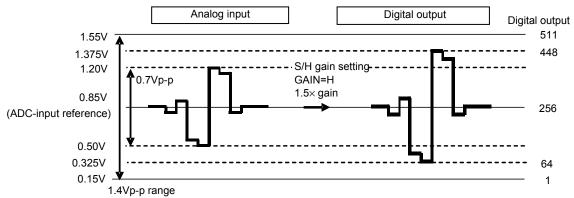

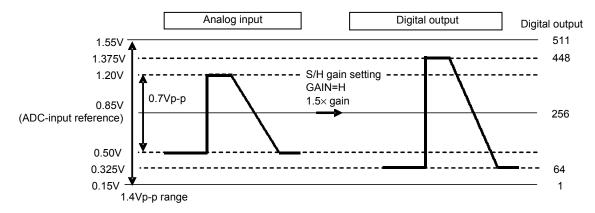

# 6. ADC

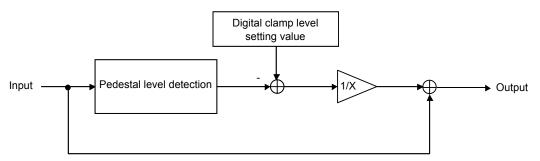

1) Analog clamp Registers related to analog clamp control

| Name           | Functions                                                                             | Sub address | bit width |

|----------------|---------------------------------------------------------------------------------------|-------------|-----------|

| STBB           | This register controls the band gap VREF circuit.                                     | 0x21        | 1         |

|                | 0: Band gap VREF circuit enters standby mode.                                         |             |           |

|                | 1: Band gap VREF circuit enters normal operating mode.                                |             |           |

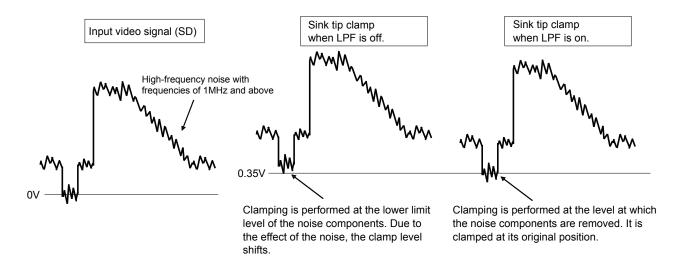

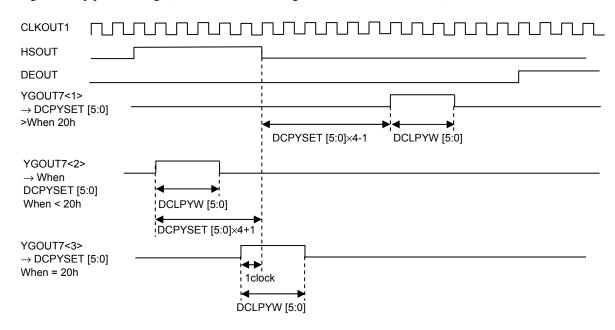

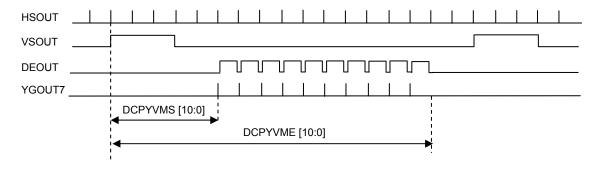

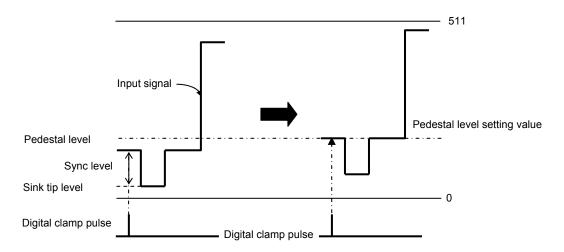

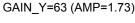

|                | * This must be set in line with the operation mode of ADC.                            |             |           |