## PCI 6520CB Data Book

Preliminary

# PCI 6520CB Data Book

Version 2.0

May 2004

Website:

http://www.plxtech.com

Technical Support:

http://www.plxtech.com/support/

Phone:

408 774-9060

800 759-3735

FAX:

408 774-2169

© 2004 PLX Technology, Inc. All rights reserved.

PLX Technology, Inc., retains the right to make changes to this product at any time, without notice. Products may have minor variations to this publication, known as errata. PLX assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of PLX products.

This device is not designed, intended, authorized, or warranted to be suitable for use in medical or life-support applications, devices, or systems, or other critical applications.

PLX Technology and the PLX logo are registered trademarks and FastLane is a trademark of PLX Technology, Inc.

HyperTransport is a trademark of the HyperTransport Technology Consortium.

Other brands and names are the property of their respective owners.

Order Number: PCI 6520CB-SIL-DB-P1-2.0

Printed in the USA, May 2004

### CONTENTS

| Figuresxi                                                                                                                                                                                                                                                                                                                                             |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Tables                                                                                                                                                                                                                                                                                                                                                |  |  |

| Registersxv                                                                                                                                                                                                                                                                                                                                           |  |  |

| Preface                                                                                                                                                                                                                                                                                                                                               |  |  |

| Supplemental Documentation       xvi         Data Assignment Conventions       xvii         Revision History       xvii                                                                                                                                                                                                                               |  |  |

| Feature Summaryxix                                                                                                                                                                                                                                                                                                                                    |  |  |

| 1. Introduction                                                                                                                                                                                                                                                                                                                                       |  |  |

| 1.1. Company and Product Information       1-1         1.2. FastLane PCI 6000 Bridge Series       1-1         1.2.1. PCI 6520       1-5         1.3. Feature Description       1-5         1.4. Applications       1-6         1.4.1. Multiple Device Expansion       1-6                                                                             |  |  |

| 2. Functional Overview                                                                                                                                                                                                                                                                                                                                |  |  |

| 2.1. General Operation       2-1         2.2. Write Transactions       2-2         2.3. Read Transactions       2-2                                                                                                                                                                                                                                   |  |  |

| 3. Pin Description                                                                                                                                                                                                                                                                                                                                    |  |  |

| 3.1. Pin Summary3-13.2. Pull-Up and Pull-Down Resistor Recommendations.3-23.2.1. PCI Bus Interface Pins.3-23.2.2. Clock-Related Pins3-33.2.3. Reset Pins.3-33.2.4. JTAG/Boundary Scan Pins3-33.2.5. Serial EEPROM Pins.3-33.2.6. GPIO Pins3-33.2.7. Miscellaneous Pins3-33.2.8. System Voltage Pins3-43.3. Power Supply De-Coupling.3-53.4. Pinout3-6 |  |  |

| 4. Clocking                                                                                                                                                                                                                                                                                                                                           |  |  |

| 4.1. Primary and Secondary Clock Inputs4-14.2. Secondary Clock Outputs4-14.2.1. Disabling Secondary Clock Outputs4-14.2.2. Secondary Clock Control4-14.3. Using an External Clock Source4-44.4. Frequency Division Options4-44.5. Running Secondary Port Faster than Primary Port.4-44.6. PLL and Clock Jitter4-4                                     |  |  |

|          | 4.7. Detecting PCI Bus Speed with the Reference Clock         4.8. Primary or Secondary Clock Frequency Measurement |       |

|----------|---------------------------------------------------------------------------------------------------------------------|-------|

| 5. Reset | and Initialization                                                                                                  | 5-1   |

|          | 5.1. PCI-XCAP Connections and Operating Frequency                                                                   | . 5-1 |

|          | 5.1.1. Primary Port PCI-XCAP Connection                                                                             |       |

|          | 5.1.2. Secondary Port PCI-XCAP Connection                                                                           |       |

|          | 5.2. Secondary Bus Mode and Frequency Initialization Sequence                                                       |       |

|          | 5.3. Conventional PCI Mode 66 MHZ Operation                                                                         |       |

|          | 5.4. Reset                                                                                                          |       |

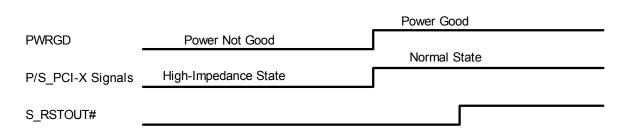

|          | 5.4.1. Power Good Reset                                                                                             | . 5-2 |

|          | 5.4.2. Primary Reset Input                                                                                          | . 5-3 |

|          | 5.4.3. Secondary Reset Output                                                                                       | . 5-3 |

|          | 5.4.4. JTAG Reset                                                                                                   |       |

|          | 5.4.5. Software Resets                                                                                              |       |

|          | 5.4.6. Power Management Internal Reset                                                                              |       |

|          | 5.4.7. Reset Inputs Effect on PCI 6520                                                                              |       |

|          | 5.4.8. Pin States during PWRGD and Primary Reset                                                                    |       |

|          | 5.5. Register Initialization.                                                                                       |       |

|          | 5.5.1. Default Initialization                                                                                       |       |

|          | 5.5.2. Serial EEPROM Initialization                                                                                 |       |

|          | 5.5.3. Host Initialization                                                                                          | . 5-7 |

| 6. Reais | ters                                                                                                                | 6-1   |

| <b>J</b> |                                                                                                                     |       |

|          | 6.1. PCI Configuration Register Address Mapping                                                                     |       |

|          | 6.1.1. PCI Type 1 Header                                                                                            |       |

|          | 6.1.2. Device-Specific                                                                                              |       |

|          | 6.1.2.1. Chip, Diagnostic, and Arbiter Control                                                                      |       |

|          | 6.1.2.2. Primary Flow-Through Control                                                                               |       |

|          | 6.1.2.3. Timeout Control                                                                                            |       |

|          | 6.1.2.5. Prefetch Control                                                                                           |       |

|          | 6.1.2.6. Secondary Flow-Through Control.                                                                            |       |

|          | 6.1.2.7. Buffer and Internal Arbiter Control                                                                        |       |

|          | 6.1.2.8. Test and Serial EEPROM                                                                                     |       |

|          | 6.1.2.9. Timer.                                                                                                     |       |

|          | 6.1.2.10. Primary System Error Event                                                                                |       |

|          | 6.1.2.11. GPIO[3:0]                                                                                                 |       |

|          | 6.1.2.12. Clock Control                                                                                             |       |

|          | 6.1.2.13. Primary System Error Status                                                                               | 6-35  |

|          | 6.1.2.14. Clock Run                                                                                                 | 6-36  |

|          | 6.1.2.15. Private Memory                                                                                            | 6-37  |

|          | 6.1.2.16. Read-Only Register Control                                                                                | 6-38  |

|          | 6.1.2.17. GPIO[7:4]                                                                                                 | 6-39  |

|          | 6.1.2.18. Extended and Smart Prefetch                                                                               |       |

|          | 6.1.2.19. Power Management Capability                                                                               |       |

|          | 6.1.2.20. VPD Capability                                                                                            |       |

|          | 6.1.2.21. PCI-X Capability                                                                                          | 6-50  |

| 7. Seria | EEPROM                                                                                                              | 7-1   |

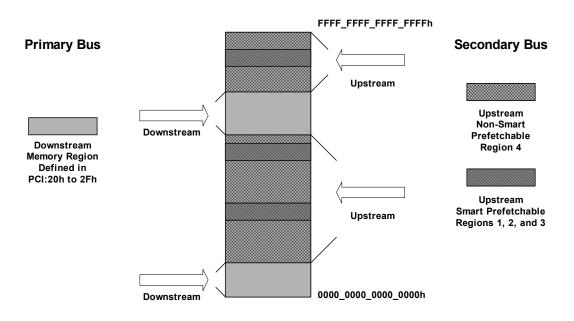

|          | 7.1. Overview                                                                                                       | . 7-1 |

|          | 7.2. Serial EEPROM Access                                                                                           |       |

|          | 7.3. Serial EEPROM Autoload Mode at Reset.                                                                          |       |

|          | 7.4. Serial EEPROM Data Structure                                                                                   | . 7-2 |

|          | 7.4.1. Serial EEPROM Address and Corresponding PCI 6520 Registers                                                   |       |

| 8. PCI Bu | us Operation                                        |

|-----------|-----------------------------------------------------|

|           | 8.1. Conventional PCI Transactions                  |

|           | 8.2. Single Address Phase                           |

|           | 8.3. Dual Address Phase                             |

|           | 8.4. Device Select (DEVSEL#) Generation             |

|           | 8.5. Data Phase                                     |

|           | 8.5.1. Posted Write Transactions                    |

|           | 8.5.2. Memory Write and Invalidate Transactions     |

|           | 8.5.3. Delayed Write Transactions                   |

|           | 8.5.4. Write Transaction Address Boundaries         |

|           | 8.5.5. Buffering Multiple Write Transactions        |

|           | 8.5.6. Read Transactions                            |

|           | 8.5.7. Prefetchable Read Transactions               |

|           |                                                     |

|           | 8.5.8. Non-Prefetchable Read Transactions           |

|           | 8.5.9. Read Prefetch Address Boundaries             |

|           | 8.5.10. Delayed Read Requests                       |

|           | 8.5.11. Delayed Read Completion with Target         |

|           | 8.5.12. Delayed Read Completion on Initiator Bus    |

|           | 8.5.13. Configuration Transactions                  |

|           | 8.5.14. PCI 6520 Type 0 Access                      |

|           | 8.5.15. Type 1-to-Type 0 Translation                |

|           | 8.5.16. Type 1-to-Type 1 Forwarding                 |

|           | 8.5.17. Special Cycles                              |

|           | 8.6. Conventional PCI Mode Transaction Termination  |

|           | 8.6.1. PCI 6520-Initiated Master Termination8-12    |

|           | 8.6.2. Master Abort Received by PCI 6520            |

|           | 8.6.3. Target Termination Received by PCI 6520 8-13 |

|           | 8.6.3.1. Posted Write Target Termination Response   |

|           | 8.6.3.2. Delayed Write Target Termination Response  |

|           | 8.6.3.3. Delayed Read Target Termination Response   |

|           | 8.6.4. PCI 6520-Initiated Target Termination.       |

|           | 8.6.4.1. Target Retry                               |

|           | 8.6.4.2. Target Disconnect                          |

|           | 8.6.4.3. Target Abort                               |

|           |                                                     |

| 9. PCI-X  | Bus Operation                                       |

|           |                                                     |

|           | 9.1. Overview                                       |

|           | 9.2. General Bus Rules                              |

|           | 9.2.1. Initiator Rules                              |

|           | 9.2.2. Target Rules                                 |

|           | 9.2.3. Bus Arbitration Rules                        |

|           | 9.2.4. Configuration Transaction Rules              |

|           | 9.2.5. Parity Error Rules                           |

|           | 9.2.6. Bus Data Width Rules                         |

|           | 9.2.7. Split Transaction Rules                      |

|           | 9.3. PCI-X Sequences                                |

|           | 9.4. ADB and Buffer Size                            |

|           | 9.5. Dependencies between AD and CBE Buses          |

|           | 9.6. PCI-X Command Encoding                         |

|           | 9.7. Attributes                                     |

|           | 9.8. Burst Transactions                             |

|           | 9.8.1. Burst Write and Split Completion             |

|           | 9.8.2. Burst Read Transactions                      |

|           | 9.9. DWORD Transactions                             |

|           | 9.10. Device Select Timing                          |

|           | 9.11. Wait States and Target Initial Latency        |

|           |                                                     |

| 9.12. Split Transactions                                                                                                                                                                                                                                                                                  |      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 9.12.1. Split Completion Transaction                                                                                                                                                                                                                                                                      |      |

| 9.12.2. Immediate Completion by the Completer.                                                                                                                                                                                                                                                            |      |

| 9.12.3. Split Completion Address                                                                                                                                                                                                                                                                          |      |

| 9.12.4. Completer Attributes                                                                                                                                                                                                                                                                              |      |

| 9.12.5. Split Completion Acceptance Requirement                                                                                                                                                                                                                                                           |      |

| 9.12.6. Split Completion Messages                                                                                                                                                                                                                                                                         |      |

| 9.13. PCI-X Mode Transaction Termination.                                                                                                                                                                                                                                                                 |      |

| 9.13.1. PCI 6520 Initiator Termination                                                                                                                                                                                                                                                                    |      |

| 9.13.1.1. Byte Count Disconnection or Satisfaction.                                                                                                                                                                                                                                                       |      |

| 9.13.1.2. PCI 6520 Master Abort Termination                                                                                                                                                                                                                                                               |      |

| 9.13.2. PCI 6520 Target Termination                                                                                                                                                                                                                                                                       |      |

| 9.13.2.1. PCI 6520 Disconnects at Next ADB                                                                                                                                                                                                                                                                |      |

| 9.13.2.2. PCI 6520 Retry Termination                                                                                                                                                                                                                                                                      |      |

| 9.13.2.3. PCI 6520 Split Response Termination                                                                                                                                                                                                                                                             |      |

| 9.14. PCI-X Mode Bus and Data Transfer Width                                                                                                                                                                                                                                                              |      |

| 9.15. Connecting Conventional PCI and PCI-X Interfaces                                                                                                                                                                                                                                                    |      |

| 9.15.1. Conventional PCI Requester, PCI-X Completer                                                                                                                                                                                                                                                       |      |

| 9.15.2. PCI-X Requester, Conventional PCI Completer                                                                                                                                                                                                                                                       |      |

|                                                                                                                                                                                                                                                                                                           |      |

| 10. Address Decoding                                                                                                                                                                                                                                                                                      |      |

|                                                                                                                                                                                                                                                                                                           | 10.1 |

| 10.1. Overview.                                                                                                                                                                                                                                                                                           |      |

| 10.2. Address Ranges                                                                                                                                                                                                                                                                                      |      |

| 10.2.1. I/O Address Decoding                                                                                                                                                                                                                                                                              |      |

| 10.2.1.1. I/O Base and Limit Address Registers                                                                                                                                                                                                                                                            |      |

| 10.3. Memory Address Decoding                                                                                                                                                                                                                                                                             |      |

| 10.3.1. Memory-Mapped I/O Base and Limit Address Registers.                                                                                                                                                                                                                                               |      |

| 10.3.2. Prefetchable Memory Base and Limit Address Registers                                                                                                                                                                                                                                              |      |

| 10.4. ISA Mode                                                                                                                                                                                                                                                                                            |      |

| 10.5. VGA Support.                                                                                                                                                                                                                                                                                        |      |

| 10.5.1. VGA Mode                                                                                                                                                                                                                                                                                          |      |

| 10.5.2. VGA Snoop Mode                                                                                                                                                                                                                                                                                    |      |

| 10.6. Private Device Support                                                                                                                                                                                                                                                                              |      |

| 11 Transsetter Ordenian                                                                                                                                                                                                                                                                                   |      |

| 11. Transaction Ordering                                                                                                                                                                                                                                                                                  |      |

| 11.1. Conventional PCI Transaction Ordering                                                                                                                                                                                                                                                               | 11-1 |

| 11.1.1. Transactions Governed by Ordering Rules                                                                                                                                                                                                                                                           |      |

| 11.1.2. General Ordering Guidelines                                                                                                                                                                                                                                                                       |      |

| 11.1.3. Ordering Rules.                                                                                                                                                                                                                                                                                   |      |

| 11.1.4. Data Synchronization.                                                                                                                                                                                                                                                                             |      |

| 11.2. PCI-X Transaction Ordering                                                                                                                                                                                                                                                                          |      |

| 11.2.1. Relaxed Ordering Attribute Bit                                                                                                                                                                                                                                                                    |      |

| 11.2.2. Split Transactions                                                                                                                                                                                                                                                                                |      |

|                                                                                                                                                                                                                                                                                                           |      |

| 12. Error Handling                                                                                                                                                                                                                                                                                        |      |

| -                                                                                                                                                                                                                                                                                                         |      |

| 12.1. Overview                                                                                                                                                                                                                                                                                            |      |

|                                                                                                                                                                                                                                                                                                           |      |

| 12.2. Address Parity Errors                                                                                                                                                                                                                                                                               |      |

| 12.3. Attribute Parity Errors— PCI-X Mode                                                                                                                                                                                                                                                                 |      |

| 12.3. Attribute Parity Errors— PCI-X Mode                                                                                                                                                                                                                                                                 |      |

| 12.3. Attribute Parity Errors       PCI-X Mode         12.4. Data Parity Errors       12.4.1. Configuration Write Transactions to Configuration Space                                                                                                                                                     |      |

| 12.3. Attribute Parity Errors       PCI-X Mode         12.4. Data Parity Errors       12.4.1. Configuration Write Transactions to Configuration Space         12.4.2. Read Transactions       12.4.2. Read Transactions                                                                                   |      |

| 12.3. Attribute Parity Errors       PCI-X Mode         12.4. Data Parity Errors       12.4.1. Configuration Write Transactions to Configuration Space         12.4.2. Read Transactions       12.4.2. Read Transactions         12.4.3. Posted Write Transactions       12.4.3. Posted Write Transactions |      |

| <ul> <li>12.3. Attribute Parity Errors— PCI-X Mode</li></ul>                                                                                                                                                                                                                                              |      |

| <ul> <li>12.3. Attribute Parity Errors— PCI-X Mode</li></ul>                                                                                                                                                                                                                                              |      |

| <ul> <li>12.3. Attribute Parity Errors— PCI-X Mode</li></ul>                                                                                                                                                                                                                                              |      |

| 12.5. Data Parity Error Reporting Summary       12-4         12.6. System Error (P_SERR#) Reporting.       12-13                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13. Exclusive Access                                                                                                                                                                                                                                                                                                                                                                                        |

| 13.1. Concurrent Locks       13-1         13.2. Acquiring Exclusive Access across PCI 6520.       13-1         13.3. Ending Exclusive Access       13-2                                                                                                                                                                                                                                                     |

| 14. PCI Bus Arbitration                                                                                                                                                                                                                                                                                                                                                                                     |

| 14.1. Overview.14-114.2. Primary PCI Bus Arbitration14-114.3. Secondary PCI Bus Arbitration14-114.3.1. Secondary Bus Arbitration Using Internal Arbiter14-114.3.2. Rotating-Priority Scheme14-214.3.3. Fixed-Priority Scheme14-214.3.4. Secondary Bus Arbitration Using External Arbiter14-314.4. Arbitration Bus Parking14-314.4.1. Software Controlled PCI 64-Bit Extension Signals Parking14-3           |

| 15. GPIO Interface                                                                                                                                                                                                                                                                                                                                                                                          |

| 15.1. GPIO Interface Pins       15-1         15.2. GPIO Control Registers       15-1         15.3. GPIO Serial Stream       15-1                                                                                                                                                                                                                                                                            |

| 16. Supported Commands                                                                                                                                                                                                                                                                                                                                                                                      |

| 16.1. Primary Interface Command Set.       16-1         16.2. Secondary Interface Command Set       16-3                                                                                                                                                                                                                                                                                                    |

| 17. Bridge Behavior                                                                                                                                                                                                                                                                                                                                                                                         |

| 17.1. Bridge Actions for Various Cycle Types       17-1         17.2. Abnormal Termination (Master Abort, Initiated by Bridge Master)       17-2         17.3. Parity and Error Reporting       17-2                                                                                                                                                                                                        |

| 18. PCI Flow-Through Optimization                                                                                                                                                                                                                                                                                                                                                                           |

| 18.1. Overview.18-118.2. Precautions when Using Non-Optimized PCI Master Devices18-118.3. Posted Write Flow Through18-118.4. Delayed Read Flow Through18-218.5. Read Cycle Optimization18-218.5.1. Primary and Secondary Initial Prefetch Count.18-218.5.2. Primary and Secondary Incremental Prefetch Count.18-318.5.3. Primary and Secondary Maximum Prefetch Count18-318.6. Read Prefetch Boundaries18-3 |

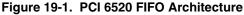

| 19. FIFO Architecture                                                                                                                                                                                                                                                                                                                                                                                       |

| 19.1. Overview.       19-1         19.2. Memory Writes       19-2         19.2.1. PCI-to-PCI-X Memory Writes.       19-2         19.2.2. PCI-X-to-PCI Memory Writes.       19-2         19.2.3. PCI-X-to-PCI-X Memory Writes.       19-2         19.2.3. PCI-X-to-PCI-X Memory Writes.       19-2                                                                                                           |

| <ul> <li>19.3. Memory Reads.</li> <li>19.3.1. PCI-to-PCI-X Memory Reads.</li> <li>19.3.1.1. Prefetched Data Timeout Flushing.</li> <li>19.3.1.2. Setting the Prefetch Count.</li> <li>19.3.1.2.1. PCI Read from Conventional PCI Port</li> <li>19.3.1.2.2. PCI Read from PCI-X Port.</li> <li>19.3.2. PCI-X-to-PCI Memory Reads.</li> <li>19.3.3. PCI-X-to-PCI-X Memory Reads.</li> </ul> | 19-2<br>19-3<br>19-4<br>19-4<br>19-4<br>19-4 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 20. Power Management                                                                                                                                                                                                                                                                                                                                                                      | 20-1                                         |

| 20.1. Overview                                                                                                                                                                                                                                                                                                                                                                            |                                              |

| 21. VPD                                                                                                                                                                                                                                                                                                                                                                                   | 21-1                                         |

| 22. Testability/Debug                                                                                                                                                                                                                                                                                                                                                                     | 22-1                                         |

| 22.1. JTAG Interface .<br>22.1.1. IEEE 1149.1 Test Access Port .<br>22.1.2. JTAG Instructions .<br>22.1.3. JTAG Boundary Scan .<br>22.1.4. JTAG Reset Input TRST# .                                                                                                                                                                                                                       | 22-1<br>22-1<br>22-2                         |

| 23. Electrical Specs                                                                                                                                                                                                                                                                                                                                                                      | 23-1                                         |

| 23.1. General Electrical Specifications      23.2. PLL and Clock Jitter      23.3. PCI/PCI-X Signal Timing Specification                                                                                                                                                                                                                                                                  | 23-3                                         |

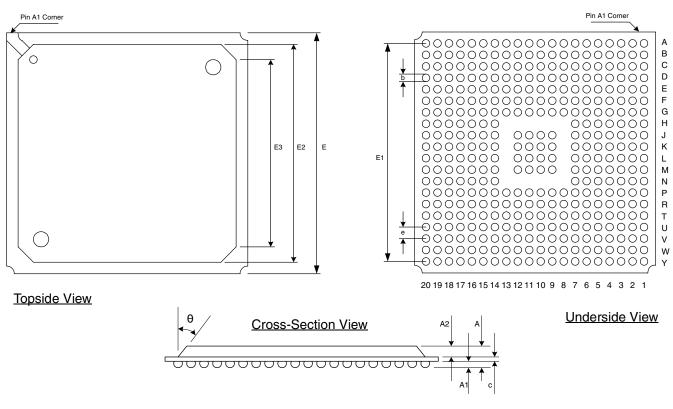

| 24. Mechanical Specs                                                                                                                                                                                                                                                                                                                                                                      | 24-1                                         |

| 24.1. Mechanical Dimensions                                                                                                                                                                                                                                                                                                                                                               |                                              |

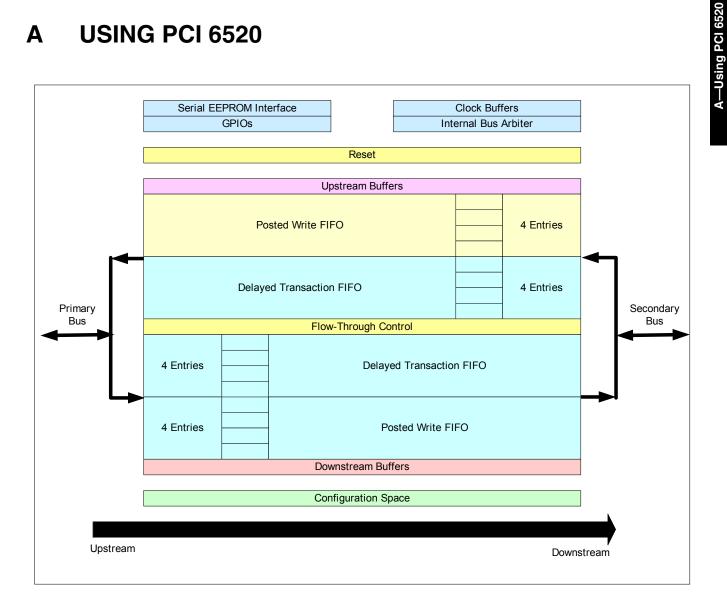

| A. Using PCI 6520                                                                                                                                                                                                                                                                                                                                                                         | A-1                                          |

| A.1. Application                                                                                                                                                                                                                                                                                                                                                                          | . A-2                                        |

| B. PCI-X Clock and Frequency Initialization Sequence                                                                                                                                                                                                                                                                                                                                      | B-1                                          |

| B.1. Bus Speed and Type Detection      B.2. Secondary Clock Outputs      B.3. Internal Clock Divider                                                                                                                                                                                                                                                                                      | . B-2                                        |

| C. PCI 6520CB and PCI 6540CB Pin Comparison                                                                                                                                                                                                                                                                                                                                               | C-1                                          |

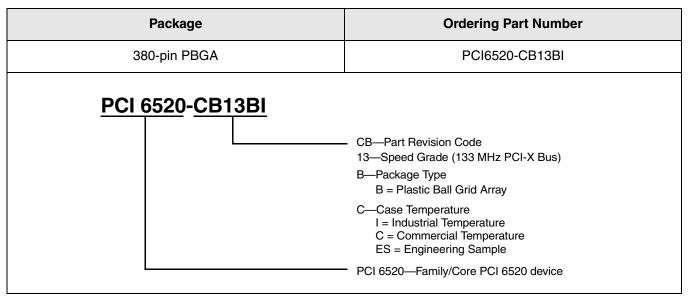

| D. General Information                                                                                                                                                                                                                                                                                                                                                                    | D-1                                          |

| D.1. Package Ordering<br>D.2. United States and International Representatives, and Distributors<br>D.3. Technical Support                                                                                                                                                                                                                                                                 | . D-2                                        |

| Index Inde                                                                                                                                                                                                                                                                                                                                                                                | ex-1                                         |

### **FIGURES**

| 1-1. FastLane PCI 6000 Bridge Series1-4                                               |

|---------------------------------------------------------------------------------------|

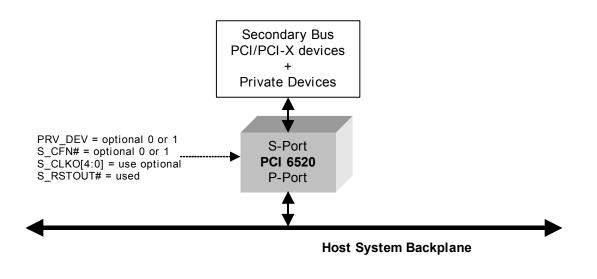

| 1-2. PCI 6520 PCI-X-to-PCI-X Bridge1-5                                                |

| 1-3. Multiple Device Expansion                                                        |

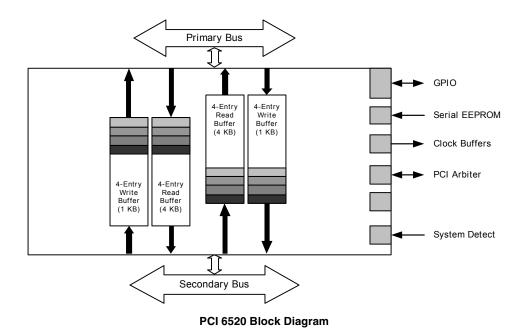

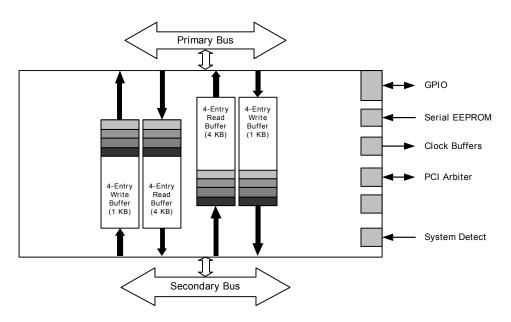

| 2-1. PCI 6520 Block Diagram                                                           |

| 3-1. Worst-Case Power Dissipation Example                                             |

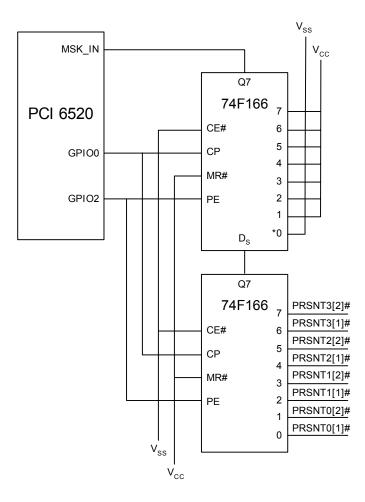

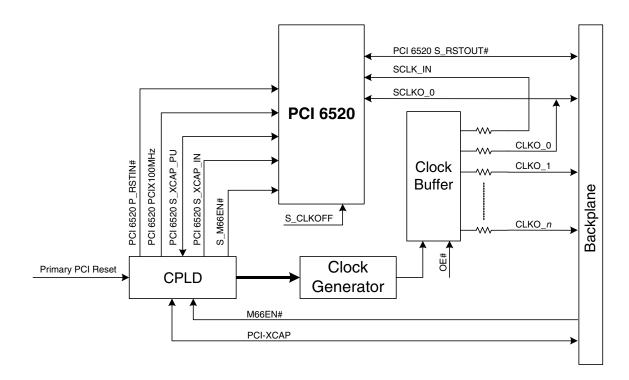

| 4-1. GPIO Clock Mask Implementation on System Board Example                           |

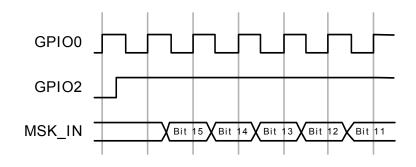

| 4-2. Clock Mask and Load Shift Timing                                                 |

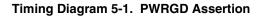

| 6-1. Sample Memory Map of Smart Prefetch Upstream Memory, Regions 1 through 4         |

| 7-1. Serial EEPROM Data Structure                                                     |

| 9-1. Requester Attribute Bit Assignments                                              |

| 9-2. Split Completion Address                                                         |

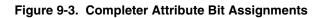

| 9-3. Completer Attribute Bit Assignments9-14                                          |

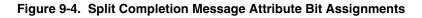

| 9-4. Split Completion Message Attribute Bit Assignments9-16                           |

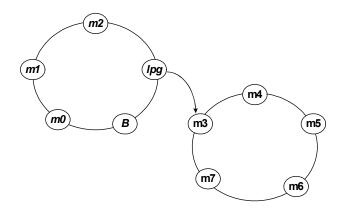

| 14-1. Secondary Bus Arbiter Example14-2                                               |

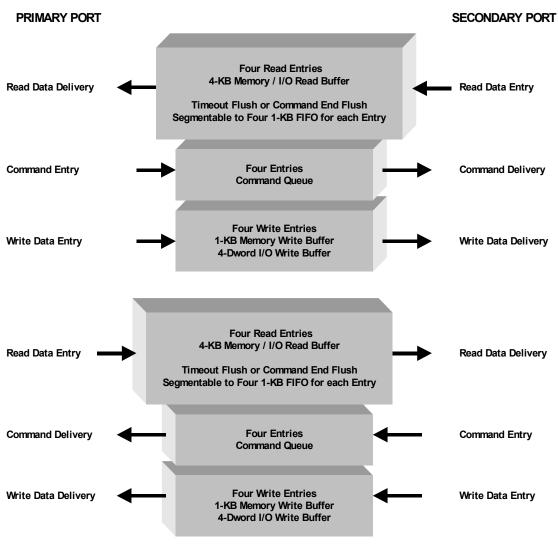

| 19-1. PCI 6520 FIFO Architecture                                                      |

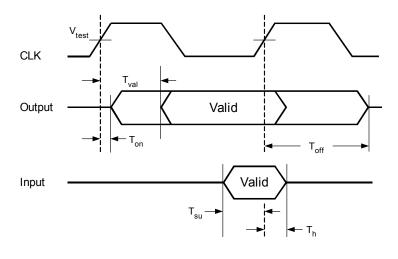

| 23-1. PCI/PCI-X Signal Timing Specification                                           |

| 24-1. PCI 6520 Mechanical Dimensions                                                  |

| 24-2. PCI 6520 Physical Layout with Pinout—Topside View (A1–A10 through Y1–Y10)24-4   |

| 24-3. PCI 6520 Physical Layout with Pinout—Topside View (A11–A20 through Y11–Y20)24-5 |

|                                                                                       |

### TABLES

| 1-1. FastLane PCI 6000 Series PCI and PCI-X Bridge Product Comparison                      | 1-2 |

|--------------------------------------------------------------------------------------------|-----|

| 3-1. Pin Type Abbreviations                                                                | 3-1 |

| 3-2. Generic PCI Bus Interface Pins that follow PCI r2.3 and PCI-X r1.0b Layout Guidelines | 3-2 |

| 3-3. Clock Pin Pull-Up/Pull-Down Resistor Requirements                                     | 3-3 |

| 3-4. Primary PCI/PCI-X Bus Interface Pins                                                  | 3-6 |

| 3-5. Secondary PCI/PCI-X Bus Interface Pins                                                | -10 |

| 3-6. Clock-Related Pins                                                                    | -15 |

| 3-7. Reset Pins                                                                            | -18 |

| 3-8. JTAG/Boundary Scan Pins                                                               | -19 |

| 3-9. Serial EEPROM Pins                                                                    | -19 |

| 3-10. General Purpose I/O Pins                                                             | -20 |

| 3-11. Miscellaneous Pins                                                                   | -21 |

| 3-12. Power, Ground, and No Connect Pins                                                   | -24 |

| 4-1. GPIO Shift Register Operation                                                         | 4-3 |

| 4-2. GPIO Serial Data Format                                                               | 4-3 |

| 4-3. PCI Clock Frequency Division Ratios                                                   | 4-4 |

| 4-4. M66EN and PCI-XCAP Encoding                                                           | 4-5 |

| 4-5. PLL and Clock Jitter Parameters                                                       | 4-5 |

| 5-1. Reset Input Effect on PCI 6520                                                        | 5-4 |

| 5-2. Pin States during PWRGD and P_RSTIN#                                                  | 5-5 |

| 6-1. PCI Configuration Register Address Mapping                                            | 6-2 |

| 6-2. Extended Register Map—Offset from Extended Register Index                             | -41 |

| 6-3. Secondary Clock Frequency Values (PCIXSSR[8:6]; PCI:F2h)6                             | -51 |

| 7-1. Serial EEPROM Address and Corresponding PCI 6520 Registers                            | 7-3 |

| 8-1. Conventional PCI Transactions                                                         | 8-1 |

| 8-2. Write Transaction Forwarding                                                          | 8-2 |

| 8-3. Write Transaction Disconnect Address Boundaries                                       | 8-5 |

| 8-4. Read Transaction Prefetching                                                          | 8-5 |

| 8-5. Read Prefetch Address Boundaries                                                      | 8-6 |

| 8-6. Device Number to IDSEL S_AD Pin Mapping8                                              | -10 |

| 8-7. P_SERR# Assertion Requirements in Response to Master Abort on Posted Write            |     |

| 8-8. Response to Posted Write Target Termination                                           | -14 |

| 8-9. P_SERR# Assertion Requirements in Response to Posted Write Parity Error               | -14 |

| 8-10. Response to Delayed Write Target Termination                                         | -15 |

| 8-11. P_SERR# Assertion Requirements in Response to Delayed Write                          | -15 |

| 8-12. Response to Delayed Read Target Termination                                          | -16 |

| 8-13. P_SERR# Assertion Requirements in Response to Delayed Read                           | -16 |

| 9-1. Transaction Phase Definitions                                                         |     |

| 9-2. Byte Lane Assignments                                                                 | 9-5 |

| 9-3. PCI-X Command Encoding                                                                |     |

| 9-4. Requester Attribute Bit Definitions                                                   |     |

| 9-5. DEVSEL# Timing                                                                        |     |

| 9-6. Target Initial Latency                                                                |     |

| 9-7. Split Completion Address Bit Definitions                                              |     |

|                                                                                            |     |

| 9-8. Completer Attribute Bit Definitions9-14                                  |

|-------------------------------------------------------------------------------|

| 9-9. Split Completion Message Bit Definitions9-16                             |

| 9-10. PCI 6520 Error Message Indices9-17                                      |

| 9-11. PCI 6520 Data Phase Signaling9-19                                       |

| 9-12. Conventional PCI-to-PCI-X Command Translation9-21                       |

| 9-13. PCI-X-to-Conventional PCI Command Translation9-22                       |

| 11-1. Conventional PCI Transaction Ordering Summary11-3                       |

| 11-2. PCI-X Transaction Ordering and Deadlock-Avoidance Rules                 |

| 11-3. PCI-X Split Transactions—Case-by-Case Discussion                        |

| 12-1. Primary Interface Parity Error Detected Bit Status                      |

| 12-2. Secondary Interface Parity Error Detected Bit Status                    |

| 12-3. Primary Interface Data Parity Error Detected Bit Status                 |

| 12-4. Secondary Interface Data Parity Error Detected Bit Status               |

| 12-5. P_PERR# Assertion                                                       |

| 12-6. S_PERR# Assertion                                                       |

| 12-7. P_SERR# or S_SERR# for Data Parity Error Assertion                      |

| 15-1. GPIO Pin Alternate Functions                                            |

| 16-1. Primary Interface Supported Commands16-1                                |

| 16-2. Secondary Interface Supported Commands                                  |

| 17-1. Bridge Actions for Various Cycle Types17-1                              |

| 18-1. Reprogramming Prefetch Registers                                        |

| 19-1. Prefetched Data Timeout Flushing19-3                                    |

| 20-1. States and Related Actions during Power Management Transitions          |

| 22-1. PCI 6520 JTAG IDCODE Value                                              |

| 22-2. JTAG Instructions (IEEE Standard 1149.1-1990)                           |

| 23-1. Maximum Ratings                                                         |

| 23-2. Functional Operating Range                                              |

| 23-3. DC Electrical Characteristics                                           |

| 23-4. M66EN and PCI-XCAP Encoding                                             |

| 23-5. PLL and Clock Jitter Parameters                                         |

| 23-6. 66 MHz PCI and 133 MHz PCI-X Signal Timing for Figure 23-1              |

| 24-1. PCI 6520 Mechanical Dimensions for Figure 24-1 Symbols (in Millimeters) |

| C-1. PCI 6520CB Versus PCI 6540CB Pin Assignment Comparison                   |

| D-1. Available PackageD-1                                                     |

### REGISTERS

| 6-1. (PCIIDR; PCI:00h) PCI Configuration ID                          | 6-4  |

|----------------------------------------------------------------------|------|

| 6-2. (PCICR; PCI:04h) Primary PCI Command                            | 6-4  |

| 6-3. (PCISR; PCI:06h) Primary PCI Status                             | 6-5  |

| 6-4. (PCIREV; PCI:08h) PCI Revision ID                               | 6-6  |

| 6-5. (PCICCR; PCI:09h – 0Bh) PCI Class Code                          | 6-6  |

| 6-6. (PCICLSR; PCI:0Ch) PCI Cache Line Size                          | 6-6  |

| 6-7. (PCILTR; PCI:0Dh) Primary PCI Bus Latency Timer                 | 6-6  |

| 6-8. (PCIHTR; PCI:0Eh) PCI Header Type                               | 6-7  |

| 6-9. (PCIBISTR; PCI:0Fh) PCI Built-In Self-Test                      | 6-7  |

| 6-10. (PCIPBNO; PCI:18h) PCI Primary Bus Number                      | 6-8  |

| 6-11. (PCISBNO; PCI:19h) PCI Secondary Bus Number                    | 6-8  |

| 6-12. (PCISUBNO; PCI:1Ah) PCI Subordinate Bus Number                 | 6-8  |

| 6-13. (PCISLTR; PCI:1Bh) Secondary PCI Bus Latency Timer             | 6-8  |

| 6-14. (PCIIOBAR; PCI:1Ch) I/O Base                                   | 6-9  |

| 6-15. (PCIIOLMT; PCI:1Dh) I/O Limit                                  | 6-9  |

| 6-16. (PCISSR; PCI:1Eh) Secondary PCI Status                         | 6-10 |

| 6-17. (PCIMBAR; PCI:20h) Memory Base                                 | 6-11 |

| 6-18. (PCIMLMT; PCI:22h) Memory Limit                                | 6-11 |

| 6-19. (PCIPMBAR; PCI:24h) Prefetchable Memory Base                   | 6-12 |

| 6-20. (PCIPMLMT; PCI:26h) Prefetchable Memory Limit                  | 6-12 |

| 6-21. (PCIPMBARU32; PCI:28h) Prefetchable Memory Base Upper 32 Bits  | 6-13 |

| 6-22. (PCIPMLMTU32; PCI:2Ch) Prefetchable Memory Limit Upper 32 Bits | 6-13 |

| 6-23. (PCIIOBARU16; PCI:30h) I/O Base Upper 16 Bits                  | 6-13 |

| 6-24. (PCIIOLMTU16; PCI:32h) I/O Limit Upper 16 Bits.                | 6-13 |

| 6-25. (CAP_PTR; PCI:34h) New Capability Pointer                      | 6-14 |

| 6-26. (PCIIPR; PCI:3Dh) PCI Interrupt Pin                            | 6-14 |

| 6-27. (BCNTRL; PCI:3Eh) Bridge Control                               | 6-14 |

| 6-28. (CCNTRL; PCI:40h) Chip Control                                 | 6-16 |

| 6-29. (DCNTRL; PCI:41h) Diagnostic Control                           | 6-17 |

| 6-30. (ACNTRL; PCI:42h) Arbiter Control.                             | 6-17 |

| 6-31. (PFTCR; PCI:44h) Primary Flow-Through Control                  | 6-18 |

| 6-32. (TOCNTRL; PCI:45h) Timeout Control                             | 6-19 |

| 6-33. (MSCOPT; PCI:46h) Miscellaneous Options.                       | 6-20 |

| 6-34. (PITLPCNT; PCI:48h) Primary Initial Prefetch Count             | 6-22 |

| 6-35. (SITLPCNT; PCI:49h) Secondary Initial Prefetch Count           | 6-23 |

| 6-36. (PINCPCNT; PCI:4Ah) Primary Incremental Prefetch Count         | 6-24 |

| 6-37. (SINCPCNT; PCI:4Bh) Secondary Incremental Prefetch Count       | 6-24 |

| 6-38. (PMAXPCNT; PCI:4Ch) Primary Maximum Prefetch Count             | 6-25 |

| 6-39. (SMAXPCNT; PCI:4Dh) Secondary Maximum Prefetch Count           | 6-25 |

| 6-40. (SFTCR; PCI:4Eh) Secondary Flow-Through Control                | 6-26 |

| 6-41. (BUFCR; PCI:4Fh) Buffer Control                                | 6-27 |

| 6-42. (IACNTRL; PCI:50h) Internal Arbiter Control                    | 6-28 |

|                                                                      | 6-29 |

| 6-44. (EEPCNTRL; PCI:54h) Serial EEPROM Control.                     | 6-29 |

|                                                                      |      |

| 6-45. | (EEPADDR; PCI:55h) Serial EEPROM Address                                    | 6-30 |

|-------|-----------------------------------------------------------------------------|------|

| 6-46. | (EEPDATA; PCI:56h) Serial EEPROM Data                                       | 6-30 |

| 6-47. | (TMRCNTRL; PCI:61h) Timer Control.                                          | 6-31 |

| 6-48. | (TMRCNT; PCI:62h) Timer Counter                                             | 6-31 |

| 6-49. | (PSERRED; PCI:64h) P_SERR# Event Disable                                    | 6-32 |

| 6-50. | (GPIOOD[3:0]; PCI:65h) GPIO[3:0] Output Data                                | 6-33 |

| 6-51. | (GPIOOE[3:0]; PCI:66h) GPIO[3:0] Output Enable                              | 6-33 |

| 6-52. | (GPIOID[3:0]; PCI:67h) GPIO[3:0] Input Data                                 | 6-33 |

| 6-53. | (CLKCNTRL; PCI:68h) Clock Control                                           | 6-34 |

| 6-54. | (PSERRSR; PCI:6Ah) P_SERR# Status                                           | 6-35 |

| 6-55. | (CLKRUN; PCI:6Bh) Clock Run.                                                | 6-36 |

| 6-56. | (PVTMBAR; PCI:6Ch) Private Memory Base                                      | 6-37 |

| 6-57. | (PVTMLMT; PCI:6Eh) Private Memory Limit                                     | 6-37 |

| 6-58. | (PVTMBARU32; PCI:70h) Private Memory Base Upper 32 Bits                     | 6-37 |

| 6-59. | (PVTMLMTU32; PCI:74h) Private Memory Limit Upper 32 Bits                    | 6-37 |

| 6-60. | (RRC; PCI:9Ch) Read-Only Register Control                                   | 6-38 |

| 6-61. | (GPIOOD[7:4]; PCI:9Dh) GPIO[7:4] Output Data                                | 6-39 |

| 6-62. | (GPIOOE[7:4]; PCI:9Eh) GPIO[7:4] Output Enable                              | 6-39 |

| 6-63. | (GPIOID[7:4]; PCI:9Fh) GPIO[7:4] Input Data                                 | 6-39 |

| 6-64. | (EXTRIDX; PCI:D3h) Extended Register Index.                                 | 6-41 |

| 6-65. | (EXTRDATA; PCI:D4h) Extended Register Data                                  | 6-41 |

| 6-66. | (SPUL32BAR1; EXT:10h) Region 1 Upstream Lower 32-Bit Smart Prefetch BAR     | 6-41 |

| 6-67. | (SPUU32BAR1; EXT:11h) Region 1 Upstream Lower 32-Bit Smart Prefetch BAR     | 6-42 |

| 6-68. | (SPUL32BAR2; EXT:12h) Region 2 Upstream Lower 32-Bit Smart Prefetch BAR     | 6-42 |

| 6-69. | (SPUU32BAR2; EXT:13h) Region 2 Upstream Lower 32-Bit Smart Prefetch BAR     | 6-42 |

| 6-70. | (SPUL32BAR3; EXT:14h) Region 3 Upstream Lower 32-Bit Smart Prefetch BAR     | 6-43 |

| 6-71. | (SPUU32BAR3; EXT:15h) Region 3 Upstream Lower 32-Bit Smart Prefetch BAR     | 6-43 |

| 6-72. | (SPUBARDx; EXT:16h–19h) Regions 1–4 Upstream Smart Prefetch BAR Descriptors | 6-43 |

| 6-73. | (PMCAPID; PCI:DCh) Power Management Capability ID                           | 6-46 |

| 6-74. | (PMNEXT; PCI:DDh) Power Management Next Capability Pointer                  | 6-46 |

| 6-75. | (PMC; PCI:DEh) Power Management Capabilities                                | 6-47 |

| 6-76. | (PMCSR; PCI:E0h) Power Management Control/Status                            | 6-48 |

| 6-77. | (PMCSR_BSE; PCI:E2h) PMCSR Bridge Supports Extensions                       | 6-48 |

| 6-78. | (PMCDATA; PCI:E3h) Power Management Data                                    | 6-48 |

| 6-79. | (PVPDID; PCI:E8h) Vital Product Data Capability ID                          | 6-49 |

| 6-80. | (PVPD_NEXT; PCI:E9h) Vital Product Data Next Capability Pointer             | 6-49 |

| 6-81. | (PVPDAD; PCI:EAh) Vital Product Data Address                                | 6-49 |

| 6-82. | (PVPDATA; PCI:ECh) VPD Data.                                                | 6-49 |

| 6-83. | (PCIXCAPID; PCI:F0h) PCI-X Capability ID                                    | 6-50 |

| 6-84. | (PCIX_NEXT; PCI:F1h) PCI-X Next Capability Pointer                          | 6-50 |

| 6-85. | (PCIXSSR; PCI:F2h) PCI-X Secondary Status                                   | 6-50 |

| 6-86. | (PCIXBSR; PCI:F4h) PCI-X Bridge Status                                      | 6-52 |

| 6-87. | (PCIXUPSTR; PCI:F8h) PCI-X Upstream Split Transaction                       | 6-53 |

| 6-88. | (PCIXDNSTR; PCI:FCh) PCI-X Downstream Split Transaction                     | 6-53 |

### PREFACE

The information contained in this document is subject to change without notice. Although an effort has been made maintain accurate information, there may be misleading or even incorrect statements made herein.

#### **Supplemental Documentation**

The following is a list of documentation to provide further details:

- PCI Local Bus Specification, Revision 2.1, June 1, 1995

PCI Special Interest Group (PCI-SIG)

5440 SW Westgate Drive #217, Portland, OR 97221 USA

Tel: 503 291-2569, Fax: 503 297-1090, http://www.pcisig.com/home

- PCI Local Bus Specification, Revision 2.3 PCI Special Interest Group (PCI-SIG)

5440 SW Westgate Drive #217, Portland, OR 97221 USA Tel: 503 291-2569, Fax: 503 297-1090, http://www.pcisig.com/home

- PCI to PCI Bridge Architecture Specification, Revision 1.2, June 9, 2003 PCI Special Interest Group (PCI-SIG)

5440 SW Westgate Drive #217, Portland, OR 97221 USA Tel: 503 291-2569, Fax: 503 297-1090, http://www.pcisig.com/home

- PCI Bus Power Management Interface Specification, Revision 1.1, December 18, 1998 PCI Special Interest Group (PCI-SIG)

5440 SW Westgate Drive #217, Portland, OR 97221 USA Tel: 503 291-2569, Fax: 503 297-1090, http://www.pcisig.com/home

- PCI-X Addendum to PCI Local Bus Specification, Revision 1.0b PCI Special Interest Group (PCI-SIG) 5440 SW Westgate Drive #217, Portland, OR 97221 USA Tel: 503 291-2569, Fax: 503 297-1090, http://www.pcisig.com/home

- IEEE Standard 1149.1-1990, *IEEE Standard Test Access Port and Boundary-Scan Architecture*, 1990 The Institute of Electrical and Electronics Engineers, Inc. 445 Hoes Lane, PO Box 1331, Piscataway, NJ 08855-1331, USA Tel: 800 678-4333 (domestic only) or 732 981-0060, Fax: 732 981-1721, http://www.ieee.org/portal/index.jsp

Note: In this data book, shortened titles are provided to the previously listed documents. The following table lists these abbreviations.

**Supplemental Documentation Abbreviations**

| Abbreviation              | Document                                                       |

|---------------------------|----------------------------------------------------------------|

| PCI r2.1                  | PCI Local Bus Specification, Revision 2.1                      |

| PCI r2.3                  | PCI Local Bus Specification, Revision 2.3                      |

| P-to-P Bridge r1.2        | PCI to PCI Bridge Architecture Specification, Revision 1.2     |

| PCI Power Mgmt. r1.1      | PCI Bus Power Management Interface Specification, Revision 1.1 |

| PCI-X r1.0b               | PCI-X Addendum to PCI Local Bus Specification, Revision 1.0b   |

| IEEE Standard 1149.1-1990 | IEEE Standard Test Access Port and Boundary-Scan Architecture  |

#### DATA ASSIGNMENT CONVENTIONS

#### **Data Assignment Conventions**

| Data Width        | PCI 6520 Convention |

|-------------------|---------------------|

| 1 byte (8 bits)   | Byte                |

| 2 bytes (16 bits) | Word                |

| 4 bytes (32 bits) | DWORD/Dword         |

| 8 bytes (64 bits) | QWORD/Qword         |

#### **REVISION HISTORY**

| Date  | Version | Comments                                 |

|-------|---------|------------------------------------------|

| 04/04 | 1.0     | Production Release, Silicon Revision BB. |

| 05/04 | 2.0     | Production Release, Silicon Revision CB. |

### PCI 6520 Transparent PCI-X-to-PCI-X Bridge

May 2004 Version 2.0 Asynchronous 64-Bit, 133 MHz PCI-X-to-PCI-X Bridge for Servers, Storage, Telecommunications, Networking, and Embedded Applications and High-Performance 10-KB Buffer PCI-X-to-PCI Bridging

### FEATURE SUMMARY

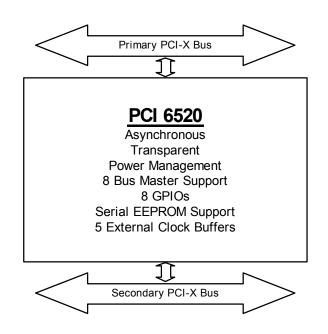

The PLX FastLane<sup>™</sup> PCI 6520 PCI-X-to-PCI-X Bridge is a device capable of 64-bit, 133 MHz operation. The device is designed for high-performance and high-availability uses such as PCI-X slot expansion, PCI-X-to-PCI conversion, multi-device attachment, and frequency conversion. The PCI 6520 has sophisticated buffer management and buffer configuration options designed to provide customizable performance for efficient throughput.

- PCI-X r1.0b-compliant at 64-bit, 133 MHz

- Backward compatible with PCI r2.3

- Support for input-pin-enforced PCI-X operation

- 5V tolerant I/O

- Asynchronous design for primary and secondary ports

- 33 to 133 MHz operation

- Either port may run at the higher frequency

- 8 GPIO pins with output control, with power-up status latch capabilities

- Primary port can be set to PCI-X protocol, without requiring the normal reset initialization sequence

- Flow-through, zero wait state bursts of up to 4 KB

- Optimal for large volume Data transfer

- Supports up to four simultaneous Posted Writes and Delayed transactions in each direction

- Supports up to four simultaneous Split transactions in each direction in PCI-X mode

- Optional segmented 1-KB buffer for each of the four Read FIFO entries

- 10-KB buffers

- 1-KB downstream Posted Write buffer

- 1-KB upstream Posted Write buffer

- 4-KB downstream Read Data buffer

- 4-KB upstream Read Data buffer

- Configurable prefetch size of up to 2 KB

- Ideal for PCI-to-PCI-X transfers

- 5 secondary clock outputs

- Pin-controlled enable

- Individual maskable control

- Supports downstream and upstream Lock

- Supports secondary port PCI/PCI-X Private Devices and Private Memory space (equivalent to Opaque memory)

- Reference clock input option

- Primary and secondary port PCI-X frequency detection

- Serial EEPROM loadable

- Programmable *PCI Read-Only* register configurations

- Programmable arbitration for eight secondary bus

masters

- Optional External Arbiter

- PCI Mobile Design Guide and Power Management D<sub>3cold</sub> Wakeup capable

- Enhanced address decoding

- Supports 32-bit I/O address range

- 32-bit Memory-Mapped I/O Address range

- ISA-Aware mode for legacy support in the first 64 KB of I/O address range

- VGA addressing and palette snooping support

- IEEE Standard 1149.1-1990 JTAG interface

- Low power 0.25µ CMOS process

- Industry standard 27 x 27 mm 380-pin (ball) PBGA package

## **1** INTRODUCTION

This section provides information about PLX Technology, Inc., and its products, the FastLane<sup>™</sup> PCI 6000 Bridge Series, and PCI 6520 features and applications.

#### 1.1 COMPANY AND PRODUCT INFORMATION

PLX Technology, Inc., is the leading supplier of standard interconnect silicon to the storage, communications, server, and embedded-control industries. PLX's comprehensive I/O interconnect product offering ranges from I/O accelerators, PCI-to-PCI bridges, PCI-X-to-PCI-X bridges, and HyperTransport<sup>™</sup> bridges to the PLX PCI Express-based family of switches and bridges currently under development.

In addition to a broad product offering, PLX provides development tool support through Software Development Kits (SDKs), hardware Rapid Development Kits (RDKs), and third-party tool support through the PLX Partner Program. Our complete tool offering, combined with leadership PLX silicon, enables system designers to maximize system throughput, lower development costs, minimize system design risk, and provide faster time to market.

The PLX commitment to meeting customer requirements extends beyond complete product solutions, and includes active participation in industry associations. PLX contributes to the key standard-setting bodies in our industry, including PCI-SIG<sup>™</sup> (the special interest group responsible for the creation and release of all PCI specifications), PICMG<sup>®</sup> (the organization responsible for CompactPCI and the new AdvancedTCA<sup>™</sup> standard for fabrics), HyperTransport<sup>™</sup> Consortium, and Blade Systems Alliance (BladeS). Furthermore, PLX is a key developer for PCI Express technology and a member of the Intel Developers Network for PCI Express Technology.

Founded in 1986, PLX has been developing products based on the PCI industry standard since 1994. PLX is publicly traded (NASDAQ:PLXT) and headquartered in Sunnyvale, CA, USA, with other domestic offices in Utah and Southern California. PLX European operations are based in the United Kingdom and Asian operations are based in China and Japan.

#### 1.2 FASTLANE PCI 6000 BRIDGE SERIES

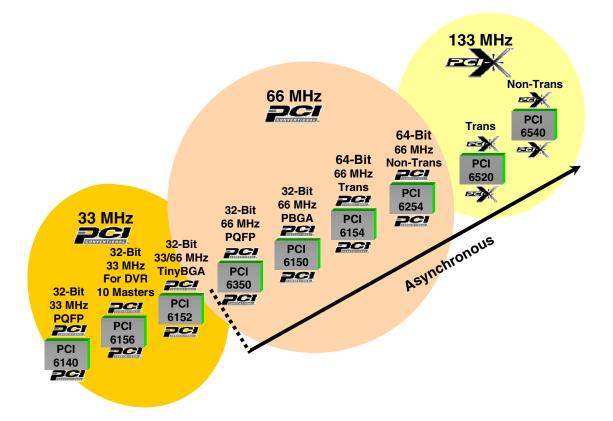

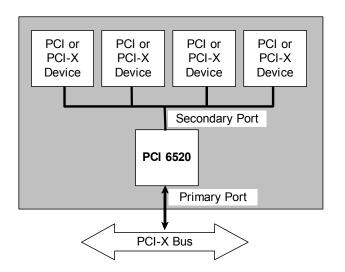

The PLX FastLane PCI 6000 series offers the industry's broadest set of PCI-to-PCI and PCI-X-to-PCI-X bridges. These bridges allow additional devices to be attached to the PCI Bus, and provide the ability to include intelligent adapters on a PCI Bus. In addition, these bridges allow PCI Buses of different speeds to be part of the same subsystem. (Refer to Table 1-1 and Figure 1-1.)

The PLX PCI and PCI-X family of interconnect products include both PCI-to-PCI and PCI-X-to-PCI-X bridging devices, offering system designers innovative features along with improved I/O performance. The PLX FastLane PCI 6000 series of PCI-to-PCI bridging products provide support for the entire range of current PCI Bus data widths and speeds, including 32-bit 33 MHz, 64-bit 66 MHz, and the latest 64-bit 133 MHz PCI-X variety of the standard.