# Edge4717D Quad Channel, Per Pin Precision Measurement Unit

## TEST AND MEASUREMENT PRODUCTS

### Description

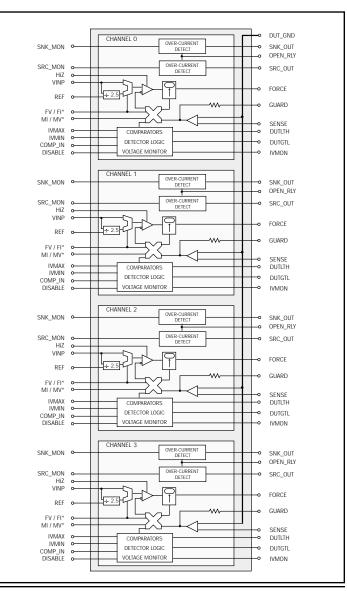

The Edge4717D is a precision measurement unit designed for automated test equipment and instrumentation. Manufactured in a wide voltage CMOS process, it is a monolithic solution for a guad channel per pin PMU.

Each channel of the Edge4717D features a PMU that can force or measure voltage over a typical 15V I/O range, and supports 4 current ranges:  $\pm$  3.2  $\mu$ A,  $\pm$  80  $\mu$ A,  $\pm$  2 mA,  $\pm$  30 mA.

The Edge4717D has an on-board window comparator per channel that provides two bits of information — DUT too high and DUT too low. There is also a monitor pin which provides a real time analog signal proportional to either the voltage or current measured at the DUT.

The Edge4717D is designed to be a low power, low cost, small footprint solution to allow high pin count testers to support a PMU per pin.

On-board voltage clamps, with over-current detection, provide protection to the DUT and 4717D.

The Edge4717D also has a sample-and-hold feature available for capturing DUT current or voltage measurements.

The Edge4717D is a design improvement to the Edge4717 that features:

- Increased FV/MV range

- Improved over-current detection circuit functionality

- LVTTL comparator outputs (pull-up resistors no longer required)

- Improved HiZ switching characteristics

- Improved Force Voltage Linearity

# **Applications**

- Automated Test Equipment

- Memory Testers

- VLSI Testers

- Mixed Signal Tester

### **Features**

- FV / MI Capability

- FI / MV Capability

- FV / MV Capability

- FI / MI Capability

- 4 Current Ranges (± 3.2 μA, ± 80 μA, ± 2 mA, ± 30 mA)

- –5.5V to 9.5V Nominal Output Range (Zero Current)

- -3.5 to 7.5V Nominal Output Range (Full Scale Current)

- On-board Voltage Clamps

- Internal Sample and Hold

- 228 Pin 23 mm x 23 mm TBGA Package

## Functional Block Diagram

# PIN Description

| Pin Name     | Pin #                | Description                                                                                                        |

|--------------|----------------------|--------------------------------------------------------------------------------------------------------------------|

| VINP[0:3]    | B19, H22, N21, V22   | Analog voltage input which forces the output voltage (FV mode) and the output current (FI mode) (one per channel). |

| REF[0:3]     | A19, G22, M21, U22   | Reference pin for divide by 2.5 circuit for force current mode; this reference is typically set to 2.25V.          |

| FORCE[0:3]   | E2, J2, N2, U2       | Analog output pin which forces current or voltage.                                                                 |

| SENSE[0:3]   | E3, J3, N3, U3       | Analog input pin which senses voltage.                                                                             |

| FV_FI*[0:3]  | A7, C11, A14, B17    | TTL compatible input which determines whether the PMU is forcing current or forcing voltage.                       |

| MI_MV*[0:3]  | C9, B11, B14, C16    | TTL compatible input which determines whether the PMU is measuring current or measuring voltage.                   |

| RS0[0:3]     | C7, B9, C12, B15     | TTL compatible current range select inputs.                                                                        |

| RS1[0:3]     | C6, A8, B12, A15     | TTL compatible current range select inputs.                                                                        |

| IVMIN[0:3]   | C17, H20, M20, U21   | Analog input voltages which establish the lower threshold level for the measurement comparator.                    |

| IVMAX[0:3]   | C18, H21, N22, U20   | Analog input voltages which establish the upper threshold level for the measurement comparator.                    |

| COMP_IN[0:3] | D2, H2, M2, T2       | Analog voltage input to measurement comparator.                                                                    |

| DUT_LTH[0:3] | AA13, Y12, AA10, Y9  | Digital comparator output that indicates the DUT measurement is less than the upper threshold.                     |

| DUT_GTL[0:3] | AA14, AA12, Y11, AA9 | Digital comparator output that indicates the DUT measurement is greater than the lower threshold.                  |

| DISABLE[0:3] | A6, B10, B13, B16    | TTL compatible input which places IVMON output in high impedance.                                                  |

| HIZ[0:3]     | B7, A10, C13, A17    | TTL compatible input that places the FORCE output into high impedance.                                             |

| RA[0:3]      | F3, K3, P3, V3       | External resistor input corresponding to Range A.                                                                  |

| RB[0:3]      | F2, K2, P2, V2       | External resistor input corresponding to Range B.                                                                  |

| RC[0:3]      | F1, K1, P1, V1       | External resistor input corresponding to Range C.                                                                  |

| RD[0:3]      | G3, L3, R3, W3       | External resistor input corresponding to Range D.                                                                  |

| SNK_MON[0:3] | F21, K22, R22, AA17  | Analog voltage input to sink current clamp.                                                                        |

| SRC_MON[0:3] | F22, L22, T22, Y16   | Analog voltage input to source current clamp.                                                                      |

| SNK_OUT[0:3] | C1, G1, L1, R1       | Clamp output.                                                                                                      |

| SRC_OUT[0:3] | E1, J1, N1, U1       | Clamp output.                                                                                                      |

# PIN Description (continued)

| Pin Name                 | Pin #                                                                                                                                                            | Description                                                                                                       |  |  |  |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|

| OPEN_RLY[0:3]            | Y14, Y13, AA11, Y10                                                                                                                                              | Open drain output that is used for opening relays between tester and DUT in case of an over-current condition.    |  |  |  |

| IVMON[0:3]               | B18, G21, M22, T21                                                                                                                                               | Analog voltage output that provides a real time monitor of either the measured voltage or measured current level. |  |  |  |

| LTCH_MODE[0:3]           | B6, C10, A12, A16                                                                                                                                                | Controls a mux for determination of whether IVMONITOR is from sample-and-hold or not sampled.                     |  |  |  |

| SAMPLE[0:3]              | C8, A9, A13, C15                                                                                                                                                 | Used for sampling the voltage on the SENSE[0:3] voltage monitor pins.                                             |  |  |  |

| GUARD[0:3]               | D1, H1, M1, T1                                                                                                                                                   | Driven guard pin used for guard traces.                                                                           |  |  |  |

| TEST[0:3]                | B8, A11, C14, A18                                                                                                                                                | Digital input control pin for mux for testing sample-and-hold.                                                    |  |  |  |

| TEST_IN[0:3]             | C19, J22, N20, V21                                                                                                                                               | Analog input for testing the sample-and-hold.                                                                     |  |  |  |

| COMP1[0:3]<br>COMP2[0:3] | D20, J20, P21, V20<br>D21, J21, P20, Y19                                                                                                                         | Internal compensation pins that require an external capacitor connection between the two pins.                    |  |  |  |

| COMP3[0:3]               | E21, K21, R21, Y18                                                                                                                                               | Internal compensation pin that requires an external capacitor connection between the pin and ground.              |  |  |  |

| COMP4[0:3]               | F20, K20, R20, Y17                                                                                                                                               | Internal compensation pin that requires an external capacitor connection between the pin and FORCE output.        |  |  |  |

| DUT_GND                  | Y6                                                                                                                                                               | Input reference pin that should be connected to DUT ground line.                                                  |  |  |  |

| Power Pins               |                                                                                                                                                                  |                                                                                                                   |  |  |  |

| VCC                      | A1, A2, A21, A22,<br>B1, B2, B21, B22,<br>C3, C20, Y3, Y20, AA1,<br>AA2, AA21, AA22, AB1,<br>AB2, AB21, AB22                                                     | Positive analog power supply.                                                                                     |  |  |  |

| VDD                      | Y15                                                                                                                                                              | Positive digital supply (comparator).                                                                             |  |  |  |

| VEE                      | A20, B20, C21, C22,<br>D22, E22, G2, L2, R2,<br>W2, W21, W22, Y21, Y22,<br>AA15, AA18, AA19, AA20,<br>AB13, AB14, AB15, AB16,<br>AB17, AB18, AB19, AB20          | Negative analog power supply.                                                                                     |  |  |  |

| GND                      | A3, A4, A5, B3, B4, B5,<br>C2, C4, C5, W1, Y1, Y2,<br>Y4, Y5, Y7, Y8, AA3, AA4,<br>AA5, AA6, AA7, AA8, AB3,<br>AB4, AB5, AB6, AB7, AB8,<br>AB9, AB10, AB11, AB12 | Ground.                                                                                                           |  |  |  |

| NC                       | D3, E20, H3, G20, L20,<br>L21, M3, P22, T3, T20,<br>W20, AA16                                                                                                    | No Connection. (Unused pins; leave unconnected).                                                                  |  |  |  |

PIN Description (continued)

A1 Ball Pad Indicator

# **Top View**

# 23mm x 23mm 228 Pin TBGA

|    | 1               | 2              | 3            | 4         | 5            | 6                | 7             | 8             | 9               | 10                 | 11                  | 12                  | 13                | 14               | 15             | 16                 | 17                | 18             | 19              | 20                      | 21                      | 22               |

|----|-----------------|----------------|--------------|-----------|--------------|------------------|---------------|---------------|-----------------|--------------------|---------------------|---------------------|-------------------|------------------|----------------|--------------------|-------------------|----------------|-----------------|-------------------------|-------------------------|------------------|

| Α  | A1<br>VCC       | A2<br>VCC      | (A3)         | (A4)      | (A5)         | A6<br>DISABLEO   | A7<br>FV_FINO | (A8)<br>RS11  | A9<br>SAMPLE1   | (A10)<br>HIZ1      | (A11)<br>TEST1      | (A12)<br>LTCH_MODE2 | A13)<br>SAMPLE2   | (A14)<br>FV_FIN2 | A15)           | A16)<br>LTCH_MODE3 | A17<br>HIZ3       | (A18)<br>TEST3 | A19<br>IREFO    | (A20)<br>VEE            | A21<br>VCC              | A22<br>VCC       |

| В  | B1<br>VCC       | B2<br>VCC      | B3<br>GND    | B4<br>GND | B5<br>GND    | B6<br>LTCH_MODEO | B7            | (B8)<br>TESTO | B9<br>RS01      | B10<br>DISABLE1    | B11)<br>MI_MVN1     | B12)<br>RS12        | B13)<br>DISABLE2  | B14)<br>MLMVN2   | B15)           | B16)<br>DISABLE3   | B17<br>FV_FIN3    | B18<br>IVMONO  | B19<br>VINPO    | B20<br>VEE              | B21)                    | B22<br>VCC       |

| С  | C1<br>SNK_OUTO  | C2<br>GND      | C3<br>VCC    | C4<br>GND | C5<br>GND    | C6<br>RS10       | C7<br>RS00    | C8<br>SAMPLEO | C9<br>MI_MVN0   | C10<br>LTCH_MODE1  | C11)<br>FV_FIN1     | C12<br>RS02         | C13)              | C14<br>TEST2     | C15<br>SAMPLE3 | C16<br>MI_MVN3     | C17<br>IV_MINO    | C18<br>IV_MAXO | C19<br>TEST_INO | C2O<br>VCC              | C21<br>VEE              | C22<br>VEE       |

| D  | D1<br>GUARDO    | D2<br>COMP_INO | D3<br>NC     | D4        |              |                  |               |               | D9              |                    |                     |                     |                   | D14              |                |                    |                   |                | D19             | D20<br>COMP10           | D21<br>COMP20           | D22<br>VEE       |

| Е  | E1<br>SRC_OUTO  | E2<br>FORCEO   | E3<br>SENSEO | E4        |              |                  | E7            |               | E9              | E10                |                     |                     |                   | E14              | E15            |                    |                   |                | E19             | E20<br>NC               | E21<br>COMP30           | E22<br>VEE       |

| F  | F1<br>RCO       | F2<br>RBO      | F3<br>RAD    | F4        |              |                  |               |               | F9              |                    |                     |                     |                   | F14              |                | F16                |                   |                | F19             | F20<br>COMP40           | F21<br>SNK_MONO         | F22<br>SRC_MONO  |

| G  | G1<br>SNK_OUT1  | G2<br>VEE      | G3<br>RD0    | G4        |              |                  |               |               | G9              |                    |                     |                     |                   | G14              |                |                    |                   |                | G19             | G20<br>HLD CAPO<br>(NC) | G21<br>IVMON1           | G22<br>IREF1     |

| Н  | H1<br>GUARD1    | H2<br>COMP_IN1 | H3<br>NC     | Н4        |              |                  |               |               | Н9              |                    |                     |                     |                   | H14              |                |                    |                   |                | H19             | H20<br>IV_MIN1          | H21)                    | H22<br>VINP1     |

| J  | J1<br>SRC_OUT1  | J2<br>FORCE1   | J3<br>SENSE1 | J4        |              | J6               |               |               | J9              |                    |                     |                     |                   | J14              |                |                    |                   |                | J19             | J20<br>COMP11           | J21<br>COMP21           | J22<br>TEST_IN1  |

| K  | K1<br>RC1       | K2<br>RB1      | K3<br>RA1    | K4        | K5           | К6               | K7            | K8            | K9              | K10                | K11                 | K12                 | K13               | K14              | K15            | K16                | K17               | K18            | K19             | (K20)<br>COMP41         | K21<br>COMP31           | K22<br>SNK_MON1  |

| L  | L1<br>SNK_OUT2  | L2<br>VEE      | L3<br>RD1    | L4        |              | L6               |               |               | L9              |                    |                     |                     |                   | L14              |                |                    |                   |                | L19             | L20<br>NC               | L21<br>HLD_CAP1<br>(NC) | L22<br>SRC_MON1  |

| Μ  | M1)<br>GUARD2   | M2<br>COMP_IN2 | M3<br>NC     | M4        |              |                  | M7            |               | M9              |                    |                     |                     |                   | M14              | M15            |                    |                   |                | M19             | M20<br>IV_MIN2          | M21)                    | M22<br>IVMON2    |

| N  | N1<br>SRC_OUT2  | N2<br>FORCE2   | N3<br>SENSE2 | N4        |              |                  | N7            |               | N9              | N10                | N11                 |                     | N13               | N14              | N15            |                    |                   |                | N19             | N20<br>TEST_IN2         | N21<br>VINP2            | N22<br>IV_MAX2   |

| Р  | P1<br>RC2       | P2<br>RB2      | P3<br>RA2    | P4        |              |                  |               |               | P9              |                    |                     |                     |                   | P14              |                | P16                |                   |                | P19             | P20<br>COMP22           | P21<br>COMP12           | P22<br>NC        |

| R  | R1<br>SNK_OUT3  | R2<br>VEE      | R3<br>RD2    | R4        | R5           |                  | R7            |               | R9              | R10                | R11                 | R12                 | R13               | R14              | R15            | R16                | R17               | R18            | R19             | R20<br>COMP42           | R21)<br>COMP32          | R22)<br>SNK_MON2 |

| Т  | T1)             | T2<br>COMP_IN3 | T3<br>NC     | T4        |              |                  |               |               | Т9              |                    |                     |                     |                   | T14              |                |                    |                   |                | T19             | T20<br>HLD_CAP2<br>(NC) | T21)                    | T22<br>SRC_MON2  |

| U  | U1)<br>SRC_OUT3 | U2<br>FORCE3   | U3<br>SENSE3 | U4        |              |                  |               |               | U9              |                    |                     |                     |                   | U14              |                |                    |                   |                | U19             | U20<br>IV_MAX3          | U21)<br>IV_MIN3         | U22<br>IREF3     |

| V  | V1<br>RC3       | V2<br>RB3      | V3<br>RA3    | V4        |              |                  | V7            |               | V9              | V10                | V11                 | V12                 | V13               | V14              | V15            | V16                | V17               | V18            | V19             | V20)<br>COMP13          | V21)<br>TEST_IN3        | V22<br>VINP3     |

| W  | W1<br>GND       | W2<br>VEE      | W3<br>RD3    | W4        |              |                  |               |               | W9              |                    |                     |                     |                   | W14              |                |                    |                   |                | W19             | W20)<br>NC              | W21)<br>VEE             | W22<br>VEE       |

| Υ  | Y1<br>GND       | Y2<br>GND      | Y3<br>VCC    | Y4<br>GND | Y5<br>GND    | Y6<br>DUT_GND    | (Y7)<br>GND   | (Y8)          | Y9<br>DUT_LITH3 | Y10<br>OPEN_RLY3   | Y11)<br>DUT_GTL2    | Y12)<br>DUT_LTH1    | Y13)<br>OPEN_RLY1 | Y14<br>OPEN_RLYO | Y15)<br>VDD    | (Y16)<br>SRC_MON3  | (Y17)<br>COMP43   | Y18<br>COMP33  | (Y19)<br>COMP23 | Y20<br>VCC              | Y21)<br>VEE             | Y22<br>VEE       |

| AA | (AA1)           | (AA2)          | (AA3)        | (AA4)     | (AA5)<br>GND | (AA6)            | (AA7)         | (AA8)         | AA9<br>DUT_GTL3 | (AA10)<br>DUT_LTH2 | (AA11)<br>OPEN_RLY2 | AA12)<br>DUT_GTL1   | (AA13)            | AA14)            | (AA15)<br>VEE  | (NC)               | (A17)<br>SNK_MON3 | (AA18)<br>VEE  | (AA19)<br>VEE   | (AA20)<br>VEE           | (AA21)                  | (AA22)<br>VCC    |

| AB | AB1)            | (AB2)          | (AB3)        | (AB4)     | (AB5)        | (AB6)            | (AB7)         | (AB8)         | (AB9)           | (AB10)<br>GND      | (AB11)              | (AB12)              | (AB13)<br>VEE     | (AB14)<br>VEE    | AB15)<br>VEE   | (AB16)<br>VEE      | (AB17)<br>VEE     | AB18)<br>VEE   | AB19)<br>VEE    | AB20<br>VEE             | AB21)                   | (AB22)<br>VCC    |

PIN Description (continued)

A1 Ball Pad Indicator (see gold triangle located at the corner)

### **Bottom View**

### 23mm x 23mm 228 Pin TBGA

| 22               | 21               | 20                      | 19              | 18                | 17                | 16                  | 15             | 14                 | 13               | 12                | 11                  | 10                | 9                | 8             | 7             | 6                | 5         | 4         | 3            | 2               | 1               |    |

|------------------|------------------|-------------------------|-----------------|-------------------|-------------------|---------------------|----------------|--------------------|------------------|-------------------|---------------------|-------------------|------------------|---------------|---------------|------------------|-----------|-----------|--------------|-----------------|-----------------|----|

| A22<br>VCC       | (A21)<br>VCC     | (A20)<br>VEE            | A19<br>IREFO    | (A18)<br>TEST3    | A17<br>HIZ3       | (A16)<br>LTCH_MODE3 | (A15)<br>RS13  | (A14)<br>FV_FIN2   | A13)<br>SAMPLE2  | A12<br>LTCH_MODE2 | (A11)<br>TEST1      | (A10)<br>HIZ1     | A9<br>SAMPLE1    | A8<br>RS11    | A7<br>FV_FINO | A6<br>DISABLEO   | (A5)      | (A4)      | (A3)<br>GND  | A2<br>VCC       | A1<br>VCC       | Α  |

| B22<br>VCC       | B21)<br>vcc      | B20<br>VEE              | B19<br>VINPO    | B18<br>IVMONITORO | B17<br>FV_FIN3    | B16<br>DISABLE3     | B15)<br>RS03   | B14<br>MLMVN2      | B13<br>DISABLE2  | B12<br>RS12       | B11)<br>MLMVN1      | B10<br>DISABLE1   | B9<br>RS01       | (B8)<br>TESTO | B7<br>HIZO    | B6<br>LTCH_MODEO | B5<br>GND | B4<br>GND | B3<br>GND    | B2<br>vcc       | B1)             | В  |

| C22<br>VEE       | C21<br>VEE       | C2O<br>VCC              | C19<br>TEST_INO | C18<br>IV_MAXO    | C17<br>IV_MINO    | C16<br>MLMVN3       | C15<br>SAMPLE3 | C14<br>TEST2       | C13<br>HIZ2      | C12<br>RS02       | C11<br>FV_FIN1      | C10<br>LTCH_MODE1 | C9<br>MI_MVNO    | C8<br>SAMPLEO | C7<br>RS00    | (C6)<br>RS10     | C5<br>GND | C4<br>GND | C3<br>VCC    | C2<br>GND       | C1<br>SNK_OUTO  | С  |

| D22<br>VEE       | D21<br>COMP20    | D20<br>COMP10           | D19             |                   |                   |                     |                | D14                |                  |                   |                     |                   | D9               |               |               |                  |           | D4        | D3<br>NC     | D2<br>COMP_INO  | D1<br>GUARDO    | D  |

| E22<br>VEE       | E21<br>COMP30    | E20<br>NC               | E19             |                   |                   |                     |                | E14                |                  |                   |                     |                   | E9               |               |               |                  |           | E4        | E3<br>SENSEO | E2<br>FORCEO    | E1<br>SRC_OUTO  | Е  |

| F22<br>SRC_MONO  | F21<br>SNK_MONO  | F20<br>COMP40           | F19             |                   | F17               |                     |                | F14                |                  | F12               |                     |                   | F9               |               | F7            |                  |           | F4        | F3<br>RAO    | F2<br>RB0       | F1<br>RCO       | F  |

| G22<br>IREF1     | G21<br>IVMON1    | G20<br>HLD CAPO<br>(NC) | G19             |                   |                   |                     |                | G14                |                  |                   |                     |                   | G9               |               |               |                  |           | G4        | G3<br>RD0    | G2<br>VEE       | G1<br>SNK_OUT1  | G  |

| H22<br>VINP1     | H21<br>IV_MAX1   | H20<br>IV_MIN1          | H19             |                   |                   |                     |                | H14                |                  |                   |                     |                   | H9               |               |               |                  |           | H4        | H3<br>NC     | H2<br>COMP_IN1  | H1<br>GUARD1    | Н  |

| J22<br>TEST_IN1  | J21<br>COMP21    | J20<br>COMP11           | J19             |                   |                   |                     |                | J14                |                  |                   |                     |                   | J9               |               |               |                  |           | J4        | J3<br>SENSE1 | J2<br>FORCE1    | J1<br>SRC_OUT1  | J  |

| K22<br>SNK_MON1  | K21<br>COMP31    | K20<br>COMP41           | K19             | K18               | K17               | K16                 | K15            | K14                | K13              | K12               | K11                 | K10               | K9               | K8            | K7            | K6               | K5        | K4        | K3<br>RA1    | K2<br>RB1       | K1<br>RC1       | K  |

| L22<br>SRC_MON1  | L21<br>HLD CAP1  | L20<br>NC               | L19             |                   |                   | L16                 |                | L14                |                  |                   |                     |                   | L9               |               |               | L6               |           | L4        | L3<br>RD1    | L2<br>VEE       | L1<br>SNK_OUT2  | L  |

| M22<br>IVMON2    | M21<br>IREF2     | M20<br>IV_MIN2          | M19             | M18               | M17               |                     |                | M14                | M13              |                   | M11                 |                   | M9               |               |               |                  |           | M4        | M3<br>NC     | M2)<br>COMP_IN2 | M1)<br>GUARD2   | М  |

| N22<br>IV_MAX2   | N21<br>VINP2     | N20<br>TEST_IN2         | N19             |                   |                   |                     | N15            | N14                |                  | N12               |                     | N10               |                  |               |               |                  |           | N4        | N3<br>SENSE2 | N2<br>FORCE2    | N1)<br>SRC_OUT2 | N  |

| P22<br>NC        | P21<br>COMP12    | P20<br>COMP22           | P19             |                   |                   |                     |                | P14                |                  |                   |                     |                   | P9               |               |               |                  |           | P4        | P3<br>RA2    | P2<br>RB2       | P1<br>RC2       | Р  |

| R22<br>SNK_MON2  | R21<br>COMP32    | R20<br>COMP42           | R19             | R18               | R17               | R16                 | R15            | R14                | R13              | R12               | R11                 | R10               | R9               |               | R7            |                  |           | R4        | R3<br>RD2    | R2<br>VEE       | R1<br>SNK_OUT3  | R  |

| T22)<br>SRC_MON2 | T21)             | T20<br>HLD CAP2         | T19             |                   |                   |                     |                | T14                |                  |                   |                     |                   | Т9               |               |               |                  |           | T4        | T3<br>NC     | T2<br>COMP_IN3  | T1)             | T  |

| U22<br>IREF3     | U21)<br>IV_MIN3  | U20<br>IV_MAX3          | U19             |                   |                   |                     |                | U14                |                  |                   |                     |                   | U9               |               |               |                  |           | U4        | U3<br>SENSE3 | U2<br>FORCE3    | U1)<br>SRC_OUT3 | U  |

| V22)<br>VINP3    | V21)<br>TEST_IN3 | V20<br>COMP13           | V19             | V18               | V17               |                     | V15            | V14                | V13              | V12               | V11                 | V10               | V9               |               | V7            |                  |           | V4        | V3<br>RA3    | V2<br>RB3       | V1)             | V  |

| W22<br>VEE       | W21)<br>VEE      | W2O<br>NC               | W19             | W18               | W17               | W16                 | W15            | W14                | W13              | W12               | W11                 | W10               | W9               | W8            | W7            | W6               | W5        | W4        | W3<br>RD3    | W2<br>VEE       | W1)<br>GND      | W  |

| Y22<br>VEE       | Y21<br>VEE       | Y20<br>VCC              | (Y19)<br>COMP23 | Y18<br>COMP33     | Y17<br>COMP43     | Y16<br>SRC_MON3     | Y15<br>VDD     | Y14<br>OPEN_RLYO   | Y13<br>OPEN_RLY1 | Y12)<br>DUT_LTH1  | Y11)<br>DUT_GTL2    | Y10<br>OPEN_RLY3  | V9<br>DUT_LTH3   | Y8<br>GND     | Y7<br>GND     | Y6<br>DUT_GND    | Y5<br>GND | Y4<br>GND | Y3<br>VCC    | Y2<br>GND       | Y1)<br>GND      | Υ  |

| (AA22)<br>VCC    | (AA21)<br>VCC    | (AA20)<br>VEE           | (AA19)<br>VEE   | (AA18)<br>VEE     | (A17)<br>SNK_MON3 | AA16<br>HLD CAP3    | (AA15)<br>VEE  | (AA14)<br>DUT_GTLO | AA13<br>DUT_LTHO | AA12<br>DUT_GTL1  | (AA11)<br>OPEN_RLY2 | AA10<br>DUT_LTH2  | AA9)<br>DUT_GTL3 | (AA8)         | (AA7)         | (AA6)<br>GND     | (AA5)     | (AA4)     | (AA3)        | (AA2)<br>VCC    | (AA1)           | AA |

| (AB22)<br>VCC    | (AB21)           | (AB20)<br>VEE           | (AB19)<br>VEE   | (AB18)<br>VEE     | (B17)<br>VEE      | (AB16)<br>VEE       | (AB15)<br>VEE  | (AB14)<br>VEE      | (AB13)<br>VEE    | AB12<br>GND       | (AB11)              | AB10)<br>GND      | (AB9)            | (AB8)         | (AB7)         | (AB6)            | (AB5)     | (AB4)     | (AB3)        | (AB2)           | (AB1)           | AB |

# Circuit Description

#### **Circuit Overview**

The Edge4717D is a quad channel parametric test and measurement unit that can :

- Force Voltage / Measure Current

- Force Current / Measure Voltage

- Force Voltage / Measure Voltage

- Force Current / Measure Current

- Measure Voltage / Force Disable

The Edge4717D features a PMU (per channel) that can force or measure voltage over a 15V range and force or measure current over four distinct ranges:

- $\pm 3.2 \,\mu\text{A}$

- $\pm 80 \mu A$

- ± 2 mA

- ± 30 mA

The Edge4717D features an on-board window comparator (per channel) that provides two bit measurement range classification.

Also, a monitor pin, IVMON, is capable of outputting either a real time analog voltage signal which tracks the measured parameter, or a sampled value of the measurement parameter captured using the sample and hold circuitry.

### **PMU Functionality**

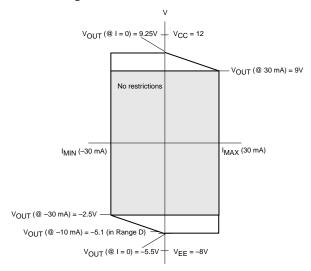

The trapezoid in Figure 1 describes the current-voltage functionality of the PMU with VCC = 12V and VEE = -8V, in Range D.

NOTE: Negative current is defined as current flowing into PMU from DUT.

Figure 1. PMU Functionality

### **Control Inputs**

FV / FI\* is a TTL compatible input which determines whether the PMU forces current or voltage, and MI/MV\* is a TTL compatible input which determines whether the PMU measures current or voltage. FV/FI\* and MI/MV\* are independent for each channel of the Edge4717D. HIZ is a TTL compatible input which can be used to place the PMU's force amp into a high impedance state. Tables 1 and 2 describe the modes of operation related to these three input pins.

| HIZ | FV / FI* | MI/MV* | Mode of Operation              |  |  |  |

|-----|----------|--------|--------------------------------|--|--|--|

| 1   | Х        | Х      | High Impedance                 |  |  |  |

| 0   | 0        | 0      | Force Current, Measure Voltage |  |  |  |

| 0   | 0        | 1      | Force Current, Measure Current |  |  |  |

| 0   | 1        | 0      | Force Voltage, Measure Voltage |  |  |  |

| 0   | 1        | 1      | Force Voltage, Measure Current |  |  |  |

Table 1.

RSO and RS1 are TTL compatible inputs to an internal analog MUX which selects an external resistor corresponding to a desired current range. The truth table for RSO and RS1, along with the associated external resistor values and current ranges, is shown in Table 2. RSO and RS1 are independent for each channel of the Edge4717D.

| RS1 | RS0 | Range | Current<br>Range | "Nominal" Ext. R  |

|-----|-----|-------|------------------|-------------------|

| 0   | 0   | А     | 3.2 µA           | $RA = 625K\Omega$ |

| 0   | 1   | В     | 80 μΑ            | $RB = 25K\Omega$  |

| 1   | 0   | С     | 2 mA             | $RC = 1K\Omega$   |

| 1   | 1   | D     | 30 mA            | $RD = 40\Omega$   |

Table 2.

# Circuit Description (continued)

#### FORCE/SENSE

FORCE is an analog output which either forces a current or forces a voltage, depending on which operating mode is selected. In FV mode, the voltage forced is equivalent to the voltage applied to the VINP pin. In FI mode, the current forced is mapped to the input as described in the Force Current section. FORCE can be placed in a high-impedance state through the setting of the HIZ input pin.

When the HIZ input pin is set to logical "O", the Edge4717D FORCE output will be controlled by the internal driver amplifier, and the Edge4717D will force a user-defined current or voltage (depending upon the setting of FV/FI\*) at the FORCE pin. When HIZ is set to logical "1", the FORCE output is placed into a low-leakage, high impedance state.

SENSE is a high impedance analog input which measures the DUT voltage in the MV operating mode.

(FORCE and SENSE are brought out to separate pins to allow remote sensing.)

#### **IVMON**

IVMON is a real time analog voltage output which tracks the sensed parameter.

In the MV mode (MI/MV $^*$  = 0), the output voltage displayed at IVMON is a 1:1 mapping of the SENSE voltage. In the MI mode (MI/MV $^*$  = 1), IVMON follows the equation:

IVMON = I(measured) \* REXT

Using nominal values for the external resistors (RA, RB, and RC), a voltage at IVMON of +2V corresponds to Imax, and -2V corresponds to Imin of the selected current range. For Range D, +1.2V corresponds to Imax and -1.2V corresponds to Imin.

The IVMON pin can also be placed into a high impedance state by using the DISABLE input (see Table 3).

| Disable | MI / MV* | Sensed Parameter |

|---------|----------|------------------|

| 1       | Х        | High Impedance   |

| 0       | 0        | Measured Voltage |

| 0       | 1        | Measured Current |

Table 3.

### Sample and Hold

The Edge4717D features a sample and hold circuit (per channel) which can be used to capture the corresponding voltage value of the sensed parameter (MI or MV) to be displayed at IVMON.

The output of the sample and hold is internally connected to IVMON through a latch controlled by LTCH\_MODE. The setting of LTCH\_MODE determines whether the data at IVMON comes from the sample and hold circuit or directly from the sensed parameter (see Table 4).

| LTCH_MODE | Sample           | Sample-and_Hold State |  |  |

|-----------|------------------|-----------------------|--|--|

| 0         | Х                | Transparent           |  |  |

| 1         | ▼ (Falling Edge) | Sample Data           |  |  |

| 1         | 0                | Hold Data             |  |  |

| 1         | 1                | Transparent           |  |  |

Table 4.

*Note:* No update is performed on the sample-and-hold.

#### Sample and Hold Testing

An analog MUX in the 4717D allows for testing of the sample-and-hold circuit.

The MUX control pin, TEST, is a TTL compatible input whose operation is described in Table 5. To test the sample and hold circuitry, an analog signal can be applied to the TEST IN pin and sampled.

# Circuit Description (continued)

| TEST | Function                                     |

|------|----------------------------------------------|

| 0    | Normal Operation                             |

| 1    | TEST_IN used for sample-<br>and-hold testing |

Table 5.

#### **Test Head Ground Reference**

The Edge4717D features a test head ground referencing feature which allows the force voltage function to be referenced to a separate ground reference other than the ground (GND) power used for the device. The test head ground should be connected to the DUT\_GND pin of the Edge4717D. The maximum allowed variation between DUT\_GND and GND is  $\pm$  250 mV.

### **Force Voltage Mode**

In the FV mode (FV/FI $^*$  = 1), VINP is a high impedance, analog voltage input that maps directly to the voltage forced at the FORCE pin.

#### **Measure Current Mode**

In the MI mode (MI/MV $^*$  = 1), a current monitor is connected in series with the PMU forcing amplifier. This monitor generates a voltage that is proportional to the current passing through it, and is brought out to IVMON. This voltage (corresponding to the measured current) can also be tested by the on-board window comparator.

#### **Force Current Mode**

In the FI mode ( $FV/FI^* = 0$ ), VINP is a high impedance, analog voltage input that is converted into a current at the FORCE pin (see Figure 1) using the following relationship:

Forced Current =

$$\frac{\text{VINP} - \text{VREF}}{(\text{REXT} * 2.5)}$$

where VREF is the reference voltage input at the REF pin which is nominally set at 2.25V. (Positive current is defined as current flowing out of the PMU.) Table 6 describes the relationship between the voltage applied to VINP and the current at FORCE for Ranges A, B, and C.

| VINP        | Corresponding Forced Current        |

|-------------|-------------------------------------|

| VREF + 5.5V | ≥ Imax (Full-Scale, Ranges A, B, C) |

| VREF + 3.5V | ≥ Imax (Full-Scale, Range D)        |

| VREF        | 0                                   |

| VREF – 3.5V | ≤ Imin (Full-Scale, Range D)        |

| VREF – 5.5V | ≤ Imin (Full-Scale, Ranges A, B, C) |

Table 6.

In the Force Current mode, the voltage at VINP is divided by 2.5 internally on the chip, so that  $a \pm 2V$  range is used internally for forcing currents on Ranges A, B, and C. Range D uses  $a \pm 1.2V$  range across REXT for forcing currents.

### Measure Voltage Mode

In the MV mode (MI/MV $^*$  = 0), DUT voltage is measured via the SENSE input pin. This measured voltage can be displayed on the IVMON pin and tested using the internal window comparator.

### Comparator

The Edge4717D features an on-board window comparator which provides two-bit measurement range classification. IVMAX and IVMIN are high impedance analog inputs that establish the upper and lower thresholds for the window comparator. COMP\_IN is the window comparator input pin. COMP\_IN should be connected to IVMON on each channel if it is desired to use the comparator to indicate PMU measurements.

In the MI mode, an I/V MAX input of +2V will set the upper threshold of the window comparator to a voltage corresponding to +FSC (full-scale current), and an I/V MIN input of -2V will set the lower threshold to a voltage corresponding to -FSC for Ranges A, B, and C. Similarly for Range D, -1.2V corresponds to sinking full-scale current, and +1.2V corresponds to sourcing full-scale current (positive current is defined as current flowing out of the PMU).

DUTGTL the DUTLTH are LVTTL compatible outputs which indicate the range of the measured parameter in relation to IVMIN and IVMAX. Comparator functionality is summarized in Table 7.

# Circuit Description (continued)

| TEST CONDITION                            | DUT LTH | DUT GTL |

|-------------------------------------------|---------|---------|

| COMP_IN > IVMAX<br>COMP_IN < IVMAX        | 0<br>1  | N/A     |

| COMP_IN > IVMIN<br>COMP_IN < IVMIN        | N/A     | 1<br>0  |

| COMP_IN < IVMAX<br>and<br>COMP_IN > IVMIN | 1       | 1       |

Table 7. Comparator Truth Table

#### **REXT Selection**

The Edge4717D is designed such that the maximum voltage drop across REXT (RA, RB, RC, or RD depending on range selected using RSO and RS1 inputs) is  $\leq 2V$ .

Resistor values can be chosen to operate the PMU at any current range up to  $\pm\,50\,$  mA in accordance with the following equation:

$$\label{eq:REXT} \begin{split} \text{REXT}[\Omega] = & \ \frac{2 \ [\text{V}]}{\text{IMAX}[\text{A}]} \ , \ \text{IMAX} \leq \ 50 \ \text{mA} \ \text{for Range D} \\ & \ \text{IMAX} \leq \ 2 \ \text{mA} \ \text{for Range C} \\ & \ \text{IMAX} \leq \ 80 \ \mu \text{A} \ \text{for Range B} \\ & \ \text{IMAX} \leq \ 3.2 \ \text{mA} \ \text{for Range A} \end{split}$$

#### **Voltage Clamps/Over-Current Detection**

The Edge4717D features four pairs of on-board clamps (one pair per channel), which can be used to clamp the voltage of pins connected to SRC OUT and SNK OUT between limits set by the voltages applied to SRC MON and SNK\_MON. SNK\_MON is a high impedance input that establishes the upper clamping limit, while SRC\_MON is a high impedance analog input that establishes the lower clamping limit. In addition to voltage clamping functionality, the clamp circuitry of the Edge4717D also features overcurrent detection capability. Over-current detection is only enabled when one of the voltage clamping thresholds is exceeded (FORCE +  $V_{diode}$  > SNK\_MON or FORCE -Vdiode < SRC\_MON). When enabled, an over-current condition is signaled via the OPEN-RLY pin. OPEN\_RLY is an open drain output pin that pulls down when an overcurrent condition is detected. OPEN\_RLY functionality is depicted in Table 8.

| Clamp Condition                    | Clamp Diode<br>Current                                   | OPEN_RLY |

|------------------------------------|----------------------------------------------------------|----------|

| SRC_OUT < FORCE-V <sub>diode</sub> | N/A                                                      | 1        |

| SRC_OUT > FORCE-V <sub>diode</sub> | I <sub>CLAMP</sub> > 55 mA<br>I <sub>CLAMP</sub> < 55 mA | 0<br>1   |

| SNK_OUT < FORCE+V <sub>diode</sub> | I <sub>CLAMP</sub> > 55 mA<br>I <sub>CLAMP</sub> < 55 mA | 0<br>1   |

| SNK_OUT > FORCE+V <sub>diode</sub> | N/A                                                      | 1        |

Table 8. Over-Current Detection Circuit Functionality (V<sub>diode</sub> is the forward voltage of the external clamp diode).

For applications that require the use of external resistors that are much smaller in Ohmic value than those that are outlined in Table 2, one will need to account for the variation in switch resistance vs. common mode voltage of the range selection switches (A-D in Figure 3) when specifying the overall accuracy of the application.

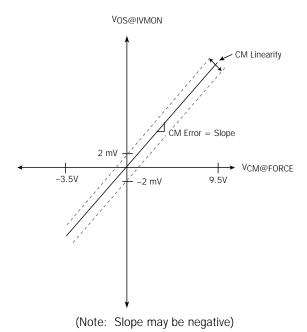

#### Common Mode Error/Calibration

In order to attain a high degree of accuracy in a typical ATE application, offset and gain errors are accounted for through software calibration. When operating the Edge4717D in the Measure Current (MI) or Force Current (FI) modes, an additional source of error, common mode error, should be accounted for. Common mode error is a measure of how the common mode voltage,  $V_{CM}$ , at the input of the current sense amplifier affects the forced or measured current values (see Figure 2). Since this error is created by internal resistors in the current sense amplifier, it is very linear in nature.

Using the common mode error and common mode linearity specifications, one can see that with a small number of calibration steps (see Applications note PMU-A1), the effect of this error can be significantly reduced.

# Circuit Description (continued)

Figure 2. Graphical Representation of

Common Mode Error

## **Transient Clamps**

The Edge4717D has on-board transient clamps to limit the voltage and current spikes that might result from either changing the current range or changing the operating mode.

#### **Driven Guard Pin**

The Edge4717D features a pin (per channel), GUARD, which can be used to drive the guard traces of a FORCE/ SENSE pair. By surrounding FORCE and SENSE traces with guard traces which connect to the GUARD pin, an effective method to achieve minimal leakage can be achieved.

### **Power Supply Sequencing**

In order to avoid the possibility of latch-up, the following power-up requirements must be satisified:

- 1.  $VEE \leq GND \leq VDD \leq VCC$  at all times

- 2.  $VEE \leq All inputs \leq VCC$

The following power supply sequencing can be used as a guideline when operating the Edge4717D:

### Power Up Sequence

- 1. VCC (substrate)

- 2. VEE/VDD

- 3. Digital Inputs

- 4. Analog Inputs

#### Power Down Sequence

- 1. Analog Inputs

- 2. Digital Inputs

- 3. VEE/VDD

- 4. VCC (substrate)

# Circuit Description (continued)

Figure 3. Functional Schematic

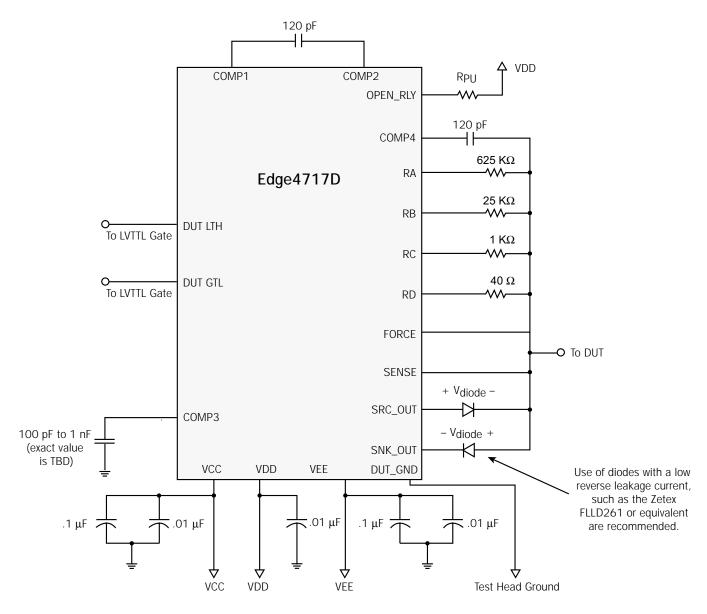

# **Application Information**

Actual decoupling capacitor values depend on the actual system environment.

Figure 4. Required External Components (Per Channel)

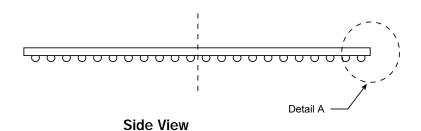

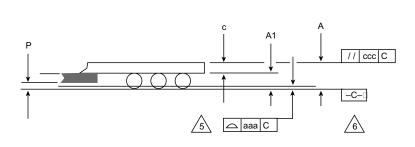

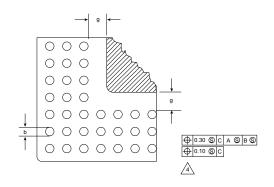

# Package Information

**Top View**

**Bottom View**

## Package Information (continued)

Detail A Detail B

#### NOTES:

- 1. All dimensions are in millimeters.

- 2. "e" represents the basic solder ball grid pitch.

- 3. "M" represents the basic solder ball matrix size, and symbol "N" is the maximum allowable number of balls after depopulating.

"b" is measured at the maximum solder ball diameter (after reflow) parallel to primary datum  $\boxed{-C-}$ .

Dimension "aaa" is measured parallel to primary datum \_-C\_ .

Primary datum —C— and seating plane are defined by the spherical crowns of the solder balls.

- 7. Package surface shall be black oxide.

- 8. Cavity depth varies with die thickness.

- 9. Substrate material base is copper.

$\frac{1}{2}$

Bilateral tolerance zone is applied to each side of package body. 45 degree 0.5 mm Chamfer corner and white dot for Pin 1 identification.

| D    | Dimensional References |           |       |  |  |  |

|------|------------------------|-----------|-------|--|--|--|

| REF. | MIN.                   | MAX.      |       |  |  |  |

| А    | 1.25                   | 1.4       | 1.55  |  |  |  |

| A1   | 0.40                   | 0.50      | 0.60  |  |  |  |

| D    | 22.80                  | 23.00     | 23.20 |  |  |  |

| D1   |                        | 21.00 BSC |       |  |  |  |

| E    | 22.80                  | 23.00     | 23.20 |  |  |  |

| E1   | 21.00 BSC              |           |       |  |  |  |

| b    | 0.525                  | 0.65      | 0.775 |  |  |  |

| С    | 0.85                   | 0.90      | 0.95  |  |  |  |

| М    |                        | 22        |       |  |  |  |

| Ν    |                        | 228       |       |  |  |  |

| aaa  |                        |           | 0.15  |  |  |  |

| ссс  |                        |           | 0.25  |  |  |  |

| е    | 1.00 TYP               |           |       |  |  |  |

| g    | 0.35                   |           |       |  |  |  |

| Р    | 0.15                   |           |       |  |  |  |

# **Recommended Operating Conditions**

| Parameter                                        | Symbol    | Min  | Тур | Max  | Units |

|--------------------------------------------------|-----------|------|-----|------|-------|

| Positive Analog Power Supply                     | VCC       | 11.5 | 12  | 12.5 | V     |

| Negative Analog Power Supply                     | VEE       | -8.5 | -8  | -7.5 | V     |

| Total Analog Power Supply                        | VCC – VEE | 19   | 20  | 21   | V     |

| Digital Power Supply                             | VDD       | 3.0  | 3.3 | 5.25 | V     |

| Case Temperature                                 | TC        | 25   |     | +65  | °C    |

| Thermal Resistance of Package (Junction to Case) | θјс       |      | 0.3 |      | °C/W  |

# Absolute Maximum Ratings

| Parameter             | Symbol    | Min      | Тур | Max      | Units |

|-----------------------|-----------|----------|-----|----------|-------|

| Positive Power Supply | VCC       |          |     | +15      | V     |

| Negative Power Supply | VEE       | -15      |     |          | V     |

| Total Power Supply    | VCC – VEE | 0        |     | 22       | V     |

| Digital Power Supply  | VDD       | 0        |     | + 7      | V     |

| Digital Inputs        |           | 5        |     | 7.0      | V     |

| Analog Inputs         |           | VEE – .5 |     | VCC + .5 | V     |

| Storage Temperature   |           | -55      |     | +125     | °C    |

| Case Temperature      |           |          |     | 100      | °C    |

| Soldering Temperature |           |          |     | 260      | °C    |

Stresses above listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# DC Characteristics

| Parameter                                                                                         | Symbol                | Min                    | Тур                  | Max                    | Units                |

|---------------------------------------------------------------------------------------------------|-----------------------|------------------------|----------------------|------------------------|----------------------|

| Power Supplies                                                                                    |                       |                        |                      |                        |                      |

| Power Supply Consumption (No-Load) Positive Supply Negative Supply "Digital" Supply               | ICC<br>IEE<br>IDD     |                        | 35<br>35             | 72<br>72<br>5          | mA<br>mA<br>mA       |

| Power Supply Rejection Ratio VCC to any Analog Output (except in Hold mode) 1 MHz 500 kHz 100 kHz | PSRR                  |                        | 20<br>20<br>25       |                        | dB<br>dB<br>dB       |

| VEE to any Analog Output (except in Hold mode)<br>1 MHz<br>500 kHz<br>100 kHz                     |                       |                        | 16<br>18<br>25       |                        | dB<br>dB<br>dB       |

| VDD to any Analog Output (except in Hold mode)<br>< 1 MHz                                         |                       |                        | 60                   |                        | dB                   |

| VCC to IVMON (Hold Mode) 1 MHz 500 kHz 100 kHz 200 Hz                                             |                       |                        | 0.6<br>6<br>20<br>30 |                        | dB<br>dB<br>dB<br>dB |

| VEE to IVMON (Hold Mode)  1 MHz 500 kHz 100 kHz 200 Hz                                            |                       |                        | 1.7<br>7<br>21<br>30 |                        | dB<br>dB<br>dB<br>dB |

| VDD to IVMON (Hold Mode) < 1 MHz                                                                  |                       |                        | 60                   |                        | dB                   |

| Force Voltage Mode                                                                                |                       |                        |                      |                        |                      |

| Input Voltage Range<br>Input Leakage Current                                                      | VINP<br>Ileak         | VEE + 2.0<br>-1        | 0                    | VCC - 2.0<br>1         | V<br>µA              |

| Output Forcing Voltage (Positive Full-Scale Current through R <sub>EXT</sub> )                    | VFORCE                | VEE + 2.5              |                      | VCC - 4.5              | V                    |

| Output Forcing Voltage (O Current through R <sub>EXT</sub> )                                      | VFORCE                | VEE + 2.5              |                      | VCC - 2.5              | V                    |

| Output Forcing Voltage (Negative Full-Scale Current through $R_{\text{EXT}}$ )                    | VFORCE                | VEE + 4.5              |                      | VCC - 2.5              | V                    |

| Voltage Accuracy<br>Offset<br>Gain<br>Linearity                                                   | VOS<br>Gain<br>FV INL | -200<br>.985<br>-0.025 | .01                  | 200<br>1.015<br>+0.025 | mV<br>V/V<br>% FSVR  |

# DC Characteristics (continued)

| Parameter                                                                                      | Symbol                         | Min                                 | Тур | Max                                 | Units                |

|------------------------------------------------------------------------------------------------|--------------------------------|-------------------------------------|-----|-------------------------------------|----------------------|

| Measure Current Mode                                                                           |                                |                                     |     |                                     |                      |

| Current Measurement Range Range A Range B Range C Range D                                      | <sup>I</sup> MEASURE           | -3.2<br>-80<br>-2<br>-30            |     | 3.2<br>80<br>2<br>30                | μΑ<br>μΑ<br>mA<br>mA |

| Current Measurement Accuracy Offset (@ IVMON) Gain (Note 1) Linearity Ranges A, B, C           | VOS<br>Gain<br>MI INL          | –150<br>.985<br>–.08                |     | 150<br>1.015                        | mV<br>V/V<br>% FSCR  |

| Range D                                                                                        |                                | -80                                 |     | +80                                 | μA                   |

| Common Mode Error Common Mode Linearity                                                        | CM Error                       | -5.5                                |     | 5.5                                 | mV/V                 |

| FORCE = VEE + 4.5V to VCC - 4.75V IVMON Output Impedance                                       | CM INL<br>Rout                 | 05                                  | 500 | .05                                 | %FSCR<br>Ω           |

| IVMON Leakage Current (IVMON = VEE+2.5V TO VCC-2.5V)                                           | ILEAK                          | -100                                |     | 100                                 | nA                   |

| Force Current Mode                                                                             |                                |                                     |     |                                     |                      |

| Input Voltage Range<br>Input Leakage Current<br>REF Input Voltage Range<br>REF Leakage Current | VINP<br>Ileak<br>Vref<br>Ileak | VREF - 5.5<br>-1<br>0<br>-1         | 0   | VREF + 5.5<br>1<br>2.5<br>–1        | V<br>µA<br>V<br>µA   |

| Output Forcing Current Range A Range B Range C Range D                                         | IFORCE                         | -3.2<br>-80<br>-2<br>-30            |     | 3.2<br>80<br>2<br>30                | μΑ<br>μΑ<br>mA<br>mA |

| Compliance Voltage Range Positive Full-Scale Current O Current Negative Full-Scale Current     | VFORCE                         | VEE + 2.5<br>VEE + 2.5<br>VEE + 3.0 |     | VCC - 3.0<br>VCC - 2.5<br>VCC - 2.5 | V<br>V<br>V          |

| Current Accuracy Offset Gain (Note 2) Linearity                                                | IOS<br>Gain<br>FI INL          | -3.6<br>.385                        | .4  | 3.6<br>.415                         | % FSCR<br>V/V        |

| Ranges A, B, C<br>Range D                                                                      | I I IIVL                       | 08<br>-80                           |     | .08<br>+80                          | % FSCR<br>µA         |

| Common Mode Error                                                                              | CM Error                       | -5.5                                |     | 5.5                                 | mV/V                 |

| Common Mode Linearity FORCE = VEE + 4.5V to VCC - 4.5V                                         | CM INL                         | 05                                  |     | .05                                 | % FSCR               |

# DC Characteristics (continued)

| Parameter                                                                                                                                                                                                                 | Symbol                                                                  | Min                        | Тур  | Max                        | Units                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------|------|----------------------------|-------------------------------------|

| Measure Voltage Mode                                                                                                                                                                                                      |                                                                         |                            |      |                            |                                     |

| Voltage Measurement Range                                                                                                                                                                                                 | VSENSE                                                                  | VEE + 2.5                  |      | VCC - 2.5                  | V                                   |

| Voltage Measurement Accuracy Offset Gain Linearity FORCE/SENSE Combined Leakage Current in HiZ (FV/FI*=0, FORCE/SENSE = VEE+2.5V to VCC-2.5V) IVMON Output Impedance IVMON Leakage Current (IVMON = VEE+2.5V to VCC-2.5V) | VOS<br>Gain<br>MV INL<br>I <sub>LEAK</sub><br>ROUT<br>I <sub>LEAK</sub> | -200<br>.985<br>025<br>-10 | ±.01 | 200<br>1.015<br>.025<br>10 | mV<br>V/V<br>%FSVR<br>nA<br>Ω<br>nA |

| Digital Inputs (FV/FI*, MI/MV*, RS0, RS1, DISABLE, TEST, HiZ, LTCH_MODE, SAMPLE)                                                                                                                                          |                                                                         |                            |      |                            |                                     |

| Input Low Level                                                                                                                                                                                                           | VIL                                                                     |                            |      | 0.8                        | V                                   |

| Input High Level                                                                                                                                                                                                          | VIH                                                                     | 2.0                        |      |                            | V                                   |

| Input Leakage Current                                                                                                                                                                                                     | lleak                                                                   | -1                         | 0    | 1                          | μΑ                                  |

| Voltage Clamps                                                                                                                                                                                                            |                                                                         |                            |      |                            |                                     |

| Range                                                                                                                                                                                                                     | SNK_MON -<br>SRC_MON                                                    | .5                         |      | 16.0                       | V                                   |

| Effective Output Impedance of Clamps                                                                                                                                                                                      | Rout                                                                    |                            |      | 10                         | Ω                                   |

| Sink Clamp Voltage Range                                                                                                                                                                                                  | SNK_MON                                                                 | VEE + 2.5                  |      | VCC - 2.0                  | V                                   |

| Source Clamp Voltage Range                                                                                                                                                                                                | SRC_MON                                                                 | VEE + 2.0                  |      | VCC - 2.5                  | V                                   |

| SRC_MON Leakage Current                                                                                                                                                                                                   | ILEAK                                                                   | -1                         |      | 1                          | μΑ                                  |

| SNK_MON Leakage Current                                                                                                                                                                                                   | I <sub>LEAK</sub>                                                       | -1                         |      | 1                          | μΑ                                  |

| Linearity @ 5 mA Constant Current                                                                                                                                                                                         | CLAMP INL                                                               | 400                        |      | +.400                      | % FSVR                              |

| Offset @ 5 mA Constant Current                                                                                                                                                                                            | VOS                                                                     | -150                       |      | +150                       | mV                                  |

| PPMU Voltage Clamps Current Interrupt Limit (OPEN_RLY Trigger Current)                                                                                                                                                    | ICLAMP                                                                  | 35                         |      | 95                         | mA                                  |

| PPMU Voltage Clamps Current Limiting Range                                                                                                                                                                                | I <sub>LIMIT</sub>                                                      | 35                         |      | 95                         | mA                                  |

| Output Low Voltage for OPEN_RLY Pin @ 1 mA                                                                                                                                                                                | V <sub>OL</sub>                                                         |                            |      | 500                        | mV                                  |

| TEST_IN Leakage Current                                                                                                                                                                                                   | I <sub>LEAK</sub>                                                       | -1                         |      | 1                          | μΑ                                  |

| OPEN_RLY Leakage Current @ 5V                                                                                                                                                                                             | I <sub>LEAK</sub>                                                       | -1                         |      | 1                          | μΑ                                  |

| Sample and Hold Circuit                                                                                                                                                                                                   |                                                                         |                            |      |                            |                                     |

| Linearity Error                                                                                                                                                                                                           | S&H INL                                                                 | 025                        | .01  | .025                       | % FSVR                              |

| Hold Step                                                                                                                                                                                                                 | V <sub>HS</sub>                                                         |                            | 16   | 20                         | mV                                  |

| TempCo of Hold Step (Note 3)                                                                                                                                                                                              | ΔV / Δ°C                                                                |                            |      | 50                         | μV/°C                               |

| Output Impedance of IVMON (Note 3)                                                                                                                                                                                        | Rout                                                                    |                            | 500  |                            | Ω                                   |

# DC Characteristics (continued)

| Parameter                                     | Symbol            | Min        | Тур | Max        | Units |

|-----------------------------------------------|-------------------|------------|-----|------------|-------|

| Short Circuit Protection                      |                   |            |     |            |       |

| Forcing Op-Amp Current Limit (Note 3)         | I <sub>MAX</sub>  | 35         |     | 75         | mA    |

| Driven Guard / Test Head Ground               |                   |            |     |            |       |

| GUARD - SENSE<br>@ DUT_GND = 0<br>SENSE = 5V  | V <sub>DIFF</sub> | -100       |     | +100       | mV    |

| DUT_GND to GND Voltage Range                  | Vos               | -250       |     | +250       | mV    |

| DUT_GND Leakage Current                       | I <sub>LEAK</sub> | -1         |     | 1          | μA    |

| Comparator                                    |                   |            |     |            |       |

| IVMAX Voltage Range                           | IVMAX             | VEE + 1.75 |     | VCC - 1.75 | V     |

| IVMIN Voltage Range                           | IVMIN             | VEE + 1.75 |     | VCC - 1.75 | V     |

| Comparator Offset (IVMIN, IVMAX)              | Vos               | -100       |     | +100       | mV    |

| Input Bias Current at (IVMIN, IVMAX, COMP_IN) | l <sub>bias</sub> | -1         |     | +1         | μΑ    |

| Digital Outputs (DUTLTH, DUTGTL)              |                   |            |     |            |       |

| Output Low Level (TBD load)                   | Vol               |            |     | 400        | mV    |

| Output High Level (TBD load)                  | V <sub>OH</sub>   | 2.4        |     | VDD        | V     |

Note 1: Gain =  $\frac{IVMON}{V_{EXT}}$ , where  $V_{EXT}$  is the voltage across  $R_{EXT}$ , which corresponds to measured current.

Note 2: Gain =  $\frac{V_{EXT}}{VINP - REF}$ , REF = 2.25V nominal,  $V_{EXT}$  is the voltage across  $R_{EXT}$ , which corresponds to forced current.

Note 3: Guaranteed by design and characterization. Not production tested.

Unit Definitions:

FSCR = Full Scale Current Range

Range A,  $\pm$  3.2  $\mu$ A

Range B, ± 80 µA

Range C,  $\pm$  2 mA

Range D, ± 30 mA

FSVR = Full Scale Voltage Range

FV mode, no current = 14V minimum

FV mode, current load = 12V minimum

MV mode = 14V minimum

# AC Characteristics

| Parameter                                                                                            | Symbol                                               | Min | Тур | Max      | Units    |

|------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----|-----|----------|----------|

| Force Voltage / Measure Current                                                                      |                                                      |     |     |          |          |

| FORCE Output Voltage Settling Time (Note 1) (To 0.1% of 10V step) RANGE A RANGES B, C, D             | <sup>t</sup> settle                                  |     |     | 2<br>300 | ms<br>µs |

| Measured Current Settling Time (Note 1) (To 0.1% of FSCR step) RANGE A RANGES B, C, D                | <sup>t</sup> settle                                  |     |     | 4<br>300 | ms<br>µs |

| Stability (Note 1) Capacitive Loading Range for Stable Operation                                     | C <sub>LOAD</sub>                                    | 0   |     | 10       | nF       |

| Force Amp Saturation Recovery Time HiZ True to FORCE Disable Time HiZ False to FORCE Enable Time     | t <sub>sr</sub><br>t <sub>z</sub><br>t <sub>oe</sub> |     | 25  | 1<br>15  | µs<br>µs |

| Force Current / Measure Voltage                                                                      |                                                      |     |     |          |          |

| FORCE Output Current Settling Time (Note 1) (To 0.1% of FSCR step) RANGE A RANGES B, C, D            | tsettle                                              |     |     | 4<br>300 | ms<br>µs |

| SENSE (Measure) Voltage Settling Time (Note 1)<br>(To 0.1% of 10V step)<br>RANGE A<br>RANGES B, C, D | tsettle                                              |     |     | 4<br>300 | ms<br>µs |

| Stability (Note 1) Capacitive Loading Range for Stable Operation                                     | C <sub>LOAD</sub>                                    | 0   |     | 10       | nF       |

| Force Amp Saturation Recovery Time HiZ True to FORCE Disable Time HiZ False to FORCE Enable Time     | t <sub>sr</sub><br>t <sub>z</sub><br>t <sub>oe</sub> |     | 25  | 1<br>15  | µs<br>µs |

| I/V Monitor                                                                                          |                                                      |     |     |          |          |

| Enable Time                                                                                          | toe                                                  |     |     | 500      | ns       |

| Disable Time                                                                                         | t <sub>z</sub>                                       |     |     | 500      | ns       |

# AC Characteristics (continued)

| Parameter                                                                                           | Symbol          | Min | Тур        | Max      | Units     |

|-----------------------------------------------------------------------------------------------------|-----------------|-----|------------|----------|-----------|

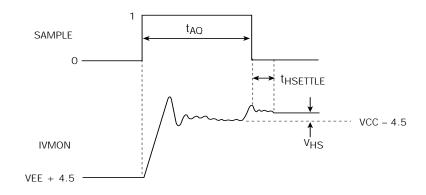

| Sample and Hold Circuit                                                                             |                 |     |            |          |           |

| Droop Rate                                                                                          | ΔV/Δt           |     |            | 40       | mV/s      |

| Acquisition Time (to 0.025% of Sampled Value)                                                       | t <sub>AQ</sub> |     | 1          | 10       | μs        |

| Hold Mode Settling Time (Notes 1, 2) Measure Voltage Mode To 0.1% of 10V Step To 0.025% of 10V Step | th settle       |     | 0.8<br>1.4 | 1.5<br>2 | μs<br>μs  |

| Measure Current Mode (Notes 1, 2) To 0.1% of 4V Step To 0.025% of 4V Step                           | thsettle        |     | 1.3<br>1.8 | 2<br>3   | μs<br>μsf |

| Comparators                                                                                         |                 |     |            |          |           |

| Propagation Delay                                                                                   | tpd             |     |            | 25       | μs        |

AC Test Conditions: COMP3 = 120 pF to Ground; COMP4 = 120 pF to FORCE; Capacitor between COMP1

COMP2 = 120 pF; Load at FORCE/SENSE combined output = 100 pF.

*Note 1:* Guaranteed by design and characterization. Not production tested.

Note 2: Sample and Hold Circuit Acquisition Time  $(t_{AQ})$  and Settling Time  $(t_{HSETTLE})$  are described below:

CONDITIONS:

$LTCH\_MODE = 1$ IVMON = 100 pF to GND

# Ordering Information

| Model Number | Package                    |

|--------------|----------------------------|