# **Revision History**

Revision 0.1 (Nov. 2011) -First release.

# 2Gb (16M×8Bank×16) Double DATA RATE 2 SDRAM

#### **Features**

- JEDEC Standard VDD/VDDQ = 1.8V±0.1V.

- All inputs and outputs are compatible with SSTL\_18 interface.

- Fully differential clock inputs (CK, /CK) operation.

- Eight Banks

- Posted CAS

- Bust length: 4 and 8.

- Programmable CAS Latency (CL): 5, 7

- Programmable Additive Latency (AL): 0, 1, 2, 3, 4, 5 & 6.

- Write Latency (WL) =Read Latency (RL) -1.

- Read Latency (RL) = Programmable Additive Latency (AL) + CAS Latency (CL)

- Bi-directional Differential Data Strobe (DQS).

- Data inputs on DQS centers when write.

- Data outputs on DQS, /DQS edges when read.

- On chip DLL align DQ, DQS and /DQS transition with CK transition.

- DM mask write data-in at the both rising and falling edges of the data strobe.

- Sequential & Interleaved Burst type available.

- Off-Chip Driver (OCD) Impedance Adjustment

- On Die Termination (ODT)

- Auto Refresh and Self Refresh

- 8,192 Refresh Cycles / 64ms

- Average Refresh Period 7.8us

- RoHS Compliance

- High Temperature Self-Refresh rate enable

#### Description

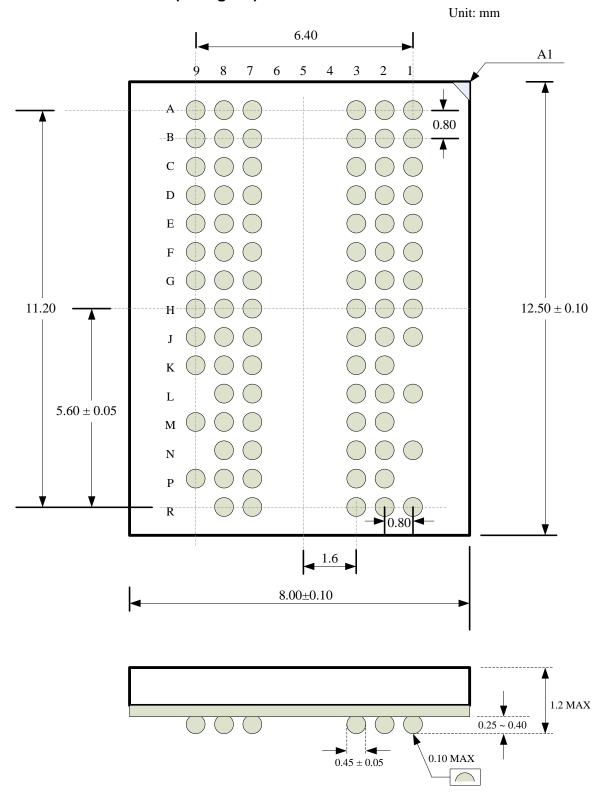

The EM44DM1688LBB is a high speed Double Date Rate 2 (DDR2) Synchronous DRAM fabricated with ultra high performance CMOS process containing 2,147,483,648 bits which organized as 16Mbits x 8 banks by 16 bits. This synchronous device achieves high speed double-data-rate transfer rates of up to 1066 Mb/sec/pin (DDR2-1066) for general applications. The chip is designed to comply with the following key DDR2 SDRAM features: (1) posted CAS with additive latency, (2) write latency = read latency -1, (3) Off-Chip Driver (OCD) impedance adjustment and On Die Termination (4) normal and weak strength data output driver. All of the control and address inputs are synchronized with a pair of externally supplied differential clocks. Inputs are latched at the cross point of differential clocks (CK rising and /CK falling). All I/Os are synchronized with a pair of bidirectional strobes (DQS and /DQS) in a source synchronous fashion. The address bus is used to convey row, column and bank address information in a /RAS and /CAS multiplexing style. The 2Gb DDR2 device operates with a single power supply:  $1.8V \pm 0.1V$  VDD and VDDQ. Available package: FBGA-84Ball (with 0.8mm x 0.8mm ball pitch)

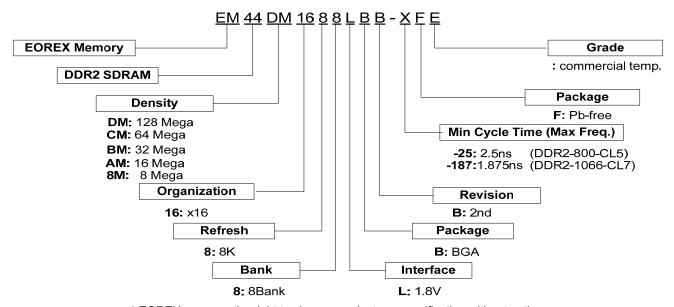

**Ordering Information**

| Part No            | Organization | Max. Freq     | Package  | Grade      | Pb   |

|--------------------|--------------|---------------|----------|------------|------|

| EM44DM1688LBB-25F  | 128M X 16    | DDR2-800-CL5  | FBGA-84B | Commercial | Free |

| EM44DM1688LBB-187F | 128M X 16    | DDR2-1066-CL7 | FBGA-84B | Commercial | Free |

### Parts Naming Rule

<sup>\*</sup> EOREX reserves the right to change products or specification without notice.

# Pin Assignment: Top View

| 1    | 2      | 3    |   | 7     | 8     | 9    |

|------|--------|------|---|-------|-------|------|

| VDD  | NC     | VSS  | Α | VSSQ  | /UDQS | VDDQ |

| DQ14 | VSSQ   | UDM  | В | UDQS  | VSSQ  | DQ15 |

| VDDQ | DQ9    | VDDQ | С | VDDQ  | DQ8   | VDDQ |

| DQ12 | VSSQ   | DQ11 | D | DQ10  | VSSQ  | DQ13 |

| VDD  | NC     | VSS  | Е | VSSQ  | /LDQS | VDDQ |

| DQ6  | VSSQ   | LDM  | F | LDQS  | VSSQ  | DQ7  |

| VDDQ | DQ1    | VDDQ | G | VDDQ  | DQ0   | VDDQ |

| DQ4  | VSSQ   | DQ3  | Н | DQ2   | VSSQ  | DQ5  |

| VDDL | VREF   | VSS  | J | VSSDL | СК    | VDD  |

|      | CKE    | /WE  | K | /RAS  | /CK   | ODT  |

| BA2  | BA0    | BA1  | L | /CAS  | /CS   |      |

|      | A10/AP | A1   | М | A2    | A0    | VDD  |

| vss  | А3     | A5   | N | A6    | A4    |      |

|      | A7     | A9   | Р | A11   | A8    | vss  |

| VDD  | A12    | NC   | R | NC    | A13   |      |

| VDD  |        |      |   |       |       |      |

#### 84Ball FBGA

Note: VDDL and VSSDL are power and ground for the DLL.

# Pin Description (Simplified)

| Pin                                                   | Name          | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|-------------------------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                       | '             | (System Clock)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| J8,K8                                                 | CK,/CK        | CK and CK are differential clock inputs. All address and control input signals are sampled on the crossing of the positive edge of CK and negative edge of CK. Output (read) data is referenced to the crossings of CK and CK (both directions of crossing).                                                                                                                                                                                                                                                                                                                                  |  |  |

|                                                       |               | (Chip Select)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| L8                                                    | /CS           | All commands are masked when CS is registered HIGH. CS provides for external Rank selection on systems with multiple Ranks. CS is considered part of the command code.                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|                                                       |               | (Clock Enable)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| K2                                                    | CKE           | CKE high activates and CKE low deactivates internal clock signals and device input buffers and output drivers. Taking CKE low provides Precharge Power-Down and Self- Refresh operation (all banks idle), or Active Power-Down (row Active in any bank). CKE is synchronous for power down entry and exit and for Self-Refresh entry. CKE is asynchronous for Self-Refresh exit. CKE must be maintained high throughout read and write accesses. Input buffers, excluding CK, /CK, ODT and CKE are disabled during Power Down. Input buffers, excluding CKE are disabled during Self-Refresh. |  |  |

|                                                       |               | (Address)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| M8,M3,M7,N2,<br>N8,N3,N7,P2,<br>P8,P3,M2,P7,<br>R2,R8 | A0~A13        | Provided the row address (RA0 – RA13) for Active commands and the column address (CA0-CA9) and Auto Precharge bit for Read/Write commands to select one location out of the memory array in the respective bank. A10 is sampled during a Precharge command to determine whether the Precharge applies to one bank (A10 LOW) or all banks (A10 HIGH). If only one bank is to be precharged, the bank is selected by BA0, BA1 & BA2. The address inputs also provide the op-code during Mode Register Set commands.                                                                             |  |  |

|                                                       |               | (Bank Address)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| L2,L3,L1                                              | BA0, BA1,BA2  | BA0 – BA2 define to which bank an Active, Read, Write or Precharge command is being applied. Bank address also determines if the mode register or extended mode register is to be accessed during a MRS or EMRS cycle.                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|                                                       |               | (On Die Termination)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| К9                                                    | ODT           | ODT (registered HIGH) enables termination resistance internal to the DDR2 SDRAM. When enabled, ODT is applied to each DQ, UDQS/UDQS, LDQS/LDQS, UDM, and LDM signal. The ODT pin will be ignored if the Extended Mode Register EMRS(1) is programmed to disable ODT.                                                                                                                                                                                                                                                                                                                          |  |  |

|                                                       |               | (Command Inputs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| K7, L7, K3                                            | /RAS,/CAS,/WE | /RAS, /CAS and /WE (along with /CS) define the command being entered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

# Pin Description (Continued)

| B7,A8,F7,E8                                                                 | UDQS,/UDQS<br>,<br>LDQS,/LDQS | (Data Strobe)  Output with read data, input with write data. Edge-aligned with read data, centered in write data. LDQS corresponds to the data on DQ0-DQ7; UDQS corresponds to the data on DQ8-DQ15. The data strobes LDQS and UDQS may be used in single ended mode or paired with optional complementary signals /LDQS and /UDQS to provide differential pair signaling to the system during both reads and writes. An EMRS(1) control bit enables or disables all complementary data strobe signals. In this data sheet, "differential DQS signals" refers to A10 = 0 of EMRS(1) using LDQS/LDQS and UDQS/UDQS.  "single-ended DQS signals" refers to A10 = 1 of EMRS(1) using LDQS and UDQS. |

|-----------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B3,F3                                                                       | UDM,LDM                       | (Input Data Mask)  DM is an input mask signal for write data. Input data is masked when DM is sampled HIGH coincident with that input data during a Write access. DM is sampled on both edges of DQS. Although DM pins are input only, the DM loading matches the DQ and DQS loading.                                                                                                                                                                                                                                                                                                                                                                                                            |

| G8,G2,H7,H3,<br>H1,H9,F1,F9,<br>C8,C2,D7,D3,<br>D1, D9,B1,B9                | DQ0~15                        | (Data Input/Output)  Data inputs and outputs are on the same pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| A1,E1,J9,M9,<br>R1/A3,E3,J3,<br>N1,P9                                       | VDD/VSS                       | (Power Supply/Ground) VDD and VSS are power supply for internal circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A9,C1,C3,C7,<br>C9,E9,G1,G3,<br>G7,G9/A7,B2,<br>B8,D2,D8,E7,<br>F2,F8,H2,H8 | VDDQ/VSSQ                     | (DQ Power Supply/DQ Ground) VDDQ and VSSQ are power supply for the output buffers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| J1/J7                                                                       | VDDL/VSSDL                    | (DLL Power Supply/DLL Ground)  VDDL and VSSDL are power supply for DLL circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| J2                                                                          | VREF                          | (Reference Voltage) SSTL_1.8 reference voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| A2,E2,R3,R7                                                                 | NC                            | (No Connection) No internal electrical connection is present.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

# Absolute Maximum Rating

| Symbol           | Item                        | Rati               | Rating      |    |

|------------------|-----------------------------|--------------------|-------------|----|

| Vin, Vout        | Input, Output Voltage       | -0.5 ~             | +2.3        | V  |

| V <sub>DD</sub>  | Power Supply Voltage        | -1.0 ~             | -1.0 ~ +2.3 |    |

| VDDQ             | Power Supply Voltage        | -0.5 ~ +2.3        |             | V  |

| V <sub>DDL</sub> | DLL Power Supply Voltage    | -0.5 ~             | -0.5 ~ +2.3 |    |

| Тор              | Operating Temperature Range | Commercial 0 ~ +70 |             | °C |

| Тѕтс             | Storage Temperature Range   | -55 ~ +100         |             | °C |

| PD               | Power Dissipation           | 1                  | 1           |    |

**Note:** Caution Exposing the device to stress above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational section of this specification. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

# Recommended DC Operating Conditions (T<sub>A</sub>=-0°C ~+70°C)

| Symbol           | Parameter                     | Min.                    | Тур.          | Max.                   | Units |

|------------------|-------------------------------|-------------------------|---------------|------------------------|-------|

| V <sub>DD</sub>  | Power Supply Voltage          | 1.7                     | 1.8           | 1.9                    | V     |

| V <sub>DDL</sub> | Power Supply for DLL Voltage  | 1.7                     | 1.8           | 1.9                    | V     |

| VDDQ             | Power Supply for I/O Voltage  | 1.7                     | 1.8           | 1.9                    | V     |

| VREF             | I/O Reference Voltage         | 0.49 V <sub>DDQ</sub>   | $0.50V_{DDQ}$ | 0.51 VDDQ              | V     |

| VTT              | I/O Termination Voltage       | VREF-0.04               | VREF          | V <sub>REF</sub> +0.04 | V     |

| VID              | DC Differential Input Voltage | -0.3                    | -             | VREF-0.15              | V     |

| VIH              | Input Logic High Voltage      | V <sub>REF</sub> +0.125 | -             | V <sub>DDQ</sub> +0.3  | V     |

| VIL              | Input Logic Low Voltage       | -0.3                    | -             | VREF-0.125             | V     |

### Recommended DC Operating Conditions

$(V_{DD}=1.8V\pm0.1V)$

| Symbol Parameter  |                                                                 | Test Conditions                                                                                                                                                                                                                                                                                              | -187(1066) | -25(800) | Units  |

|-------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|--------|

| Syllibol          | Parameter                                                       | Test Conditions                                                                                                                                                                                                                                                                                              | Ма         | X        | Ullits |

| I <sub>DD1</sub>  | Operating Current (Note 1)                                      | IOUT = 0mA BL = 4, CL = CL(IDD), AL = 0 tCK = tCK(IDD), tRC = tRC (IDD) tRAS = tRASmin(IDD), tRCD = tRCD(IDD) CKE=HIGH CS=HIGH between valid commands Address bus inputs are SWITCHING Data pattern is same as IDD4W                                                                                         | 140        | 120      | mA     |

| IDD2P             | Precharge Standby Current in Power Down Mode                    | All banks idle tCK = tCK(IDD), CKE is LOW Other control and address bus inputs are STABLE Data bus inputs are FLOATING                                                                                                                                                                                       | 12         | 12       | mA     |

| Idd2n             | Precharge Standby Current in NON-power down mode All banks idle | All banks idle tCK = tCK(IDD), CKE is HIGH, CS is HIGH Other control and address bus inputs are SWITCHING Data bus inputs are SWITCHING                                                                                                                                                                      | 70         | 60       | mA     |

| IDD3P             | Active Standby Current in Power Down Mode (A12=0)               | All banks open tCK = tCK(IDD), CKE is LOW Other control and address bus inputs are                                                                                                                                                                                                                           | 35         | 30       | mA     |

| I <sub>DD3P</sub> | Active Standby Current in Power Down Mode (A12=1)               | STABLE<br>Data bus inputs are FLOATING                                                                                                                                                                                                                                                                       | 25         | 25       | mA     |

| lddзn             | Active Standby Current in Non-power Down Mode                   | All banks open tCK = tCK(IDD), tRAS = tRASmax(IDD) tRP = tRP(IDD), CKE is HIGH CS is HIGH between valid commands Other control and address bus inputs are SWITCHING Data bus inputs are SWITCHING                                                                                                            | 80         | 70       | mA     |

| IDD4W             | Operating Current (Burst                                        | All banks open, Continuous burst writes BL = 4, CL = CL(IDD), AL = 0 tCK = tCK(IDD), tRAS = tRASmax(IDD) tRP = tRP(IDD), CKE is HIGH                                                                                                                                                                         | 230        | 200      | mA     |

| IDD4R             | Mode) (Note 2)                                                  | CS is HIGH between valid commands<br>Address bus inputs are SWITCHING<br>Data bus inputs are SWITCHING                                                                                                                                                                                                       | 230 200    |          |        |

| IDD5              | Refresh Current (Note 3)                                        | tCK = tCK(IDD) Refresh command at every tRFC(IDD) interval CKE is HIGH, CS is HIGH between valid commands Other control and address bus inputs are SWITCHING Data bus inputs are SWITCHING                                                                                                                   | 140        | 130      | mA     |

| IDD6              | Self Refresh Current                                            | CK and CK at 0 V, CKE 0.2 V Other control and address bus inputs are FLOATING, Data bus inputs are FLOATING                                                                                                                                                                                                  | 10         | 10       | mA     |

| I <sub>DD7</sub>  | Operating Current                                               | All bank interleaving reads IOUT = 0mA, BL = 4, CL = CL(IDD) AL = tRCD(IDD) - 1 x tCK(IDD) tCK = tCK(IDD), tRC = tRC(IDD) tRRD = tRRD(IDD), tFAW = tFAW(IDD) tRCD = 1 x tCK(IDD), CKE is HIGH CS is HIGH between valid commands Address bus inputs are STABLE during DESELECTs Data pattern is same as IDD4R | 190        | 170      | mA     |

<sup>\*</sup>All voltages referenced to VSS.

Note 1: IDD1 depends on output loading and cycle rates. (CL=CLmin, AL=0)

Note 2: IDD4 depends on output loading and cycle rates. Input signals SWITCHING

Note 3: Min. of trec (Auto refresh Row Cycle Times) is shown at AC Characteristics.

# Recommended DC Operating Conditions (Continued)

| Symbol | Parameter                     | Test Conditions | Min.  | Max.  | Units |

|--------|-------------------------------|-----------------|-------|-------|-------|

| IOH    | Output Minimum Source Current | *Note1, 3, 4    | -13.4 |       | mA    |

| IOL    | Output Minimum Sink Current   | *Note2, 3, 4    |       | +13.4 | mA    |

**Note1:** VDDQ = 1.7 V; VOUT = 1.42 V. (VOUT-VDDQ) / IOH must be less than 21 ohm for values of VOUT between VDDQ and VDDQ - 280 mV.

**Note2:** VDDQ = 1.7 V; VOUT = 280 mV. VOUT / IOL must be less than 21 ohm for values of VOUT between 0V and 280 mV.

*Note3:* The dc value of VREF applied to the receiving device is set to VTT.

Note4: The values of IOH(dc) and IOL(dc) are based on the conditions given in note 1 and 2. They are used to test drive current capability to ensure VIHmin plus a noise margin and VILmax minus a noise margin are delivered to an SSTL\_18 receiver. The actual current values are derived by shifting the desired driver operating points along 21ohm load line to define a convenient current for measurement.

Note5: The VDDQ of the device under test is referenced.

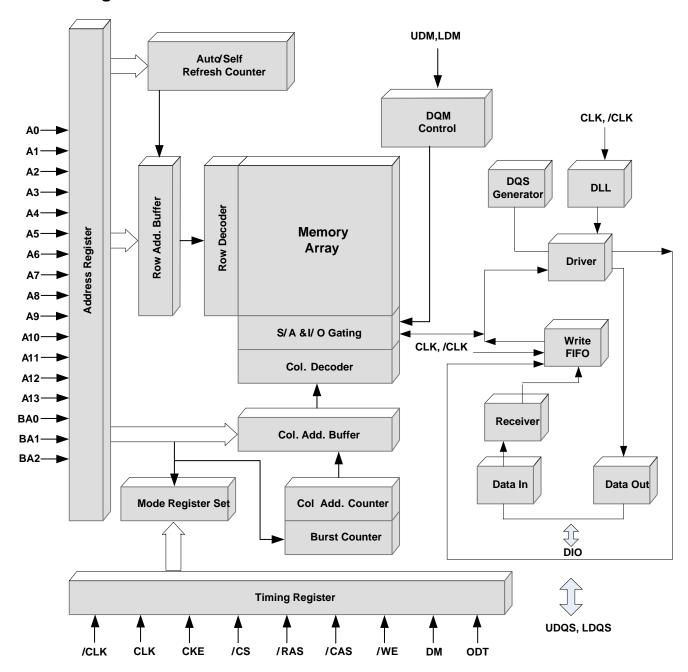

### **Block Diagram**

# **OCD Default Setting Table**

| Parameter                                      | Min. | Тур. | Max. | Units |

|------------------------------------------------|------|------|------|-------|

| Output Impedance step size for OCD calibration | 0    | -    | 1.5  | Ω     |

| Pull-up / Pull-down mismatch                   | 0    | -    | 4    | Ω     |

| Output Slew Rate                               | 1.5  | -    | 5.0  | V/ns  |

# **AC Operating Test Conditions**

(V<sub>DD</sub>=1.8V±0.1V)

| Symbol                    | Parameter                               | Value         | Units |

|---------------------------|-----------------------------------------|---------------|-------|

| V <sub>SWING</sub> (max.) | Input Signal Maximum Peak to Peak Swing | 1.0           | ٧     |

| SLEW                      | Input Signal Minimum Slew Rate          | 1.0           | V/ns  |

| $V_{REF}$                 | Input Reference Level                   | $0.5*V_{DDQ}$ | V     |

# **AC Operating Test Conditions**

| Symbol          | Parameter                                  | Min.                        | Max.                        | Units |

|-----------------|--------------------------------------------|-----------------------------|-----------------------------|-------|

| $V_{\text{ID}}$ | AC Differential Input Voltage              | 0.5                         | $V_{DDQ}$                   | V     |

| V <sub>IX</sub> | AC Differential Cross Point Input Voltage  | 0.5*V <sub>DDQ</sub> -0.175 | 0.5*V <sub>DDQ</sub> +0.175 | V     |

| V <sub>OX</sub> | AC Differential Cross Point Output Voltage | 0.5*V <sub>DDQ</sub> -0.125 | 0.5*V <sub>DDQ</sub> +0.125 | V     |

| V <sub>IH</sub> | Input Logic High Voltage                   | V <sub>REF</sub> +0.2       | $V_{DDQ}$ + $V_{peak}$      | V     |

| V <sub>IL</sub> | Input Logic High Voltage                   | $V_{SSQ}$ - $V_{peak}$      | V <sub>REF</sub> -0.2       | V     |

# AC Operating Test Characteristics

$(V_{DD}=1.8V\pm0.1V)$

| Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | O. mada ad            | Deservator                           | -187 (DDR2-1066)  |                 | -25 (DDR2-800)    |                 | Units           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------------------------|-------------------|-----------------|-------------------|-----------------|-----------------|

| todsck         DQS output access from CLK,/CLK         -350         350         -350         350         ps           t_CL, t_CH         CL low/high level width         0.48         0.52         0.48         0.52         t <sub>CK</sub> t_CK         Clock Cycle Time         1.875         8         2.5         8         ns           t_DS         DQ and DM setup time         50         -         50         -         ps           t_DH         DQ and DM hold time         75         -         125         -         ps           t_DH         DQ and DM input pulse width for each input         0.35         -         0.35         -         tck           t_HZ         DATE out high impedance time from CLK,/CLK         -         t_AC         -         t_AC         -         t_AC         -         t_AC         -         t_AC         -         -         t_AC         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Symbol                | Parameter                            | Min.              | Max.            | Min.              | Max.            |                 |

| t <sub>CL,t</sub> CH         CL low/high level width         0.48         0.52         0.48         0.52         t <sub>CK</sub> t <sub>CK</sub> Clock Cycle Time         1.875         8         2.5         8         ns           t <sub>DS</sub> DQ and DM setup time         50         -         50         -         ps           t <sub>DH</sub> DQ and DM hold time         75         -         125         -         ps           t <sub>DH</sub> DQ and DM input pulse width for each input         0.35         -         0.35         -         t <sub>CK</sub> t <sub>HZ</sub> Data out high impedance time from CLK,/CLK         -         t <sub>AC</sub> (max)         -         t <sub>AC</sub> (max)         ns           t <sub>LZ (DQ)</sub> DQ low impedance time from CLK,/CLK         2*t <sub>AC</sub> (min)         t <sub>AC</sub> (max)         t <sub>AC</sub> (max)         ns           t <sub>LZ (DQS)</sub> DQS,/DQS low impedance time from CLK,/CLK         t <sub>AC</sub> (min)         t <sub>AC</sub> (max)         t <sub>AC</sub> (max)         ns           t <sub>DQS</sub> ,/DQS low impedance time from CLK,/CLK         t <sub>AC</sub> (min)         t <sub>AC</sub> (max)         ns         ns           t <sub>DQS</sub> ,/DQS low impedance time from CLK,/CLK         t <sub>AC</sub> (min)         t <sub>AC</sub> t <sub>AC</sub> t <sub>AC</sub> (min)         ns         ns           t <sub>DSS</sub> , t <sub>DQS</sub> ,DQS low impedance time from CLK,/CLK         t <sub>AC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | t <sub>AC</sub>       | DQ output access from CLK,/CLK       | -350              | 350             | -400              | 400             | ps              |

| t <sub>CK</sub> Clock Cycle Time         1.875         8         2.5         8         ns           t <sub>DS</sub> DQ and DM setup time         50         -         50         -         ps           t <sub>DH</sub> DQ and DM hold time         75         -         125         -         ps           t <sub>DHPW</sub> DQ and DM input pulse width for each input         0.35         -         0.35         -         t <sub>CK</sub> t <sub>LZ</sub> (DQ)         Data out high impedance time from CLK,/CLK         -         t <sub>AC</sub> (max)         -         t <sub>AC</sub> (max)         -         t <sub>AC</sub> (max)         ns           t <sub>LZ</sub> (DQ)         DQ low impedance time from CLK,/CLK         2*t <sub>AC</sub> (min) (max)         t <sub>AC</sub> (max)         t <sub>AC</sub> t <sub>AC</sub> (max)         t <sub>AC</sub> t <sub>AC</sub> t <sub>AC</sub> t <sub>AC</sub> (max)         ns           t <sub>LZ</sub> (DQS)         DQS,/DQS low impedance time from CLK,/CLK         t <sub>AC</sub> | t <sub>DQSCK</sub>    | DQS output access from CLK,/CLK      | -350              | 350             | -350              | 350             | ps              |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $t_{CL}, t_{CH}$      | CL low/high level width              | 0.48              | 0.52            | 0.48              | 0.52            | t <sub>CK</sub> |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | t <sub>CK</sub>       | Clock Cycle Time                     | 1.875             | 8               | 2.5               | 8               | ns              |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | t <sub>DS</sub>       | DQ and DM setup time                 | 50                | -               | 50                | -               | ps              |

| the text of the te                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | t <sub>DH</sub>       | DQ and DM hold time                  | 75                | -               | 125               | -               | ps              |

| tHz         CLK/CLK         -         (max)         -         (max)         ns           tLZ (DQ)         DQ low impedance time from CLK,/CLK         2*tAC (min)         tAC (max)         tAC (min)         ms           tDQSQ         DQS low,HQS low impedance time from CLK,/CLK         tAC (min)         tAC (min)         ms         ms           tQHS         DQS sex bow impedance time from CLK,/CLK         tAC (min)         tAC (min)         ms         ms           tQHS         DQS low,HQB impedance time from CLK,/CLK         TAC (min)         ms         ms         ms           tDQSQ         DQS base feather                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | t <sub>DIPW</sub>     |                                      | 0.35              | -               | 0.35              | -               | t <sub>CK</sub> |

| $t_{LZ(DO)}  DQ \ low \ impedance \ time \ from \ CLK,/CLK \\ t_{LZ(DQS)}  DQS,/DQS \ low \ impedance \ time \ from \\ t_{LZ(DQS)}  DQS,/DQS \ low \ impedance \ time \ from \\ t_{LZ(DQS)}  DQS,/DQS \ low \ impedance \ time \ from \\ CLK,/CLK  ms \\ t_{DQSQ}  DQS-DQ \ skew \ for \ associated \ DQ \ signal \\ t_{DQSD}  Data \ hold \ skew \ factor  - 250  - 300  ps \\ t_{DQSS}  Write \ command \ to \ first \ latching \ DQS \\ transition  -0.25  0.25  -0.25  0.25  t_{CK} \\ t_{DQSL} \ t_{DQSL}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | t <sub>HZ</sub>       |                                      | -                 |                 | -                 |                 | ns              |

| t <sub>LZ (DQS)</sub> DQS,/DQS low impedance time from CLK,/CLK         t <sub>AC</sub> (min)         t <sub>AC</sub> (max)         t <sub>AC</sub> (min)         t <sub>AC</sub> (max)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | t <sub>LZ (DQ)</sub>  | · ·                                  | 2*t <sub>AC</sub> | · · ·           | 2*t <sub>AC</sub> | ` ,             | ns              |

| t_Lz (DQS)         CLK,/CLK         (min)         (max)         (min)         (max)         ns           t_DQSQ         DQS-DQ skew for associated DQ signal         -         175         -         200         ps           t_DHS         Data hold skew factor         -         250         -         300         ps           t_DHS         Write command to first latching DQS transition         -0.25         0.25         -0.25         0.25         t_CK           t_DQSL, t_DGH         DQS Low/High input pulse width         0.35         -         0.35         -         t_CK           t_DSL, t_DSH         DQS input valid window         0.20         -         0.20         -         t_CK           t_MRD         Mode Register Set command cycle time         2         -         2         -         t_CK           t_WPRES         Write Preamble setup time         0         -         0         -         ns           t_WPST         Write Postamble         0.4         0.6         0.4         0.6         t_CK           t_IS         Address/control input setup time (fast slew rate)         0.25         -         0.275         -         ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (,                    |                                      | · · ·             | ` '             | . ,               | ` '             |                 |

| t <sub>DQSQ</sub> DQS-DQ skew for associated DQ signal         -         175         -         200         ps           t <sub>QHS</sub> Data hold skew factor         -         250         -         300         ps           t <sub>DQSS</sub> Write command to first latching DQS transition         -0.25         0.25         -0.25         0.25         t <sub>CK</sub> t <sub>DQSL</sub> ,t <sub>DQSH</sub> DQS Low/High input pulse width         0.35         -         0.35         -         t <sub>CK</sub> t <sub>DSL</sub> ,t <sub>DSH</sub> DQS input valid window         0.20         -         0.20         -         t <sub>CK</sub> t <sub>MRD</sub> Mode Register Set command cycle time         2         -         2         -         t <sub>CK</sub> t <sub>WPRES</sub> Write Preamble setup time         0         -         0         -         ns           t <sub>WPST</sub> Write Postamble         0.4         0.6         0.4         0.6         t <sub>CK</sub> t <sub>IS</sub> Address/control input setup time (fast slew rate)         0.175         -         0.20         -         ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | t <sub>LZ (DQS)</sub> |                                      | t <sub>AC</sub>   | t <sub>AC</sub> | t <sub>AC</sub>   | t <sub>AC</sub> | ns              |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                       |                                      | , ,               | ` ′             | ` ,               | ` ,             |                 |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                       |                                      | -                 | _               | -                 |                 | · ·             |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | t <sub>QHS</sub>      |                                      | -                 | 250             | -                 | 300             | ps              |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | t <sub>DQSS</sub>     |                                      | -0.25             | 0.25            | -0.25             | 0.25            | t <sub>CK</sub> |