### Preliminary specification

## Analog Voice Scrambler / Descrambler

The PCD4440 is a silicon gate CMOS integrated circuit intended to be used in radio, mobileand line powered telecommunications products utilizing a microcontroller for the control functions. Analog scrambling / descrambling is based on the split frequency method realized in a sophisticated switched-capacitor technology. The PCD4440 is compatible with most microcontrollers and communicates via a two line bidirectional bus (I<sup>2</sup>C).

#### **Features**

- Scrambler or descrambler function

- Scrambling in frequency domain

- Selectable split frequency (up to 10 selections per second)

- Telephony-band filtering included

- No increase in bandwidth

- No external components required

- Small signal delay

- Insensitive to distortion and group delay of transmission channel

- Control via serial (I2C) bus

- Low transfer loss of speech

- Mute option

- Transparent mode

- High signal input impedance

- Low signal output impedance

- Low power consumption

### **Applications**

- Cordless telephones

- Security telephones

- Portable phones

- PMR

### Package outlines

PCD4440T: 8-lead mini-pack (SO8L; SOT176C)

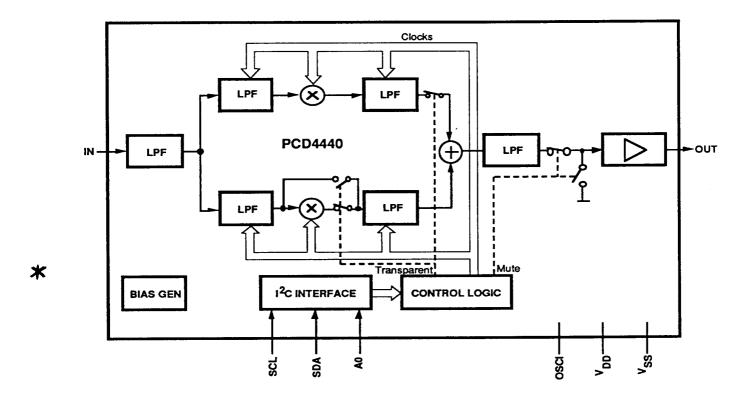

## **BLOCK DIAGRAM**

Fig. 1 Block diagram PCD4440

PHILIPS 2 FEB 92

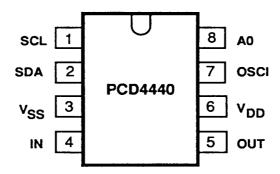

## PINNING DIAGRAM

Fig. 2 Pinning PCD4440T

| Pin | Name     | Function                  |

|-----|----------|---------------------------|

| 1   | SCL      | Serial Clock Line (I2C)   |

| 2   | SDA      | Serial Data Line (I2C)    |

| 3   | $V_{SS}$ | Negative Supply           |

| 4   | IN       | Signal input              |

| 5   | OUT      | Signal output             |

| 6   | $V_{DD}$ | Positive supply           |

| 7   | OSCI     | Oscillator input          |

| 8   | Α0       | Slave address input (I2C) |

|     |          |                           |

#### **FUNCTIONAL DESCRIPTION**

To provide privacy for the end user of a cordless telephone set, the radio-link audio signal must be scrambled. In the microphone as well as the incoming telephone line audio path a scrambler circuit has to be implemented. Consequently the audio signal to the telephone line as well as to the earpiece must be descrambled. Both functions can be fulfilled by the PCD4440 by simply inserting it in the audio path.

The PCD4440 accomplishes this task by first filtering the incoming signal, limiting the bandwidth to 3500 Hz. Then the signal is split into a high (> f<sub>S</sub>) and a low (< f<sub>S</sub>) frequency band. Both frequency bands are inverted and added again to provide a single output signal. Values for 9 split frequencies f<sub>S</sub> can be controlled by a scramble code table in the microcontroller. Control of these split frequencies is accomplished via the serial two wire I<sup>2</sup>C bus (see table 1). In addition to the split frequencies (f<sub>S</sub>), a transparent mode and mute instruction can be selected (see table 1).

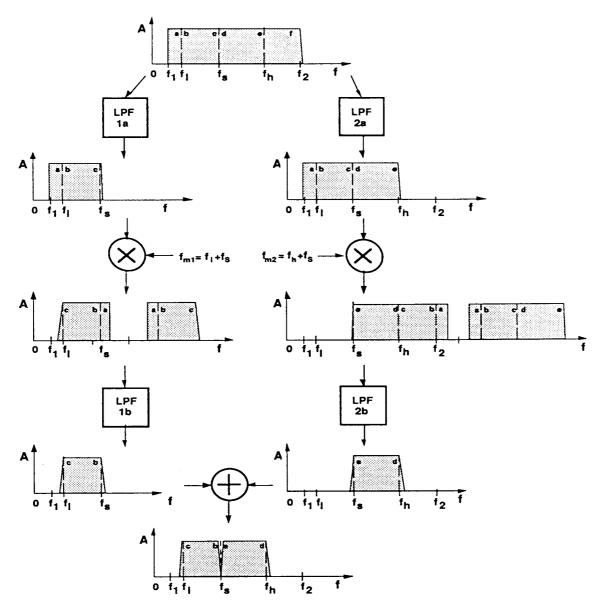

In Fig. 3, the signal path for both bands is drawn. The lower band path (on the left side of the diagram) works on frequencies  $f \le f_S$  (Split Frequency), the upper band path (on the right side) on frequencies  $f \ge f_S$ .

PHILIPS 4 FEB 92

Fig. 3 Scrambler signal path

The input signal contains frequencies from f<sub>1</sub> up to f<sub>2</sub>. The output signal is bandlimited (only in scrambling mode) from f<sub>I</sub> (300 Hz) to f<sub>h</sub> (3500 Hz). In the left path, the input signal is first limited to fs. The following modulator inverts the lower band. fl is folded up to fs, fs down to fl. In general, an input frequency  $f_{in}$  is folded to  $f_{out} = f_S + f_I - f_{in}$ . Finally the folded signal is bandlimited to fs again.

In the right path, the input signal is first limited to fh. The following modulator inverts the upper band.  $f_S$  is folded up to  $f_h$ ,  $f_h$  down to  $f_S$ . In general, an input frequency  $f_{in}$  is folded to  $f_{out} = f_S + f_{out}$ fh - fin. Finally, the folded signal is bandlimited to fh again. In the last step, the bands are added and buffered.

5 **FEB 92 PHILIPS**

$\star$

In the transparent mode, the input signal is band limited to 3500 Hz. Frequencies form 0 - 300 Hz are not filtered out.

## Power supply (V<sub>DD</sub>, V<sub>SS</sub>)

The positive supply of the circuit ( $V_{DD}$ ) must meet the voltage requirement as indicated in the characteristics. To avoid undefined states of the device when powered-on, an internal power-on circuit clears the control logic. The power-on reset has the highest priority; it blocks and resets the complete circuit.

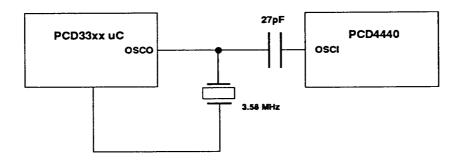

## Oscillator (OSCI)

The time base for the PCD4440 is a 3.58 MHz input signal which can be derived from OSCO (oscillator output) of Philips' microcontroller families PCD33xx or PCF84Cxx.

Figure 4 OCSI (freq. input) connection

PHILIPS 6 FEB 92

| D3 | D2 | D1 | D0 | HEX | APPLICATION                        | Fs (Hz*) |

|----|----|----|----|-----|------------------------------------|----------|

| 0  | 0  | 0  | 1  | 01  | MUTE MODE                          | -        |

| 0  | 0  | 1  | 0  | 02  | SELECT Fs                          | 2461     |

| 0  | 0  | 1  | 1  | 03  | SELECT Fs                          | 1853     |

| 0  | 1  | 0  | 0  | 04  | SELECT Fs                          | 1507     |

| 0  | 1  | 0  | 1  | 05  | SELECT Fs                          | 1279     |

| 0  | 1  | 1  | 0  | 06  | SELECT Fs                          | 1117     |

| 0  | 1  | 1  | 1  | 07  | SELECT Fs                          | 1018     |

| 1  | 0  | 0  | 0  | 08  | SELECT Fs                          | 899      |

| 1  | 0  | 0  | 1  | 09  | SELECT Fs                          | 837      |

| 1  | 0  | 1  | 0  | 0A  | SELECT Fs                          | 767      |

| 1  | 0  | 1  | 1  | ОВ  | Transparent Mode                   | •        |

| 1  | 1  | 1  | 1  | 0F  | Start scramble/<br>descramble mode | •        |

\*Fosc=3.58MHz

Table 1 input data code

Note: input codes other than shown in the table are not allowed.

## Serial clock input (SCL), Serial data input (SDA)

SCL and SDA are serial clock and data lines according to the Philips' I<sup>2</sup>C bus specification (see CHARACTERISTICS OF THE I<sup>2</sup>C BUS). Both inputs must be pulled-up externally to  $V_{DD}$  (through approximately  $10K\Omega$ ).

## Address input (A0)

A0 is the slave address input and it identifies the device when up to two PCD4440 devices are connected to the same I2C bus. In any case A0 must be connected to  $V_{DD}$  or  $V_{SS}$ .

PHILIPS 7 FEB 92

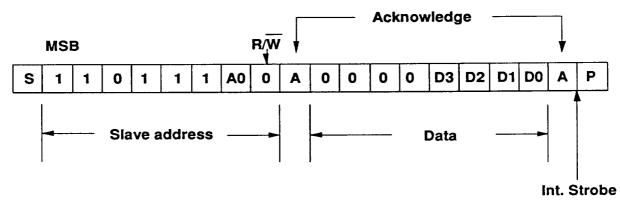

## I2C bus data configuration (see fig. 5)

The PCD4440 is always a slave receiver in the I<sup>2</sup>C bus configuration (R/W bit = 0). The slave address consist of 7 bits, where the least significant bit is selectable by hardware on input A0. The more significant bits are internally fixed. See figure 5, "I<sup>2</sup>C bus data format". For definition of D0-D4, see table 1.

Figure 5 I2C bus data format

# ★ Signal input (IN), Signal output (OUT)

Signal input for the scrambler / descrambler is coupled into a Sallen and Key anti-aliasing filter configuration. A DC bias voltage of  $1/2V_{DD}$  is built-in.

The analog signal output is buffered to achieve a relatively low output impedance of roughly 1  $K\Omega$  which is sufficiently low to drive the earpiece amplifier or similar application.

PHILIPS 8 FEB 92

## CHARACTERISTICS OF THE I2C BUS

The I<sup>2</sup>C-bus is for bi-directional, two-line communication between different ICs or modules. The two lines are a serial data line (SDA) and a serial clock line (SCL). Both lines must be connected to a positive supply via a pull-up resistor. Data transfer may be initiated only when the bus is not busy.

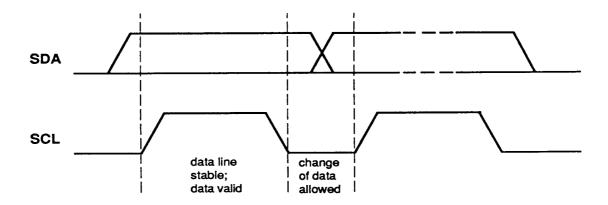

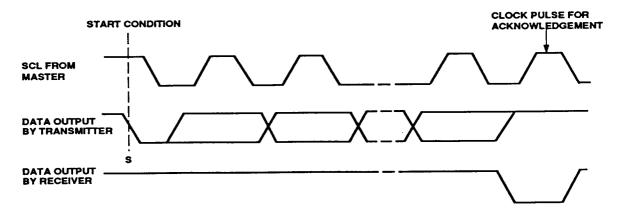

### Bit transfer

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the HIGH period of the clock pulse as changes in the data line at this time will be interpreted as a control signal.

Fig. 6 Bit transfer

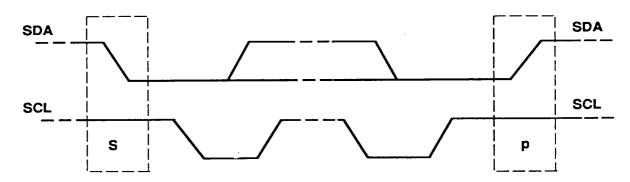

## Start and stop conditions

Both data and clock lines remain HIGH when the bus is not busy. A HIGH-to-LOW transition of the data line, while the clock is HIGH is defined as the start condition (S). A LOW-to-HIGH transition of the data line while the clock is HIGH is defined as the stop condition (P).

Fig. 7 Definition of start and stop conditions

PHILIPS 9 FEB 92

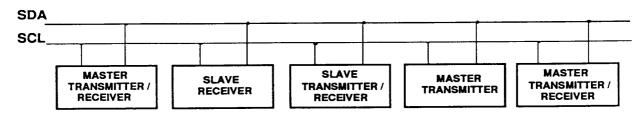

## System configuration

A device generating a message is a "transmitter", a device receiving a message is the "receiver". The device that controls the message is the "master" and the devices which are controlled by the master are the "slaves".

Fig.8 System configuration

## Acknowledge

The number of data bytes transferred between the start and stop conditions from transmitter to receiver is unlimited. Each byte of eight bits is followed by an acknowledge bit. The acknowledge bit is a HIGH level put on the bus by the transmitter during which time the master generates an extra acknowledge related clock pulse. A slave receiver which is addressed must generate an acknowledge after the reception of each byte. Also a master receiver must generate an acknowledge after the reception of each byte that has been clocked out of the slave transmitter. The device that acknowledges must pull down the SDA line during the acknowledge clock pulse, so that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse (set-up and hold times must be taken into consideration). A master receiver must signal an end of data to the transmitter by not generating an acknowledge on the last byte that has been clocked out of the slave. In this event the transmitter must leave the data line HIGH to enable the master to generate a stop condition.

Fig. 9 Acknowledgement on the I2C-bus

Note: The general characteristics and detailed specification of the I<sup>2</sup>C-Bus are available on request.

PHILIPS 10 FEB 92

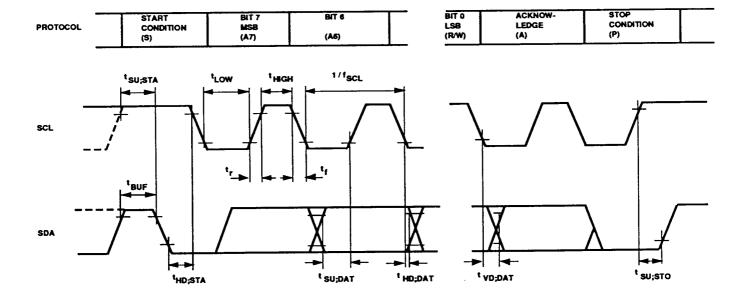

### 12C BUS TIMING SPECIFICATIONS

All the timing values area valid within the operating supply voltage and ambient temperature range and refer to  $V_{il}$  and  $V_{ih}$  with an input voltage swing of  $V_{ss}$  to  $V_{DD}$ .

| Parameter                   | symbol              | min. | max. | units |

|-----------------------------|---------------------|------|------|-------|

| SCL clock frequency         | fscL                | 0    | 100  | kHz   |

| Tolerable bus spike width   | T <sub>sw</sub>     | -    | 100  | ns    |

| Bus free time               | T <sub>buf</sub>    | 4.7  | -    | μs    |

| Start condition set-up time | T <sub>su;STA</sub> | 4.7  | -    | μs    |

| Start condition hold time   | T <sub>hd;STA</sub> | 4.0  | -    | μs    |

| SCL LOW time                | Tlow                | 4.7  | -    | μs    |

| SCL HIGH time               | $T_{high}$          | 4.0  | -    | μs    |

| SCL and SDA rise time       | $T_r$               | -    | 1.0  | μs    |

| SCL and SDA fall time       | $T_f$               | -    | 0.3  | μs    |

| Data set-up time            | $T_{su;DAT}$        | 250  | -    | ns    |

| Data hold time              | $T_{hd;DAT}$        | 0    | -    | ns    |

| Stop condition set-up time  | T <sub>su;STO</sub> | 4.0  | -    | μs    |

Fig. 10 I2C-bus timing diagram

### **CHARACTERISTICS**

$V_{DD}$  = 5.0 V;  $V_{SS}$  = 0 V;  $T_{amb}$  = +25 °C;  $f_{osc}$  = 3.579 MHz unless otherwise specified

| parameter                                                                                                                                                        | Symbol                                                         | Conditions                                     | Min                                 | Тур                               | Max                                         | Units              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------|-------------------------------------|-----------------------------------|---------------------------------------------|--------------------|

| Supply Supply voltage Supply current mute mode Operating                                                                                                         | V <sub>DD</sub>                                                | V <sub>DD</sub> = 3 V<br>V <sub>DD</sub> = 3 V | 2.8<br>-<br>-                       | -<br>2.2<br>13                    | 6.0                                         | V<br>mA<br>mA      |

| Inputs/Outputs  A0; SCL; SDA Input voltage LOW Input voltage HIGH input capacitance  SDA output current low at VoL = 0.4 V                                       | V <sub>IL</sub><br>V <sub>IH</sub><br>C <sub>1</sub>           |                                                | 0<br>0.7V <sub>DD</sub><br>-<br>3.0 |                                   | 0. 3V <sub>DD</sub><br>V <sub>DD</sub><br>7 | V<br>V<br>pF<br>mA |

| Signal input<br>IN<br>DC voltage level<br>allowed amplitude<br>input impedance                                                                                   | V <sub>DC</sub><br>V <sub>i(P-P)</sub><br>abs(Z <sub>i</sub> ) | freq. = 1 kHz                                  | -<br>-<br>-                         | 1/2V <sub>DD</sub><br>1.25<br>120 | -<br>V <sub>DD</sub> -1<br>-                | V<br>V<br>kΩ       |

| Signal output OUT DC voltage level output impedance Unwanted Frequency Supression at $V_{i(P-P)} = 1.25 \text{ V}$ $F_{split} = 767 \text{ or } 2461 \text{ Hz}$ | V <sub>DC</sub><br>abs(Z <sub>0</sub> )                        | freq. = 1 kHz                                  | -                                   | 1/2V <sub>DD</sub><br>-           | -<br>1                                      | V<br>kΩ            |

| F <sub>in</sub> = 1 kHz  Transfer loss V <sub>o</sub> / V <sub>i</sub> :  transparent mode operating mode                                                        | ufs<br>abs(A <sub>tr</sub> )<br>abs(A <sub>op</sub> )          | V <sub>DD</sub> = 3 V or 5 V                   | 40                                  | 3.5<br>0                          | -                                           | dB<br>dB<br>dB     |

| Freq. input OSCI DC voltage level Input voltage LOW Input voltage HIGH                                                                                           | V <sub>DC</sub><br>V <sub>IL</sub><br>V <sub>IH</sub>          |                                                | -<br>-<br>0.7V <sub>DD</sub>        | 1/2V <sub>DD</sub><br>-<br>-      | -<br>0.3V <sub>DD</sub><br>-                | V<br>V<br>V        |

PHILIPS 12 FEB 92

### **ABSOLUTE MAXIMUM RATINGS**

Limiting values in accordance with the Absolute Maximum System (IEC 134)

| Supply voltage range                | $V_{DD}$           | -0.3 V to 7.0 V                 |

|-------------------------------------|--------------------|---------------------------------|

| Voltage range on any input*         | VI                 | -0.8 to V <sub>DD</sub> + 0.8 V |

| DC input current (any input)        | +/- i <sub>i</sub> | 10 mA                           |

| DC output current (any input)       | +/- I <sub>O</sub> | 20 mA                           |

| Total power dissipation             | P <sub>TOT</sub>   | 300 mW                          |

| Power dissipation per output        | P                  | 50 mW                           |

| Operating ambient temperature range | T <sub>AMB</sub>   | -25 to +70 °C                   |

| Storage temperature range           | T <sub>STR</sub>   | -65 to +150 °C                  |

<sup>\*</sup>Measured via a 500 Ohm resistor

Note: Stresses above those listed under "ABSOLUTE MAXIMUM RATINGS" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating condition for extended periods may affect reliability.

## **HANDLING**

Inputs and Outputs are protected against electrostatic discharge in normal handling. However, it is good practice to take normal precautions appropriate to handling MOS devices (see "Handling MOS devices").

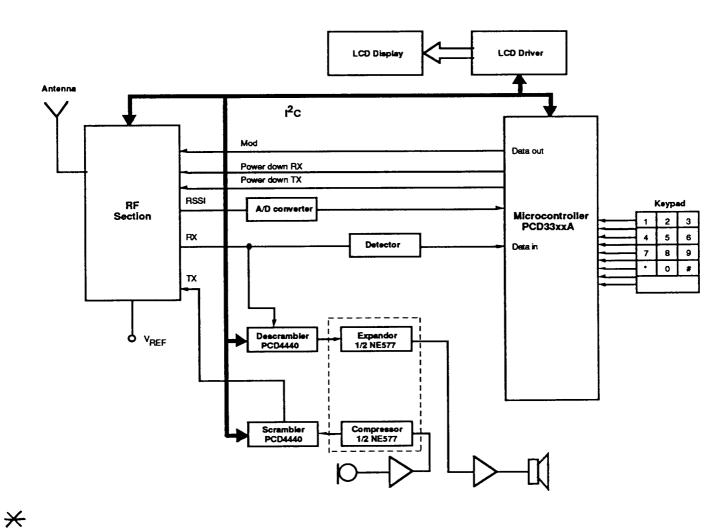

Fig. 11 Typical application: CT0 handset with direct (Manchester code) data system

**/**\

PHILIPS 14 FEB 92

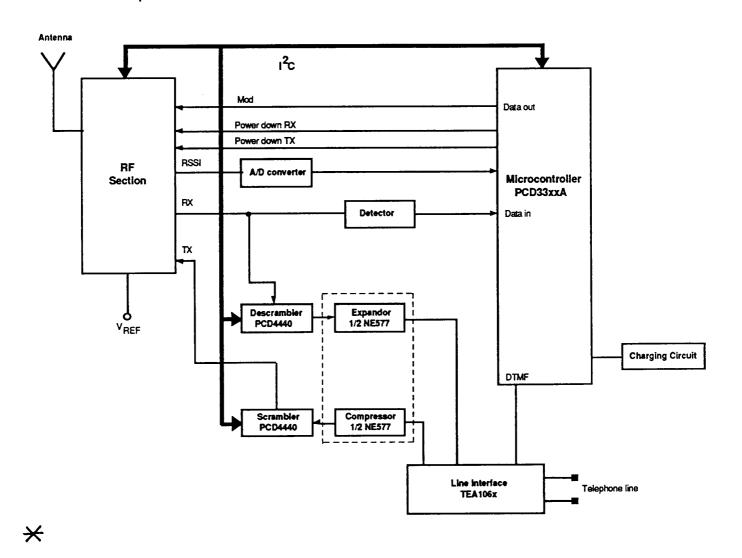

Fig. 12 Typical applications; CT0 Base unit with direct (Manchester code) data system

PHILIPS 15 FEB 92

#### **DEFINITIONS**

#### Data sheet status

Objective specification:

This data sheet contains target or goal specifications for product

development.

Preliminary specification:

This data sheet contains preliminary data; supplementary data

may be published later.

Product specification:

This data sheet contains final product specifications.

## Limiting values

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of this specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

## ©Philips Export B.V. 1991

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not imply any license under patent- or other industrial or intellectual property rights.

Printed in Switzerland