# Am53C974A PCscsı™II

# **Technical Manual**

**Revision 1.0**

ADVANCED MICRO DEVICES 🗖

#### © 1994 Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

This publication neither states nor implies any warranty of any kind, including but not limited to implied warrants of merchantability or fitness for a particular application. AMD<sup>®</sup> assumes no responsibility for the use of any circuitry other than the circuitry in an AMD product.

The information in this publication is believed to be accurate in all respects at the time of publication, but is subject to change without notice. AMD assumes no responsibility for any errors or omissions, and disclaims responsibility for any consequences resulting from the use of the information included herein. Additionally, AMD assumes no responsibility for the functioning of undescribed features or parameters.

#### Trademarks

AMD is a registered trademark of Advanced Micro Devices, Inc.

PCscsi and GLITCH EATER are trademarks of Advanced Micro Devices, Inc.

Microsoft is a registered trademark of Microsoft Corporation.

Windows NT Miniport is a trademark of Microsoft Corporation.

Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

# TABLE OF CONTENTS

# Л

| Chapter 1 General Information                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                                                                                     | 1-1                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Chapter 1       General information         1.1       Introduction         1.2       Hardware         1.2.1       Fast SCSI Block         1.2.1.1       Features         1.2.1.1       Access FIFO Command         1.2.1.1.2       Reduced Power Mode         1.2.1.1.3       Programmable GLITCH EATER Circuitry         1.2.1.1.4       Programmable Active Negation         1.2.2       DMA Engine | · · · · · 1<br>· · · · · 1<br>· · · · 1<br>· · · ·                                                                                    | I-1<br>I-2<br>I-3<br>I-3<br>I-3<br>I-3<br>I-3<br>I-4<br>I-5                                                  |

| 1.3 Software                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                     | 1-5                                                                                                          |

| 1.3.1 AMD's PCscsi Software Solution                                                                                                                                                                                                                                                                                                                                                                  | 1                                                                                                                                     | 1-5                                                                                                          |

| Chapter 2 Signal Descriptions                                                                                                                                                                                                                                                                                                                                                                         | 2                                                                                                                                     | 2-1                                                                                                          |

| 2.1Logic Symbol2.2Quick Reference Pin Descriptions2.3Signal Descriptions2.3.1Address and Data Pins2.3.2PCI Interface Control Pins2.3.3Arbitration Pins2.3.4System Pins2.3.5Error Reporting Pins2.3.6Interrupt Request Pins2.3.7SCSI Interface Signals2.3.8Power Management Signals2.3.9Boot ROM Support Pins2.3.10Miscellaneous Signals2.3.11Power Supply Pins                                        | 2          2          2          2          2          2          2          2          2          2          2          2          2 | 2-1<br>2-2<br>2-3<br>2-3<br>2-5<br>2-5<br>2-5<br>2-5<br>2-5<br>2-5<br>2-6<br>2-7<br>2-8<br>2-8<br>2-8<br>2-9 |

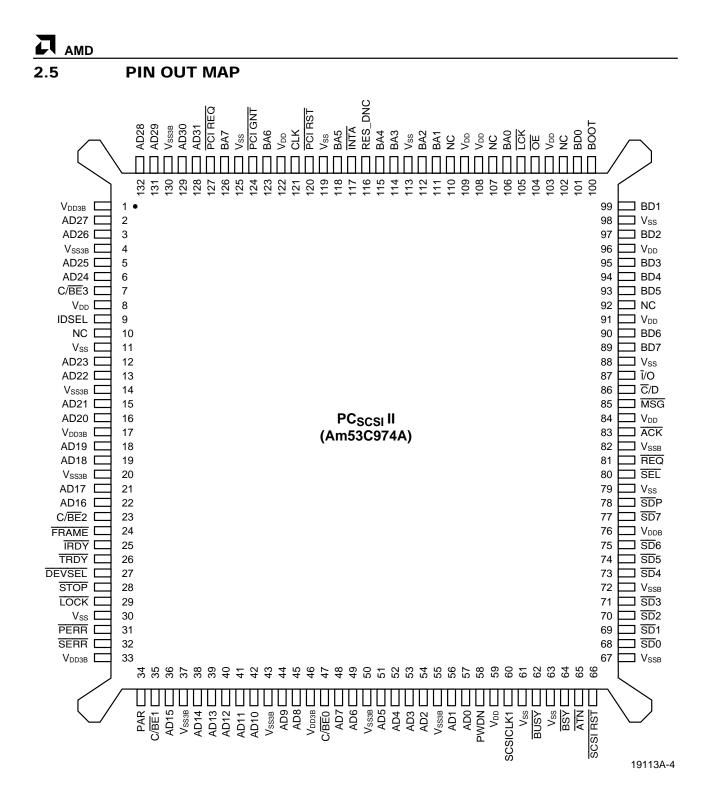

| <ul> <li>2.4 Connection Diagram Tables</li> <li>2.4.1 Listed by Pin Number</li> <li>2.4.2 Listed by Pin Name</li> <li>2.5 Pin Out Map</li> <li>2.6 NAND Tree Testing</li> <li>2.7 Am53C974A Register Map</li> </ul>                                                                                                                                                                                   | 2-<br>2-<br>2-<br>2-<br>2-                                                                                                            | 10<br>11<br>12<br>13                                                                                         |

| Chapter 3 Power Management Features                                                                                                                                                                                                                                                                                                                                                                   | 3                                                                                                                                     | 3-1                                                                                                          |

| 3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                       | 3-1                                                                                                          |

| 3.2 SCSI Activity Indicators                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                       | 3-1                                                                                                          |

| 3.2.1       Reduced Power Mode         3.3       Power Down Pin (PWDN Pin)                                                                                                                                                                                                                                                                                                                            |                                                                                                                                       | 3-1<br>3-1                                                                                                   |

| 3.3.1 Software Disk Spin-Down                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                       | 3-1                                                                                                          |

| Chapter 4 | The F | PCI Bus I | nterface          | Jnit                                            | 4-1  |  |  |

|-----------|-------|-----------|-------------------|-------------------------------------------------|------|--|--|

|           | 4.1   | Introduc  | tion              |                                                 | 4-1  |  |  |

|           | 4.2   | Address   | sing              |                                                 | 4-1  |  |  |

|           | 4.3   | Bus Acc   | quisition .       |                                                 | 4-1  |  |  |

|           | 4.4   | Bus Cyc   | cle Definiti      | on                                              | 4-2  |  |  |

|           | 4.5   | Bus Cyc   | cle Diagrar       | ns                                              | 4-3  |  |  |

|           |       | 4.5.1     | Slave I/C         | Read                                            | 4-3  |  |  |

|           |       | 4.5.2     |                   | Write                                           | 4-4  |  |  |

|           |       | 4.5.3     |                   | lemory Read                                     | 4-5  |  |  |

|           |       | 4.5.4     |                   | mory Read                                       | 4-6  |  |  |

|           |       | 4.5.5     |                   | lemory Write                                    | 4-7  |  |  |

|           |       | 4.5.6     | Slave Co          | nfiguration Read                                | 4-8  |  |  |

|           |       | 4.5.7     |                   | nfiguration Write                               | 4-9  |  |  |

|           |       | 4.5.8     |                   | lemory Read Line                                | 4-10 |  |  |

|           | 4.6   | Transac   | tion Termi        | nation                                          | 4-11 |  |  |

|           |       | 4.6.1     | Target In         | itiated Termination                             | 4-11 |  |  |

|           |       |           | 4.6.1.1           | Disconnect With Data Transfer                   | 4-11 |  |  |

|           |       |           | 4.6.1.2           | Disconnect Without Data Transfer                | 4-12 |  |  |

|           |       |           | 4.6.1.3           | Target Abort                                    | 4-13 |  |  |

|           |       | 4.6.2     | Master Ir         | itiated Termination                             |      |  |  |

|           |       |           | 4.6.2.1           | Preemption                                      | 4-14 |  |  |

|           |       |           | 4.6.2.2           | Master Abort                                    | 4-15 |  |  |

|           | 4.7   | Configu   | uration Registers |                                                 |      |  |  |

|           |       | 4.7.1     | Predefine         | ed Header Register Description                  | 4-17 |  |  |

|           |       |           | 4.7.1.1           | Vendor ID Register                              | 4-17 |  |  |

|           |       |           | 4.7.1.2           | Device ID Register                              | 4-17 |  |  |

|           |       |           | 4.7.1.3           | Command Register                                |      |  |  |

|           |       |           | 4.7.1.4           | Status Register                                 | 4-19 |  |  |

|           |       |           | 4.7.1.5           | Revision ID Register                            | 4-20 |  |  |

|           |       |           | 4.7.1.6           | Programming Interface Register                  | 4-20 |  |  |

|           |       |           | 4.7.1.7           | Sub-Class Register                              | 4-20 |  |  |

|           |       |           | 4.7.1.8           | Base Class Register                             | 4-20 |  |  |

|           |       |           | 4.7.1.9           | Latency Timer Register                          | 4-20 |  |  |

|           |       |           | 4.7.1.10          | Header Type Register                            |      |  |  |

|           |       |           | 4.7.1.11          | Base Address Register                           | 4-21 |  |  |

|           |       |           | 4.7.1.12          | Expansion ROM Base Address Register             | 4-22 |  |  |

|           |       |           | 4.7.1.13          | Interrupt Line Register                         | 4-23 |  |  |

|           |       |           | 4.7.1.14          | Interrupt Pin Register                          | 4-23 |  |  |

|           |       |           | 4.7.1.15          | Min_Gnt Register                                | 4-23 |  |  |

|           |       |           |                   | Max_Lat Register                                |      |  |  |

|           |       | 4.7.2     |                   | ependent Register Description                   |      |  |  |

|           |       | 4.7.3     |                   | cratch Register Usage                           |      |  |  |

|           |       |           | 4.7.3.1           | Target Device Configuration Register Definition | 4-24 |  |  |

|           |       |           | 4.7.3.2           | Host Configuration Register Definition          | 4-26 |  |  |

#

| Chapter 5 | The F | AST SC   | SI Block           |                                                 | 5-1        |

|-----------|-------|----------|--------------------|-------------------------------------------------|------------|

|           | 5.1   | Functior | nal Overvie        | ew                                              | 5-1        |

|           |       | 5.1.1    | Part-Unic          | que ID                                          | 5-1        |

|           |       | 5.1.2    | SCSI FIF           | O Threshold                                     | 5-1        |

|           |       | 5.1.3    |                    | nsmission                                       | 5-1        |

|           |       | 5.1.4    |                    | K Control                                       | 5-2        |

|           |       | 5.1.5    | •                  |                                                 | 5-3        |

|           |       |          | 5.1.5.1            | Parity from the SCSI Bus                        | 5-3        |

|           |       | 5.1.6    |                    | vels                                            | 5-4        |

|           |       |          | 5.1.6.1            | Hard Resets: (H)                                | 5-4        |

|           |       |          | 5.1.6.2            | Soft Reset: (S)                                 | 5-4        |

|           | 5.0   | Deviates | 5.1.6.3            | Disconnected Reset: (D)                         | 5-5        |

|           | 5.2   | •        | r Descripti        |                                                 | 5-6        |

|           |       | 5.2.1    | -                  | Bit Map: Read                                   | 5-7        |

|           |       | 5.2.2    | -                  | Bit Map: Write                                  | 5-8        |

|           |       | 5.2.3    | 5.2.3.1            | Descriptions<br>Current Transfer Count Register | 5-9<br>5-9 |

|           |       |          | 5.2.3.1            | Start Transfer Count Register                   |            |

|           |       |          | 5.2.3.2            | SCSI FIFO Register                              |            |

|           |       |          | 5.2.3.4            | SCSI Command Register                           |            |

|           |       |          | 5.2.3.5            | SCSI Status Register                            |            |

|           |       |          | 5.2.3.6            | SCSI Destination ID Register                    |            |

|           |       |          | 5.2.3.7            | Interrupt Status Register                       |            |

|           |       |          | 5.2.3.8            | SCSI Timeout Register                           |            |

|           |       |          | 5.2.3.9            | Internal State Register                         |            |

|           |       |          |                    | Synchronous Transfer Period Register            |            |

|           |       |          |                    | Current FIFO/Internal State Register            |            |

|           |       |          |                    | Synchronous Offset Register                     |            |

|           |       |          | 5.2.3.13           | Control Register One                            | 5-24       |

|           |       |          | 5.2.3.14           | Clock Factor Register                           | 5-25       |

|           |       |          | 5.2.3.15           | Reserved                                        | 5-25       |

|           |       |          | 5.2.3.16           | Control Register Two                            | 5-26       |

|           |       |          |                    | Control Register Three                          |            |

|           |       |          |                    | Control Register Four                           |            |

|           |       |          |                    | Reserved                                        |            |

|           |       |          |                    | Part-Unique ID Register                         |            |

|           | 5.3   |          |                    | s                                               |            |

|           |       | 5.3.1    |                    | d Stacking                                      |            |

|           |       | 5.3.2    |                    | ommands                                         |            |

|           |       | 5.3.3    |                    | d Window                                        |            |

|           |       | 5.3.4    |                    | Commands                                        |            |

|           |       |          | 5.3.4.1            | Information Transfer Command                    |            |

|           |       |          | 5.3.4.2            | Initiator Command Complete Steps                |            |

|           |       |          | 5.3.4.3            | Message Accepted Command                        |            |

|           |       |          | 5.3.4.4<br>5.3.4.5 | Transfer Pad Bytes Command                      |            |

|           |       |          | 5.3.4.5            | Reset ATN Command                               | 5-35       |

|           |       | 5.3.5    |                    | ommands                                         |            |

|           |       | 5.5.5    | 5.3.5.1            | Send Message Command                            |            |

|           |       |          | 5.3.5.1            | Send Status Command                             |            |

|           |       |          | 5.3.5.3            | Send Data Command                               |            |

|           |       |          | 5.3.5.4            | Disconnect Steps Command                        |            |

|           |       |          | 5.3.5.5            | Terminate Steps Command                         |            |

|           |       |          | 5.3.5.6            | Target Command Complete Steps Command           |            |

|           |       |          | 5.3.5.7            | Disconnect Command                              | 5-37       |

|           |       |          | 5.3.5.8            | Receive Message Steps Command                   |            |

|           |       |          | 5.3.5.9            | Receive Commands Command                        |            |

|           |      |          | 5.3.5.10     | Receive Data Command                           | 5-37 |

|-----------|------|----------|--------------|------------------------------------------------|------|

|           |      |          | 5.3.5.11     | Receive Command Steps Command                  | 5-38 |

|           |      |          | 5.3.5.12     | DMA Stop Command                               | 5-38 |

|           |      |          | 5.3.5.13     | Access FIFO Command                            | 5-39 |

|           |      | 5.3.6    | Idle State   | e Commands                                     | 5-39 |

|           |      |          | 5.3.6.1      | Reselect Steps Command                         | 5-39 |

|           |      |          | 5.3.6.2      | Select without ATN Steps Command               | 5-40 |

|           |      |          | 5.3.6.3      | Select with ATN Steps Command                  | 5-40 |

|           |      |          | 5.3.6.4      | Select with ATN and Stop Steps Command         |      |

|           |      |          | 5.3.6.5      | Enable Selection/Reselection Command           |      |

|           |      |          | 5.3.6.6      | Disable Selection/Reselection Command          | 5-40 |

|           |      |          | 5.3.6.7      | Select with ATN3 Steps Command                 |      |

|           |      |          | 5.3.6.8      | Reselect with ATN3 Steps Command               | 5-41 |

|           |      | 5.3.7    | General (    | Commands                                       |      |

|           |      |          | 5.3.7.1      | No Operation Command                           | 5-42 |

|           |      |          | 5.3.7.2      | Clear FIFO Command                             |      |

|           |      |          | 5.3.7.3      | Reset Device Command                           |      |

|           |      |          | 5.3.7.4      | Reset SCSI Bus Command                         | 5-42 |

| Chapter 6 | DMA  | Engine   |              |                                                | 6-1  |

| enapter e | 6.1  | •        |              |                                                |      |

|           | 6.2  |          |              |                                                |      |

|           | 6.3  |          |              |                                                |      |

|           | 0.0  | 6.3.1    |              | st Command                                     |      |

|           | 6.4  | Funnel   |              |                                                |      |

|           | 6.5  |          |              | amming Sequence                                |      |

|           | 6.6  |          | -            | Programming                                    |      |

|           | 6.7  |          |              |                                                |      |

|           |      | 6.7.1    |              | ld Register                                    |      |

|           |      | 6.7.2    |              | Transfer Count                                 |      |

|           |      | 6.7.3    | Starting F   | Physical Address                               | 6-6  |

|           |      | 6.7.4    |              | Byte Counter                                   |      |

|           |      | 6.7.5    | Working      | Address Counter                                | 6-7  |

|           |      | 6.7.6    | Status Re    | egister                                        | 6-8  |

|           |      | 6.7.7    | Starting I   | Memory Descriptor List Address (SMDLA)         | 6-10 |

|           |      | 6.7.8    | Working      | MDL Address Counter (WMAC)                     | 6-10 |

|           |      | 6.7.9    |              | s and Control (SBAC)                           |      |

|           | 6.8  | DMA S    | Scatter-Gath | ner Mechanism                                  | 6-13 |

|           |      | 6.8.1    | ,            | Descriptor List (MDL)                          | -    |

|           |      | 6.8.2    |              | atter – Gather Operation (4k aligned elements) | 6-14 |

|           |      | 6.8.3    |              | atter – Gather Operation                       | 0 47 |

|           | 6.9  | Intorru  | •            | aligned elements MDL not set)                  |      |

|           | 0.9  | menu     | μις          |                                                | 0-17 |

| Chapter 7 | Ехра | ansion R | OM Suppo     | ort                                            | 7-1  |

|           | 7.1  |          |              |                                                |      |

|           | 7.2  |          |              | ss Register                                    |      |

|           | 7.3  |          |              | itation                                        |      |

|           | 7.4  |          |              | le                                             |      |

|           | 7.5  | Expans   | sion ROM N   | Mapping                                        | 7-4  |

#

| Chapter 8  | SCAI         | M Tutorial                                           | 8-1          |

|------------|--------------|------------------------------------------------------|--------------|

|            | 8.1          | Introduction                                         | 8-1          |

|            | 8.2          | Requirements                                         | 8-1          |

|            | 8.3          | SCAM Terminology                                     | 8-1          |

|            | 8.4          | Normal SCSI and SCAM Selections                      | 8-2          |

|            |              | 8.4.1 Normal SCSI Selection                          | 8-2          |

|            |              | 8.4.2 Level 1 SCAM Selection                         | 8-2          |

|            | 8.5          | SCAM Protocol                                        | 8-4          |

|            |              | 8.5.1 SCAM Master Device Operation                   | 8-5          |

|            |              | 8.5.2 SCAM Slave Device Operation                    | 8-6          |

|            | 8.6          | SCAM Examples                                        | 8-7          |

|            | 8.7          | ID Assignment                                        | 8-8<br>8-8   |

|            |              | 8.7.2 Function Codes                                 |              |

|            |              | 8.7.3 Identification String                          |              |

|            |              | 8.7.4 Assigning IDs                                  |              |

|            |              | 8.7.5 Default ID and ID Assignment                   |              |

|            | _            | •                                                    |              |

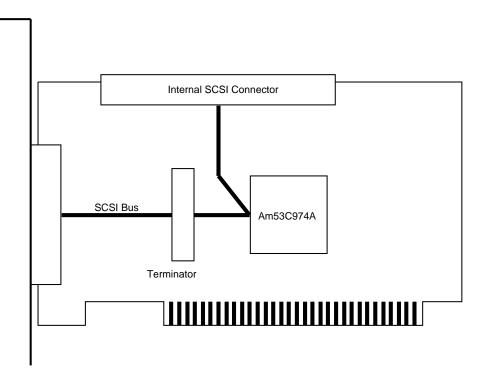

| Chapter 9  | Desig        | gn Considerations for Motherboards and Adapter Cards | 9-1          |

|            | 9.1          |                                                      | 9-1          |

|            | 9.2          | Signal Routing and SCSI Placement                    | 9-1          |

|            |              | 9.2.1 The Motherboard                                | 9-3          |

|            |              | 9.2.1.1 Layout #1                                    | 9-3          |

|            |              | 9.2.1.2 Layout #2                                    | 9-4          |

|            | 9.3          | 9.2.2 The Adapter Card                               | 9-5<br>9-6   |

|            | 9.5          | 9.3.1 Electromagnetic Interference (EMI)             | 9-6<br>9-6   |

|            |              | 9.3.2 Decoupling Methods                             | 9-0<br>9-6   |

|            | 9.4          | Termination Considerations                           | 9-8          |

|            | 0.1          | 9.4.1 Termination                                    | 9-8          |

|            |              | 9.4.1.1 Scheme #1                                    | 9-8          |

|            |              | 9.4.1.2 Scheme #2                                    | 9-8          |

|            |              | 9.4.1.3 Scheme #3                                    | 9-9          |

|            | 9.5          | Other Considerations                                 | 9-9          |

| Chapter 10 |              | 's PCscsi Software                                   | 10-1         |

| Chapter 10 |              | Introduction                                         | -            |

|            | 10.1<br>10.2 | PCscsi Software Architecture                         | 10-1<br>10-1 |

|            | 10.2         |                                                      | 10-1         |

|            | 10.5         | 10.3.1 DOS                                           |              |

|            |              | 10.3.2 Netware                                       | 10-3         |

|            |              | 10.3.3 OS/2                                          |              |

|            |              | 10.3.4 Windows                                       |              |

|            |              | 10.3.5 Windows NT                                    | 10-4         |

|            |              | 10.3.6 SCO UNIX                                      | 10-4         |

|            |              | 10.3.7 SCSI ROM BIOS                                 | 10-4         |

|            | 10.4         | Peripheral Support                                   | 10-5         |

| Appendix A | Am5          | 3C974A Literature/Tool Support                       | A-1          |

# SCSI TECHNOLOGY OVERVIEW

### INTRODUCTION

This chapter is included in the technical specification for the PCI family of AMD SCSI solutions because of the nature of these devices. Each SCSI chip is effectively a complete solution for integrating SCSI on a PCI adapter card or onto the motherboard of a PCI based system. All of the logic required for a SCSI port is included in the PCI SCSI device. Because AMD also furnishes the software solution for PC operating systems, users are (for the first time) looking at SCSI as a standard I/O solution, but may have little experience in the basics of the standard. This introduction will provide a basic understanding of the relevant information so that users can quickly integrate and use the SCSI interface.

Before the SCSI standard was defined, in the 1979 time frame, the typical introduction of new peripheral technology required 18 to 24 months. The tasks consisted of:

- 1. Designing a disk controller board

- 2. Designing a host adapter board

- 3. Changing system software to accommodate new device characteristics

- 4. Testing the new configuration

Disk drive manufacturers were faced with a delay that severely impacted business. If disk development required 18 months, and integration took another 18 months, the total time to revenue was three years. Clearly, this technology bottleneck caused problems for the disk industry. Consequently, vendors began to define logical interfaces that could survive beyond each model, and allow integrators to preserve the majority of their development investment. SCSI was one of these definitions that survived. Originally defined by Shugart Associates, SASI (Shugart Associates Systems Interface) was offered as a public document by Shugart in hopes that other system vendors would use it and establish it as a defacto standard. Within a short time, an ANSI standards group was formed, the name was changed to Small Computer Systems Interface, and the standardization efforts began.

With support from peripheral vendors, the document defined a logical interface to a wide variety of peripherals. This interface would allow system vendors to attach peripherals easily and quickly to new systems, in order to meet a fast moving market window. The standard defined a physical level (mechanical and electrical) as well as a logical level (commands and messages). The actual command passing protocol and the set of peripheral command sets were defined by the standard. Using logical addressing mechanisms, rather than physical addressing (sector 347 vs. cylinder 13, head 2, sector 3), the standard allowed the physical details of the peripheral to be hidden from the system software. Therefore, after the standard was defined, a typical integration cycle was reduced to three months, and consisted of:

- 1. Replacing the current SCSI disk with a new model

- 2. Testing the new configuration for compliance

The process was complicated because new peripherals offered features that were enabled through the system software, and because vendors did not offer devices that were compatible with other vendors. But in general, the process was much simpler and faster than before.

Since 1979, the SCSI standard passed through several key stages as it matured into today's standard. These stages are:

SASI (1979 – 1982) — This was a DTC/Shugart collaboration that was a controller board shipped with Shugart drives. Although limited in function, it highlighted the advantages of a high level logical interface for disk drives.

SCSI-1 (1982 – 1986) — A group of companies (Shugart, Adaptec, NCR, & OMTI) banded together and approached ANSI for permission to develop a SCSI standard. The effort generated industry wide interest and was quickly written because of the participants' common interest (i.e. everyone desired quick time to market for their products). The ANSI specification (X3.131–1986) won final approval in May of 1986.

CCS (1985 – 1986) — Upon finalization of the SCSI-1 specification, the participants barely had time to congratulate each other before the weakness of the document began to emerge. The number of options allowed vendors were to develop disks that worked fine, but which were not compatible with each other. Thus system vendors could not easily integrate disk drives from all vendors into their system. So, disk vendors met to define an extended subset of SCSI that would (if followed closely) permit vendors to produce compatible disk products. This document (Common Command Set) became a defacto standard and allowed further standardization of the SCSI market.

SCSI-2 (1986 – 199X) — As soon as the CCS specification was written, the complete SCSI community realized the benefit of these extensions and restarted the SCSI effort to bring the benefits of CCS into the complete SCSI standard document. The original goal was to quickly fold CCS into the disk section and expand other command sets to include CCS features. Unfortunately, the door of improvement, once open, allowed a flood of improvements to come in. Updates were cut off by 1990 and the specification has been finalized as of August 1990.

SCSI-3 (1990 – 199X) — The stated goal of the first two SCSI specifications was downward compatibility, but with SCSI-3, backward compatibility was sacrificed. The goal was to define a protocol that accommodated the new serial interfaces and solved some of the problems of the parallel interface. The result is a family of documents being written for SCSI-3.

## Basic SCSI

The standard SCSI parallel bus allows connection for 8 or 16 devices (computers or peripherals). Each has a unique identifier that allows selection and communication between any two devices on the SCSI bus. An Initiator is an entity on the bus that issues a command to a Target. Note that any device on the bus, peripheral or computer system, can initiate a command sequence. The Initiator arbitrates for and wins the SCSI bus, selects the desired Target, and sends a command to that Target. At this point, the Target controls the bus and directs the remainder of the command sequence. The Initiator can always regain control by use of the attention line that signals the Target that something is coming. But in general, the Target remains in control.

There are nine control signals on the SCSI bus that allow the complete handshake to happen. Target or Initiator controls the Bus depending on the phase of the command sequence. There are 8, 16, or 32 data lines with each 8 bit set having a parity line. The data width can be negotiated for, with 8 being the default, and 16 or 32 being

options. Sixteen-bit SCSI devices are available but are not in widespread use, while 32-bit devices are not yet available. There is considerable inertia resisting going beyond 8-bit cables because of the physical sizes involved. There is a Fast SCSI option that allows SCSI to transfer data at 10 mega transfers per second, thus allowing 10 MB/sec on 8-bit cables. This configuration is the clear winner in today's market, because it allows faster transfers with no change in the physical environment. Single ended SCSI is by far the most popular implementation and the specification allows 6 meter cables in this environment. Fast SCSI is not defined for single-ended cables, however, vendors are providing silicon that will allow data to be transferred at the higher speeds.

The SCSI protocol defines the phases required to complete a SCSI I/O. The Message phase allows short transfers of protocol related information to be sent across the bus to establish and control the logical connection between an Initiator and a Target. The Command phase allows the Initiator to tell the Target what action must be performed. Read, write, rewind, etc. are all SCSI commands. User data is transferred during the Data phase, allowing the data to be sent into or out from the Initiator. This data can be written to the media, or it can be control information that is used to communicate operating modes or sensed information to(from) the peripheral. Status information (one byte only) is sent to the Initiator from the Target at the end of the complete SCSI command sequence. If an error occurred, the Initiator must request the details of the problem with a subsequent SCSI command.

The basic SCSI command sequence follows:

- Bus is free and any device is allowed to arbitrate for ownership

- An Initiator arbitrates for the bus and selects a Target device

- The Target, after sensing selection, goes to Message Out phase and receives a one byte ID message from the Initiator that establishes which physical device the Initiator wants to communicate with

- After switching to Command phase, the Target receives the SCSI command.

- Changing to the appropriate Data phase (in/out) the Target handshakes the data across the bus

- A single status byte is sent to the Initiator

- A command complete message is sent to the Initiator to signal completion of the SCSI I/O

- The Target then physically disconnects from the SCSI bus, and it is free for the next device to use

Any time after the ID message is sent, the Target controls the sequence and directs the Initiator's next step. The Target is allowed to disconnect, temporarily get off the bus and reselect later. In this manner, data can be multiplexed from various peripherals to the host computer, in support of overlapped physical actions at the peripheral and multi-threaded I/O in the operating system.

SCSI-1 provided the basic protocol functionality that supported the original goals of device connectability, allowing 8 bit buses and a limited protocol flexibility. As noted above, the plug and play aspects of the specification were not quickly realized because of the large set of options. The CCS specification defined the extended subset of the SCSI-1 document that allowed multiple disk vendors to work in one system environment without compatibility issues in the host software. The main SCSI-2 features were:

Compatibility — There must be an evolutionary growth, and mixed environments were permitted. Requirements in SCSI-2 were popular options in SCSI-1.

- High Performance The original 5 MB/sec limit was pushed to 40 MB/sec using a combination of 32-bit buses and 10 Mega transfers per second. The maximum cable limits were still set at 6 (single ended) and 25 (differential) meters. Eight devices were allowed on the bus, but a working paper described how sixteen devices could be attached.

- Hardware Requirements Parity on the bus is required for data integrity, and disconnect/reconnect is required for multiplexing the SCSI bus. SCSI-1 had no requirement for messages (all were optional) because of compatibility with SASI, but SCSI-2 required certain messages to make SCSI more usable in a complex systems environment.

- Logical interface improvements A group of features were defined to generally improve SCSI. Features included were queueing of 256 commands at the peripheral, more detailed definition for all control data used to change device characteristics (or report information about the device), cache support for direct access devices, and tape partition support.

- New Command Sets New device command sets were for scanners, optical memory devices, medium changers, and communication devices.

These changes dramatically increased the size of the SCSI-2 specification, and moved the definition into a more high performance system environment.

SCSI-3 has given SCSI a totally new set of capabilities. The basic desire was to increase the functionality to cover all the physical interfaces and allow the architecture to be extended to the future requirements with few restrictions for compatibility. The standard was divided into multiple documents to ease the pain of an editor. There are four transport layers:

- Standard parallel interface for 8- and 16-bit cables

- Fiber channel for 100 MB/sec, full duplex transfers

- Serial Storage Architecture in support of high performance (20 MB/sec) disks

- P1394 allows 400 Mb/sec isochronous transfers

- Five protocols:

- Interlocked

- Fiber channel

- SSA

- Serial bus

- Generic packetized

Five command sets:

- Primary

- Block

- Stream

- Graphics

- Medium Changer

The target release date for these set of documents is 1994, but if the past is any indication, SCSI-3 will require many years of work before being ready for official release. The delay will not stop products from emerging however, because products with the new interfaces and features are already appearing in the marketplace.

Before SCSI could penetrate the PC market, a critical piece of technology was required: I/O software drivers to support the SCSI capabilities in the PC operating system environments. As the first vendors introduced host adapter boards that connected SCSI devices to the PC, the user quickly learned the importance of software. Consider the following scenario:

- User buys a SCSI disk with host adapter

- A tape drive is required to back up the disk

- User buys a tape drive

- The tape can be connected, but there is no software to drive the device

- User buys a host adapter to drive the tape

- The tape works now, but there is no software to move data to/from the disk

Point solutions became available, but general solutions were not available until 1991. Although the hardware was available and certain systems vendors were able to make SCSI work, there was no guarantee that a user could find an off-the-shelf solution for the DOS/Windows environment. Host adapter companies quickly began to offer limited software capabilities that allowed several devices to be used in the PC.

Several defacto interfaces were available and in the interest of standardization, a Common Access Method (CAM) committee was formed to standardize access to the SCSI interface for each PC operating system environment. Unfortunately, once software was running, users were reluctant to change. Therefore, the CAM specification, although technically sound, has never been widely accepted as a standard. The Advanced SCSI Programming Interface (ASPI) instead became a defacto standard interface for I/O application software such as CD-ROM and tape backup utilities. Consequently, ASPI seems to be entrenched as the interface of choice for DOS/ Windows.

However, more sophisticated operating systems already have a logical I/O interface defined and do not share the same limitations as DOS. As the new operating systems become more widely used in PCs and DOS I/O gradually becomes buried in an emulation mode, the critical driver issues for the PC will disappear. Until then (as Yogi Berra says, "Tomorrow isn't here yet"), highly integrated SCSI chips must be supplied with SCSI I/O drivers for the operating systems that execute on a PC. The drivers must be architected carefully so as to require minimal change when the SCSI device changes. Known as a two layer software interface, a good architecture will isolate changes in the operating system from changes in the SCSI interface. Software technology like this allows SCSI to be commonly available in the PC environment.

Another key element in the I/O performance saga is the availability of bus mastering in the PC environment. Rather inexpensive 32 bit bus mastering SCSI chips with FIFO's in the chip have taken high performance I/O to new levels. The combination of bus mastering on the chip, extremely high performance system processors and increasing levels of silicon integration have combined recently to result in high performance low cost solutions in a single chip.

Performance that was once only available as a host adapter board (with a separate processor, SCSI chip, RAM, and system interface) is now achieved using a single chip. System processors offer a level of MIPS on the motherboard that can easily support I/O silicon on the motherboard, thus simplifying the SCSI port dramatically. This new level of cost effective silicon, combined with a complete software solution will no doubt enable SCSI in a new environment and drive the industry to another level of capability.

# GENERAL INFORMATION

# 1.1 INTRODUCTION

The Am53C974A from Advanced Micro Devices was developed in response to the PC industry's need for a hardware solution which harnessed the speed and flexibility of high bandwidth local and I/O buses. Combining the performance of the PCI local bus with the intelligence of the SCSI I/O bus, Advanced Micro Devices offers this Bus Mastering SCSI Controller for PCI systems. The Am53C974A is one member of a family of AMD's plug compatible PCI products which share a common software solution. These products are compliant with PCI specification rev 2.0; the Am53C974A also complies with ANSI standards X3.131–1986 (SCSI-1) and X3.131–199X (SCSI-2).

The Am53C974A offers a glueless interface to the PCI Bus, making it an ideal choice for motherboard as well as adapter card designs. The on-chip state machine which controls SCSI sequences in hardware is coupled with a bus-mastering DMA engine to eliminate the need for an additional RISC processor. The result is a PCI-SCSI controller with a superior price/performance advantage. Furthermore, AMD's value-added proposition for the Am53C974A offering is a complete, licensable solution to minimize your time to market.

#### **Distinctive Features:**

PCI Bus Interface Unit

- PCI specification rev 2.0 compliant interface

- 32-bit address/data bus master DMA Host interface

- Glueless interface to 33 MHz 32-bit PCI Bus

- 96-byte DMA FIFO for low bus latency

SCSI Controller Features

- Single chip PCI to SCSI interface

- Boot ROM support

- Level 1 SCAM support

- SCSI-2 compliant, 8-bit Fast SCSI interface

- Supports single-ended SCSI bus

- 48 mA SCSI drivers

Performance

- 10 MByte/s synchronous and 7 MByte/s asynchronous transfer rates on the SCSI bus

- 132 MByte/s burst DMA transfer rate

- Supports Scatter-Gather data transfers

**Power Management**

Sleep mode capability for Fast SCSI block — Power down for SCSI receivers

- SCSI activity monitoring pin and status bit

- Fully static design for low frequency operation

- SCSI clock disconnect capability

SCSI Bus Reliability

- AMD's patented Programmable GLITCH EATER<sup>™</sup> Circuitry on REQ and ACK inputs

- Programmable Active Negation on REQ, ACK and data lines

**Other Features**

- 132-pin PQFP

- Uses state of the art advanced CMOS technology

The Am53C974A hardware solution is complemented by an extensive software package for all major operating systems. The software solution incorporates AMD's portable SCSI software which is based in part on the Microsoft<sup>®</sup> Windows NT Miniport<sup>™</sup> model.

#### 1.2 HARDWARE

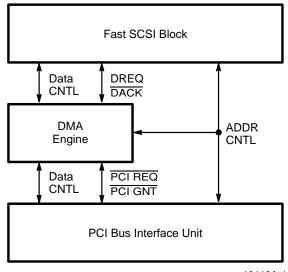

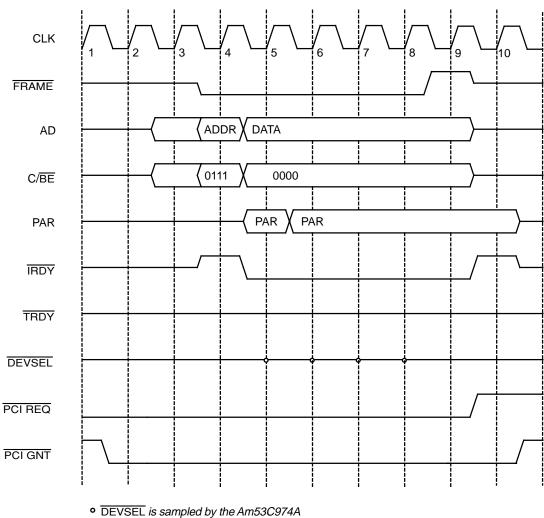

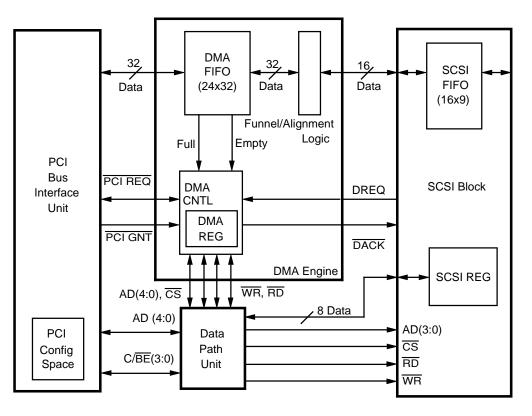

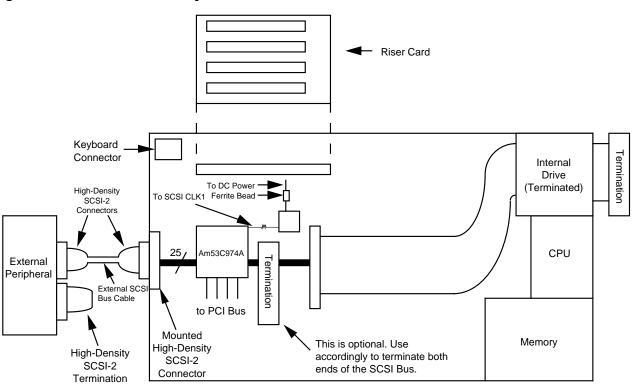

The Am53C974A is a high performance PCI local bus-SCSI controller. It is comprised of the PCI Bus Interface Unit (BIU), a Fast SCSI block, and a bus master DMA engine. The PCI BIU consists of configuration space and a PCI master/slave interface as defined in rev 2.0 of the PCI specification. Figure 1-1 shows the basic interface block diagram of the Am53C974A.

#### Figure 1-1 PCI-DMA-SCSI Interface Block Diagram

19113A-1

# 1.2.1 Fast SCSI Block

The Am53C974A's Fast SCSI block supports SCSI transfer rates of up to 10 MBytes/s synchronously, and up to 7 MByte/s asynchronously. The Am53C974A combines this functionality with features such as programmable Active Negation, and a 24-bit transfer counter. AMD's proprietary features such as power-down mode for SCSI receivers and programmable GLITCH EATER Circuitry are also included for improved product performance.

The Am53C974A has an 8-bit SCSI data interface and can operate as either an Initiator or a Target to support all SCSI applications. The SCSI block is designed to minimize host intervention by implementing common SCSI sequences in hardware. Selection, Reselection, Information Transfer and Disconnection commands are directly supported. For example, functions such as Target Selection/Initiator Reselection, Command, Message, and data transfers between the SCSI bus and the SCSI FIFO are internal processes that the Am53C974A handles without microprocessor intervention. An on-chip state machine reduces protocol overhead by performing the required sequences in response to a single command from the host.

Additionally, a 16-byte SCSI FIFO further assists in minimizing host involvement. The FIFO provides a temporary storage for all command, data, status and message bytes as they are transferred between the 32-bit host data bus and the 8-bit SCSI data bus. Parity checking on data received from the SCSI bus is optional. Parity is generated in the SCSI block as data is loaded into the SCSI FIFO. Data transfers between the SCSI bus and the SCSI FIFO are internal processes that the Am53C974A also handles without microprocessor intervention.

#### 1.2.1.1 Features

Key features in the Am53C974A Fast SCSI block are highlighted below:

#### 1.2.1.1.1 Access FIFO Command

The Target command set for the Am53C974A includes the Access FIFO command. This command allows the host or DMA controller to remove remaining FIFO data following the host's issuance of a Target abort DMA command, or following an abort due to parity error. This command facilitates data recovery and thereby minimizes the need to re-transmit data. For more details, refer to the Target Command Set.

#### 1.2.1.1.2 Reduced Power Mode

AMD's exclusive power-down feature can be enabled to help reduce power consumption. The receivers on the SCSI bus may be turned off to eliminate current flow due to termination power (~3 V) near the trip point of the input buffers. Additionally, the clock to the SCSI core can be disconnected for further power reduction.

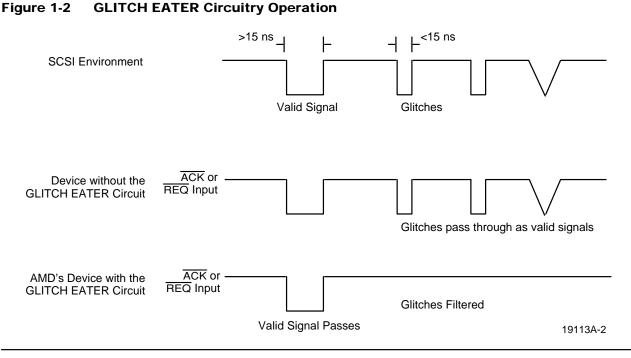

## 1.2.1.1.3 Programmable GLITCH EATER Circuitry

The patented GLITCH EATER Circuitry in the Am53C974A PCscsII Controller can be programmed to filter glitches with widths up to 35 ns. It is designed to dramatically increase system reliability by detecting and removing glitches that may cause system failure. The GLITCH EATER Circuitry is implemented on the REQ and ACK inputs since these lines are most susceptible to electrical anomalies such as reflections and voltage spikes. Such signal inconsistencies can trigger false REQ/ACK handshaking, false data transfers, addition of random data, and double clocking. AMD's GLITCH EATER Circuitry therefore maintains system performance and improves reliability. The following diagram illustrates this circuit's operation.

By default, this feature is enabled and will filter glitches with widths up to 12 ns. When this feature is implemented, the setup and hold times for the following parameters are modified. However, they are still compliant with the SCSI-2 specification and have no effect on the Am53C974A's ability to meet Fast SCSI timings.

**^** ... -

10 .....

|                                                                        | 0 ns<br>Window | 12 ns<br>Window |

|------------------------------------------------------------------------|----------------|-----------------|

| Data to REQ or ACK Setup Time:                                         |                |                 |

| Fast SCSI ANSI Requirement:                                            | 25 ns          |                 |

| Normal SCSI ANSI Requirement:                                          | 55 ns          |                 |

| Data to REQ Setup Time                                                 |                |                 |

| (Async Initiator Receive Mode):                                        | 0 ns           | 12 ns           |

| Data to ACK Setup Time                                                 |                |                 |

| (Async Target Receive Mode):                                           | 0 ns           | 12 ns           |

| Data to REQ or ACK Setup Time<br>(Sync Initiator/Target Receive Mode): | 5 ns           | 12 ns           |

## 1.2.1.1.4 Programmable Active Negation

AMD offers programmable active negation, a feature which, when implemented, will actively drive the REQ, ACK and SCSI Data lines to a high state. This feature is especially helpful for reducing SCSI Bus noise and improving data reliability. By actively driving these signals to their high state, Active Negation eliminates unwanted signal transitions and associated data double-clocking.

This feature is controlled by bits 3:2 in the SCSI Control Register Four ((B)+34h), and may be implemented on  $\overline{REQ}$  and  $\overline{ACK}$ , or on  $\overline{REQ}$ ,  $\overline{ACK}$ , and data lines during all SCSI Bus phases except Arbitration and Selection. For more information on programming options, refer to Control Register Four ((B)+34h) bit level descriptions.

#### 1.2.2 DMA Engine

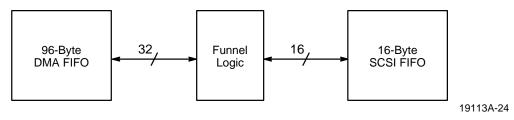

The Am53C974A bridges the PCI and SCSI buses by providing a buffer for these buses. A 96-byte DMA FIFO (24 Double Words) internally interfaces with the 16-byte SCSI FIFO to provide temporary storage for command, data, status, and message bytes as they are transferred between the two buses.

The DMA engine is also capable of handling block type transfers (4 KB pages) during scatter-gather operations. Odd/even boundary conditions are handled through hardware to minimize software overhead.

#### 1.3 SOFTWARE

To minimize your time to market, AMD offers a complete software solution for the Am53C974A. This combination represents a powerful PCI systems solution which enhances the flexibility of your system.

#### 1.3.1 AMD's PCscsi II Software Solution

AMD's PC<sub>SCSI</sub> II Software maximizes reusability and portability of SCSI protocol chip and device driver source code across multiple operating system platforms. The software architecture was based in part on the Microsoft Windows NT SCSI Miniport Driver model.

AMD's SCSI Software architecture supports the following features:

- Device level overlapped/multithreaded operation

- Tagged-queuing

- Automatic request sense

- Scatter-gather operations

- Synchronous Transfers (including Fast SCSI)

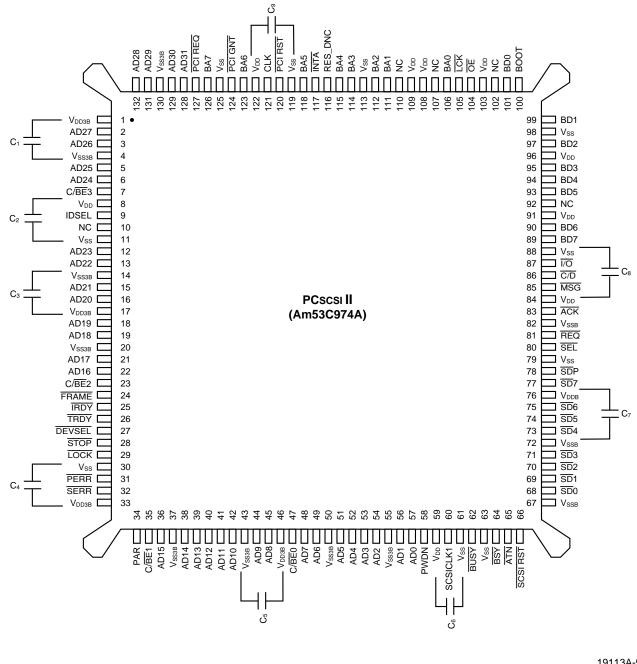

# 2 SIGNAL DESCRIPTIONS

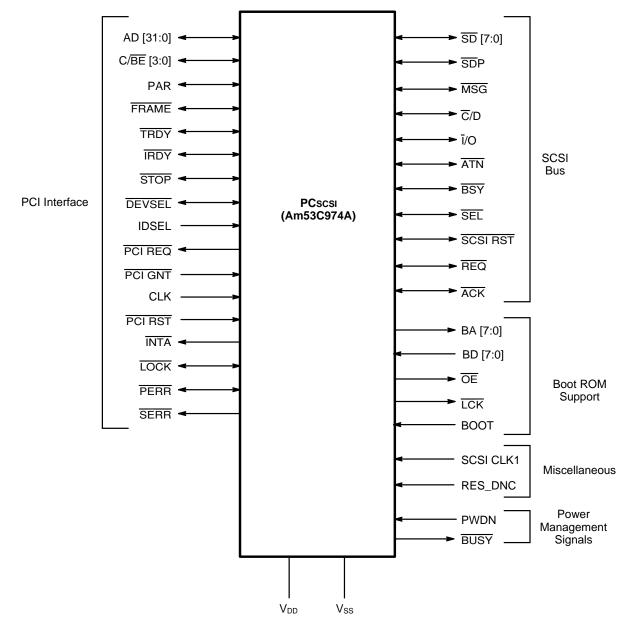

# 2.1 LOGIC SYMBOL

Figure 2-1 Am53C974A Logic Symbol

## QUICK REFERENCE PIN DESCRIPTIONS

| PCI           AD [31:00]         IN/           C/BE [3:0]         IN/           PAR         IN/           FRAME         IN/ | n Type | Description                          |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------|--|--|--|

| AD [31:00]         IN/           C/BE [3:0]         IN/           PAR         IN/           FRAME         IN/               |        |                                      |  |  |  |

| C/BE [3:0]         IN/           PAR         IN/           FRAME         IN/                                                |        | Address/Data Bus                     |  |  |  |

| PAR IN/<br>FRAME IN/                                                                                                        |        | Command/Byte Enable signals          |  |  |  |

| FRAME IN/                                                                                                                   |        | Parity Signal                        |  |  |  |

|                                                                                                                             |        | Cycle Frame                          |  |  |  |

|                                                                                                                             | /OUT   | Target Ready                         |  |  |  |

|                                                                                                                             | /OUT   | Initiator Ready                      |  |  |  |

|                                                                                                                             | /OUT   | •                                    |  |  |  |

|                                                                                                                             | /OUT   | Stop<br>Lock                         |  |  |  |

|                                                                                                                             |        | Lock<br>Initialization Device Select |  |  |  |

| IDSEL IN                                                                                                                    |        |                                      |  |  |  |

|                                                                                                                             | /OUT   | Device Select                        |  |  |  |

| PCI REQ OL                                                                                                                  |        | PCI Request                          |  |  |  |

| PCI GNT IN                                                                                                                  |        | PCI Grant                            |  |  |  |

| CLK IN                                                                                                                      |        | PCI Clock                            |  |  |  |

| PCI RST IN                                                                                                                  |        | PCI Reset                            |  |  |  |

|                                                                                                                             | /OUT   | Parity Error                         |  |  |  |

| SERR OL                                                                                                                     |        | System Error                         |  |  |  |

| INTA OL                                                                                                                     | JT     | Interrupt                            |  |  |  |

| SCSI Interface                                                                                                              |        |                                      |  |  |  |

| <b>SD</b> [7:0] IN/                                                                                                         | /OUT   | SCSI Data                            |  |  |  |

|                                                                                                                             | /OUT   | SCSI Data Parity                     |  |  |  |

|                                                                                                                             | /OUT   | Message                              |  |  |  |

|                                                                                                                             | /OUT   | Command/Data                         |  |  |  |

|                                                                                                                             | /OUT   | Input/Output                         |  |  |  |

|                                                                                                                             | /OUT   | Attention                            |  |  |  |

|                                                                                                                             | /OUT   | Busy                                 |  |  |  |

|                                                                                                                             | /OUT   | Select                               |  |  |  |

|                                                                                                                             | /OUT   | SCSI Bus Reset                       |  |  |  |

|                                                                                                                             | /OUT   | Request                              |  |  |  |

|                                                                                                                             | /OUT   | Acknowledge                          |  |  |  |

| Boot ROM Interface                                                                                                          |        |                                      |  |  |  |

|                                                                                                                             |        |                                      |  |  |  |

| BOOT IN                                                                                                                     |        | Boot ROM Enable                      |  |  |  |

| BA [7:0] OL                                                                                                                 |        | Boot ROM Address                     |  |  |  |

| BD [7:0] IN                                                                                                                 |        | Boot ROM Data                        |  |  |  |

|                                                                                                                             |        | ROM Output Enable                    |  |  |  |

|                                                                                                                             | JI     | High Address Byte Latch Clock        |  |  |  |

| Miscellaneous                                                                                                               |        |                                      |  |  |  |

| SCSI CLK1 IN                                                                                                                |        | SCSI Core Clock                      |  |  |  |

| RES_DNC IN                                                                                                                  |        | Reserved, DO NOT CONNECT             |  |  |  |

| Power Management                                                                                                            |        |                                      |  |  |  |

| PWDN IN                                                                                                                     |        | Power Down Indicator                 |  |  |  |

| BUSY OL                                                                                                                     |        | SCSI Bus Activity Pin                |  |  |  |

|                                                                                                                             |        |                                      |  |  |  |

| Power Supply                                                                                                                |        |                                      |  |  |  |

| V <sub>DD</sub>                                                                                                             |        | +5 V                                 |  |  |  |

| V <sub>SS</sub>                                                                                                             |        | GND                                  |  |  |  |

| V <sub>DDB</sub>                                                                                                            |        | +5 V (Buffer)                        |  |  |  |

| V <sub>SSB</sub>                                                                                                            |        | GND (Buffer)                         |  |  |  |

| V <sub>DD3B</sub>                                                                                                           |        | +5 V (PCI)                           |  |  |  |

| V <sub>SS3B</sub>                                                                                                           |        | GND (5 V PCI)                        |  |  |  |

# 2.3 SIGNAL DESCRIPTIONS

## 2.3.1 Address and Data Pins

#### AD (31:00)

Address/Data (Input/Output, Active High)

Address and Data are multiplexed on the same PCI pins. During the first clock of a transaction the AD (31:00) contains the physical address (32 bits). During subsequent clocks AD (31:00) may contain data. Little-endian byte ordering is used. AD (07:00) is defined as least significant byte and AD (31:24) is defined as the most significant byte.

When PCI RST is active, AD(31:00) are inputs for NAND tree testing.

#### C/BE (3:0)

Bus Command/Byte Enable (Input/Output, Active Low)

Command and Byte Enables are multiplexed on the same PCI pins. During the address phase of the transaction, C/BE(3:0) define the bus command. During the data phase C/BE(3:0) are used as Byte Enables. The Byte Enables define which byte lanes carry meaningful data. C/BE(0) applies to the least significant byte (byte 0) and C/BE(3) applies to the most significant byte (byte 3).

When PCI RST is active, C/BE (3:0) are inputs for NAND tree testing.

#### PAR

Parity (Input/Output, Active High)

Parity is even across AD(31:00) and C/BE (3:0). Parity is generated and driven during Master Address Cycle, Memory Write, I/O Read, and Configuration Read cycles. Parity is checked during Slave Address Cycle, Memory Read, I/O Write, and Configuration Write cycles.

When PCI RST is active, PAR is an input for NAND tree testing.

## 2.3.2 PCI Interface Control Pins

#### FRAME

Cycle Frame (Input/Output, Active Low)

This signal is driven by the Am53C974A when it is the bus master to indicate the beginning and duration of the access. FRAME is asserted to indicate that bus transaction is beginning. FRAME is asserted while data transfers continue. FRAME is driven high when the transaction is in the final data phase.

When PCI RST is active, FRAME is an input for NAND tree testing.

TRDY

Target Ready (Input/Output, Active Low)

When the Am53C974A is selected as a slave, it will drive(low) this signal to indicate its ability to complete the current data phase of the transaction. As a master, this signal is an input to the Am53C974A from the selected (slave) device.

TRDY is used in conjunction with IRDY to indicate completion of the data phase. The data phase is complete (on any clock) when both TRDY and IRDY are sampled asserted. During a read transaction, TRDY is asserted when valid data is present on AD (31:00), while during a write transaction, TRDY asserted indicates the target is prepared to accept data. Wait cycles are inserted until both IRDY and TRDY are asserted together.

When  $\overline{PCIRST}$  is active,  $\overline{TRDY}$  is an input for NAND tree testing.

IRDY

Initiator Ready (Input/Output, Active Low)

When the Am53C974A is the initiator (master), it will drive (low) this signal to indicate its ability to complete the current data phase of the transaction. As a slave, this signal is an input to the Am53C974A from the initiating (master) device.

**IRDY** is used in conjunction with **TRDY** to indicate completion of the data phase. The data phase is complete (on any clock) when both **IRDY** and **TRDY** are sampled asserted. During a read transaction, **IRDY** asserted indicates the master is prepared to accept data, while during a write transaction, **IRDY** is asserted to indicate that valid data is present on AD (31:00). Wait cycles are inserted until both **IRDY** and **TRDY** and **TRDY** are asserted together.

When PCI RST is active, IRDY is an input for NAND tree testing.

#### STOP

Stop (Input/Output, Active Low)

In the slave role the Am53C974A drives the STOP signal to indicate to the bus master to stop the current transaction. In the bus master role the Am53C974A receives the STOP signal and stops the current transaction.

When PCI RST is active, STOP is an input for NAND tree testing.

#### LOCK

Lock (Input/Output, Active Low)

In the master role the Am53C974A drives the  $\overline{LOCK}$  signal to indicate to the slave device that multiple transactions may be necessary to complete an operation. When  $\overline{LOCK}$  is asserted, non-exclusive transactions may proceed. Control of  $\overline{LOCK}$  is obtained under its own protocol in conjunction with PCI GNT. In the slave role the Am53C974A receives the  $\overline{LOCK}$  signal from the master.

When PCI RST is active, LOCK is an input for NAND tree testing.

**Note**: In the current implementation, the Am53C974A as a master will never generate a LOCK. However in slave role, the chip will respond to a LOCK asserted by a master.

IDSEL

Initialization Device Select (Input, Active High)

This signal is used as a chip select for the Am53C974A in lieu of the 24 address lines during configuration read and write transaction.

When PCI RST is active, IDSEL is an input for NAND tree testing.

#### DEVSEL

Device Select (Input/Output, Active Low)

This signal when actively driven by the Am53C974A as a slave device signals to the master device that it has decoded its address as the target of the current access. As an input it indicates whether any device on the bus has been selected.

When PCI RST is active, DEVSEL is an input for NAND tree testing.

#### 2.3.3 Arbitration Pins

#### PCI REQ

PCI Request (Output, Active Low, Tristate)

This signal indicates to the arbiter that the Am53C974A desires use of the bus. This is a point to point signal. Every master has its own equivalent of  $\overrightarrow{\text{PCI REQ}}$ , which will be tristated after a power-up or a chip reset.

When PCI RST is active, PCI REQ is an input for NAND tree testing.

#### PCI GNT

PCI Grant (Input, Active Low)

This signal indicates that the access to the bus has been granted to the Am53C974A. This is a point to point signal. Every master has its own equivalent of PCI GNT.

When PCI RST is active, PCI GNT is an input for NAND tree testing.

#### 2.3.4 System Pins

#### CLK

Clock (Input)

This signal provides timing for all the transactions on the PCI bus and all PCI devices on the bus including the Am53C974A. All signals are sampled on the rising edge of CLK and all parameters are defined with respect to this edge. The Am53C974A operates up to 33 MHz.

When PCI RST is active, CLK is an input for NAND tree testing.

#### PCI RST

PCI Reset (Input, Active Low)

This signal forces the Am53C974A sequencer to a known state. All Three-State bi-directional signals are forced to a high impedance state and all Sustained Open Drain signals are allowed to float high. The Am53C974A will tristate PCI REQ, and completely reset the Am53C974A. PCI RST may be asynchronous to the CLK when asserted or driven low. It is recommended that the deassertion be synchronous to guarantee a clean and bounce free edge.

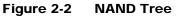

When PCI RST is active, NAND tree testing is enabled. All PCI interface pins are input mode. The result of the NAND tree testing can be observed on the BUSY output (pin 62).

#### 2.3.5 Error Reporting Pins

#### PERR

Parity Error (Input/Output, Active Low)

This signal may be pulsed by the Am53C974A when it detects a parity error during any data phase when its AD (31:00) and C/BE (3:0) lines are inputs. The Am53C974A monitors the PERR input during a bus master write cycle. It will assert the Data Parity Reported bit in the Status Register of the PCI Configuration Space when a parity error is reported by the target device.

When  $\overline{\text{PCI} \text{ RST}}$  is active,  $\overline{\text{PERR}}$  is an input for NAND tree testing.

#### SERR

System Error (Output, Active Low, Open Drain)

This signal may be pulsed by the Am53C974A for reporting address parity errors when AD(31:00) are inputs.

When PCI RST is active, SERR is an input for NAND tree testing.

#### 2.3.6 Interrupt Request Pins

#### INTA

Interrupt Request (Output, Active Low, Open Drain)

This signal combines the interrupt request from both the DMA engine and the SCSI block. The interrupt source can be determined by reading the DMA Status register ((B)+70). Interrupts caused by the DMA engine may be cleared in two ways. When the Write Erase feature is not set in the SBAC register ((B)+54), the INTA signal will be cleared when the Status Register ((B)+54) is read. When the Write Erase feature is set, the INTA signal will only be cleared when a '1' is written to the bit associated with the interrupting condition. For those interrupts generated by the SCSI block, the SCSI interrupt register must be serviced in order to clear the interrupt.

When PCI RST is active, INTA is an input for NAND tree testing.

#### 2.3.7 SCSI Interface Signals

#### SD (7:0)

SCSI Data (Input/Output, Active Low, Schmitt Trigger, Open Drain/Active Negation)

These pins are defined as bi-directional SCSI data bus.

SDP

#### SCSI Data Parity

(Input/Output, Active Low, Schmitt Trigger, Open Drain/Active Negation)

This pin is defined as bi-directional SCSI data parity.

#### MSG

Message (Input/Output, Active Low, Schmitt Trigger, Open Drain)

MSG is a bi-directional signal which is asserted during a MESSAGE phase. It is a schmitt triggered input in the Initiator role and an output with a 48 mA driver in the Target role.

#### $\overline{C}/D$

Command/Data (Input/Output, Active Low, Schmitt Trigger, Open Drain)

$\overline{C}/D$  is a bi-directional signal which is used to indicate whether CONTROL or DATA information is on the SCSI data bus. It is a schmitt trigger input in the Initiator role and an output with a 48 mA driver in the Target role.

#### Ī/O

Input/Output (Input/Output, Active Low, Schmitt Trigger, Open Drain)

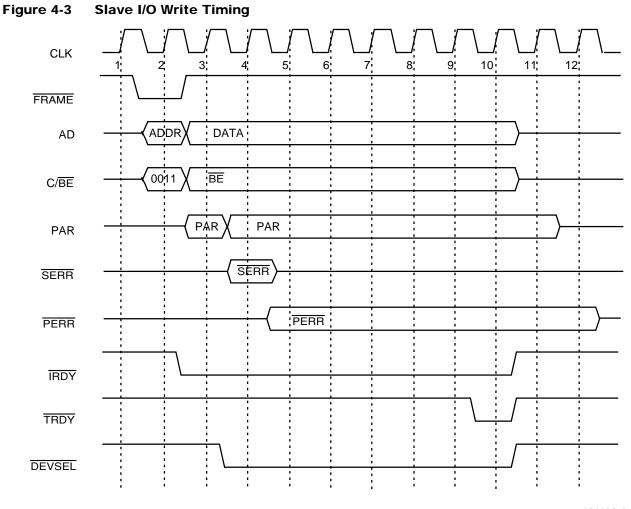

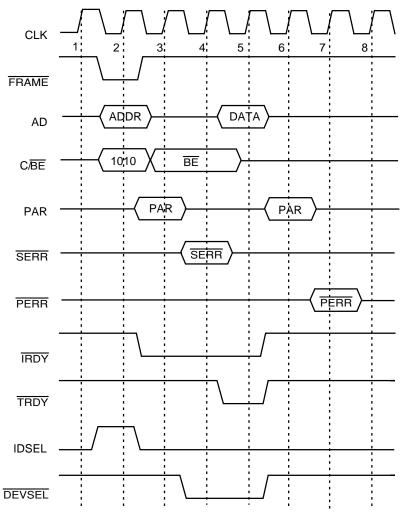

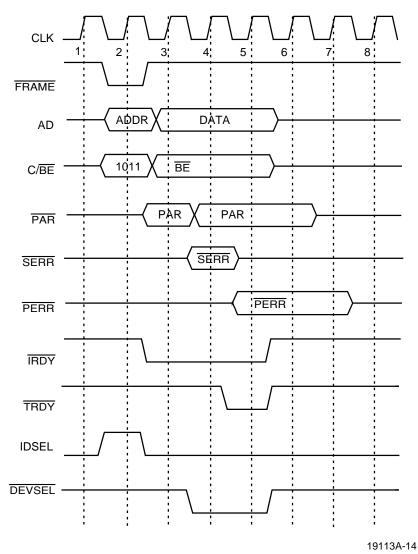

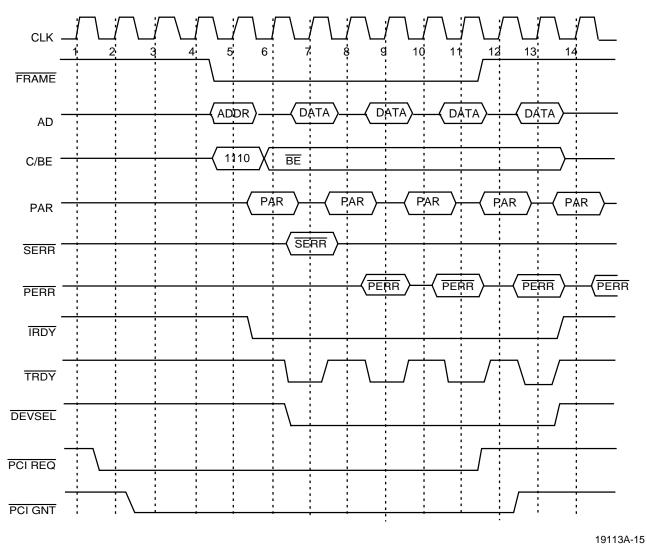

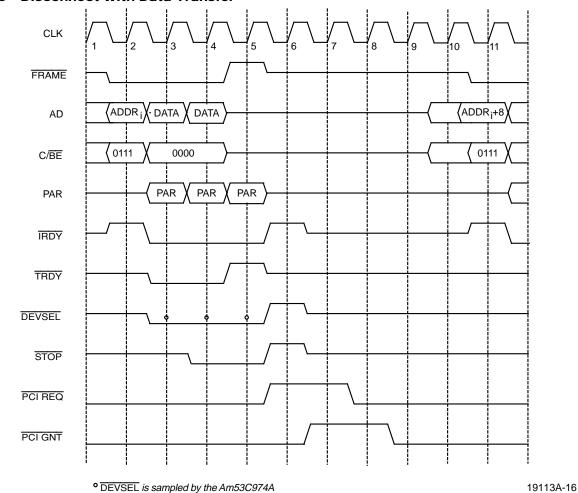

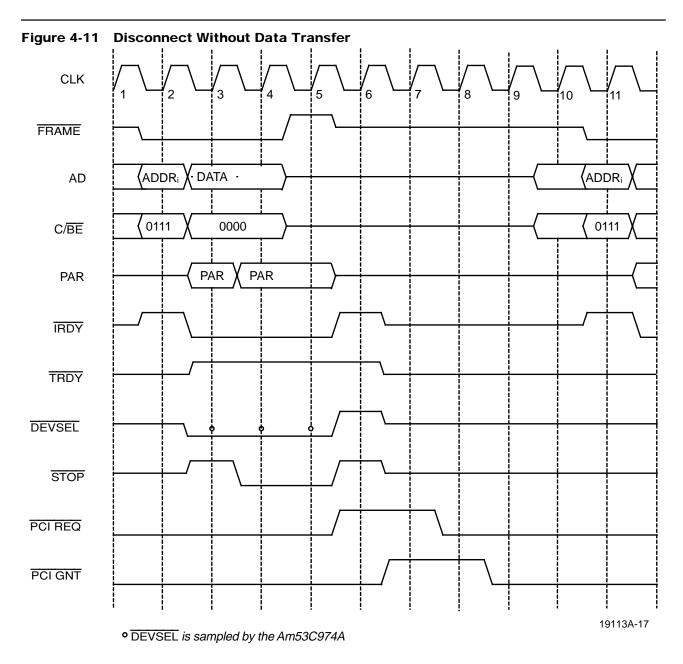

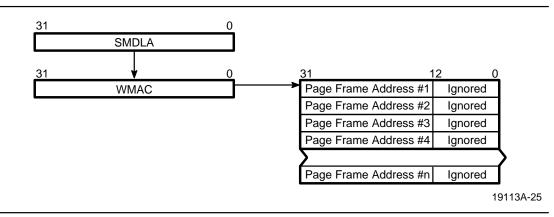

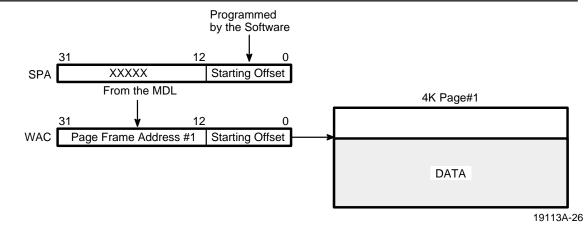

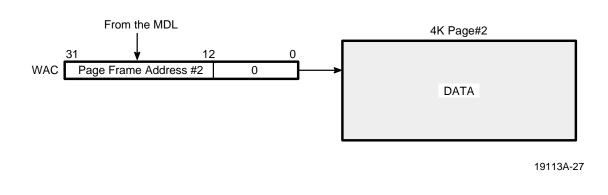

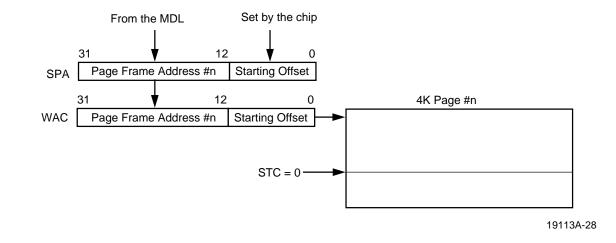

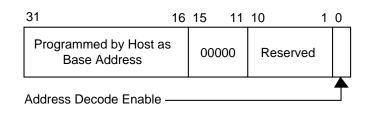

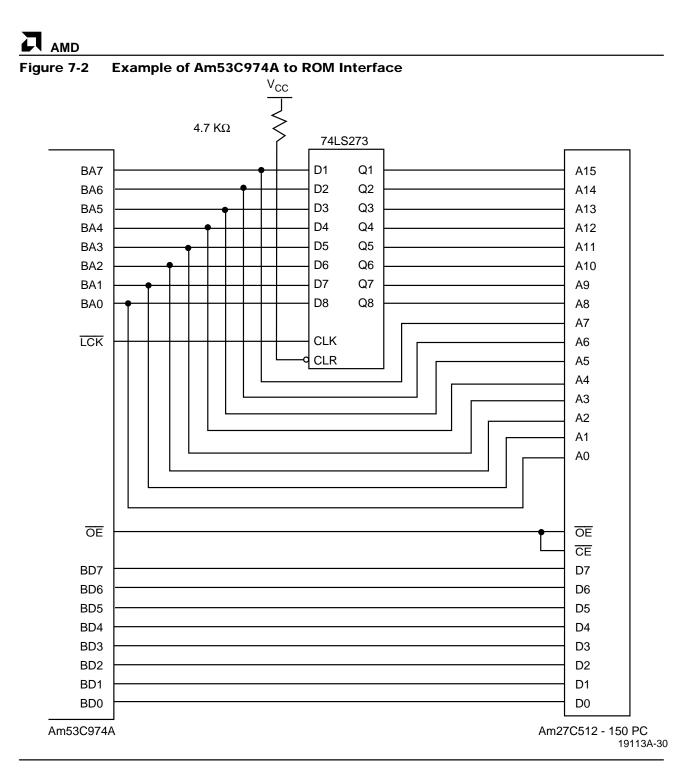

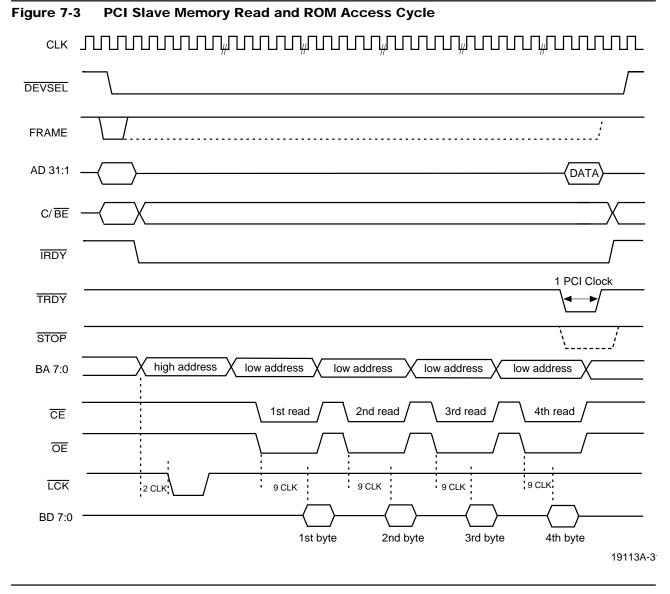

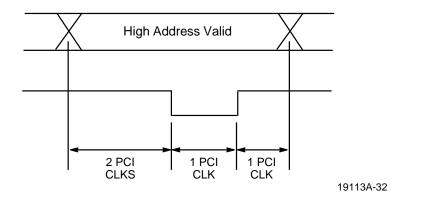

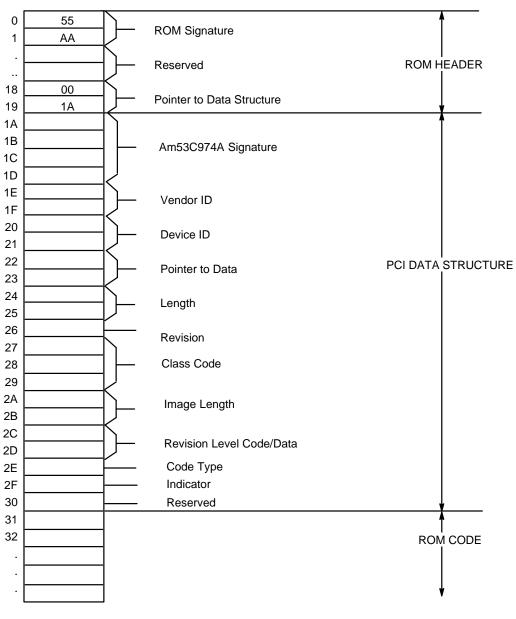

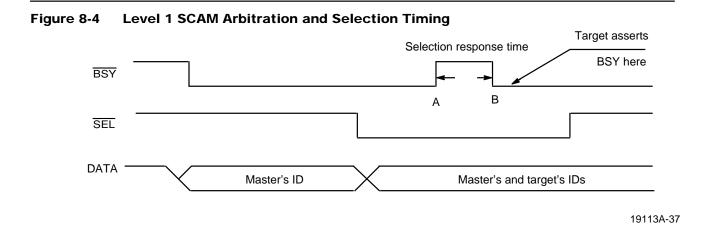

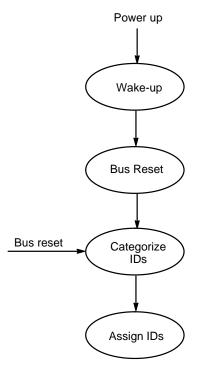

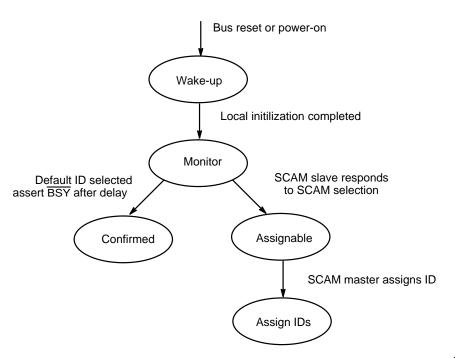

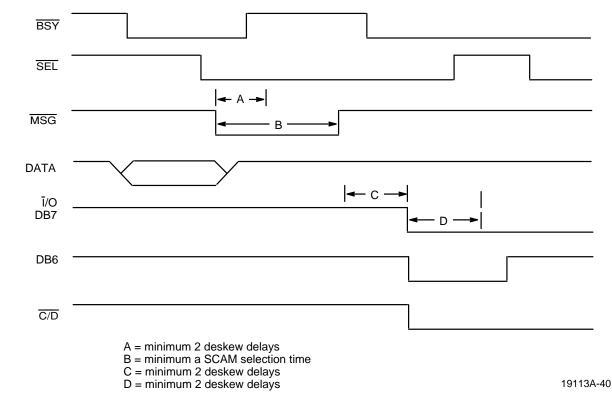

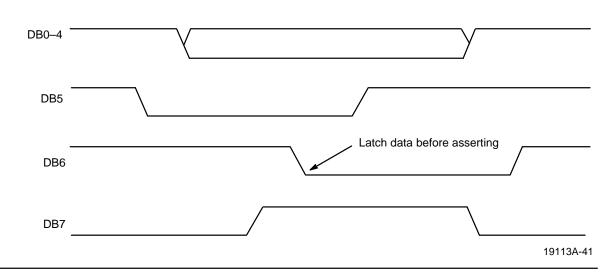

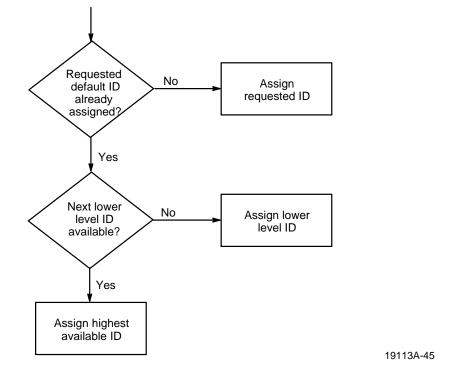

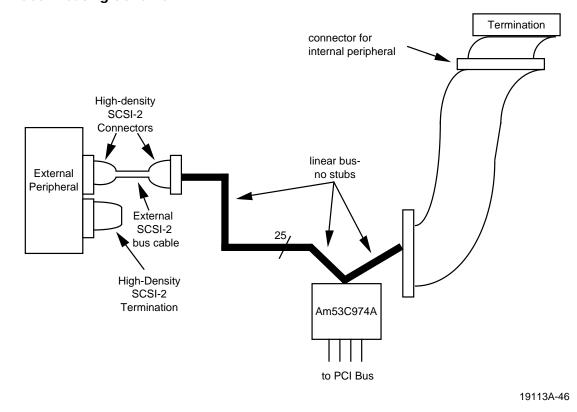

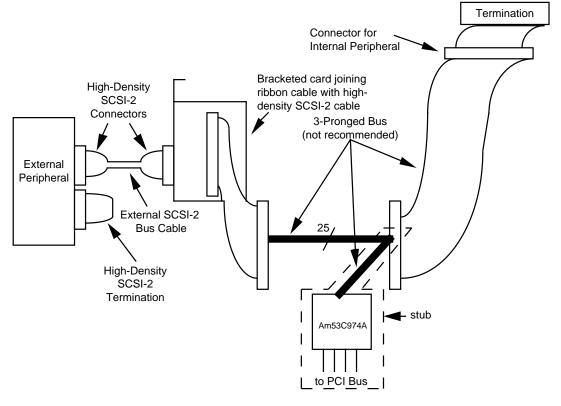

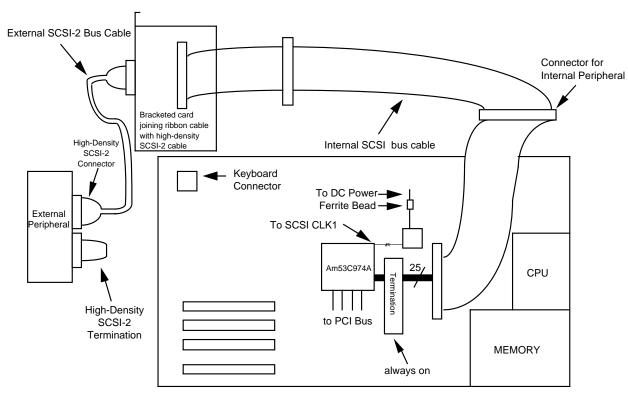

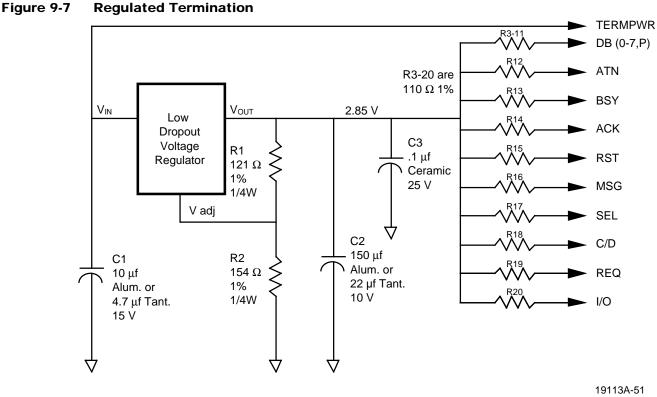

Ī/O is a bi-directional signal which controls the direction of data movement on the SCSI data bus with respect to the initiator. It is a schmitt triggered input in the Initiator role and an output with a 48 mA driver in the Target role.