# 16-Bit A/D Converter

**AD7701**

### 1.1 Scope.

This specification covers the detail requirement for a 16-bit ADC which uses a sigma-delta conversion technique. No missing codes ensures true, usable, 16-bit dynamic range, removing the need for programmable gain and level-setting circuitry.

### 1.2 Part Number.

The complete part number per Table 1 of this specification is as follows.

Device

Part Number

-1

AD7701TQ/883B

#### 1.2.3 Case Outline.

See Appendix 1 of General Specification ADI-M-1000: package outline:

Package Description

Q-20 20-Pin Cerdip

### 1.3 Absolute Maximum Ratings.

## 1.4 Recommended Operating Conditions.

| Positive Supply Voltage Range                                        |

|----------------------------------------------------------------------|

| AV <sub>DD</sub> +4.5 V dc to +5.5 V dc                              |

| $\mathrm{DV_{DD}}$                                                   |

| Negative Supply Voltage Range (AV <sub>SS</sub> , DV <sub>SS</sub> ) |

| Calibration Memory Retention Supply Voltage+2.0 V dc minimum         |

| Operating Temperature Range, T <sub>A</sub>                          |

# AD7701—SPECIFICATIONS

Table 1.

|                                                            |                             |            | Lin                   | nits                      | Sub                | Conditions <sup>1</sup> $(-55^{\circ}C \le T_A \le +125^{\circ}C$ |        |

|------------------------------------------------------------|-----------------------------|------------|-----------------------|---------------------------|--------------------|-------------------------------------------------------------------|--------|

| Test                                                       | Symbol                      | Device     | Min                   | Max                       | Groups A           | unless otherwise noted)                                           | Unit   |

| Resolution                                                 | RES                         | All        | 16                    |                           | 1, 2, 3            | Guaranteed Minimum Resolution                                     | Bits   |

| Integral Nonlinearity                                      | INL                         | All        |                       | ±0.0015                   | 1, 2, 3            |                                                                   | %FSR   |

| Differential Nonlinearity                                  | DNL                         | All        |                       | ±0.5                      | 1, 2, 3            | Guaranteed No Missing Codes                                       | LSB    |

| Positive Full-Scale Error <sup>2</sup>                     | PFSE                        | All        |                       | ±0.5                      | 1                  |                                                                   | LSB    |

| Unipolar Offset Error <sup>2</sup>                         | UOE                         | Al         |                       | ±1.0                      | 1                  |                                                                   | LSB    |

| Bipolar Zero Error <sup>2</sup>                            | BZE                         | All        |                       | ±1.0                      | 1                  |                                                                   | LSB    |

| Bipolar Negative Full-Scale Error <sup>2</sup>             | BNFSE                       | All        |                       | ±2.0                      | 1                  |                                                                   | LSB    |

| Positive Full-Scale Overrange <sup>3</sup>                 | +V <sub>FSO</sub>           | All        |                       | $V_{REF} + 0.1$           | 1                  |                                                                   | v      |

| Negative Full-Scale Overrange <sup>3</sup>                 | $-V_{FSO}$                  | All        |                       | $-(V_{REF} * 0.1)$        | 1                  |                                                                   | v      |

| Unipolar Input Offset Calibration<br>Range <sup>4, 5</sup> | V <sub>UCAL</sub>           | Ali        |                       | -(V <sub>REF</sub> + 0.1) | 1                  |                                                                   | v      |

| Bipolar Input Offset Calibration<br>Range <sup>4, 5</sup>  | V <sub>BCAL</sub>           | All        | -0.4 V <sub>REF</sub> |                           | 1                  |                                                                   | v      |

| Calibration Input Span <sup>6</sup>                        | V <sub>CIS</sub>            | All        | 0.8 V <sub>REF</sub>  | 2 V <sub>REF</sub> +0.2   | 1                  |                                                                   | v      |

| Analog Input Voltage Range,<br>Unipolar<br>Bipolar         | V <sub>AIN(U)</sub>         | All<br>All | 0<br>-2.5             | <b>2,</b> 5 +2.5          | 1, 2, 3<br>1, 2, 3 |                                                                   | v<br>v |

| Logic Input Low Voltage                                    | V <sub>IL</sub>             | All        | .,,                   | 0.8                       | 1, 2, 3            |                                                                   | v      |

| Logic Input High Voltage                                   | V <sub>IH</sub>             | All        | 2.0                   | ··                        | 1, 2, 3            | All Input Except CLKIN                                            | v      |

|                                                            |                             |            | 3.5                   |                           |                    | CLKIN                                                             |        |

| Logic Input Current                                        | I <sub>IN</sub>             | All        |                       | 10                        | 1, 2, 3            |                                                                   | μA     |

| Output Logic Low Voltage                                   | V <sub>OL</sub>             | All        |                       | 0.4                       | 1, 2, 3            | $I_{SINK} = 1.6 \text{ mA}$                                       | v      |

| Output Logic High Voltage                                  | V <sub>OH</sub>             | All        | DV <sub>DD</sub> -1.0 |                           | 1, 2, 3            | I <sub>SOURCE</sub> = 100 μA                                      | v      |

| Floating State Leakage Current                             |                             | All        |                       | ±10                       | 1, 2, 3            |                                                                   | μА     |

| Analog Positive Supply Current                             | $AI_{DD}$                   | Alì        |                       | 3.2                       | 1, 2, 3            | Note 7                                                            | mA     |

| Digital Positive Supply Current                            | $\mathrm{DI}_{\mathrm{DD}}$ | All        | -                     | 1.5                       | 1, 2, 3            | Note 7                                                            | mA     |

| Analog Negative Supply Current                             | AI <sub>SS</sub>            | All        |                       | 3.2                       | 1, 2, 3            | Note 7                                                            | mA     |

| Digital Negative Supply Current                            | DI <sub>SS</sub>            | All        |                       | 0.1                       | 1, 2, 3            | Note 7                                                            | mA     |

| Master Clock Frequency8, 9                                 | f <sub>CLKIN</sub>          | All        | 40                    | _                         | 9, 10, 11          | Internal Gate Oscillator                                          | kHz    |

|                                                            |                             |            |                       | 5000                      |                    | Externally Supplied                                               |        |

| Digital Output Rise Time <sup>8, 10</sup>                  | t <sub>r</sub>              | All        |                       | 50                        | 9, 10, 11          |                                                                   | ns     |

| Digital Output Fall Time <sup>8, 10</sup>                  | t <sub>f</sub>              | All        |                       | 50                        | 9, 10, 11          |                                                                   | ns     |

| Setup Time, SC1,<br>SC2 to CAL High                        | ti                          | All        | 0 .                   |                           | 9, 10, 11          |                                                                   | ns     |

| SC1, SC2 Hold Time After<br>CAL Goes High                  | t <sub>2</sub>              | All        | 50                    |                           | 9, 10, 11          |                                                                   | ns     |

| Setup Time, SLEEP High to CLKIN High <sup>8, 11</sup>      | t <sub>3</sub>              | All        | 1000                  |                           | 9, 10, 11          |                                                                   | ns     |

| Test                                                         | Symbol             | Device   | Lin                  | iits<br>Max                              | Sub<br>Groups A   | Conditions <sup>1</sup> $(-55^{\circ}C \leq T_A \leq +125^{\circ}C)$ unless otherwise noted) | Unit |

|--------------------------------------------------------------|--------------------|----------|----------------------|------------------------------------------|-------------------|----------------------------------------------------------------------------------------------|------|

|                                                              | т. —               | L        | 1                    | Max                                      | Groups A          | uniess otherwise noted)                                                                      | Cint |

| Synchronous Self-Clocking Mode                               | e (SSC) Tu         | ming Cha | racteristics         | <del></del>                              |                   |                                                                                              |      |

| Data Access Time (CS Low to Data Valid) <sup>8, 12</sup>     | t <sub>4</sub>     | All      | 3/f <sub>CLKIN</sub> |                                          | 9, 10, 11         |                                                                                              | ns   |

| SCLK Falling Edge to Data<br>Valid Delay <sup>8</sup>        | t <sub>5</sub>     | All      |                      | 100                                      | 9, 10, 11         |                                                                                              | ns   |

| MSB Data Setup Time <sup>8</sup>                             | t <sub>6</sub>     | All      | 250                  |                                          | 9, 10, 11         |                                                                                              | ns   |

| SCLK High Pulse Width <sup>8</sup>                           | t <sub>7</sub>     | All      |                      | 300                                      | 9, 10, 11         |                                                                                              | ns   |

| SCLK Low Pulse Width <sup>8</sup>                            | t <sub>8</sub>     | All      |                      | 790                                      | 9, 10, 11         |                                                                                              | ns   |

| SCLK Rising Edge to High<br>Impedance Delay <sup>8, 13</sup> | t <sub>9</sub>     | All      |                      | 1/f <sub>GLKIN</sub> ± 200               | 9, 10, 11         |                                                                                              | ns   |

| CS High to High Impedance<br>Delay <sup>8, 13, 14</sup>      | t <sub>10</sub>    | All      |                      | <sup>4,2</sup> CLKIN <sup>‡</sup><br>200 | <b>9</b> , 10, 11 |                                                                                              | ns   |

| Synchronous External Clock Mo                                | de (SE <b>C) I</b> | insing C | haracteristics.      |                                          |                   |                                                                                              |      |

| Serial Clock Input Frequency <sup>8</sup>                    | f <sub>sclk</sub>  | Atl'     |                      | 5.1                                      | 9, 10, 11         |                                                                                              | MHz  |

| SCLK Input High Pulse Width8                                 | t <sub>l1</sub>    | AH       | 50                   |                                          | 9, 10, 11         |                                                                                              | ns   |

| SCLK Low Pulse Width <sup>8</sup>                            | t <sub>12</sub>    | All      | 180                  |                                          | 9, 10, 11         |                                                                                              | ns   |

| Data Access Time (CS Low to Data Valid) <sup>8, 12, 15</sup> | t <sub>13</sub>    | All      |                      | 160                                      | 9, 10, 11         |                                                                                              | ns   |

| SCLK Falling Edge to<br>Data Valid Delay <sup>8, 16</sup>    | t <sub>14</sub>    | All      | 150                  |                                          | 9, 10, 11         |                                                                                              | ns   |

| CS High to High Impedance<br>Delay <sup>8, 13</sup>          | t <sub>15</sub>    | All      | 250                  |                                          | 9, 10, 11         |                                                                                              | ns   |

| SCLK Falling Edge to High<br>Impedance Delay <sup>8</sup>    | t <sub>16</sub>    | All      | 200                  |                                          | 9, 10, 11         |                                                                                              | ns   |

| Asynchronous Communications                                  | Mode (AC)          | Timing   | Characteristic       | es                                       |                   |                                                                                              |      |

| CS Setup Time <sup>8</sup>                                   | t <sub>17</sub>    | All      |                      | 40                                       | 9, 10, 11         |                                                                                              | ns   |

| Data Delay Time <sup>8</sup>                                 | t <sub>18</sub>    | All      |                      | 180                                      | 9, 10, 11         |                                                                                              | ns   |

| SCLK Falling Edge to High<br>Impedance Delay <sup>8</sup>    | t <sub>19</sub>    | All      |                      | 200                                      | 9, 10, 11         |                                                                                              | ns   |

# AD7701

#### NOTES

- $^{1}AV_{DD} = DV_{DD} = 5.0 \text{ V dc}$ ;  $AV_{SS} = DV_{SS} = -5.0 \text{ V dc}$ ;  $V_{REF} = +2.5 \text{ V dc}$ ;  $f_{CLKIN} = 4.096 \text{ MHz}$ ; bipolar mode; MODE = 5.0 V dc;  $A_{IN}$  source resistance =  $1 \text{ k}\Omega$  with 1.0 nF to AGND at  $A_{IN}$ , unless otherwise specified (the  $A_{IN}$  pin presents a very high impedance dynamic load which varies with clock frequency.)

- <sup>2</sup>Apply after calibration at the temperature of interest. Full-scale error applies for both unipolar and bipolar input ranges.

- <sup>3</sup>Applies to unipolar and bipolar ranges. After calibration, if  $A_{IN} > V_{REF}$ , the device will output all 1s. If  $A_{IN} < 0$  (unipolar) or  $-V_{REF}$  (bipolar), the device will output all 0s.

- <sup>4</sup>In unipolar mode the offset can have a negative value (-V<sub>REF</sub>) such that the unipolar mode can mimic bipolar mode operation.

- The specifications for input overrange and for input span apply additional constraints on the offset calibration range.

- <sup>6</sup>For unipolar mode, input span is the difference between full-scale and zero scale. For bipolar mode, input span is the difference between positive and negative full-scale points. When using less than the maximum input span, the span range may be place anywhere within the range of  $\pm (V_{REF} + 0.1)$ .

- <sup>7</sup>All digital outputs loaded. All digital inputs at 5.0 V dc CMOS levels.

- <sup>8</sup>Sample tested at +25°C to ensure compliance

- CLKIN Duty Cycle range is 20% to 80%. CLKIN must be supplied whenever the device is not in SLEEP mode. If no clock is present in this case, the device can draw higher current than specified and possibly become uncalibrated.

- <sup>10</sup>Specified using 10% and 90% points on waveform of interest.

- 11 In order to synchronize several devices together using the SLEEP pin, this specification must be met.

- 11t4 and t13 are measured with the load circuit of Figure xx and defined as the time required for an output to cross 0.8 V or 2.4 V.

- 13t8, t10, t15 and t16 are derived from the measured time taken by the data outputs to change 0.5 V when loaded with the circuit of

- Figure xx. The measured number is then extrapolated back to remove the effects of charging or discharging the 100 pF capacitor. This means that the time quoted in Table 1 is the true bus relinquish time of the part and as such as independent of external bus loading capacitance.

- 14If CS is returned high before all 16 bits are output, the SDATA and SCIK outputs will complete the current data bit and then go to high impedance.

- 15 If  $\overline{CS}$  is activated asynchronously to  $\overline{DRDY}$ ,  $\overline{CS}$  will not be recognized it reoccurs when  $\overline{DRDY}$  is high for four clock cycles. The propagation delay time be as great as 4 CLKIN cycles plus 160 ns. To guarantee proper clocking of SDATA when using saynchronous  $\overline{CS}$ , the SCLK input should not be taken high sooner than 4 CLKIN cycles plus 160 ns after  $\overline{CS}$  goes low.

- 16SDATA is clocked out on the falling edge of the SCLK input.

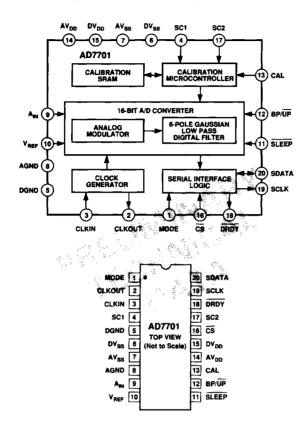

### 3.2.1 Functional Block Diagram and Terminal Assignments.

# AD7701

### 3.2.4 Microcircuit Technology Group.

This microcircuit is covered by technology group (81).

#### 4.2.1 Life Test/Burn-In Circuit.

Steady state life test is per MIL-STD-883 Method 1005. Burn-in is per MIL-STD-883 Method 1015 test condition (B).