# **Product Preview**

# Low Voltage Dual RF/IF PLL **Frequency Synthesizer**

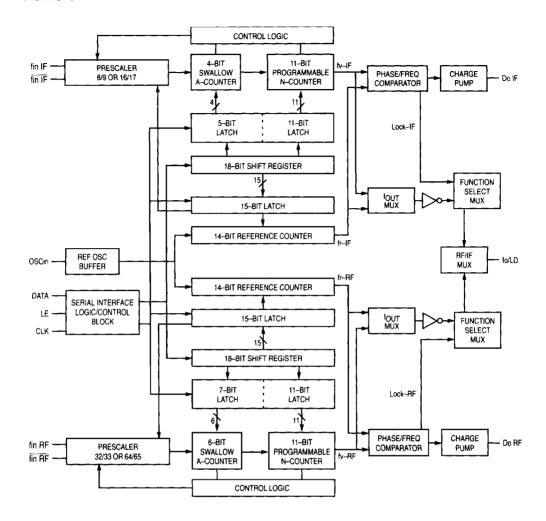

The MC12310 is a 2.5GHz (RF)/500MHz (IF) monolithic serial input dual phase locked loop (PLL) synthesizer. The device contains a complete RF prescaler/PLL synthesizer and an IF prescaler/PLL synthesizer. It is designed to provide the high frequency RF local oscillator control and IF oscillator control for dual conversion receivers or transceivers. The two synthesizers share a common serial programming port as well as the reference oscillator input. Each side contains separate reference counters for independent programming of the comparison frequency. The device is intended for RF personal communication applications where small size and low power are critical.

Motorola's advanced Bipolar MOSAIC V technology is utilized for low power operation at a minimum supply voltage of 2.7V. The device is designed for operation over a 2.7 to 5.5V supply range for input frequencies up to 2.5GHz/500 MHz with a typical current drain of 12.0mA. The low power consumption makes the MC12310 ideal for handheld battery operated applications such as cordless telephones or wireless LAN cards. Dual modulus prescalers are integrated to provide either a 32/33 or 64/65 divide ratio for the RF synthesizer and a 8/9 or 16/17 divide ratio for the IF synthesizer.

For additional applications information, two InterActiveApNote™ documents containing software (based on a Microsoft Excel spreadsheet) and an Application Note are available. Please order DK305/D and DK306/D from the Motorola Literature Distribution Center.

- Low Power Supply Current of 11.5mA Typical for I<sub>CC</sub> and 0.5mA Typical for le

- Supply Voltage of 2.7 to 5.5V

- Dual Modulus Prescaler With Selectable Divide Ratios of 32/33 or 64/65 for the RF Synthesizer and 8/9 or 16/17 for the IF Synthesizer

- · On-Chip Reference Frequency Buffer

- Two Programmable Reference Dividers Consisting of a Binary 14-Bit Reference Counter (R = 8 to 16383)

- Two Programmable Dividers Consisting of a Binary 6-Bit (4 Bit for IF) Swallow Counter and an 11-Bit Counter

- · Integrated Digital Phase/Frequency Detectors

- Balanced Charge Pump Outputs Which Can Be Disabled Individually Under Software Control

- · Multi-function Test Pin for Observing RF or IF Lock Detect Output or Any One of Four Comparison Signals

- Test Pin Can Be Disabled Under Software Control to Reduce Current Drain

- Operating Temperature Range of -40°C to +85°C

- · Space Efficient Plastic Surface Mount TSSOP Package

MOSAIC V and InterActiveApNote are trademarks of Motorola, Inc.

This document contains information on a product under development. Motorola reserves the right to change or discontinue this product without notice

#### 1/96 Motorola, Inc. 1996 224

MC12310

2.5GHz/500MHz LOW VOLTAGE DUAL PLL FREQUENCY SYNTHESIZER

## MAXIMUM RATINGS\*

| Symbol | Parameter                           | Value                   | Unit |

|--------|-------------------------------------|-------------------------|------|

| VCC    | Power Supply Voltage, Pins 1 and 20 | -0.5 to +6.0            | VDC  |

| Vp     | Power Supply Voltage, Pins 2 and 19 | V <sub>CC</sub> to +6.0 | VDC  |

| Tstg   | Storage Temperature Range           | -65 to +150             | °C   |

<sup>\*</sup> Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the Recommended Operating Conditions.

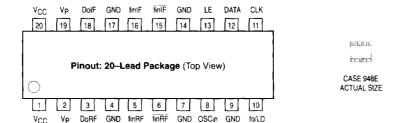

## PIN NAMES

| Name   | VΟ  | Function                                                                                                                                                                                                                                           |

|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSCin  |     | Reference oscillator input. An external oscillator source must be ac coupled in to this pin                                                                                                                                                        |

| VP     | -   | Power supply for charge pumps. Vp should be greater than or equal to V <sub>CC</sub> . Separate pins (Pin 2 for RF/Pin 19 for IF) supply the charge pump circuitry                                                                                 |

| vcc    | -   | Power supply voltage input. Bypass capacitors should be placed close to this pin and connected directly to the ground plane. Separate pins (Pin 1 for RF/Pin 20 for IF) supply the internal circuitry. Both V <sub>CC</sub> voltages must be equal |

| Do RF  | 0   | Internal charge pump output for RF synthesizer, can be disabled under SW control                                                                                                                                                                   |

| Do IF  | 0   | Internal charge pump output for IF synthesizer, can be disabled under SW control                                                                                                                                                                   |

| GND    | -   | Ground                                                                                                                                                                                                                                             |

| fo/LD  | 0   | Multi-function digital output. This output is selectable as fr-RF, fr-IF, fv-RF, fv-IF, Lock-RF or Lock-IF under software control                                                                                                                  |

| fin RF | 1   | Prescaler input for the RF synthesizer. The high-frequency VCO output signal is ac-coupled into this pin                                                                                                                                           |

| fin RF | 1   | Complementary prescaler input for the RF synthesizer. This pin is ac-bypassed to ground                                                                                                                                                            |

| fin IF | T   | Prescaler input for the IF synthesizer. The low frequency VCO output signal is ac~coupled into this pin                                                                                                                                            |

| fin IF | - 1 | Complementary prescaler input for the IF synthesizer. This pin is ac-bypassed to ground                                                                                                                                                            |

| CLK    | 1   | Clock input. Rising edge of clock shifts data into the shift registers                                                                                                                                                                             |

| DATA   | 1   | Binary serial input data                                                                                                                                                                                                                           |

| LE     | ı   | Load Enable input. When LE puises high, data stored in the shift registers is transferred into the appropriate latch (depending on the status of the control bits). In addition, while LE is high, the CLK input is disabled                       |

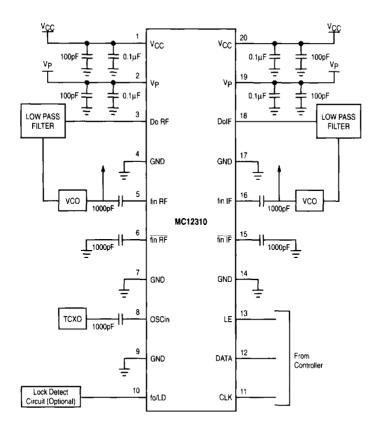

Figure 1. MC12310 Functional Block Diagram

#### SERIAL PROGRAMMING INTERFACE

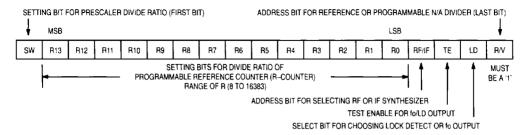

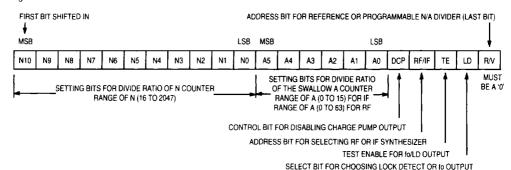

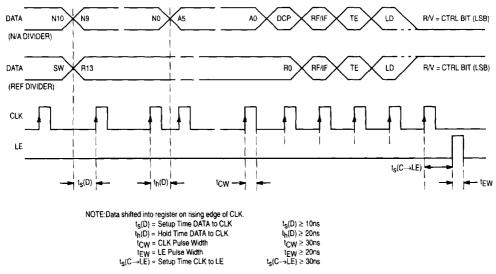

A simple 3-line uni-directional serial interface is used to program the synthesizer. The interface consists of DATA, CLK (clock), and LE (load enable) inputs. While the LE input is LOW, a rising edge of the clock shifts one bit of serial data into the internal shift registers. The most significant bit (MSB) is shifted in first (SW). The last bit is a control bit which steers the data stream to either the Reference Divider (19 bits) or Programmable N/A Divider (22 bits) Latch. When the LE input pulses HIGH, the contents shifted in will be latched into the device. Only the last 19 bits (or 22-bits) serially clocked into the device are retained. Additional leading bits are ignored. This is useful in those cases where the programmer prefers to deal with bit streams which are multiples of a byte in length.

#### PROGRAMMABLE REFERENCE DIVIDER

A 19-bit serial data format is used to access the programmable reference counter and prescaler select bit. There are 3 separate fields in this data format which are illustrated below. The first field is 1-bit wide (SW) and selects one of the two modulus prescalers. A HIGH selects the lower modulus prescaler pair while LOW selects the higher modulus prescaler pair. The next field is 14-bits wide and contains the value of the reference counter divide ratio. The final field is 4-bits wide and is used for addressing and control. The first bit in this field is RF/IF, which selects whether the data is going to be latched into the RF section (1=RF) or the IF section (0=IF). The next bit, Test Enable (TE) controls the multi-function fo/LD output (1=Active). When this bit is disabled (0=TE), the output circuitry is shut off to conserve power. The next bit, Lock Detect (LD) controls whether the lock detector signal (1=Lock) or the fout (0=fout) is routed to the fo/LD output. The final bit is a control bit R/V which must be set high (1=R/V) to address the data stream to the Reference Divider.

### DIVIDE RATIO OF PROGRAMMABLE REFERENCE (R) COUNTER

| Divide<br>Ratio R | R<br>13 | R<br>12 | H<br>11 | <b>A</b> 10 | A<br>9 | R<br>8 | R<br>7 | R<br>6 | B 5 | P 4 | Я<br>3 | R<br>2 | R<br>1 | R<br>0 |

|-------------------|---------|---------|---------|-------------|--------|--------|--------|--------|-----|-----|--------|--------|--------|--------|

| 8                 | 0       | 0       | 0       | 0           | 0      | 0      | 0      | 0      | 0   | 0   | 1      | 0      | 0      | 0      |

| 9                 | 0       | 0       | 0       | 0           | 0      | 0      | 0      | 0      | 0   | 0   | 1      | 0      | 0      | 1      |

| •                 | •       | •       | ٠       | •           | •      | •      | •      | •      | •   | •   | •      | •      | •      | •      |

| 16383             | 1       | 1       | 1       | 1           | 1      | 1      | 1      | 1      | 1   | 1   | 1      | 1      | 1      | 1      |

| PRESC       | ALER SELECT B                | SYNTHESIZER SE | TEST ENABLE | BIT   | LD SELECT BIT         |    |                         |    |

|-------------|------------------------------|----------------|-------------|-------|-----------------------|----|-------------------------|----|

| Synthesizer | Prescaler<br>Divide<br>Ratio | sw             | Synthesizer | RF/IF | Status<br>of<br>fo/LD | TE | Signal<br>From<br>fo/LD | LD |

| RF<br>RF    | 64/65<br>32/33               | 0              | IF          | 0     | Powered Down          | 0  | four                    | 0  |

| IF<br>IF    | 16/17<br>8/9                 | 0              | RF          | 1     | Active                | 1  | Lock Detect             | 1  |

#### PROGRAMMABLE N/A DIVIDER

A 22-bit serial data format is used to access the N Divider, A Divider, and some test control functions. There are 4 separate fields in this data format which are illustrated below. The first field is 11-bits wide and is used to program the N-counter. The next field is 6-bits wide and is used to program the A-counter. The next field (DCP) is 1-bit wide and it is used to enable and disable the charge pump output. If the field is set (1=DCP), the addressed charge pump is placed in a high-impedance state. In normal operation, the charge pump is enabled (0=DCP). The final field is 4-bits wide and is used for addressing and control. The first bit in this field is RF/IF, which selects whether the data is going to be latched into the RF section (1=RF) or the IF section (0=IF). The next bit, Test Enable (TE) controls the multi-function fo/LD output (1=Active). When this bit is disabled (0=TE), the output circuitry is shut off to conserve power. The next bit Lock Detect (LD) controls whether the lock detector signal (1=Lock) or the fout (0=fout) is routed to the fo/LD output. The final bit is a control bit R/V which must be set low (0=R/V) to address the data stream to the Programmable N/A Divider.

NOTE: When programming the A-counter for the IF loop, A4 and A5 should be set to '0'.

#### DIVIDE RATIO OF PROGRAMMABLE N-COUNTER

#### **DIVIDE RATIO OF SWALLOW A-COUNTER**

| Divide<br>Ratio N | N<br>10 | N 9 | 8 | N<br>7 | N 6 | N<br>5 | N<br>4 | N<br>3 | N<br>2 | N<br>1 | 20 | Divide<br>Ratio A | <b>A</b><br>5 | A<br>4 | A<br>3 | A<br>2 | A<br>1 | <b>A</b><br>0 |

|-------------------|---------|-----|---|--------|-----|--------|--------|--------|--------|--------|----|-------------------|---------------|--------|--------|--------|--------|---------------|

| 16                | 0       | 0   | 0 | 0      | 0   | 0      | 1      | 0      | 0      | 0      | 0  | 0                 | 0             | 0      | 0      | 0      | 0      | 0             |

| 17                | 0       | 0   | 0 | 0      | 0   | 0      | 1      | 0      | 0      | 0      | 1  | 1                 | 0             | 0      | 0      | 0      | 0      | 1             |

| •                 | •       | ٠   | • | •      | •   | •      | •      |        | •      | •      | •  | •                 | •             | •      | •      | •      | •      | •             |

| 2047              | 1       | 1   | 1 | 1      | 1   | 1      | 1      | 1      | 1      | 1      | 1  | 63                | 1             | 1      | 1      | 1      | 1      | 1             |

| SYNTHESIZER S | SYNTHESIZER SELECT<br>BIT |                 | BIT | LD SELECT         | ВІТ | CHARGE PUMP CONTROL<br>BIT |     |  |

|---------------|---------------------------|-----------------|-----|-------------------|-----|----------------------------|-----|--|

| Synthesizer   | RF/IF                     | Status of fo/LD | TE  | Signal from fo/LD | LD  | Do Output Status           | DCP |  |

| IF            | 0                         | Powered Down    | 0   | four              | 0   | Normal Operation           | 0   |  |

| RF            | 1                         | Active          | 1   | Lock Detect       | 1   | Disabled                   | 1   |  |

#### PROGRAMMING ORDER

There is no specific order by which the data words must be programmed for normal operation. In most applications, the RF and IF Programmable Reference Divider words are programmed first and the Programmable N/A Divider words are programmed last. The Programmable N/A Divider words are then changed as the synthesizer is tuned to different channels. It is important to note that the status of the TE and LD fields of the last word programmed determines the state of the fo/LD output.

#### PROGRAMMING THE STATE OF THE fo/LD OUTPUT

The multi-function test pin output can be used to observe any one of six internal signals: fr-RF, fr-IF, fv-RF, fv-IF, Lock-RF, and Lock-IF. In addition this output pin can be disabled to reduce current consumption of the part and minimize switching noise. All these functions are under software control. To fully configure the synthesizer, four data words must be programmed into the device to load all the latches. As previously stated, programming order is not important for normal operation. This is not the case though when the user would like to observe a test point. Under this condition, the last word loaded determines what test point will be observed. The table below illustrates which register needs to be programmed last and the state of the control bits to access each test point.

| fo/LD Output | Register          | R/V | RF/IF | TE | LD |

|--------------|-------------------|-----|-------|----|----|

| fr IF        | Reference Divider | 1   | 0     | 1  | 0  |

| fv IF        | N/A Divider       | 0   | 0     | 1  | 0  |

| Lock IF      | Either            | X   | 0     | 1  | 1  |

| fr RF        | Reference Divider | 1   | 1     | 1  | 0  |

| fv RF        | N/A Divider       | 0   | 1     | 1  | 0  |

| Lock RF      | Either            | X   | 1     | 1  | 1  |

| Disabled     | Either            | х   | X     | 0  | X  |

X = Don't Care

#### **DIVIDE RATIO SETTING**

fvco = [(P $\bullet$ N)+A] $\bullet$ fosc + R with A  $\leq$  N (for continuous frequency steps P $\bullet$ N+A  $\geq$  P(P $\sim$ 1))

fvco: Output frequency of external voltage controlled oscillator (VCO)

- N: Preset divide ratio of binary 11-bit programmable counter (16 to 2047)

- A: Preset divide ratio of binary 4-bit or 6-bit swallow counter (0 to 63, A≤N, for RF synthesizer; 0 to 15, A≤N, for IF synthesizer)

fosc: Output frequency of the external frequency oscillator

- R: Preset divide ratio of binary 14-bit programmable reference counter (8 to 16383)

- P: Preset mode of dual modulus prescaler (32 or 64 for RF synthesizer; 8 or 16 for IF synthesizer)

Figure 2. Serial Data Input Timing

## PHASE CHARACTERISTICS/VCO CHARACTERISTICS

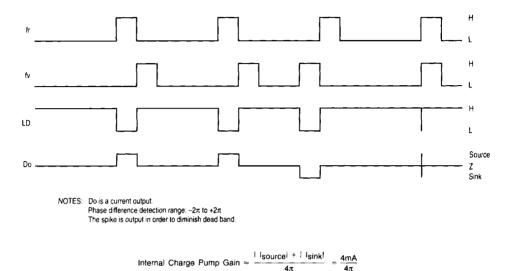

The phase comparator in the MC12310 is a high speed digital phase/frequency detector circuit. The circuit determines the "lead" or "lag" phase relationship and time difference between the leading edges of the VCO (fv) signal and the reference (fr) input. Since these edges occur only once per cycle, the detector has a range of  $\pm 2\pi$  radians.

The operation of the phase comparator is shown in 3.

Figure 3. Phase/Frequency Detector, Internal Charge Pump and Lock Detect Waveforms

## fr lags fv in phase OR fv>fr in frequency

When the phase of fr lags that of fv or the frequency of fv is greater than fr, the Do output will sink current. The pulse width will be determined by the time difference between the two rising edges.

#### fr leads to in phase OR fv<fr in frequency

When the phase of fr leads that of fv or the frequency of fv is less than fr, the Do output will source current. The pulse width will be determined by the time difference between the two rising edges.

#### fr = fv in phase and frequency

When the phase and frequency of fr and fv are equal, the charge pump will be in a quiet state, except for current spikes when signals are in phase. This situation indicates that the loop is in lock and the phase comparator will maintain the loop in its locked state.

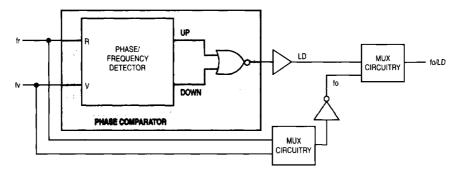

Figure 4. Detailed Phase/Frequency Comparator Block Diagram

#### LOCK DETECT

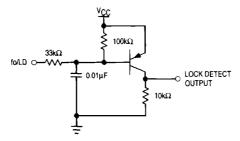

When the lock detector signal (Lock–IF or Lock–RF) is selected to be routed to the fo/LD output pin, the lock detector circuit provides a LOW pulse when fr and fv are not equal in phase or frequency. The output is normally HIGH. LD is designed to be the logical NORing of the phase frequency detector's outputs UP and DOWN. See 6. In typical applications the output signal drives external circuitry which provides a steady LOW signal when the loop is locked. See 9.

#### fo

When selected, the output frequency pin (to/LD) provides a LOW going pulse at the fr or fv rate. The pulse width is determined by the frequency in the respective counter. This output is for test purposes only and may not swing all the way down to ground. The scope probe capacitive load should be less than 5pF.

#### **OSCILLATOR INPUT**

The device incorporates an on-chip reference buffer so that an external reference oscillator signal can be ac-coupled to the OSCin pin through a coupling capacitor. The magnitude of the ac-coupled signal must be between 500 and 2200 mV peak-to-peak.

Figure 5. Typical Lock Detect Circuit

## MC12310

## **ELECTRICAL CHARACTERISTICS** ( $V_{CC} = 2.7$ to 5.5V; $V_P = V_{CC}$ to 6.0V; $T_A = -40$ to $+85^{\circ}C$ )

| Symbol              | Parameter                                                                                                    | Min                | Тур  | Max                  | Unit  | Condition                      |

|---------------------|--------------------------------------------------------------------------------------------------------------|--------------------|------|----------------------|-------|--------------------------------|

| lcc                 | Supply Current for V <sub>CC</sub>                                                                           | _                  | 11.5 |                      | mA    | Note 1                         |

|                     |                                                                                                              |                    | 12.5 |                      | mA    | Note 2                         |

| lр                  | Supply Current for Vp                                                                                        |                    | 0.5  |                      | mA    | Note 3                         |

|                     |                                                                                                              |                    | 0.7  |                      | mA    | Note 4                         |

| F <sub>IN</sub> -RF | Operating Frequency f <sub>IN</sub> max f <sub>IN</sub> min                                                  | 2500               |      | 500                  | MHz   | Note 5                         |

| F <sub>IN</sub> -IF | Operating Frequency f <sub>IN</sub> max f <sub>IN</sub> min                                                  | 500                |      | 40                   | MHz   | Note 5                         |

| Fosc                | Operating Frequency (OSCin)                                                                                  | TBD                | 12   | 40                   | MHz   | Note 5                         |

| VIN                 | Input Sensitivity f <sub>IN</sub> -RF<br>(100-500MHz) f <sub>IN</sub> -IF<br>(40-100MHz) f <sub>IN</sub> -IF | 200<br>200<br>600  |      | 1000<br>1000<br>2000 | mVb−b |                                |

| vosc                | OSCin                                                                                                        | 500                |      | 2200                 | mVp_p |                                |

| V <sub>IH</sub>     | Input HIGH Voltage CLK, DATA, LE                                                                             | 0.7V <sub>CC</sub> |      |                      | V     |                                |

| VIL                 | Input LOW Voltage CLK, DATA, LE                                                                              |                    |      | 0.3V <sub>CC</sub>   | V     |                                |

| lн                  | Input HIGH Current (DATA, CLK and LE)                                                                        |                    | 0.1  | 2.0                  | μА    | V <sub>CC</sub> = 5.5V         |

| I <sub>IL</sub>     | Input LOW Current (DATA, CLK and LE)                                                                         | -2.0               | -0.1 |                      | μА    | V <sub>CC</sub> = 5.5V         |

| losc                | Input Current (OSCin)                                                                                        |                    | TBD  |                      | μА    |                                |

| Source              | Charge Pump Output Current                                                                                   |                    | ~2.0 |                      | mA    | $V_{Do} = V_P/2; V_P = 2.7V$   |

| <sup>I</sup> Sink   | Do                                                                                                           |                    | +2.0 |                      | 1     | V <sub>CC</sub> = 2.7V; Note 6 |

| JHi~Z               | Output Disabled                                                                                              | -15                |      | +15                  | nA    | $0.5V < V_{Do} < V_{P} - 0.5V$ |

| VOH                 | Output HIGH Voltage (fo/LD)                                                                                  | 4.4                |      |                      | V     | V <sub>CC</sub> = 5.0V         |

|                     |                                                                                                              | 2.4                |      |                      | V     | V <sub>CC</sub> = 3.0V         |

| VOL                 | Output LOW Voltage (fo/LD)                                                                                   |                    |      | 0.4                  | V     | V <sub>CC</sub> = 5.0V         |

|                     |                                                                                                              |                    |      | 0.4                  | V     | V <sub>CC</sub> ≈ 3.0V         |

| Юн                  | Output HIGH Current (fo/LD)                                                                                  |                    |      | ~1.0                 | mA    |                                |

| loL                 | Output LOW Current (fo/LD)                                                                                   | 1.0                |      |                      | mA    |                                |

<sup>1.</sup> V<sub>CC</sub> = 3.3V, all outputs open. 2. V<sub>CC</sub> = 5.5V, all outputs open. 3. V<sub>P</sub> = 3.3V, all outputs open.

<sup>4.</sup> Vp = 6.0V, all outputs open.

<sup>5.</sup> AC coupling,  $F_{\mbox{\scriptsize IN}}$  measured with a 1000pF capacitor.

<sup>6.</sup> Source current flows out of the pin and sink current flows into the pin, typical charge pump sink and source curves are found in Figure 9.

Figure 6. Typical Applications Example

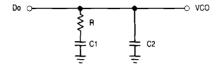

Figure 7. Typical Loop Filter

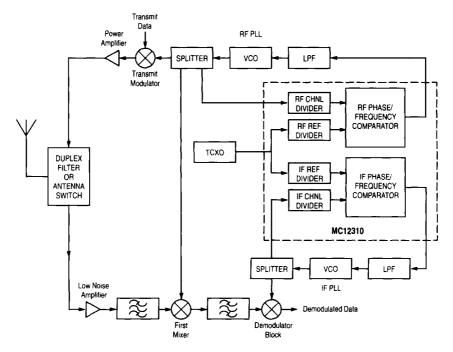

Figure 8. Typical Sub-System Block Diagram

Figure 9. Typical MC12310 Charge Pump Sink and Source Current versus  $V_{D0}$  ( $V_{CC}=2.7V,\,T_A=25^{\circ}C$ )