# AN4150 Application note

Power MOSFET technology gate current needs in a synchronous buck converter

#### Introduction

High frequency converters and applications require the best driver-MOSFET trade-off in terms of dynamic parameters to optimize the turn-on and turn-off transients. Power MOSFET technology also plays an important role in minimizing dynamic losses and improving system efficiency.

In this document, the full characterization of Power MOSFET gate current is realized by bench tests and OrCAD<sup>®</sup> simulation results, focusing on the impact of Power MOSFET technology on gate current behavior.

Ever increasing system switching frequency pushes designers and converter engineers to optimize semiconductor technology, improving device switching behavior and system efficiency. In fact, the higher the switching frequency, the larger the switching and dynamic losses; in these conditions, the best trade-off between the driver and Power MOSFET is mandatory to enhance the overall converter performance.

Power MOSFET gate current behavior during switching transients plays an important role in establishing a good trade-off between Power MOSFET and driver performance.

In this document, Power MOSFET gate current characterization is performed through bench tests and simulations (by Cadence<sup>®</sup> OrCAD Capture) on a single-phase synchronous buck converter, allowing a full understanding of the impact of the silicon technology on device gate current.

October 2012 Doc ID 023526 Rev 1 1/20

Contents AN4150

## **Contents**

| 1 | Synchronous buck converter description                 |  |  |  |  |  |

|---|--------------------------------------------------------|--|--|--|--|--|

|   | 1.1 Topology and theory of operation                   |  |  |  |  |  |

|   | 1.2 Low-side switching transients analysis             |  |  |  |  |  |

| 2 | Synchronous buck converter testing demonstration board |  |  |  |  |  |

|   | 2.1 Power MOSFET selection for comparative tests       |  |  |  |  |  |

| 3 | Bench tests and simulation results overview            |  |  |  |  |  |

| 4 | Conclusion                                             |  |  |  |  |  |

| 5 | References                                             |  |  |  |  |  |

| 6 | Revision history                                       |  |  |  |  |  |

AN4150 List of figures

## **List of figures**

| Figure 1.  | Single phase synchronous buck converter topology                             | 4  |

|------------|------------------------------------------------------------------------------|----|

| Figure 2.  | HS/LS waveforms during LS turn-off                                           |    |

| Figure 3.  | Shoot-through event caused by dv/dt                                          | 7  |

| Figure 4.  | HS/LS waveforms during LS turn-on                                            | 7  |

| Figure 5.  | Testing demonstration board schematic                                        | 8  |

| Figure 6.  | Rogowski coil package for I <sub>gate</sub> measurement                      | 9  |

| Figure 7.  | Device A (left) and device B (right) cross sections                          | 10 |

| Figure 8.  | Device A (left) and device B (right) cross sections with geometrical details | 10 |

| Figure 9.  | Gate charge comparison                                                       | 11 |

| Figure 10. | Device A gate waveforms                                                      | 12 |

| Figure 11. | Device B gate waveforms                                                      | 12 |

| Figure 12. | Device A vs. device B (experimental results)                                 | 13 |

| Figure 13. | Device A gate waveforms @ LS turn-off (simulated)                            | 14 |

| Figure 14. | Device A gate waveforms @ LS turn-on (simulated)                             | 14 |

| Figure 15. | Device B gate waveforms @ LS turn-off (simulated)                            | 14 |

| Figure 16. | Device B gate waveforms @ LS turn-on (simulated)                             | 14 |

| Figure 17. | Device A vs. device B (simulation results)                                   | 15 |

### 1 Synchronous buck converter description

#### 1.1 Topology and theory of operation

S1 gate

S2 gate

The platform used for the gate current characterization is a single-phase synchronous buck converter. In *Figure 1*, the basic schematic is depicted, where S1 is the control FET (or high-side FET) and S2 is the synchronous FET (or low-side FET). In the same image, it is also shown that the Power MOSFET gate signals are provided by the "control unit" in a synchronous way: S1 and S2 cannot be in an ON state simultaneously, avoiding the creation of a low-resistance path between the input voltage ( $V_{IN}$ ) and  $G_{ND}$  (shoot-through or cross-conduction), generating a spurious power dissipation worsening overall efficiency. L and CO form the output filter (low-pass filter), which generates a DC voltage from a square-wave signal on the low-side drain (so-called phase node).

Figure 1. Single phase synchronous buck converter topology

The synchronous buck converter is a closed-loop topology as the output voltage is compared firstly with a reference voltage, producing an error signal; this voltage is then compared to a sawtooth signal, at the desired switching frequency (fSW) (integrated in the control unit) to switch on and off the Power MOSFETs. In this way, the output voltage is regulated when line or load changes occur.

deadtime

Together with the output voltage regulation, the control unit provides complete logic control and protection (overcurrent, overvoltage, undervoltage, etc....).

When S1 is on, the current in the output coil increases linearly:

deadtime

$$\left(\frac{dI}{dt} = \frac{V_{IN} - V_{OUT}}{I}\right)$$

and  $V_L = V_{IN} - V_{OUT}$ . During the deadtime  $(t_{df})$ , the energy store in L discharges through the body-drain diode of S2 till its gate-source signal becomes high. Therefore, the load current diverts from the body-drain diode to the channel  $(V_{DS,ON} << V_{F,DIODE})$ . Finally, both gate signals are low and the body-drain diode is forward-biased, allowing the load current flow.

4/20 Doc ID 023526 Rev 1

During the deadtime and before the HS turn-on, the LS device must remove the charge stored in the LS body-drain diode (reverse recovery charge process) before sustaining drain-source voltage. Therefore, the body-drain characteristics, in terms of reverse recovery current and charge, seriously impact the Power MOSFET switching behavior and converter power losses, especially when the converter switching frequency rises up.

In a synchronous buck converter, the low-side drain is subjected to fast positive/negative slopes and high voltage spikes, which can exceed the low-side absolute maximum voltage, degrading the Power MOSFET reliability up unto its failure. Therefore, the right Power MOSFET choice and system configuration, device placement on the board, and the optimization of the stray inductances and parasitic, allow an important phase node spike reduction, improving the converter performance.

If  $t_{\text{ON}}$  is the HS conduction time and  $T_{\text{S}}$  the switching period, the converter duty cycle is defined as:

#### **Equation 1**

$$D = \frac{t_{ON}}{T_S}$$

So, the input-output relationship of a buck converter is given by:

#### **Equation 2**

$$V_{OUT} = D \bullet V_{IN}$$

#### 1.2 Low-side switching transients analysis

The low-side device works as a "synchronous rectifier" because its on-time interval is synchronized to the high-side FET on-time; moreover, it works alternatively in an OFF state (body-drain diode forward biased during deadtime) or in third quadrant ( $V_{DS} < 0$ ,  $I_{D} < 0$ ), as the load current flows from source to drain.

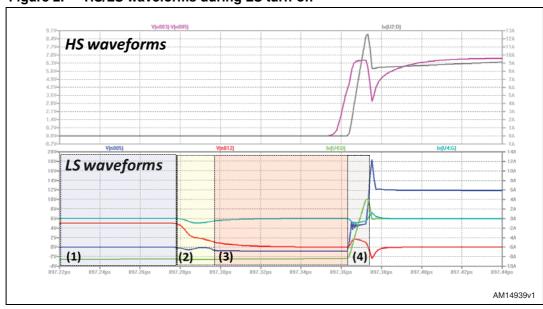

Figure 2. HS/LS waveforms during LS turn-off

In these conditions, it is interesting to analyze the switching transients.

In *Figure 2*, the HS and LS waveforms during LS turn-off are reported. The top half of the image shows HS  $V_{GS}$  (purple trace) and  $I_D$  (grey trace), while the bottom half shows LS  $V_{GS}$  (red trace),  $V_{DS}$  (blue trace),  $I_G$  (light blue trace) and  $I_D$  (light green trace).

The main LS turn-on steps are analyzed in detail, as follows:

- 1. Low-side FET is in an ON state (in this case,  $V_{GG} = 5 \text{ V}$ ), with load current flowing from source to drain (green trace). At the end of (1), the driver begins to turn off the FET.

- 2.  $V_{GS}$  goes down from  $V_{GG}$  to  $V_{th}$  and the gate current becomes negative and starts to remove the charge stored in the device intrinsic capacitances. At the end of (2), the gate-source voltage becomes equal to the threshold voltage ( $V_{GS} = V_{th}$ ): so, the gate current is dropped to low values (intrinsic caps are discharged) and the load current diverts from the Power MOSFET channel to the body-drain diode.

- During deadtime, the LS FET is in an OFF state (V<sub>GS</sub> = 0), V<sub>DS</sub> becomes negative (V<sub>DS</sub> = -V<sub>F,DIODE</sub>) and the load current flows through the body-drain diode. As a consequence, minority excess charge in both diode regions is created.

- 4. The LS current decreases linearly, while the HS current increases linearly in direct proportion to the fall of the LS FET current. To completely turn off the LS device, the excess stored charge in its body diode must be removed: so, the reverse recovery process generates an extra-current (I<sub>RR</sub>), which adds to the HS current. The maximum HS current peak is, therefore, given by:

$I_{D,HS} = I_{LOAD} + I_{RR}$

The spurious bouncing on the LS gate signal is caused by the voltage drop across package parasitic inductances (especially, source inductance), related to negative dl/dt (the current is falling to zero). Obviously, the bigger the parasitic inductance (package, wire bonding and layout) the higher the bouncing amplitude. At the same time, the low-side  $V_{DS}$  is fixed by the parasitic inductance and  $dl_{D,LS}/dt$ .

During device turn-off, the gate current is negative, because of the Power MOSFET intrinsic capacitances discharge process. The current is sunk by the driver, with a speed linked to the gate voltage level and overall gate resistance ( $R_{G.TOT} = R_{G.INT} + R_{DR.SINK}$ ).

It is important to underline that, at LS turn-off, the driver, external and intrinsic FET gate resistance should be as low as possible in order to minimize the device shoot-through risks, caused by high dv/dt across drain-source, coupled to the gate signals through Miller capacitance in *Figure 3*.

Rdr+Rg,ext

Figure 3. Shoot-through event caused by dv/dt

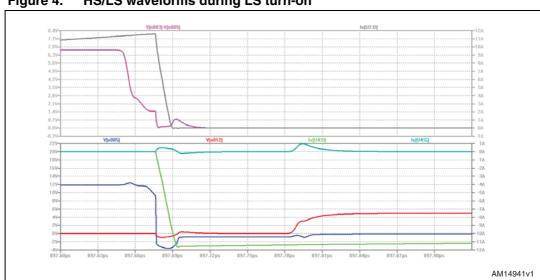

For reference, in *Figure 4* the relevant waveforms for the LS turn-on process are reported.

Figure 4. HS/LS waveforms during LS turn-on

## 2 Synchronous buck converter testing demonstration board

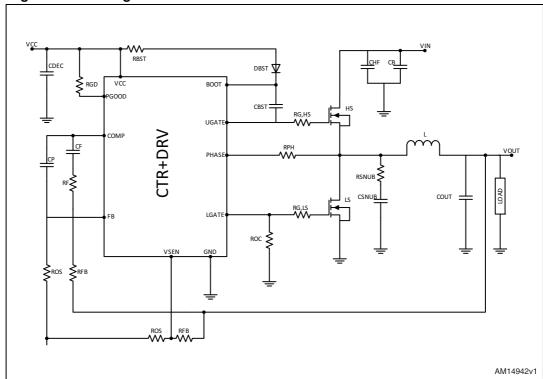

The test vehicle is a synchronous buck converter, which lowers the input voltage (12 V) in 1.25 V as output; the converter switching frequency is 300 kHz, fixed by an internal oscillator, while the maximum output current is 20 A.

Figure 5. Testing demonstration board schematic

The converter has a single device both for high-side and low-side positions. The Power MOSFET gate drive voltage is 12 V for both devices; HS and LS external gate resistances are  $2.2~\Omega$ .

The Power MOSFETs are driven by a single-phase PWM controller with integrated driver ( $I_{HS,SRC} = 2$  A,  $R_{HS,SINK} = 2$   $\Omega$   $I_{LS,SRC} = 3$  A,  $R_{LS,SINK} = 1$   $\Omega$ ). The controller shows very low LS sink resistance value in order to prevent any spurious gate-source bouncing and cross-conduction phenomenon during device turn-off.

The main advantage of this analysis is the availability of both the physical board and the full Cadence OrCAD Capture model of the converter (including driver and Power MOSFETs). Based on the same schematic, with identical passive and semiconductor devices, it is possible to use the converter Cadence OrCAD Capture model for testing various operating conditions, validating and explaining the experimental results. Moreover, the simulation data are very helpful to evaluate the Power MOSFET currents (especially drain current), as in the real board they cannot be measured easily by standard current probes, due to SMD packages and high switching frequency.

8/20 Doc ID 023526 Rev 1

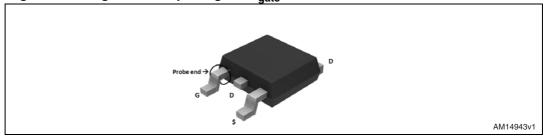

To overcome these difficulties, in the real board, the Power MOSFET gate current measurement is made by using a "Rogowski coil" current probe (CWT ultra mini), properly connected to the Power MOSFET gate pin. The features of this device are interesting, because it is flexible and open-ended and can be wrapped around a conductor without disturbing it. Moreover, it is able to respond correctly to fast-changing currents and it is highly linear even at very high current levels.

In *Figure 6*, the Rogowski coil probe end placing on a Power MOSFET DPAK gate pin is shown.

Figure 6. Rogowski coil package for Iqate measurement

#### 2.1 Power MOSFET selection for comparative tests

The aim of this document is to evaluate and explain the MOSFET technology gate current relationship; the analysis starts by choosing two different low-side devices, with the same die size, to be tested on the board:

- a) Device A "planar" technology

- b) Device B "trench" technology

All the devices are 30 V logic level FETs (1 V <  $V_{th}$  < 2.5 V). In the following table, the main Power MOSFET dynamic parameters (intrinsic capacitances and resistances) are reported:

Table 1. Power MOSFET electrical parameters

| Device | Q <sub>G</sub> @ 4.5 V<br>(nC) | Q <sub>GS</sub><br>(nC) | Q <sub>GD</sub><br>(nC) | Ciss @ 25 V | Crss @ 25 V | Coss @ 25 V | R <sub>G</sub><br>(Ω) |

|--------|--------------------------------|-------------------------|-------------------------|-------------|-------------|-------------|-----------------------|

| Α      | 14                             | 6.8                     | 4.7                     | 1850        | 58          | 380         | 1.2                   |

| В      | 20                             | 8.2                     | 7.5                     | 2200        | 280         | 400         | 1.1                   |

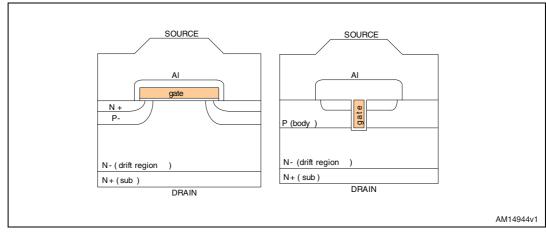

Figure 7 gives the cross sections of the two above mentioned devices.

Figure 7. Device A (left) and device B (right) cross sections

In a Power MOSFET with planar technology, the gate structure is on the device surface, realized by a planar poly-silicon electrode, a gate oxide layer and the silicon; these three layers form the "MOS" capacitor. The gate oxide isolates the metal contact and its thickness is in the range of a few or several hundreds of angstroms. The drain current flows from the source (n+region), through the conductive channel, in the vertical direction to the drain.

Considering now the trench technology, some relevant differences are immediately visible. The gate structure is realized by a deeply dug poly-silicon electrode (highly doped), isolated by a gate oxide layer. The trench depth is one of the most important process parameters, affecting device static ( $R_{DS(on)}$ ) and dynamic ( $Q_{GD}$ ) performance (it can vary in the range 1-2 µm). The drain current flows vertically along the trench sidewall towards the drain contact.

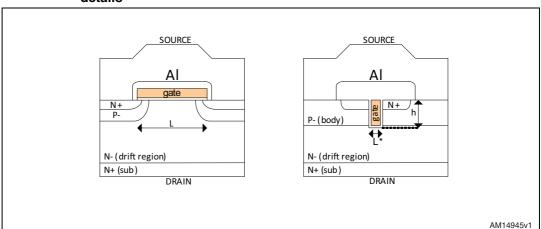

*Figure 8* shows the same device structures highlighting the geometrical aspects that affect the Power MOSFET switching performance.

Figure 8. Device A (left) and device B (right) cross sections with geometrical details

10/20 Doc ID 023526 Rev 1

For a planar structure, L is the gate electrode width while the pitch is the cell-to-cell distance. In a trench device, L\* is the trench width and h is the trench depth.  $Q_g/A$  (gate charge per area) links the Power MOSFET dynamic performance to the device geometry, providing a good tool for a technology comparison:

#### **Equation 3**

$$\frac{Q_g}{A} \propto \frac{L}{(pitch)_A}$$

#### **Equation 4**

$$\frac{Q_g}{A} \propto \frac{L^*\!\!+ 2h}{(pitch)_A}$$

*Equation 3* is valid for a planar device, while *4* is valid for trench. For modern silicon technology, the following considerations are valid:

#### **Equation 5**

L\*<< 2 h

#### **Equation 6**

L < 2h

So, merging Equation 3, 4, 5 and 6 and considering that (pitch)A > (pitch)B:

#### **Equation 7**

$$\left(\frac{Q_g}{A}\right) < \left(\frac{Q_g}{A}\right)_{trench}$$

#### **Equation 8**

$$\left(\frac{C_{xx}}{A}\right)_{planar} \left(\frac{C_{xx}}{A}\right)_{trench}$$

In other words, the intrinsic capacitive contribution of planar technology is lower than that of trench. This is of basic importance when the system/application requires switching performance improvement.

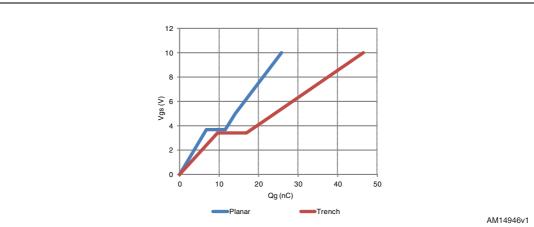

The specific capacitance difference between devices A and B shown in *Figure 8* is reflected into dissimilar gate charge curves: all the components of the gate charge are much larger for dev.B (red curve).

Figure 9. Gate charge comparison

#### 3 Bench tests and simulation results overview

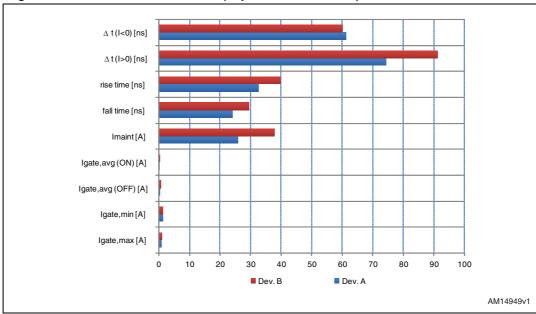

By an external DC electronic load, the converter output current is fixed at I<sub>OUT</sub> = 15 A. Low-side turn-on and turn-off transients are captured. For a complete comparison in terms of gate current performance, the following parameters are measured for both devices:

- I<sub>gate,max</sub>: maximum peak during turn-on;

- I<sub>gate,min</sub>: minimum value during turn-off;

- Δt(I>0): time interval duration with Igate > 0;

- $\Delta t(I<0)$ : time interval duration with Igate < 0;

- I<sub>gate,avg(ON)</sub>: average gate current during turn-on;

- I<sub>gate,avg(OFF)</sub>: average gate current during turn-off;

- I<sub>maint</sub>: gate current value when the device is fully ON;

- t<sub>f</sub>: low-side V<sub>GS</sub> fall time, measured from 90% to 10% of V<sub>GS</sub>;

- t<sub>r</sub>: low-side V<sub>GS</sub> rise time, measured from 10% to 90% of V<sub>GS</sub>.

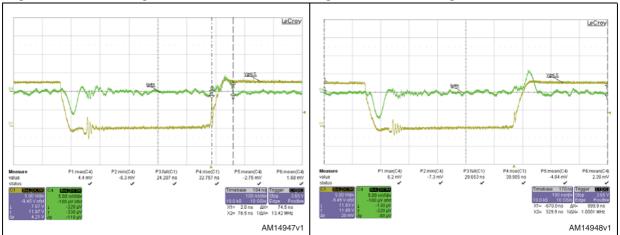

In *Figure 10* and *Figure 11* the low-side waveforms for device A and device B, respectively, are reported; the green trace is the LS gate current (1 A/div) whereas the yellow trace is  $V_{GS,LS}$  (5 V/div).

Figure 10. Device A gate waveforms

In the above images the turn-on and turn-off transients are clearly visible, with the relative gate current. During low-side turn-off, the gate current is negative, sunk by the driver to discharge Power MOSFET intrinsic capacitance. On the other hand, a positive gate current is needed to provide the right  $Q_G$  (total gate charge) to fully turn on the FET.

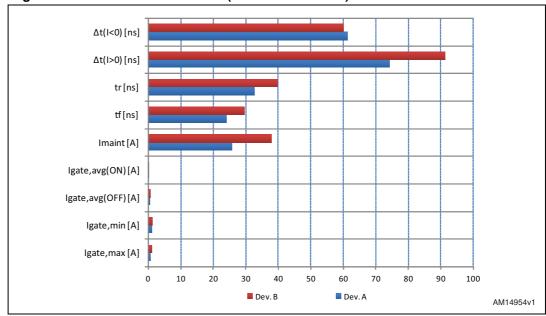

The following chart summarizes the parameter measurements performed on device A and device B:

Figure 12. Device A vs. device B (experimental results)

In Table 2 the percentage variations (device B vs. device A) of the measured parameters are reported and defined as:

$$\Delta(\text{parameter})_{\text{B-A}} = \frac{(\text{parameter})_{\text{B}} - (\text{parameter})_{\text{A}}}{(\text{parameter})_{\text{B}}}$$

| Table 2. | Percentage  | variation | (experimental  | requite)  |

|----------|-------------|-----------|----------------|-----------|

| iabie 2. | reiceillage | variation | (EXPELILIELLA) | i Couito, |

|                                  | Device B vs. device A |

|----------------------------------|-----------------------|

| ΔI <sub>gate, max</sub> (A)      | 29.03%                |

| ΔI <sub>gate, min</sub> (A)      | 13.70%                |

| ΔI <sub>gate, avg(OFF)</sub> (A) | 31.93%                |

| ΔI <sub>gate, avg(ON)</sub> (A)  | 29.41%                |

| ΔI <sub>maint</sub> (A)          | 31.58%                |

| $\Delta t_{\mathrm{f}}$ (ns)     | 18.24%                |

| $\Delta t_r$ (ns)                | 18.05%                |

| $\Delta t_{(I>0)}$ (ns)          | 18.49%                |

| $\Delta t_{(I<0)}$ (ns)          | -2.16%                |

As shown in Figure 12 and Table 2, device B shows higher values for almost all measured parameters; in particular, the gap becomes wide for maximum peak, average values at turnon and off and maintenance current.

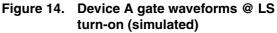

Consider now the Cadence OrCAD Capture simulator, performing a transient analysis to capture LS waveforms, at a fixed output current level ( $I_{OUT} = 15 \text{ A}$ ). In *Figure 13* and *Figure 14* device A low-side gate signals are shown:

Figure 13. Device A gate waveforms @ LS turn-off (simulated)

The red trace is the LS gate-source signal, while the green trace is the Power MOSFET gate current.

Comparing *Figure 10*, *Figure 13* and *Figure 14*, it is noticeable that the good accuracy of simulation results matches well with experimental ones in terms of waveform behavior.

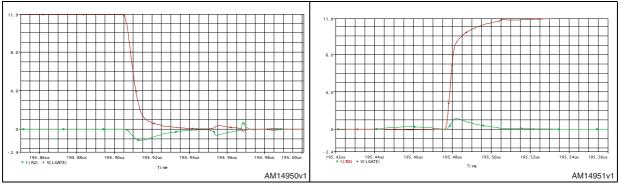

In Figure 15 and Figure 16 the LS turn-off and on waveforms of device B are reported:

Figure 15. Device B gate waveforms @ LS turn-off (simulated)

Figure 16. Device B gate waveforms @ LS turn-on (simulated)

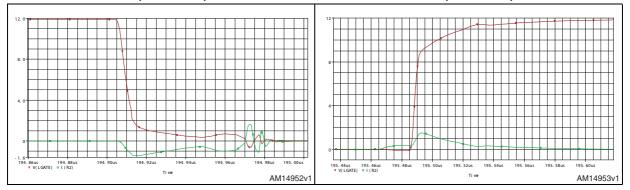

Finally, in *Figure 17* the measurements given by Cadence OrCAD Capture simulations are shown. Experimental and simulation results are strictly aligned; in fact, comparing *Figure 13* - *Figure 15* - *Figure 16*, some important observations can be made:

- Device B shows higher maximum and minimum gate current peaks, as reported in Table 3:

- b) Device B LS gate waveforms have slower rising and falling edges, with consequently longer rise and fall times;

- c) Device B gate current, at device turn-on, shows much higher peak and stays above the zero level for a longer time than device A.

Figure 17. Device A vs. device B (simulation results)

Starting from the simulation results, *Table 3* reports the switching parameters' percentage variations:

Table 3.

Percentage variation (simulation results)

|                             | Device B vs. device A |

|-----------------------------|-----------------------|

| ΔI <sub>gate, max</sub> (A) | 30.43%                |

| ΔI <sub>gate, min</sub> (A) | 18.75%                |

| $\Delta t_{f}$ (ns)         | 15.38%                |

| $\Delta t_r$ (ns)           | 28.57%                |

| $\Delta t_{(I>0)}$ (ns)     | 57.82%                |

| $\Delta t_{(I<0)}$ (ns)     | 7.10%                 |

*Table 2* and *Table 3* give very good matching between experimental and simulation results, particularly for  $I_{gate,max}$  and  $I_{gate,min}$  (maximum and minimum gate current) and for  $V_{GS}$  fall time. Furthermore, the trend is confirmed also for the other switching values.

AN4150 Conclusion

#### 4 Conclusion

These different device characteristics should be monitored particularly when application features (switching frequency, number of paralleled devices, etc....) are more critical for switching behavior, making driver-MOSFET matching optimization mandatory.

Two examples can be given to enforce the previous statements. When more FETs are paralleled, to minimize the overall  $R_{DS(on)}$  and the conduction losses, the driver must charge and discharge a bigger equivalent capacitance to switch on and off the devices. So, to minimize the gate drive losses, the driver must have special features, in terms of sink/source current and resistance, particularly when driving trench Power MOSFETs.

Similarly, in hard-switching applications, where larger losses occur during switching transients, proper driver choice is needed when higher (Cxx/A) Power MOSFETs must be turned on and off, improving gate current source and sink and reducing the switching losses.

References AN4150

## 5 References

- Power Electronics Handbook, M. H. Rashid, 2001

- Fundamentals of Power Electronics, R. W. Erickson, 2000

AN4150 Revision history

## 6 Revision history

Table 4. Document revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 12-Oct-2012 | 1        | Initial release. |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY TWO AUTHORIZED ST REPRESENTATIVES, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2012 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

20/20 Doc ID 023526 Rev 1