# RoHS Recast Compliant

# **Serial ATA Flash Drive**

mSATA M4 Product Specifications

**April 22<sup>nd</sup>, 2013**

Version 1.8

### Apacer Technology Inc.

4<sup>th</sup> Fl., 75 Hsin Tai Wu Rd., Sec.1, Xizhi, New Taipei City, Taiwan 221 Tel: +886-2-2698-2888 Fax: +886-2-2698-2889 www.apacer.com

### **Features:**

- Standard Serial ATA 2.6 (Gen. 2)

- Serial ATA 2.6 (Gen. 2)

- SATA II, 3.0 Gbps

- ATA-compatible command set

- ATA modes support

- Capacities

- 4, 8, 16, 32, 64 GB

- Performance\*

- Burst read/write: 300 MB/sec

- Sustained read: up to 165 MB/sec

- Sustained write: up to 150 MB/sec

- Intelligent endurance design

- Built-in hardware ECC, enabling up to 16/24 bit correction per 1K bytes

- Static wear-leveling scheme together with dynamical block allocation to significantly increase the lifetime of a flash device and optimize the disk performance

- Flash bad-block management

- S.M.A.R.T.

- Power Failure Management

- ATA Secure Erase

- TRIM

- NAND Flash Type: SLC

- MTBF > 2,000,000 hours

#### Temperature ranges

- Operation: 0 °C to 70 °C (32 ~ 158 °F)

- Extended: -40 °C to 85 °C (-40 ° ~ 185 °F)

- Storage: -40 °C to 100 °C (-40 ° ~ 212 °F)

- Endurance: 192 TBW (4GB), 384 TBW (8GB), 769 TBW (16GB), 1539 TBW (32GB), 3078 TBW (64GB)

- Supply voltage

- $-3.3V \pm 5\%$

- Power consumption (typical)\*

- Active mode: 490 mAIdle mode: 150 mA

- Form factor

- Mini PCle form factor (50.8 x 29.85 x 3.40, unit: mm)

- JEDEC MO-300 compliant

- Connector

- 52-pin mSATA connector

- Shock & Vibration\*\*

- Shock: 1500 GVibration: 15 G

- RoHS Recast compliant (2011/65/EU standard)

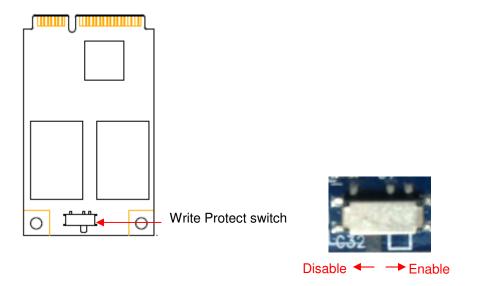

- Write Protect enabled by pin configuration\*\*\*

- Write Protect switch (optional)

- Enabled by onboard hardware switch

<sup>\*</sup>Varies from capacities. The values addressed here are typical and may vary depending on settings and platforms.

\*\*Non-operating

<sup>\*\*\*</sup>Write Protect can be enabled by pin configuration in both standard model and switch-provided model. For more information, please refer to "Pin Assignments" and "Write Protect Enabled by Pin" sections

### **Table of Contents**

| 1. | Product Description                   | 3  |

|----|---------------------------------------|----|

|    | 1.1 Introduction                      | 3  |

|    | 1.2 Functional Block Diagram          | 3  |

|    | 1.3 ATA Mode Support                  | 4  |

|    | 1.4 Capacity Specification            | 4  |

|    | 1.5 Performance                       | 4  |

|    | 1.6 Pin Assignments                   | 5  |

| 2. | Software Interface                    | 7  |

|    | 2.1 Command Set                       | 7  |

| 3. | Flash Management                      | 8  |

|    | 3.1 Error Correction/Detection        | 8  |

|    | 3.2 Bad Block Management              | 8  |

|    | 3.3 Wear Leveling                     | 8  |

|    | 3.4 Power Failure Management          | 8  |

|    | 3.5 ATA Secure Erase                  | 8  |

|    | 3.6 S.M.A.R.T.                        | 9  |

|    | 3.7 TRIM                              | 9  |

| 4. | Environmental Specifications          | 10 |

|    | 4.1 Environments                      | 10 |

|    | 4.2 Mean Time Between Failures (MTBF) | 10 |

|    | 4.3 Certification and Compliance      | 10 |

|    | 4.4 Endurance                         | 10 |

| 5. | Electrical Characteristics            | 12 |

|    | 5.1 Operating Voltage                 | 12 |

|    | 5.2 Power Consumption                 | 12 |

| 6. | Physical Characteristics              | 13 |

|    | 6.1 Mechanical Drawing                | 13 |

|    | 6.2 Write Protect Switch (optional)   | 14 |

| 7. | Write Protect Enabled by Pin          | 15 |

| 8. | Product Ordering Information          | 16 |

|    | 8.1 Product Code Designations         | 16 |

|    | 8.2 Valid Combinations                | 17 |

# 1. Product Description

#### 1.1 Introduction

Apacer's mSATA M4 is a solid-state disk (SSD) drive in mini PCIe form factor that contains a controller, embedded firmware, and flash media along with a male connector. mSATA M4 leverages the advantages of standard SATA SSDs in terms of wide compatibilities and reliable performance.

mSATA M4 drive is designed with a single-chip controller, offering capacities of up to 64 gigabytes and is compliant with the SATA  $\scriptstyle II$  high-speed interface standard. Complying with JEDEC MO-300 standard, this mSATA SSD is the widely adopted embedded storage with compact size and exceptional performance.

In addition, mSATA M4 adopts the Apacer-specific global wear-leveling scheme to allow uniform use of all storage blocks, ensuring that the lifespan of a flash media can be significantly increased and the disk performance is optimized as well. mSATA M4 provides the S.M.A.R.T. feature that follows the SATA Rev. 2.6, ATA/ATAPI-7 specifications and uses the standard SMART command B0h to read data from the drive. This feature protects the user from unscheduled downtime by monitoring and storing critical drive performance.

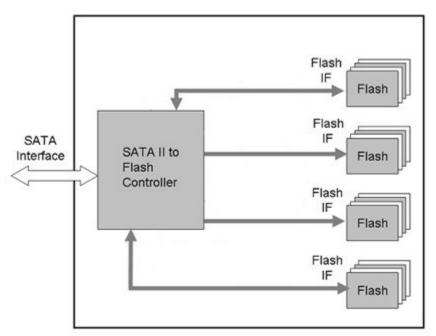

### 1.2 Functional Block Diagram

mSATA M4 drive includes a single-chip SATA II Controller and the flash media, as well as the SATA standard interface. The controller integrates the flash management unit with the controller itself to support multi-channel, multi-bank flash arrays. Figure 1-1 shows the functional block diagram.

Figure 1-1 Apacer mSATA M4 block diagram

## 1.3 ATA Mode Support

mSATA M4 provides ATA mode support as follows:

- Up to PIO mode-4

- Up to Multiword DMA mode-2

- Up to UDMA mode-5

### 1.4 Capacity Specification

Capacity specification of mSATA M4 product family is available as shown in Table 1-1. It lists the specific capacity, the default numbers of logical cylinders and heads, and the number of logical sectors per track for each product line.

Table 1-1 Capacity specification

| Capacity | Total Bytes*   | Cylinders | Heads | Sectors | Max LBA*    |

|----------|----------------|-----------|-------|---------|-------------|

| 4 GB     | 4,011,614,208  | 7773      | 16    | 63      | 7,835,184   |

| 8 GB     | 8,012,390,400  | 15525     | 16    | 63      | 15,649,200  |

| 16 GB    | 16,013,942,784 | 16383     | 16    | 63      | 31,277,232  |

| 32 GB    | 32,017,047,552 | 16383     | 16    | 63      | 62,533,296  |

| 64 GB    | 64,023,257,088 | 16383     | 16    | 63      | 125,045,424 |

<sup>\*</sup>Display of total bytes varies from file systems.

LBA count addressed in the table above indicates total user storage capacity and will remain the same throughout the lifespan of the device. However, the total usable capacity of the SSD is most likely to be less than the total physical capacity because a small portion of the capacity is reserved for device maintenance usages.

#### 1.5 Performance

Performance of mSATA M4 is shown in Table 1-2.

Table 1-2 Performance specifications

| Performance Capacity   | 4 GB | 8 GB | 16 GB | 32 GB | 64 GB |

|------------------------|------|------|-------|-------|-------|

| Sustained Read (MB/s)  | 145  | 155  | 155   | 160   | 165   |

| Sustained Write (MB/s) | 50   | 105  | 105   | 145   | 150   |

Note: Performance varies from flash configurations and/or platform settings.

<sup>\*\*</sup>Cylinders, heads or sectors are not applicable for these capacities. Only LBA addressing applies.

<sup>\*\*</sup>Notes: 1 GB = 1,000,000,000 bytes; 1 sector = 512 bytes.

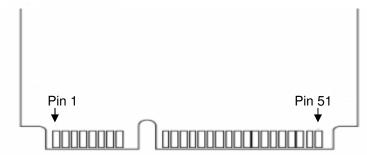

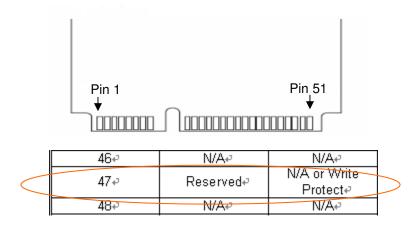

# 1.6 Pin Assignments

in assignment of the mSATA M4 is shown in Figure 1-2 and described in Table 1-3.

Figure 1-2 Apacer mSATA M4 pin assignment

Table 1-3 Pin Assignment Description

| Pin # | Assignment | Description         | Pin # | Assignment            | Description                                          |

|-------|------------|---------------------|-------|-----------------------|------------------------------------------------------|

| 1     | N/A        | N/A                 | 27    | GND                   | Return Current Path                                  |

| 2     | +3.3V      | 3.3V source         | 28    | N/A                   | N/A                                                  |

| 3     | N/A        | N/A                 | 29    | GND                   | Return Current Path                                  |

| 4     | GND        | Return Current Path | 30    | N/A                   | N/A                                                  |

| 5     | N/A        | N/A                 | 31    | Rx-                   | SATA Differential                                    |

| 6     | N/A        | N/A                 | 32    | N/A                   | N/A                                                  |

| 7     | N/A        | N/A                 | 33    | Rx+                   | SATA Differential                                    |

| 8     | N/A        | N/A                 | 34    | GND                   | Return Current Path                                  |

| 9     | GND        | Return Current Path | 35    | GND                   | Return Current Path                                  |

| 10    | N/A        | N/A                 | 36    | Reserved              | No Connect                                           |

| 11    | N/A        | N/A                 | 37    | GND                   | Return Current Path                                  |

| 12    | N/A        | N/A                 | 38    | Reserved              | No Connect                                           |

| 13    | N/A        | N/A                 | 39    | +3.3V                 | 3.3V source                                          |

| 14    | N/A        | N/A                 | 40    | GND                   | Return Current Path                                  |

| 15    | GND        | Return Current Path | 41    | +3.3V                 | 3.3V source                                          |

| 16    | N/A        | N/A                 | 42    | N/A                   | N/A                                                  |

| 17    | N/A        | N/A                 | 43    | GND                   | Return Current Path                                  |

| 18    | GND        | Return Current Path | 44    | N/A                   | N/A                                                  |

| 19    | N/A        | N/A                 | 45    | Reserved              | N/A                                                  |

| 20    | N/A        | N/A                 | 46    | N/A                   | N/A                                                  |

| 21    | GND        | Return Current Path | 47    | Reserved              | N/A or Write<br>Protect                              |

| 22    | N/A        | N/A                 | 48    | N/A                   | N/A                                                  |

| 23    | Tx+        | SATA Differential   | 49    | DA/DSS                | Device Activity /<br>Disable<br>Staggered Spin<br>Up |

| 24    | +3.3V      | 3.3V source         | 50    | GND                   | Return Current Path                                  |

| 25    | Тх-        | SATA Differential   | 51    | Presence<br>Detection | Shall be pulled<br>to GND by<br>device               |

| 26    | GND        | Return Current Path | 52    | +3.3V                 | 3.3V source                                          |

Notes: Pin47 is N/A by default with high impedance. However, the pin is internally programmed with Write Protect function. If the pin signal is pulled to "low", Write Protect will be triggered. This pin configured Write Protect is available in both the standard and the model with a hardware switch. There is no functional conflict between the pin-configured and the switch-enabled Write Protect as both adopt the same GPIO pin in the hardware and firmware design.

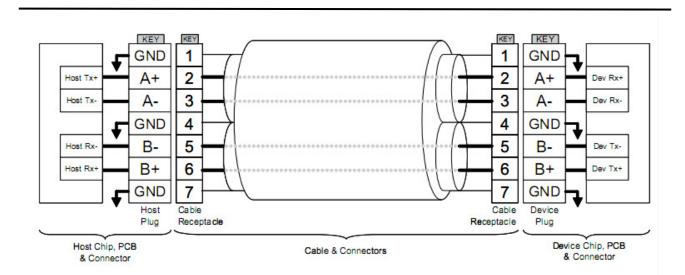

Figure 1-3 SATA Cable/Connector Connection Diagram

The connector on the left represents the Host with TX/RX differential pairs connected to a cable. The connector on the right shows the Device with TX/RX differential pairs also connected to the cable. Notice also the ground path connecting the shielding of the cable to the Cable Receptacle.

# 2. Software Interface

### 2.1 Command Set

Table 2-1 summarizes the ATA commands supported by mSATA M4.

Table 2-1: Command set

| Code | Command                      | Code | Command                |

|------|------------------------------|------|------------------------|

| E5h  | Check Power Mode             | F3h  | Security Erase Prepare |

| 06h  | Data Set Management          | F4h  | Security Erase Unit    |

| 90h  | Execute Device Diagnostic    | F5h  | Security Freeze Lock   |

| E7h  | Flush Cache                  | F1h  | Security Set Password  |

| EAh  | Flush Cache EXT              | F2h  | Security Unlock        |

| Ech  | Identify Device              | 70h  | Seek                   |

| E3h  | Idle                         | Efh  | Set Features           |

| E1h  | Idle Immediate               | C6h  | Set Multiple Mode      |

| 91h  | Initialize Device Parameters | E6h  | Sleep                  |

| C8h  | Read DMA                     | B0h  | SMART                  |

| 25h  | Read DMA EXT                 | E2h  | Standby                |

| C4h  | Read Multiple                | E0h  | Standby Immediate      |

| 29h  | Read Multiple EXT            | Cah  | Write DMA              |

| 20h  | Read Sector                  | 35h  | Write DMA EXT          |

| 24h  | Read Sector EXT              | C5h  | Write Multiple         |

| 40h  | Read Verify Sectors          | 39h  | Write Multiple EXT     |

| 42h  | Read Verify Sectors EXT      | 30h  | Write Sector           |

| 10h  | Recalibrate                  | 34h  | Write Sector EXT       |

| F6h  | Security Disable Password    |      |                        |

# 3. Flash Management

#### 3.1 Error Correction/Detection

mSATA M4 implements a hardware ECC scheme, based on the BCH algorithm. It can detect and correct up to 16 bits or 24 bits error in 1K bytes.

### 3.2 Bad Block Management

Current production technology is unable to guarantee total reliability of NAND flash memory array. When a flash memory device leaves factory, it comes with a minimal number of initial bad blocks during production or out-of-factory as there is no currently known technology that produce flash chips free of bad blocks. In addition, bad blocks may develop during program/erase cycles. When host performs program/erase command on a block, bad block may appear in Status Register. Since bad blocks are inevitable, the solution is to keep them in control. Apacer flash devices are programmed with ECC, block mapping technique and S.M.A.R.T to reduce invalidity or error. Once bad blocks are detected, data in those blocks will be transferred to free blocks and error will be corrected by designated algorithms.

### 3.3 Wear Leveling

Flash memory devices differ from Hard Disk Drives (HDDs) in terms of how blocks are utilized. For HDDs, when a change is made to stored data, like erase or update, the controller mechanism on HDDs will perform overwrites on blocks. Unlike HDDs, flash blocks cannot be overwritten and each P/E cycle wears down the lifespan of blocks gradually. Repeatedly program/erase cycles performed on the same memory cells will eventually cause some blocks to age faster than others. This would bring flash storages to their end of service term sooner. Wear leveling is an important mechanism that level out the wearing of blocks so that the wearing-down of blocks can be almost evenly distributed. This will increase the lifespan of SSDs. Commonly used wear leveling types are Static and Dynamic.

# 3.4 Power Failure Management

Power Failure Management plays a crucial role when experiencing unstable power supply. Power disruption may occur when users are storing data into the SSD. In this urgent situation, the controller would run multiple write-to-flash cycles to store the metadata for later block rebuilding. This urgent operation requires about several milliseconds to get it done. At the next power up, the firmware will perform a status tracking to retrieve the mapping table and resume previously programmed NAND blocks to check if there is any incompleteness of transmission.

#### 3.5 ATA Secure Erase

ATA Secure Erase is an ATA disk purging command currently embedded in most of the storage drives. Defined in ATA specifications, (ATA) Secure Erase is part of Security Feature Set that allows storage drives to erase all user data areas. The erase process usually runs on the firmware level as most of the ATA-based storage media currently in the market are built-in with this command. ATA Secure Erase can securely wipe out the user data in the drive and protects it from malicious attack.

#### 3.6 S.M.A.R.T.

S.M.A.R.T. is an acronym for Self-Monitoring, Analysis and Reporting Technology, an open standard allowing disk drives to automatically monitor their own health and report potential problems. It protects the user from unscheduled downtime by monitoring and storing critical drive performance and calibration parameters. Ideally, this should allow taking proactive actions to prevent impending drive failure.

Apacer devices use the standard SMART command B0h to read data out from the drive to activate our SMART feature that complies with the ATA/ATAPI-7 specifications. Based on the SFF-8035i Rev. 2.0 specifications, SMART Attribute IDs shall include Initial bad block count, Bad block count, Spare block count, Maximum erase count, Average erase count and Power cycle. When the SMART Utility running on the host, it analyzes and reports the disk status to the host before the device reaches in critical condition.

#### **3.7 TRIM**

TRIM, though in capital letters usually, is a memory computation command rather than an abbreviation. It is mainly a SATA command that enables the operating system to inform the SSD (Solid State Drive) which blocks of previously stored data are no longer valid, due to erases by the host or operating system, such as file deletions or disk formatting. Once notified, SSD will begin the discard of the invalid LBAs and retain more space for itself, in fact, the discarded is no longer recoverable.

When an LBA is replaced by the operating system, as with overwrite of a file, the SSD is informed that the originally occupied LBA is determined as no longer in use or invalid. The SSD will not save those blocks in garbage collected sectors. Noticeably, a file deletion command by host or operating system never actually erases the actual content, rather, just the file is marked as deleted. This issue is even specifically noticeable for flash based memory devices, such as SSDs. In fact, an SSD will keep garbage collecting the invalid, previously occupied LBAs, if it is not informed that these LBAs can be erased. Thus, the SSD would experience a significant performance downfall.

# 4. Environmental Specifications

#### 4.1 Environments

mSATA M4 environmental specifications follow the US Military Standard MIL-STD-810F, as shown in the following table.

Table 4-1 mSATA M4-M environmental specifications

| Environment  | Specification                                                                               |  |  |

|--------------|---------------------------------------------------------------------------------------------|--|--|

| Tamanayatıyı | 0°C to 70°C (Operating), -40°C to 85°C (Extended)                                           |  |  |

| Temperature  | -40 ℃ to 100 ℃ (Non-operating)                                                              |  |  |

| Vibration    | Non-operating : Sine wave, 15(G), 10~2000(Hz), Operating : Random, 7.69 (Grms), 20~2000(Hz) |  |  |

| Shock        | Non-operating: Acceleration, 1,500 G, 0.5 ms<br>Operating: Peak acceleration, 50 G, 11 ms   |  |  |

# 4.2 Mean Time Between Failures (MTBF)

Mean Time Between Failures (MTBF) is predicted based on reliability data for the individual components in mSATA drive. The prediction result for the mSATA M4 is more than 2,000,000 hours.

Notes about MTBF:

The prediction is based on Bellcore analysis method by assuming device failure rate can be generated by the sum of failure rates in each component.

# 4.3 Certification and Compliance

mSATA M4 complies with the following standards:

- CE

- FCC

- RoHS Recast

- MIL-STD-810F

- SATA II (SATA Rev. 2.6)

- Up to ATA/ATAPI-7 (including S.M.A.R.T.)

#### 4.4 Endurance

Terabytes Written (TBW) is an endurance rating system that indicates the maximum number of terabytes written by the host to the drive. NAND flash has a limit on how many P/E cycles it can withstand before its data retention becomes unreliable. Thus, key factors, such as Write Amplifications and the number of P/E cycles, can influence the lifespan of the drive.

| Capacity | TBW (TB) |

|----------|----------|

| 4 GB     | 194      |

| 8 GB     | 384      |

| 16 GB | 769  |

|-------|------|

| 32 GB | 1539 |

| 64 GB | 3078 |

#### Notes:

- The measurement assumes the data written to the SSD for test is under a typical and constant rate. The measurement follows the standard metric: 1 TB (Terabyte) = 1000 GB.

# 5. Electrical Characteristics

# 5.1 Operating Voltage

Table 5-1 lists the supply voltage for mSATA M4.

Table 5-1 mSATA M4 operating voltage

| Parameter      | Conditions                 |  |  |

|----------------|----------------------------|--|--|

| Supply voltage | 3.3V ±5% (3.135 - 3.465 V) |  |  |

# **5.2 Power Consumption**

**Table 5-2** Power consumption (typical)

| Mode            | 4 GB | 8 GB | 16 GB | 32 GB | 64 GB |

|-----------------|------|------|-------|-------|-------|

| Active (mA)     | 395  | 430  | 490   | 450   | 480   |

| Standby<br>(mA) | 130  | 140  | 150   | 140   | 140   |

Note: Power consumption may vary from flash configurations and/or platform settings.

# **6. Physical Characteristics**

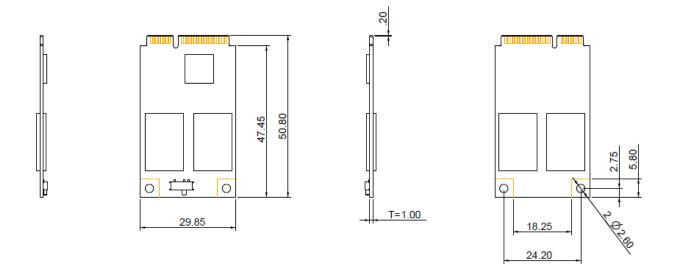

# 6.1 Mechanical Drawing

Unit: mm

Tolerance: ± 0.2

# 6.2 Write Protect Switch (optional)

#### Description of Apacer Write Protect:

To protect unauthorized data writes, Apacer implements Write Protect that functions as "Virtual Write" that allows write commands to go through the flash controller and data is temporarily stored. But since the process is "virtual", none of the data has been written to the flash. When the host resets or restarts the system, all the temporarily stored data will disappear. Since the Virtual Write scheme runs at device level, it requires no software or driver installation and is independent from the host OS.

# 7. Write Protect Enabled by Pin

The pin 47 can enable "Write Protect" function, no matter the standard model or the one with hardware switch. By default, the pin is set as "high" signal so that write operations can be performed normally. Once the signal is pulled to "low active", Write Protect will be activated. Regarding the Write Protect function, it is the same scheme implemented in our Write Protect switch.

The activation/deactivation of the pin-configured Write Protect function may require additional architectural design for the host system.

| GPIO Trigger  | Impedance Signal           |

|---------------|----------------------------|

| Write Protect | Low active since triggered |

Notes: Write Protect (Virtual Write) is a higher priority command than Erase or other erasure related commands. In other words, when Write Protect is activated, neither Erase nor other erasures can be activated.

This pin is available in both the standard and the model with the hardware switch. There is no functional conflict as both the pin-configured and the switch-enabled Write Protect adopt the same GPIO pin in its hardware and firmware design. If the Write Protect is activated by the pin, it will be deactivated by the pin as well. The following table lists out the Write Protect status corresponding to the enabling/disabling of the pin/switch.

| Switch status | Pin47 Signal | Write Protect status |

|---------------|--------------|----------------------|

| Disabled      | Enabled      | Enabled              |

| Enabled       | Disabled     | Enabled              |

| Disabled      | Disabled     | Disabled             |

| Enabled       | Enabled      | Enabled              |

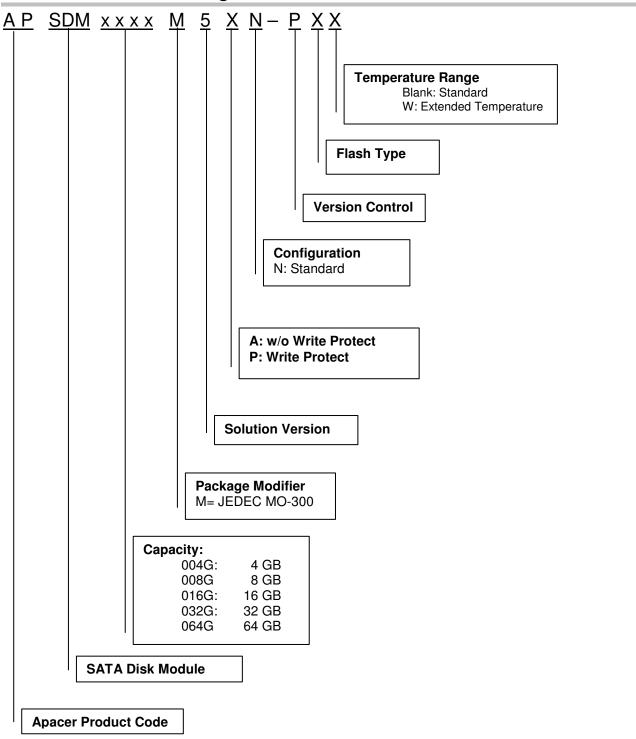

# **8. Product Ordering Information**

# 8.1 Product Code Designations

# 8.2 Valid Combinations

#### mSATA M4

| Capacity | Standard         | Extended Temperature |

|----------|------------------|----------------------|

| 4GB      | APSDM004GM5AN-PT | APSDM004GM5AN-PTW    |

| 8GB      | APSDM008GM5AN-PT | APSDM008GM5AN-PTW    |

| 16GB     | APSDM016GM5AN-PT | APSDM016GM5AN-PTW    |

| 32GB     | APSDM032GM5AN-PC | APSDM032GM5AN-PCW    |

| 64GB     | APSDM064GM5AN-PC | APSDM064GM5AN-PCW    |

#### mSATA M4 with Write Protect

| Capacity | Standard         | Extended Temperature |  |

|----------|------------------|----------------------|--|

| 4GB      | APSDM004GM5PN-PT | APSDM004GM5PN-PTW    |  |

| 8GB      | APSDM008GM5PN-PT | APSDM008GM5PN-PTW    |  |

| 16GB     | APSDM016GM5PN-PT | APSDM016GM5PN-PTW    |  |

| 32GB     | APSDM032GM5PN-PC | APSDM032GM5PN-PCW    |  |

| 64GB     | APSDM064GM5PN-PC | APSDM064GM5PN-PCW    |  |

Note: Please consult with Apacer sales representatives for availabilities.

# **Revision History**

| Revision | Description                                                                      | Date       |

|----------|----------------------------------------------------------------------------------|------------|

| 0.1      | Preliminary release                                                              | 11/07/2011 |

| 1.0      | Official release                                                                 | 12/02/2011 |

| 1.1      | Updated Electrical Specification and supply voltage information: from 5V to 3.3V | 1/2/2012   |

| 1.2      | Revised capacity information                                                     | 1/16/2012  |

| 1.3      | Added Endurance and Random Read/Write sections                                   | 05/04/2012 |

| 1.4      | Revised mechanical drawing                                                       | 08/15/2012 |

|          | Updated Product Ordering Information due to firmware upgrade                     |            |

| 1.5      | Added Write Protect option                                                       | 11/08/2012 |

| 1.6      | Added Write Protect information in pin assignment and created a chapter for it   | 12/21/2012 |

| 1.7      | Updated Product Ordering Information due to firmware upgrade                     | 03/12/2013 |

| 1.8      | Modified endurance TBW values due to firmware change                             | 04/22/2013 |

# **Global Presence**

Taiwan (Headquarters) Apacer Technology Inc.

4<sup>th</sup> Fl., 75 Hsin Tai Wu Rd., Sec.1

Xizhi, New Taipei City

Taiwan 221 R.O.C.

Tel: +886-2-2698-2888 Fax: +886-2-2698-2889 amtsales@apacer.com

U.S.A. Apacer Memory America, Inc.

386 Fairview Way, Suite102,

Milpitas, CA 95035 Tel: 1-408-518-8699 Fax: 1-408-935-9611 sa@apacerus.com

Japan Apacer Technology Corp.

5F, Matsura Bldg., Shiba, Minato-Ku

Tokyo, 105-0014, Japan Tel: 81-3-5419-2668 Fax: 81-3-5419-0018 jpservices@apacer.com

Europe Apacer Technology B.V.

Science Park Eindhoven 5051 5692 EB Son,

The Netherlands Tel: 31-40-267-0000 Fax: 31-40-267-0000#6199

sales@apacer.nl

China Apacer Electronic (Shanghai) Co., Ltd

1301, No.251, Xiaomuqiao Road, Shanghai,

200032, China

Tel: 86-21-5529-0222 Fax: 86-21-5206-6939 sales@apacer.com.cn

India Apacer Technologies Pvt Ltd,

# 535, 1st Floor, 8th cross, JP Nagar 3rd Phase,

Bangalore – 560078, India Tel: 91-80-4152-9061 sales india@apacer.com