# Low-Power, Stereo Audio Codec with FlexSound Technology

### **General Description**

### **Features**

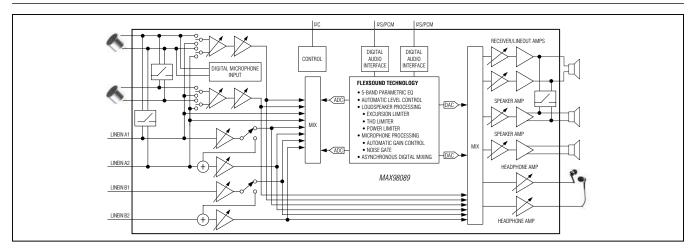

The MAX98089 is a full-featured audio codec whose high performance and low power consumption make it ideal for portable applications.

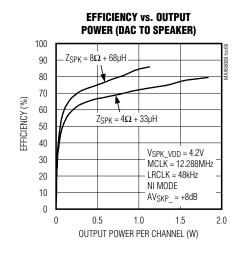

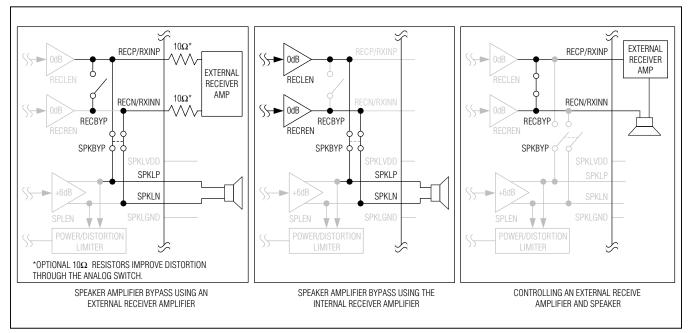

Class D speaker amplifiers provide efficient amplification for two speakers. Low radiated emissions enable completely filterless operation. Integrated bypass switches optionally connect an external amplifier to the transducer when the Class D amplifiers are disabled.

The IC features a stereo Class H headphone amplifier that utilizes a dual-mode charge pump to maximize efficiency while outputting a ground referenced signal that does not require output coupling capacitors.

The IC also features a mono differential amplifier that can also be configured as a stereo line output.

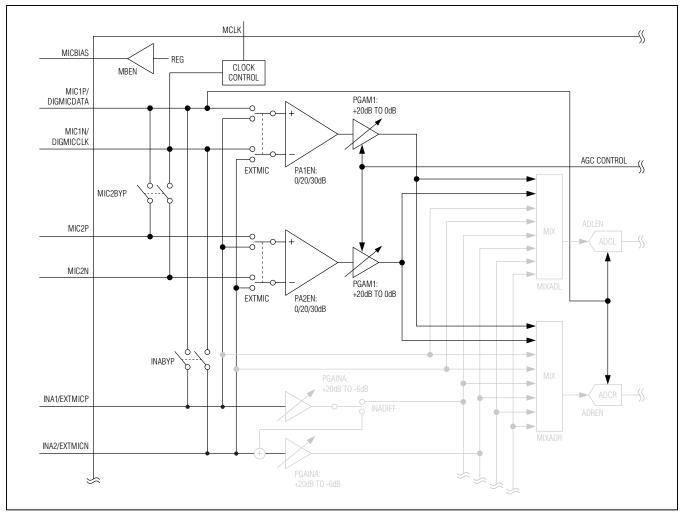

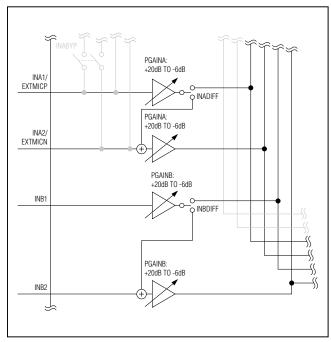

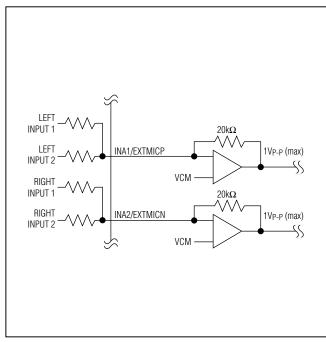

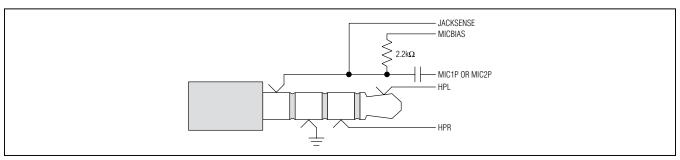

Two differential analog microphone inputs are available as well as support for two PDM digital microphones. Integrated switches allow for an additional microphone input as well as microphone signals to be routed out to external devices. Two flexible single-ended or differential line inputs may be connected to an FM radio or other sources.

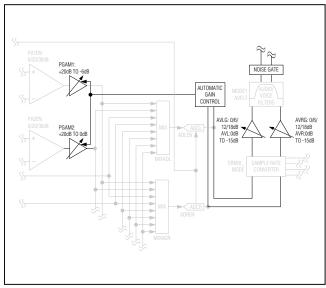

Integrated FlexSound™ technology improves loudspeaker performance by optimizing the signal level and frequency response while limiting the maximum distortion and power at the output to prevent speaker damage. Automatic gain control (AGC) and a noise gate optimize the signal level of microphone input signals to make best use of the ADC dynamic range.

The device is fully specified over the -40°C to +85°C extended temperature range.

FlexSound is a trademark of Maxim Integrated Products, Inc.

- ♦ 5.6mW Power Comsumption (DAC to HP at 97dB DR)

- ♦ 101dB DR Stereo DAC (8kHz < fs < 96kHz)

</p>

- ♦ 93dB DR Stereo ADC (8kHz < fs < 96kHz)

- ♦ Stereo Low EMI Class D Amplifiers 1.7W/Channel (8Ω, VSPK\_VDD = 5.0V) 2.9W/Channel (4Ω, VSPK\_VDD = 5.0V)

- **♦** Efficient Class H Headphone Amplifier

- ♦ Differential Receiver Amplifier/Stereo Line Outputs

- ♦ 2 Stereo Single-Ended/Mono Differential Line Inputs

- **♦** 3 Differential Microphone Inputs

- ♦ FlexSound Technology

5-Band Parametric EQ

Automatic Level Control (ALC)

Excursion Limiter

Speaker Power Limiter

Speaker Distortion Limiter

Microphone Automatic Gain Control

and Noise Gate

- ♦ Dual I2S/PCM/TDM Digital Audio Interfaces

- **♦** Asynchronous Digital Mixing

- ♦ Supports Master Clock Frequencies from 10MHz to 60MHz

- **♦ RF Immune Analog Inputs and Outputs**

- **♦** Extensive Click-and-Pop Reduction Circuitry

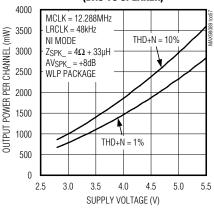

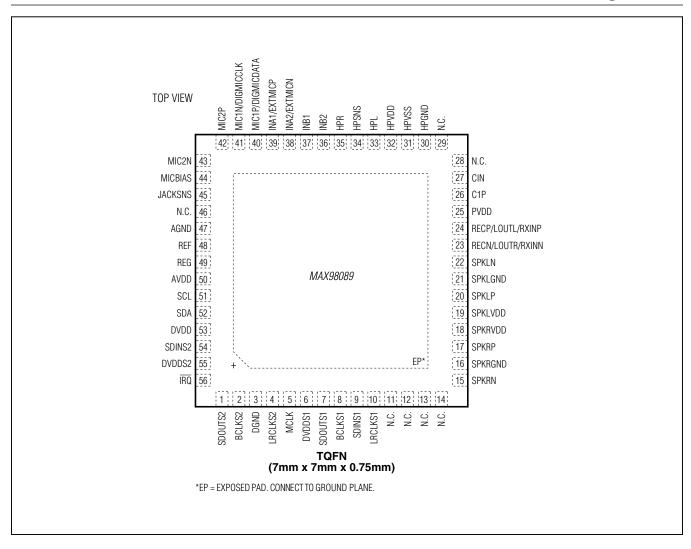

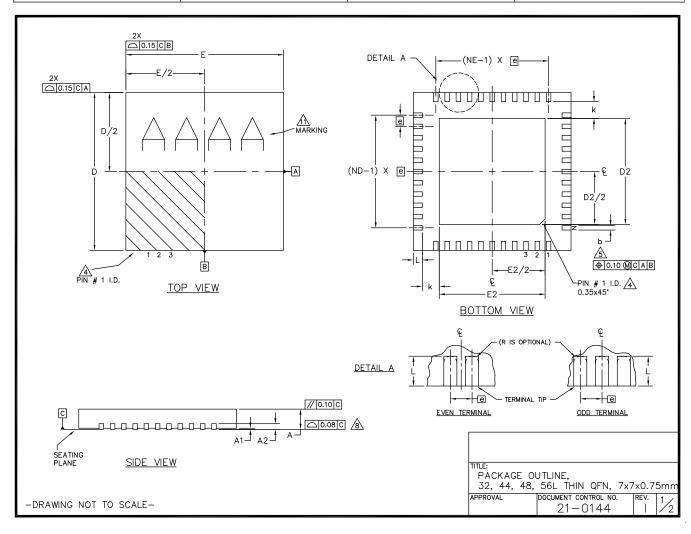

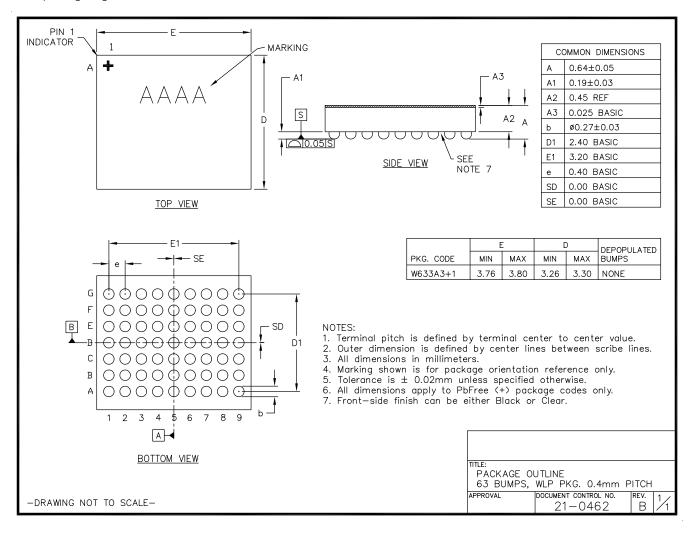

- ◆ Available in 63-Bump WLP Package (3.80mm x 3.30mm, 0.4mm Pitch) and 56-Pin TQFN Package (7mm x 7mm x 0.75mm)

Ordering Information appears at end of data sheet.

For related parts and recommended products to use with this part, refer to <a href="https://www.maxim-ic.com/MAX98089.related">www.maxim-ic.com/MAX98089.related</a>.

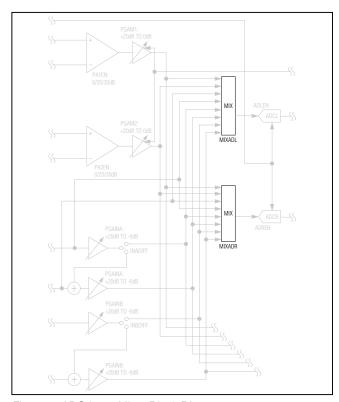

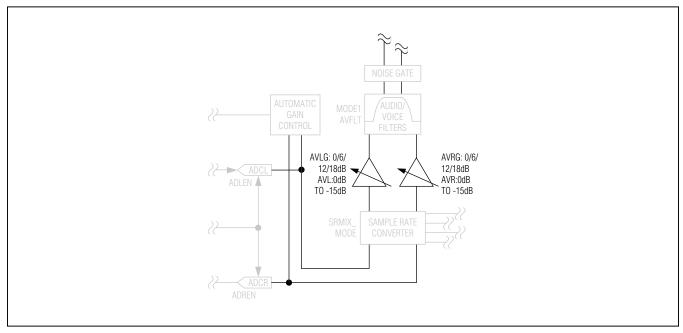

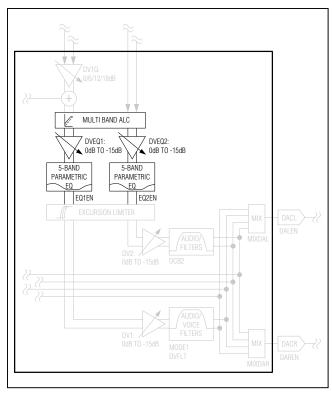

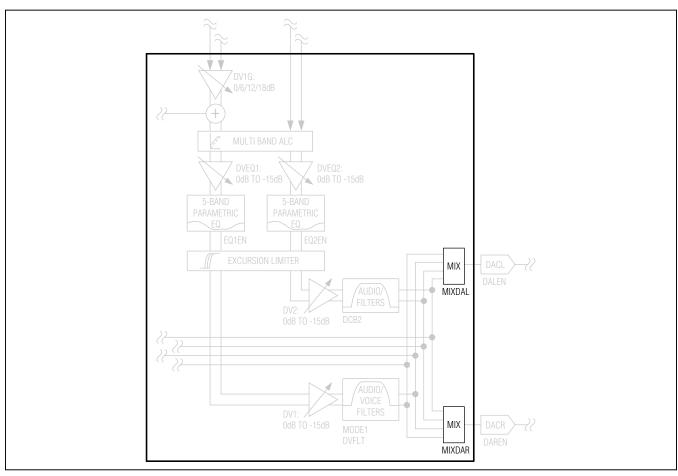

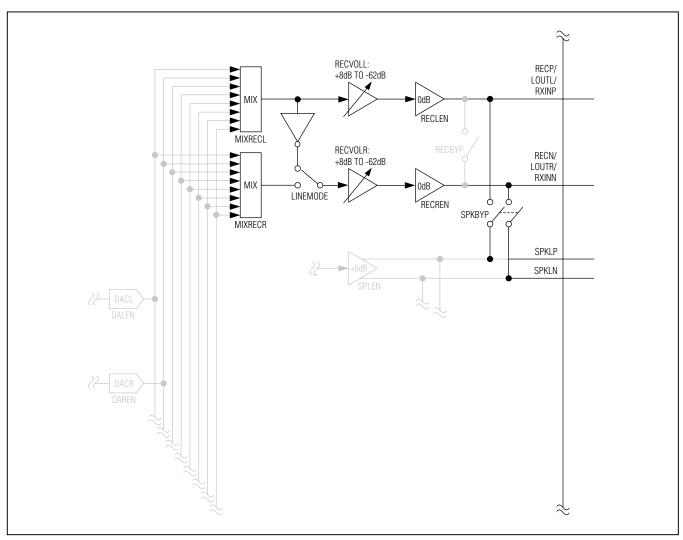

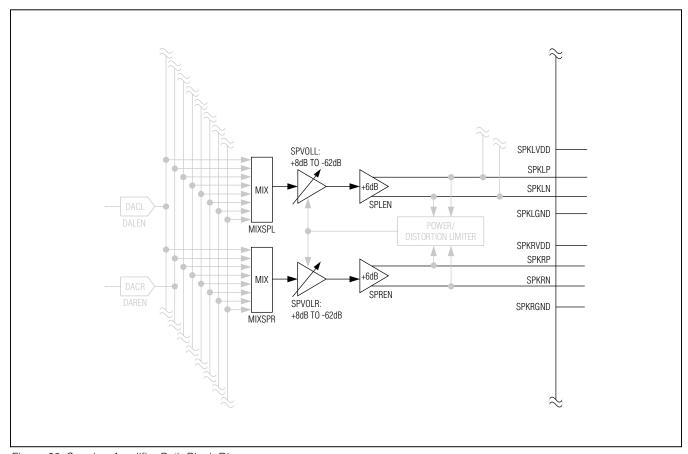

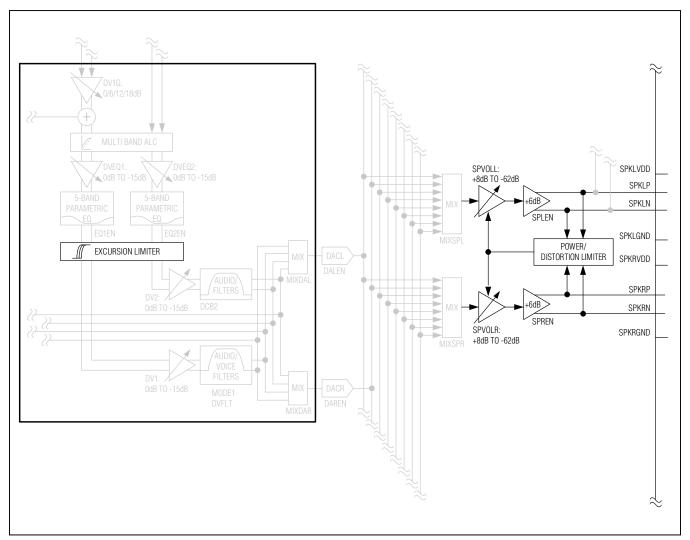

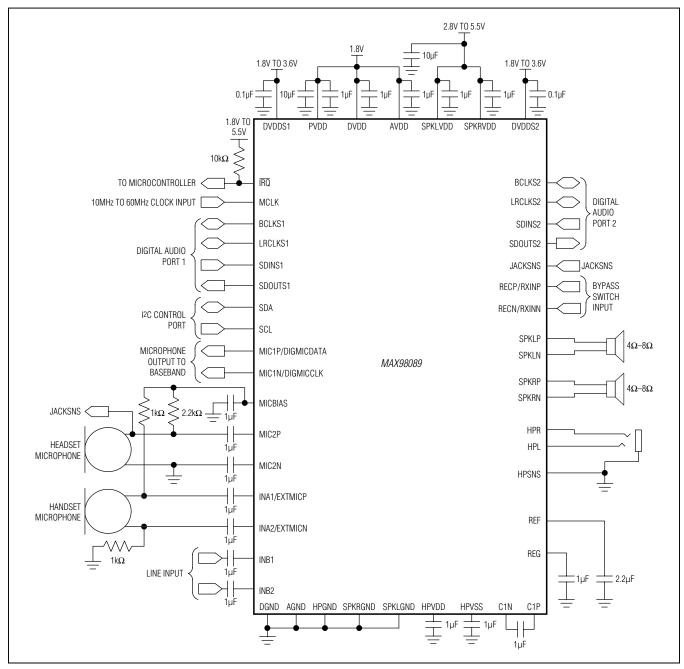

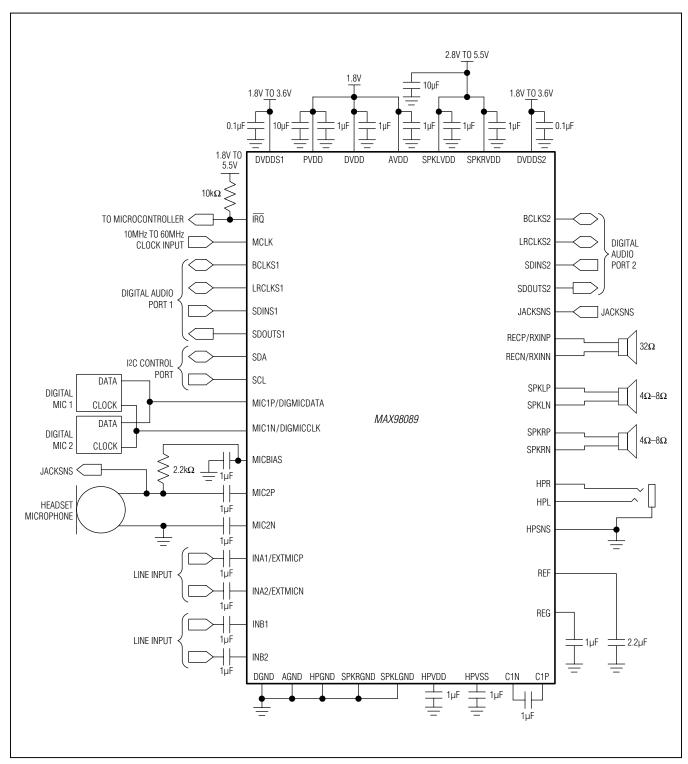

### Simplified Block Diagram

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maximintegrated.com.

19-5865; Rev 1; 3/12

# Low-Power, Stereo Audio Codec with FlexSound Technology

### **TABLE OF CONTENTS**

| General Description                      | 1   |

|------------------------------------------|-----|

| Features                                 |     |

| Simplified Block Diagram                 |     |

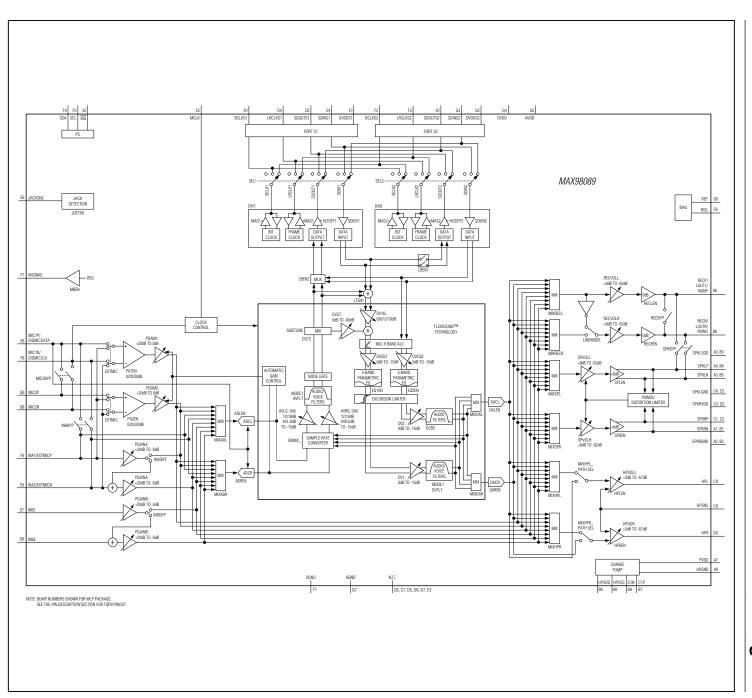

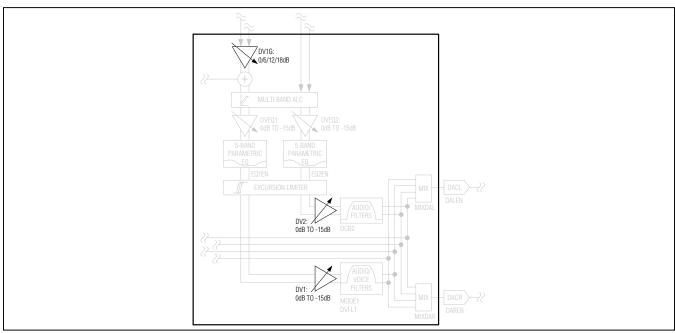

| Functional Diagram                       |     |

| Absolute Maximum Ratings                 |     |

| Electrical Characteristics               |     |

| Digital Input/Output Characteristics     | 19  |

| Input Clock Characteristics              |     |

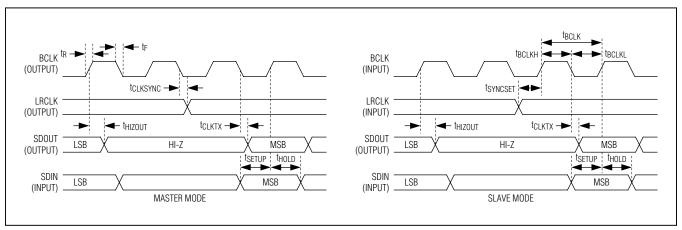

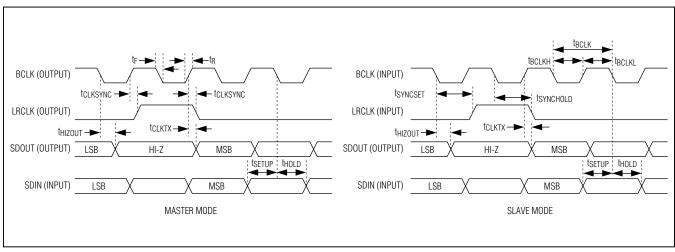

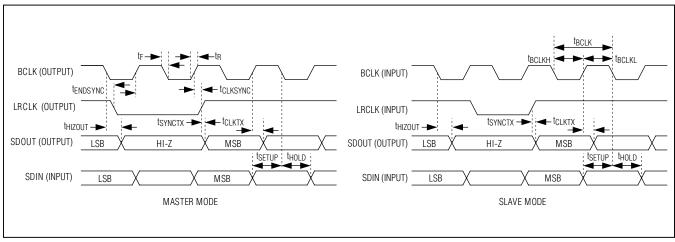

| Audio Interface Timing Characteristics   | 22  |

| Digital Microphone Timing Characterstics |     |

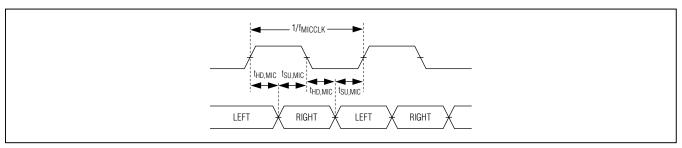

| I2C Timing Characteristics               |     |

| Power Consumption                        |     |

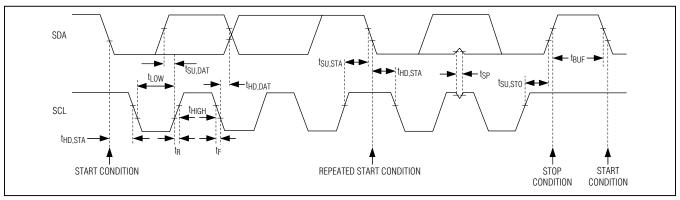

| Typical Operating Characteristics        |     |

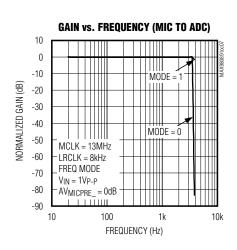

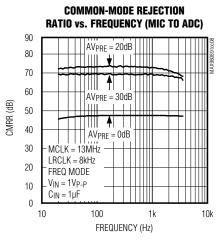

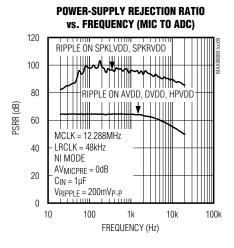

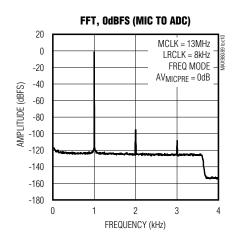

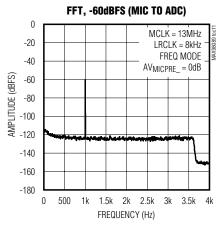

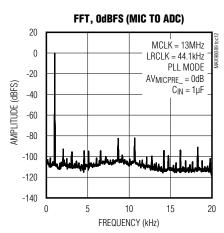

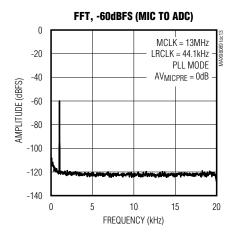

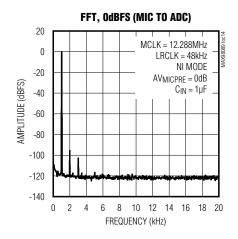

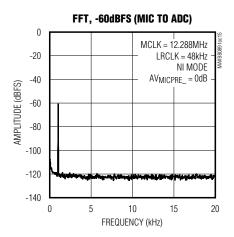

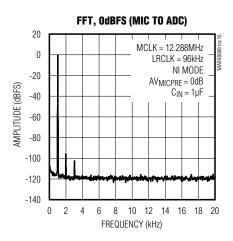

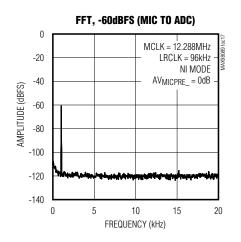

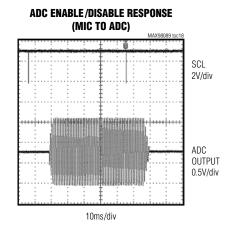

| Microphone to ADC                        |     |

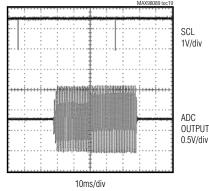

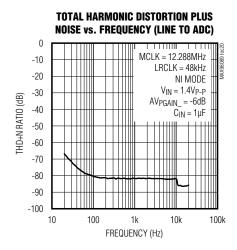

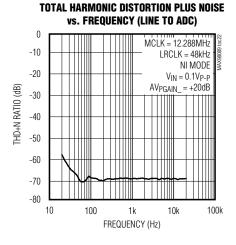

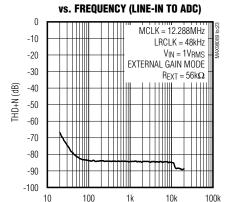

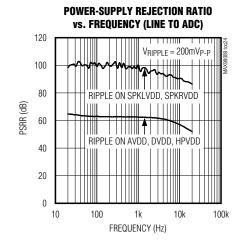

| Line to ADC                              |     |

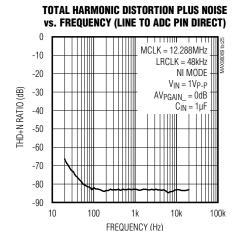

| Line-In Pin Direct to ADC                |     |

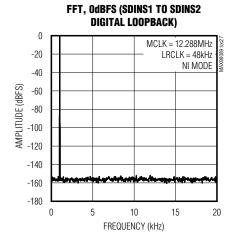

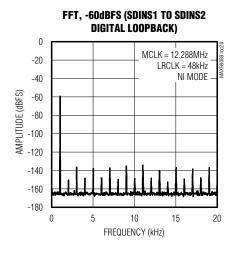

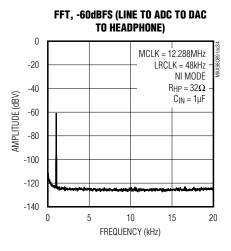

| Digital Loopback                         |     |

| Analog Loopback                          |     |

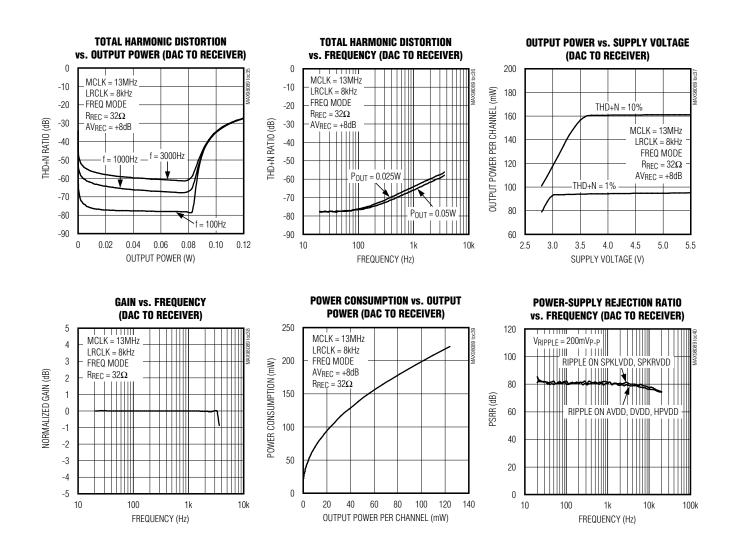

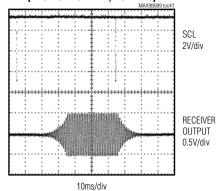

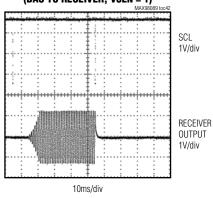

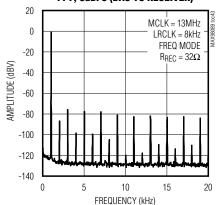

| DAC to Receiver                          | 35  |

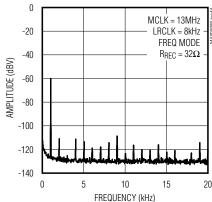

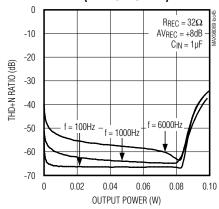

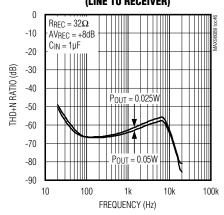

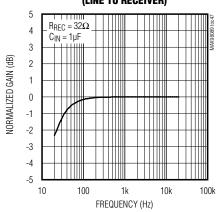

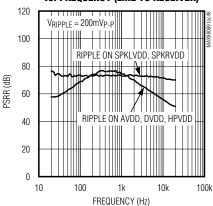

| Line to Receiver                         | 37  |

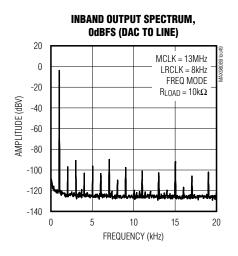

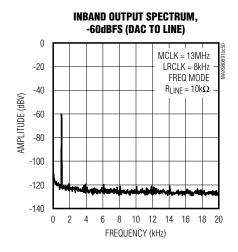

| DAC-to-Line Output                       | 38  |

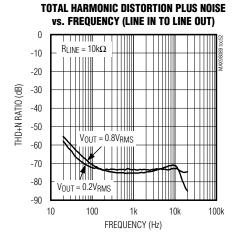

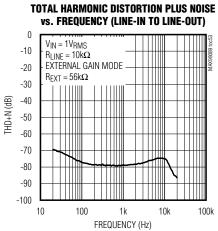

| Line-to-Line Output                      | 38  |

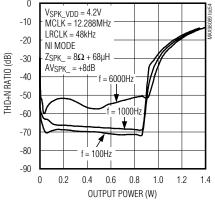

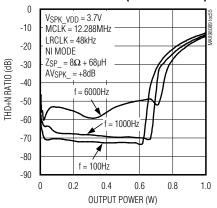

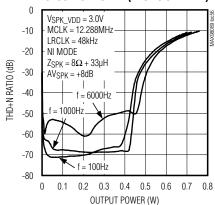

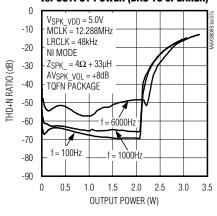

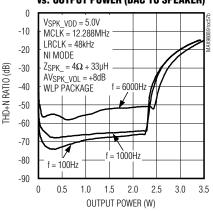

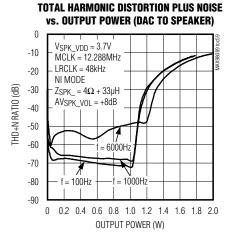

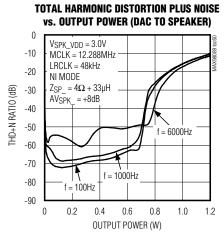

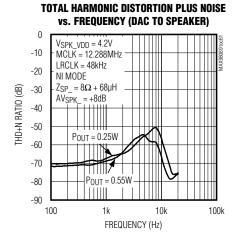

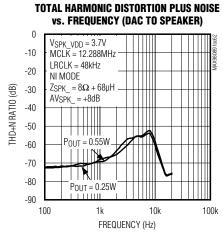

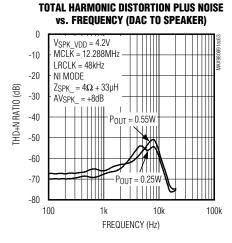

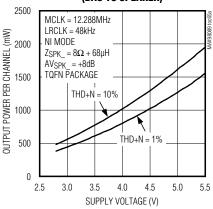

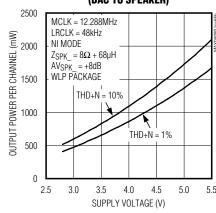

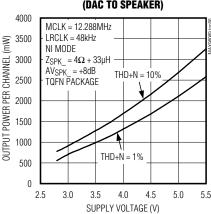

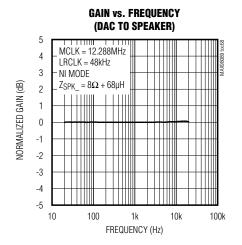

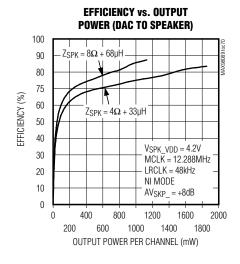

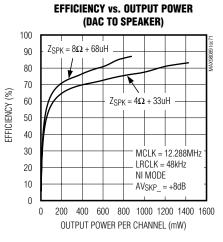

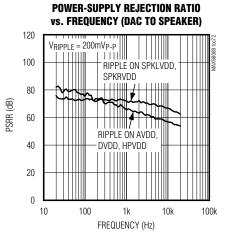

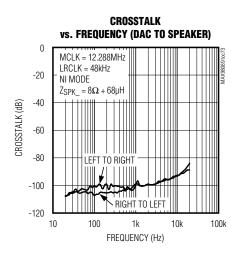

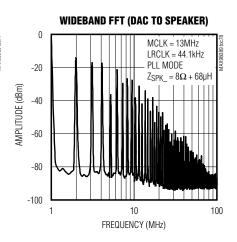

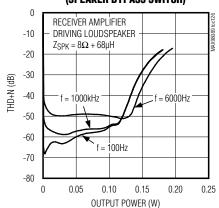

| DAC to Speaker                           | 39  |

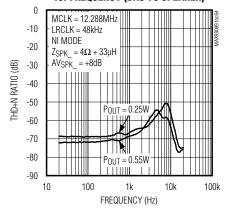

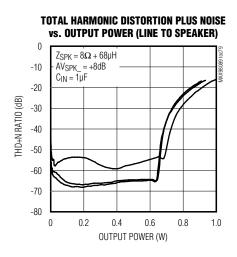

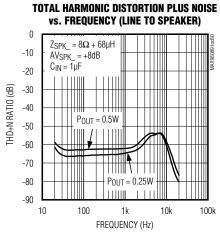

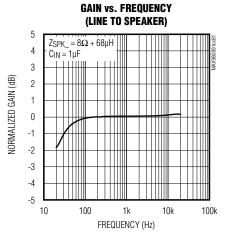

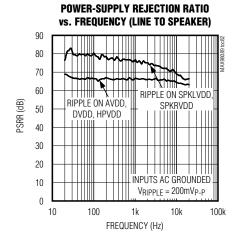

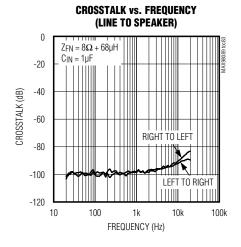

| Line to Speaker                          | 44  |

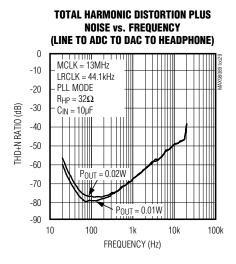

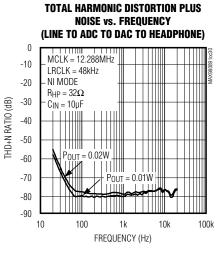

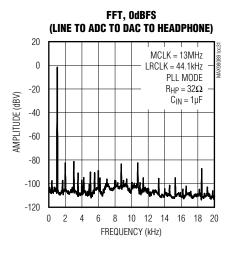

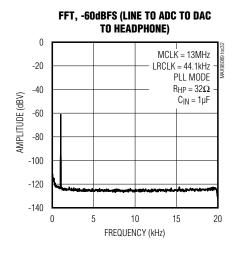

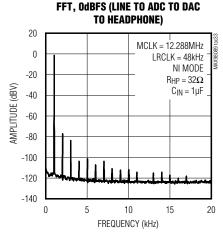

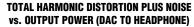

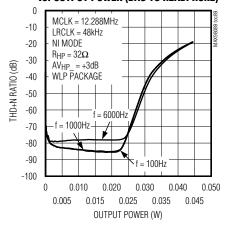

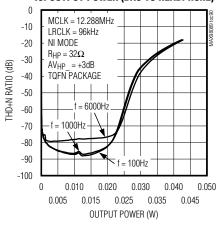

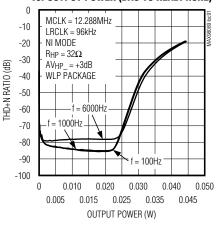

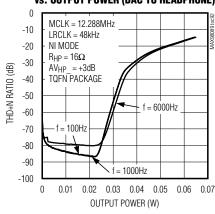

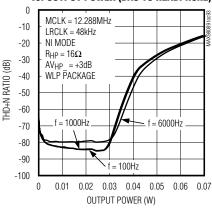

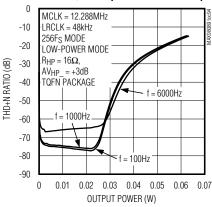

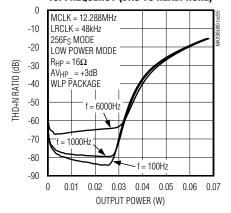

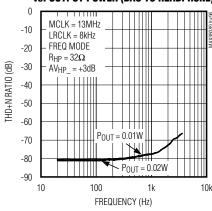

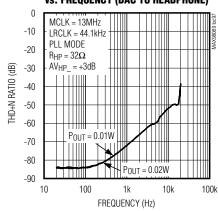

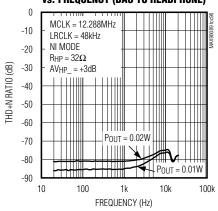

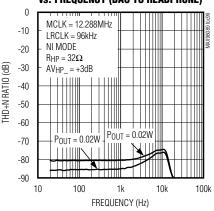

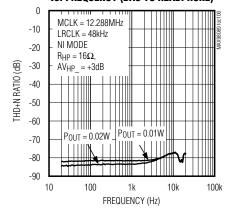

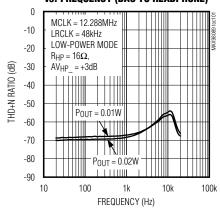

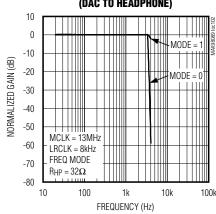

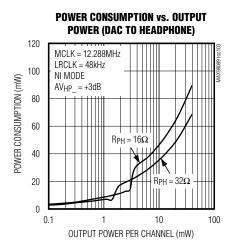

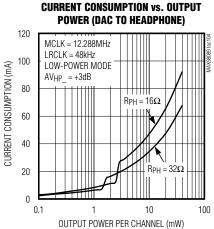

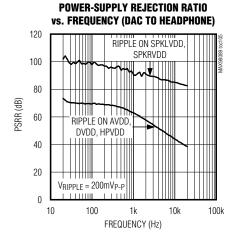

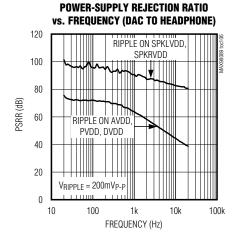

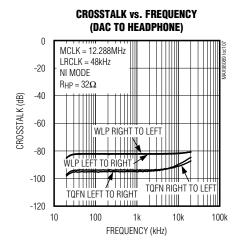

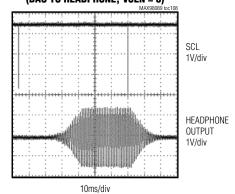

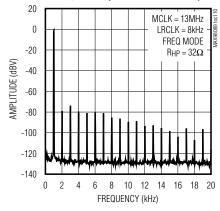

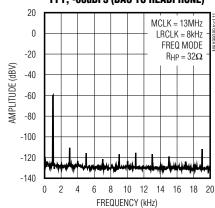

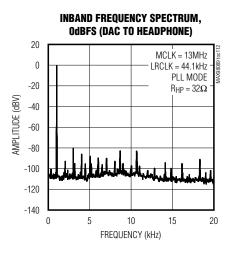

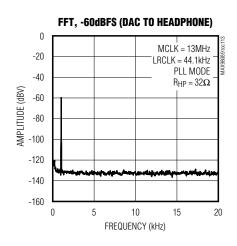

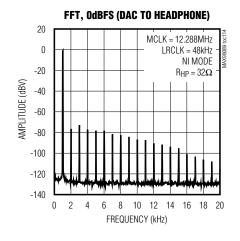

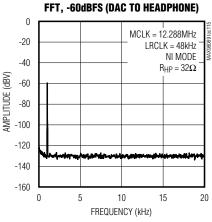

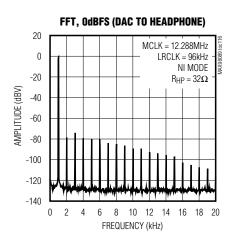

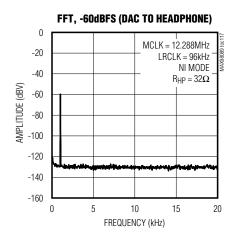

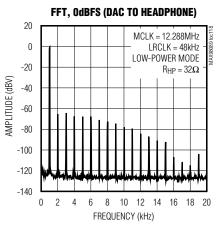

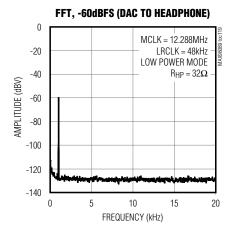

| DAC to Headphone                         | 45  |

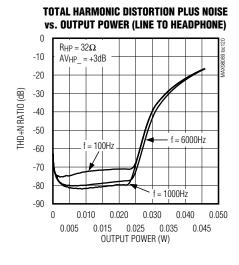

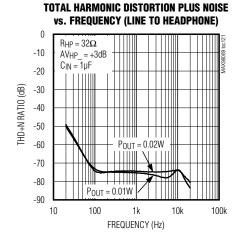

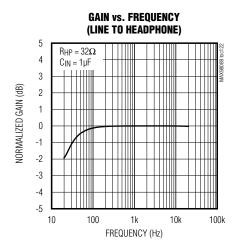

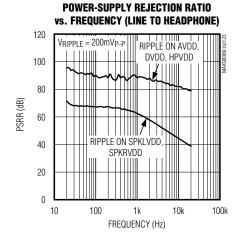

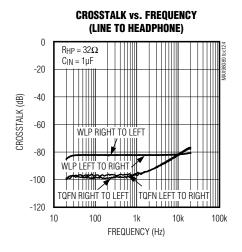

| Line to Headphone                        | 52  |

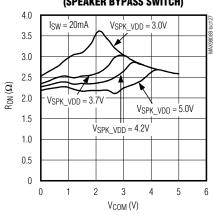

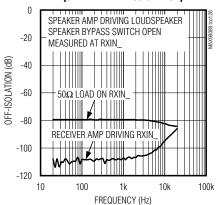

| Speaker Bypass Switch                    | 54  |

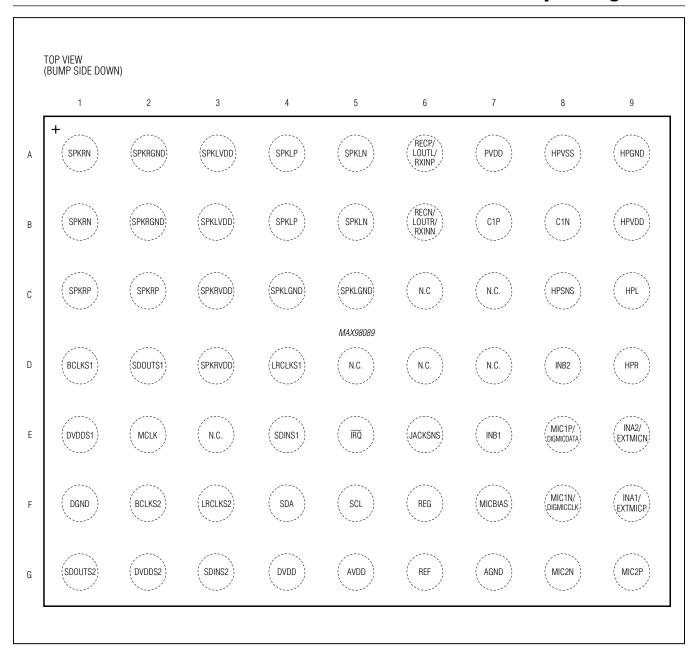

| Pin Configuration                        | 55  |

| Pin Description                          | 57  |

| Detailed Description                     | 60  |

| I <sup>2</sup> C Slave Address           | 61  |

| Registers                                | 61  |

| Power Management                         | 67  |

| Microphone Inputs                        | 69  |

| Production 1                             | 7.1 |

# Low-Power, Stereo Audio Codec with FlexSound Technology

### **TABLE OF CONTENTS (continued)**

| ADC Input Mixers                    | 72  |

|-------------------------------------|-----|

| Record Path Signal Processing.      | 73  |

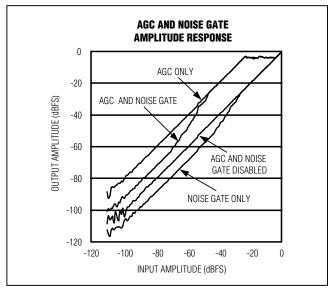

| Microphone AGC                      | 73  |

| Noise Gate                          | 73  |

| ADC Record Level Control            | 76  |

| Sidetone                            | 77  |

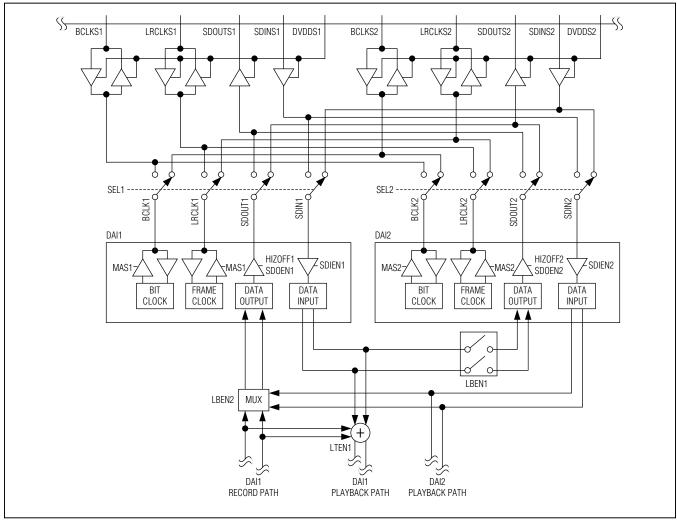

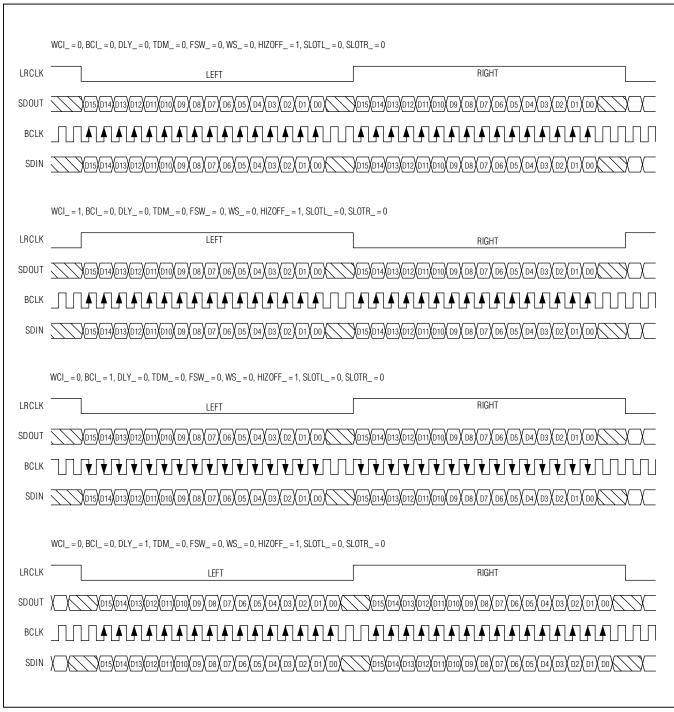

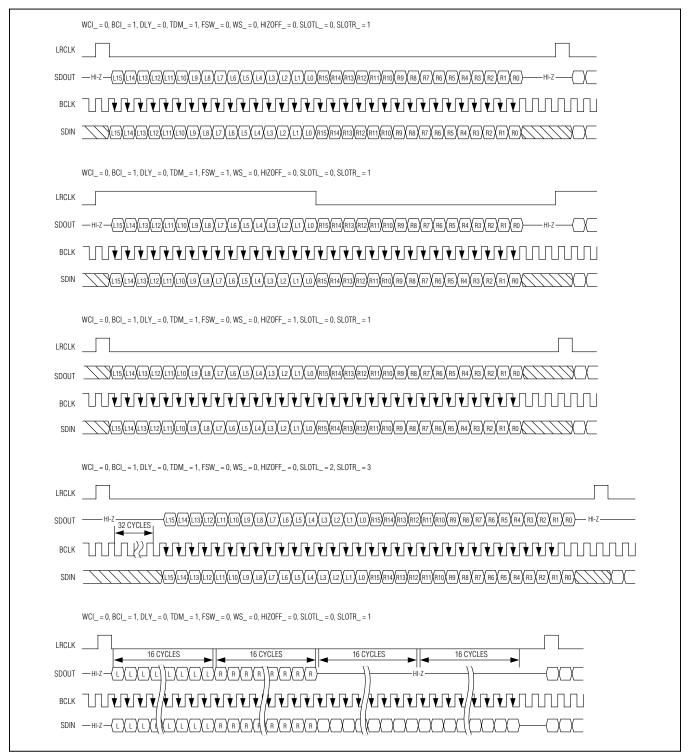

| Digital Audio Interfaces            | 78  |

| Clock Control                       | 85  |

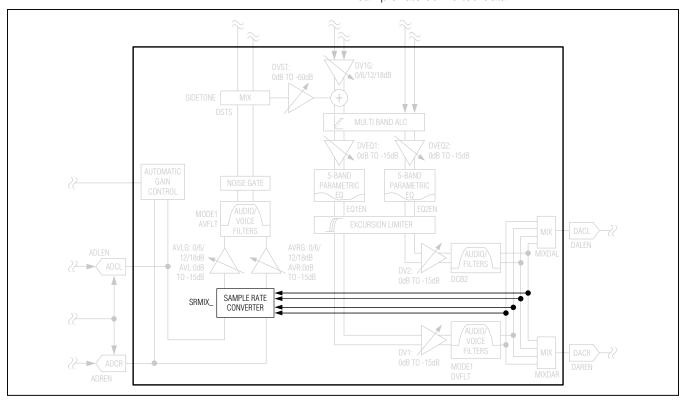

| Sample Rate Converter               | 88  |

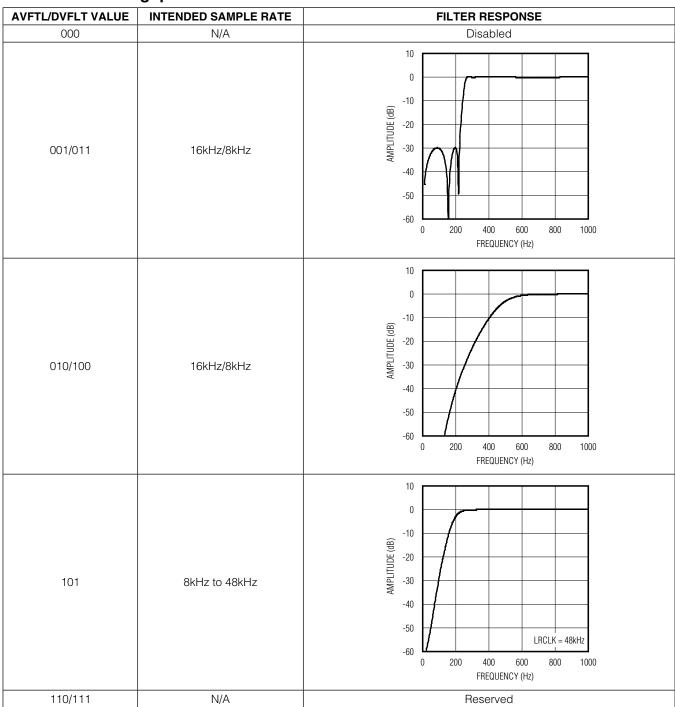

| Passband Filtering                  | 89  |

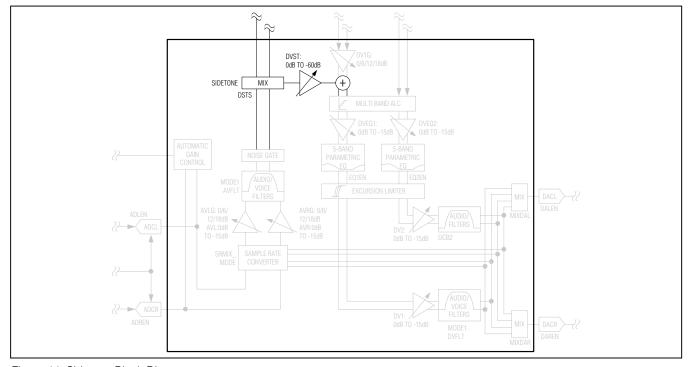

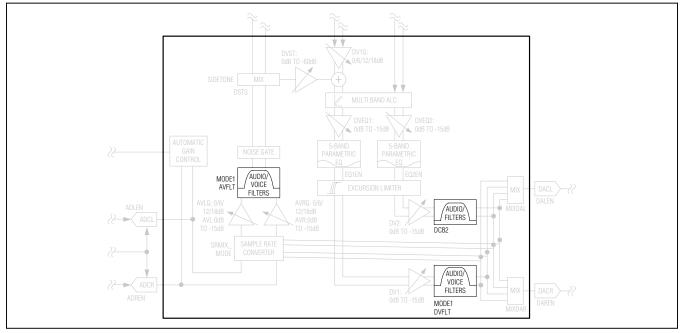

| Playback Path Signal Processing     | 92  |

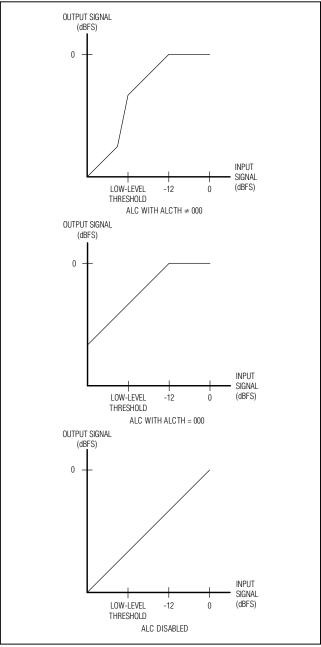

| Automatic Level Control             | 92  |

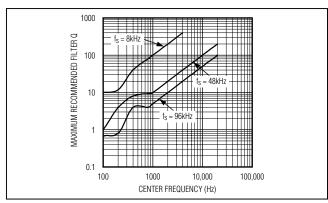

| Parametric Equalizer                | 93  |

| Playback Level Control              | 95  |

| DAC Input Mixers                    | 96  |

| Receiver Amplifier                  | 97  |

| Receiver Output Mixer               | 98  |

| Receiver Output Volume              | 99  |

| Speaker Amplifiers                  | 100 |

| Speaker Output Mixers               | 101 |

| Speaker Amplifier Signal Processing | 102 |

| Excursion Limiter                   | 102 |

| Speaker Output Volume               | 102 |

| Power Limiter                       | 105 |

| Distortion Limiter                  | 106 |

| Headphone                           | 107 |

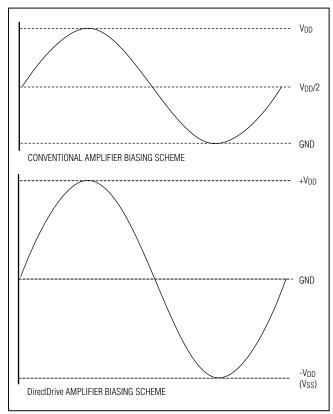

| DirectDrive Headphone Amplifier     | 107 |

| Charge Pump                         | 107 |

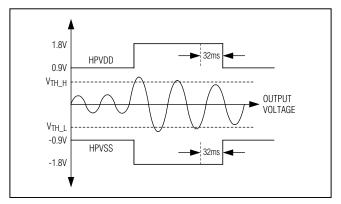

| Class H Operation                   | 108 |

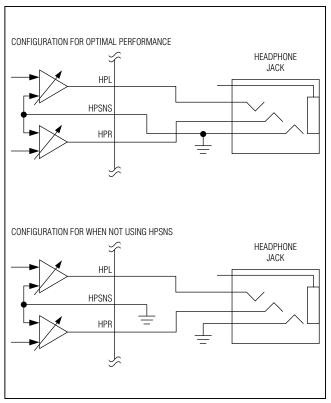

| Headphone Ground Sense (HPSNS)      | 108 |

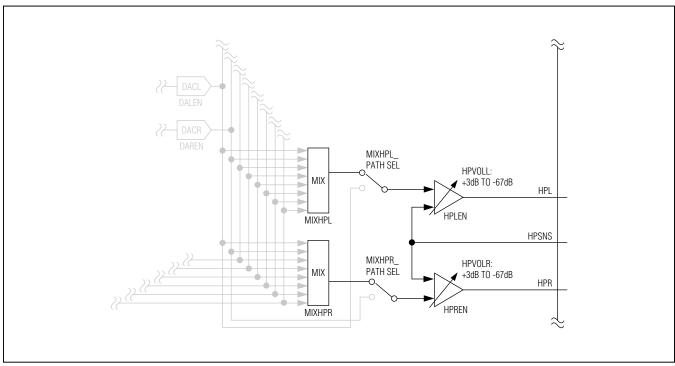

| Headphone Output Mixers             | 110 |

| Headphone Output Volume             | 111 |

| Output Bypass Switches              | 112 |

| Olial, and Day Darkerting           | 440 |

# Low-Power, Stereo Audio Codec with FlexSound Technology

### **TABLE OF CONTENTS (continued)**

| J    | ack Detection                           | . 114 |

|------|-----------------------------------------|-------|

|      | Jack Insertion                          |       |

|      | Accessory Button Detection              |       |

|      | Jack Removal                            |       |

| Е    | Battery Measurement                     |       |

|      | Device Status                           |       |

|      | Device Revision                         |       |

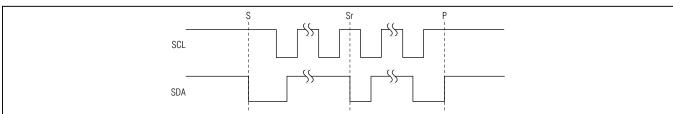

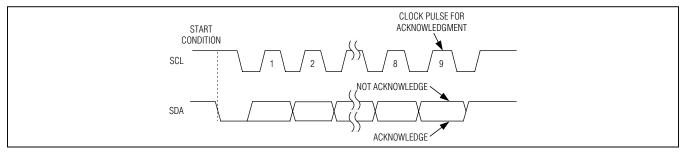

| [2   | <sup>2</sup> C Serial Interface         | . 118 |

|      | Bit Transfer                            |       |

|      | START and STOP Conditions               | . 118 |

|      | Early STOP Conditions                   | . 118 |

|      | Slave Address                           | . 119 |

|      | Acknowledge                             | . 119 |

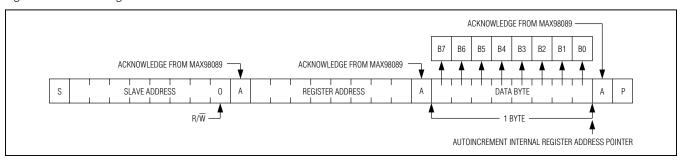

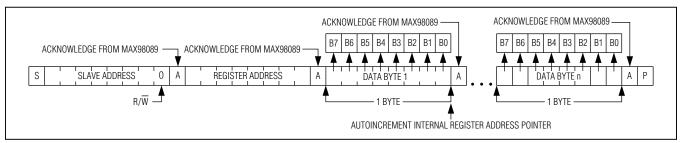

|      | Write Data Format                       | . 119 |

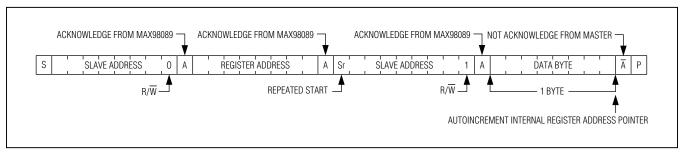

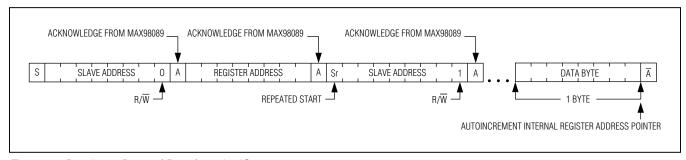

|      | Read Data Format                        | . 120 |

| Арр  | lications Information                   | 121   |

| Т    | ypical Operating Circuits               | . 121 |

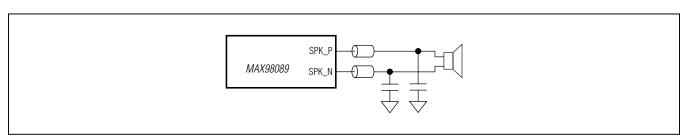

| F    | ilterless Class D Operation             | . 123 |

| F    | RF Susceptibility                       | . 123 |

| 5    | startup/Shutdown Sequencing             | . 123 |

|      | Component Selection                     | . 124 |

|      | Optional Ferrite Bead Filter            | . 124 |

|      | Input Capacitor                         | . 124 |

|      | Charge-Pump Capacitor Selection         | . 124 |

|      | Charge-Pump Flying Capacitor            | . 125 |

|      | Charge-Pump Holding Capacitors          | . 125 |

| Ĺ    | Inused Pins                             | . 125 |

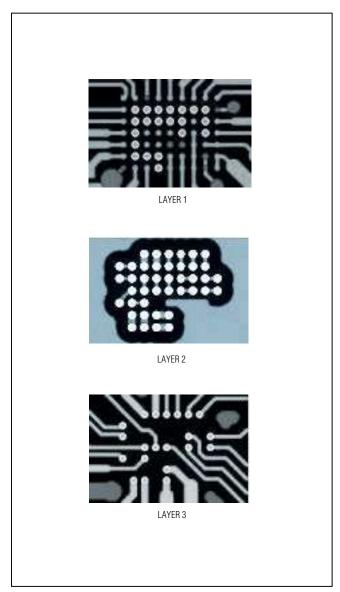

| F    | Recommended PCB Routing                 | . 126 |

| S    | Supply Bypassing, Layout, and Grounding | . 126 |

| V    | VLP Applications Information            | . 127 |

|      | ering Information                       |       |

| Pacl | kage Information                        | 128   |

| D:   | aion History                            | 101   |

# Low-Power, Stereo Audio Codec with FlexSound Technology

Functional Diagram

Maxim Integrated

Ŋ

### **ABSOLUTE MAXIMUM RATINGS**

| (Voltages with respect to AGND.) DVDD, AVDD, PVDD, HPVDD0.3V to +2.00 SPKLVDD, SPKRVDD, DVDDS1, DVDDS20.3V to +6.00 SPKRVDD. |                                                        |

|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| DGND, HPGND, SPKLGND, SPKRGND0.1V to +0.                                                                                     |                                                        |

| •                                                                                                                            |                                                        |

| HPVSS(VHPGND - 2.2V) to (VHPGND + 0.3                                                                                        | V) SPKLP, SPKLN (VSPKLGND - 0.3V) to (VSPKLVDD + 0.3V) |

| C1N(VHPVSS - 0.3V) to (VHPGND + 0.3                                                                                          | V) SPKRP, SPKRN (VSPKRGND - 0.3V) to (VSPKRVDD + 0.3V) |

| C1P(VHPGND - 0.3V) to (VHPVDD + 0.3                                                                                          | V) Continuous Power Dissipation (TA = +70°C)           |

| REF, MICBIAS0.3V to (VSPKLVDD + 0.3                                                                                          | V) 63-Bump WLP (derate 25.6mW/°C above +70°C)2.05W     |

| MCLK, SDINS1, SDINS2, JACKSNS,                                                                                               | 56-Pin TQFN (derate 40mW/°C above +70°C)               |

| SDA, SCL, TRQ0.3V to +6.0                                                                                                    | OV Operating Temperature Range40°C to +85°C            |

| LRCLKS1, BCLKS1, SDOUTS10.3V to (VDVDDS1 + 0.3                                                                               | V) Storage Temperature Range65°C to +150°C             |

| LRCLKS2, BCLKS2, SDOUTS20.3V to (VDVDDS2 + 0.3                                                                               |                                                        |

| REG, INA1/EXTMICP, INA2/EXTMICN, INB1, INB2,                                                                                 | Soldering Temperature (reflow)+260°C                   |

| MIC1P/DIGMICDATA, MIC1N/DIGMICCLK,                                                                                           |                                                        |

| MIC2P MIC2N -0.3V to +2                                                                                                      | 2V                                                     |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(VAVDD = VPVDD = VDVDDS1 = VDVDDS2 = 1.8V, VSPKLVDD = VSPKRVDD = 3.7V. Speaker loads (ZSPK) connected between SPK_P and SPK_N. Receiver load (RREC) connected between RECP and RECN. Headphone loads (RHP) connected from HPL or HPR to HPGND. Line out loads (RLOUT) connected from LOUTL or LOUTR to SPKLGND. RLOAD = RHP = <math>\infty$ , RREC =  $\infty$ , ZSPK =  $\infty$ , CREF =  $2.2\mu$ F, CMICBIAS = CREG =  $1\mu$ F, CC1N-C1P =  $1\mu$ F, CHPVDD = CHPVSS =  $1\mu$ F. AVMICPRE\_ = +20dB, AVMICPGA\_ = 0dB, AVDACATTN = 0dB, AVDACGAIN = 0dB, AVADCGAIN = 0dB, AVPGAIN\_ = 0dB, AVPG

| PARAMETER                            | SYMBOL | CONDITIONS                                                  |                     | MIN  | TYP   | MAX    | UNITS |

|--------------------------------------|--------|-------------------------------------------------------------|---------------------|------|-------|--------|-------|

| POWER SUPPLY                         |        |                                                             |                     |      |       |        |       |

|                                      |        |                                                             | VSPKLVDD, VSPKRVDD  | 2.8  |       | 5.5    |       |

| Supply Voltage Range                 |        | Guaranteed by PSRR                                          | VDVDD, VAVDD, VPVDD | 1.65 | 1.8   | 2      | V     |

|                                      |        |                                                             | VDVDDS1, VDVDDS2    | 1.65 |       | 3.6    |       |

|                                      |        | Full discolors Old In section                               | Analog              |      | 4.5   | 8      |       |

|                                      |        | Full-duplex 8kHz mono, receiver output, MAS = 1             | Speaker             |      | 1.6   | 2.3    |       |

|                                      |        | receiver output, MAS = 1                                    | Digital             |      | 1.3   | 2      |       |

| T                                    |        | DAC playback 48kHz<br>stereo, headphone<br>outputs, MAS = 1 | Analog              |      | 1.9   | 3      |       |

| Total Supply Current (Notes 2 and 3) | IVDD   |                                                             | Speaker             |      | 0.001 | 0.0058 | ] mA  |

| (Notes 2 and 3)                      |        |                                                             | Digital             |      | 2.47  | 3.5    |       |

|                                      |        | DAC playback 48kHz<br>stereo, speaker outputs,<br>MAS = 1   | Analog              |      | 3.6   | 6.5    |       |

|                                      |        |                                                             | Speaker             |      | 6.41  | 8.5    | ]     |

|                                      |        |                                                             | Digital             |      | 2.49  | 3.5    | 1     |

|                                      |        |                                                             | Analog              |      | 0.2   | 2      |       |

| Shutdown Supply Current              |        | $T_A = +25^{\circ}C$                                        | Speaker             |      | 0.01  | 1      | μΑ    |

| (Note 2)                             |        |                                                             | Digital             |      | 1     | 5      | ]     |

| REF Voltage                          |        |                                                             |                     |      | 2.5   |        | V     |

| REG Voltage                          |        |                                                             |                     |      | 0.79  |        | V     |

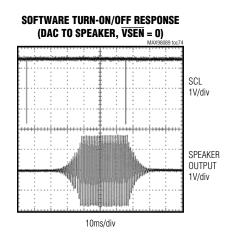

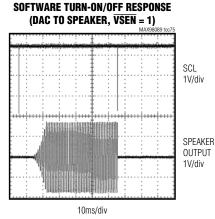

| Chutdown to Full Operation           |        | VSEN = 0                                                    |                     |      | 30    |        | ma    |

| Shutdown to Full Operation           |        | VSEN = 1                                                    |                     |      | 17    |        | ms    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(VAVDD = VPVDD = VDVDDS1 = VDVDDS2 = 1.8V, VSPKLVDD = VSPKRVDD = 3.7V. Speaker loads (ZSPK) connected between SPK_P and SPK_N. Receiver load (RREC) connected between RECP and RECN. Headphone loads (RHP) connected from HPL or HPR to HPGND. Line out loads (RLOUT) connected from LOUTL or LOUTR to SPKLGND. RLOAD = RHP = <math>\infty$ , RREC =  $\infty$ , ZSPK =  $\infty$ , CREF =  $2.2\mu$ F, CMICBIAS = CREG =  $1\mu$ F, CC1N-C1P =  $1\mu$ F, CHPVDD = CHPVSS =  $1\mu$ F. AVMICPRE\_ = +20dB, AVMICPGA\_ = 0dB, AVDACATTN = 0dB, AVDACGAIN = 0dB, AVADCLVL = 0dB, AVADCGAIN = 0dB, AVPGAIN\_ = 0dB, AVPG

| PARAMETER                         | SYMBOL      | CONI                                                          | DITIONS                             | MIN  | TYP  | MAX  | UNITS            |  |

|-----------------------------------|-------------|---------------------------------------------------------------|-------------------------------------|------|------|------|------------------|--|

| MICROPHONE TO ADC PATH            | 1           |                                                               |                                     |      |      |      | •                |  |

| Dynamic Range                     | DR          | fs = 8kHz, MODE = 0 (IIF (Note 4)                             | R voice), AVMICPRE_ = 0dB           |      | 88   |      | dB               |  |

|                                   |             | $V_{IN} = 0.1V_{P-P}$ , $f_S = 8kHz$                          | f = 1kHz                            |      | -78  |      |                  |  |

| Total Harmonic Distortion + Noise | THD+N       | AVMICPRE_ = 0dB, VIN =                                        | 1V <sub>P-P</sub> , f = 1kHz        |      | -85  |      | dB               |  |

| TVOISE                            |             | AVMICPRE_ = +30dB, VIN:                                       | =32mVp-p, f=1kHz                    |      | -71  |      |                  |  |

| Common-Mode Rejection<br>Ratio    | CMRR        | V <sub>IN</sub> = 100mV <sub>P-P</sub> , f = 217I             | Hz                                  |      | 74   |      | dB               |  |

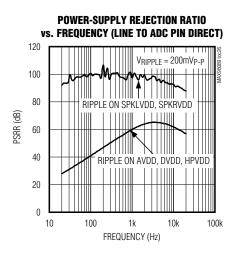

|                                   |             | V <sub>AVDD</sub> = 1.65V to 1.95V,<br>MIC inputs unconnected | input referred,                     | 50   | 62   |      |                  |  |

| Power-Supply Rejection Ratio      | PSRR        | f = 217Hz, VRIPPLE = 200                                      | OmVP-P, input referred              |      | 62   |      | dB               |  |

|                                   |             | f = 1kHz, VRIPPLE = 200mVp-p, input referred                  |                                     |      | 62   |      |                  |  |

|                                   |             | f = 10kHz, VRIPPLE = 200                                      | )mV <sub>P-P</sub> , input referred |      | 55   |      |                  |  |

|                                   |             |                                                               | MODE = 0 (IIR voice)<br>8kHz        |      | 2.2  |      |                  |  |

| Della Diagram Della               |             | 1kHz, 0dB input,<br>highpass filter disabled                  | MODE = 0 (IIR voice)<br>16kHz       |      | 1.1  |      |                  |  |

| Path Phase Delay                  |             | measured from analog input to digital output                  | MODE = 1 (FIR audio)<br>8kHz        |      | 4.5  |      | - ms             |  |

|                                   |             |                                                               | MODE = 1 (FIR audio)<br>48kHz       |      | 0.76 |      |                  |  |

| MICROPHONE PREAMP                 |             |                                                               |                                     |      |      |      |                  |  |

| Full-Scale Input                  |             | AVMICPRE_ = 0dB                                               |                                     |      | 1.05 |      | V <sub>P-P</sub> |  |

|                                   |             |                                                               | PA1EN/PA2EN = 01                    |      | 0    |      |                  |  |

| Preamplifier Gain                 | AVMICPRE_   | (Note 5)                                                      | PA1EN/PA2EN = 10                    | 19.5 | 20   | 20.5 | dB               |  |

|                                   |             |                                                               | PA1EN/PA2EN = 11                    | 29.5 | 30   | 30.5 |                  |  |

| PGA Gain                          | AVMICPGA_   | (Note 5)                                                      | PGAM1/PGAM2 = 0x00                  | 19   | 20   | 21   | dB               |  |

| i un uaiii                        | AVIVIICPGA_ | (INOLE O)                                                     | PGAM1/PGAM2 = 0x14                  |      | 0    |      | UB               |  |

| MIC Input Resistance              | RIN_MIC     | All gain settings, measure MIC1N/MIC2P/MIC2N                  | ed at MIC1P/                        |      | 50   |      | kΩ               |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(VAVDD = VPVDD = VDVDD = VDVDDS1 = VDVDDS2 = 1.8V, VSPKLVDD = VSPKRVDD = 3.7V. Speaker loads (ZSPK) connected between SPK_P and SPK_N. Receiver load (RREC) connected between RECP and RECN. Headphone loads (RHP) connected from HPL or HPR to HPGND. Line out loads (RLOUT) connected from LOUTL or LOUTR to SPKLGND. RLOAD = RHP = <math>\infty$ , RREC =  $\infty$ , ZSPK =  $\infty$ , CREF =  $2.2\mu$ F, CMICBIAS = CREG =  $1\mu$ F, CC1N-C1P =  $1\mu$ F, CHPVDD = CHPVSS =  $1\mu$ F. AVMICPRE\_ = +20dB, AVMICPGA\_ = 0dB, AVDACATTN = 0dB, AVDACGAIN = 0dB, AVADCLVL = 0dB, AVADCGAIN = 0dB, AVPGAIN\_ = 0

| PARAMETER                         | SYMBOL   | CONDITIONS                                                                                         | MIN  | TYP | MAX  | UNITS  |

|-----------------------------------|----------|----------------------------------------------------------------------------------------------------|------|-----|------|--------|

| MICROPHONE BIAS                   | •        |                                                                                                    |      |     |      |        |

| MICBIAS Output Voltage            | VMICBIAS | I <sub>LOAD</sub> = 1mA                                                                            | 2.15 | 2.2 | 2.25 | V      |

| Load Regulation                   |          | I <sub>LOAD</sub> = 1mA to 2mA                                                                     |      | 0.5 | 4.5  | mV     |

| Line Regulation                   |          | VSPKLVDD = 2.8V to 5.5V                                                                            |      | 110 |      | μV     |

| Ripple Rejection                  |          | f = 217Hz, VRIPPLE (SPKLVDD) = 100mVp-p                                                            |      | 92  |      | dB     |

| Rippie Rejection                  |          | f = 10kHz, VRIPPLE (SPKLVDD) = 100mVp-p                                                            |      | 83  |      | ] ub   |

|                                   |          | A-weighted, f = 20Hz to 20kHz                                                                      |      | 3.9 |      | μVRMS  |

| Noise Voltage                     |          | P-weighted, f = 20Hz to 4kHz                                                                       |      | 2.1 |      | PARIMS |

|                                   |          | f = 1kHz                                                                                           |      | 50  |      | nV/√Hz |

| MICROPHONE BYPASS SWI             | тсн      |                                                                                                    |      |     |      |        |

| On-Resistance                     | Ron      | IMIC1_ = 100mA, INABYP = MIC2BYP = 1,<br>VMIC2_ = VINA_ = 0V, AVDD, TA = +25°C                     |      | 5   | 30   | Ω      |

| Total Harmonic Distortion + Noise | THD+N    | $V_{IN} = 2V_{P-P}, V_{CM} = 0.9V, R_L = 10k\Omega,$<br>f = 1kHz, INABYP = MIC2BYP = 1             |      | -80 |      | dB     |

| Off-Isolation                     |          | $VIN = 2VP-P$ , $VCM = 0.9V$ , $RL = 10k\Omega$ , $f = 1kHz$                                       |      | 60  |      | dB     |

| Off-Leakage Current               |          | VMIC1_ = [0V, AVDD], VMIC2_/VINA_ = [AVDD, 0V]                                                     | -1   |     | +1   | μА     |

| LINE INPUT TO ADC PATH            |          | ,                                                                                                  | '    |     |      |        |

| Dynamic Range (Note 4)            | DR       | INA pin direct, fs = 48kHz, MODE = 1 (FIR audio)                                                   |      | 93  |      | dB     |

| Total Harmonic Distortion + Noise | THD+N    | V <sub>IN</sub> = 1V <sub>P-P</sub> , f = 1kHz                                                     |      | -82 | -74  | dB     |

| Gain Error                        |          | DC accuracy                                                                                        |      | 1   |      | %      |

|                                   |          | VAVDD = 1.65V to 1.95V, input referred, line inputs unconnected, TA = +25°C                        | 57   | 68  |      |        |

| Power-Supply Rejection Ratio      | PSRR     | f = 217Hz, VRIPPLE = 200mVp-p,<br>AVADC = 0dB, input referred                                      |      | 63  |      | - dB   |

|                                   | LOUR     | f = 1kHz, VRIPPLE = 200mVP-P,<br>AVADC = 0dB, input referred                                       |      | 63  |      | ub     |

|                                   |          | f = 10kHz, V <sub>RIPPLE</sub> = 200mV <sub>P-P</sub> ,<br>AV <sub>ADC</sub> = 0dB, input referred |      | 57  |      |        |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(VAVDD = VPVDD = VDVDD = VDVDDS1 = VDVDDS2 = 1.8V, VSPKLVDD = VSPKRVDD = 3.7V. Speaker loads (ZSPK) connected between SPK_P and SPK_N. Receiver load (RREC) connected between RECP and RECN. Headphone loads (RHP) connected from HPL or HPR to HPGND. Line out loads (RLOUT) connected from LOUTL or LOUTR to SPKLGND. RLOAD = RHP = <math>\infty$ , RREC =  $\infty$ , ZSPK =  $\infty$ , CREF =  $2.2\mu$ F, CMICBIAS = CREG =  $1\mu$ F, CC1N-C1P =  $1\mu$ F, CHPVDD = CHPVSS =  $1\mu$ F. AVMICPRE\_ = +20dB, AVMICPGA\_ = 0dB, AVDACATTN = 0dB, AVDACGAIN = 0dB, AVADCLVL = 0dB, AVADCGAIN = 0dB, AVPGAIN\_ = 0dB, AVHP\_ = 0dB, AVREC = 0dB, AVSPK\_ = 0dB, MCLK = 12.288MHz, LRCLK = 48kHz, MAS = 0.74 = 1.80MHz, unless otherwise noted. Typical values are at TA = 1.25C.) (Note 1)

| PARAMETER                     | SYMBOL     | CONDITIONS                         |                                  | MIN     | TYP | MAX       | UNITS  |

|-------------------------------|------------|------------------------------------|----------------------------------|---------|-----|-----------|--------|

| LINE INPUT PREAMP             |            |                                    |                                  |         |     |           |        |

| Full Coole Input              | \/\.       | AVPGAIN_ = 0dB                     |                                  |         | 1   |           | \/p =  |

| Full-Scale Input              | VIN        | AVPGAIN_ = -6dB                    |                                  |         | 1.4 |           | VP-P   |

|                               |            |                                    | PGAINA/PGAINB = 0x0              | 19      | 20  | 21        |        |

|                               |            |                                    | PGAINA/PGAINB = 0x1              | 13      | 14  | 15        |        |

|                               |            | 7. 0500                            | PGAINA/PGAINB = 0x2              | 2       | 3   | 4         |        |

| Level Adjust Gain             | AVPGAIN_   | T <sub>A</sub> = +25°C<br>(Note 5) | PGAINA/PGAINB = 0x3              |         | 0   |           | dB     |

|                               |            | (Note 3)                           | PGAINA/PGAINB = 0x4              | -4      | -3  | -2        | ]      |

|                               |            |                                    | PGAINA/PGAINB = 0x5,<br>0x6, 0x7 | -7      | -6  | -5        |        |

|                               |            | AVPGAIN_ = +20dB                   |                                  | 14.5    | 21  | 28        |        |

|                               |            | AVPGAIN_ = +14dB                   |                                  |         | 20  |           | 1      |

| I De l'ale                    | D          | AVPGAIN_ = +3dB<br>AVPGAIN_ = 0dB  |                                  |         | 20  |           |        |

| Input Resistance              | RIN        |                                    |                                  | 7.5     | 10  | 14        | kΩ     |

|                               |            | AVPGAIN_ = -3dB                    |                                  |         | 20  |           |        |

|                               |            | AV <sub>PGAIN</sub> _ = -6dB       |                                  |         | 20  |           |        |

| Feedback Resistance           | Du. 50     | DIV. 50 INIAEVT/INIDEVT 1          | TA = +25°C                       | 18      | 20  | 22        | kΩ     |

| reedback nesistance           | RIN_FB     | INAEXT/INBEXT = 1                  | $T_A = T_{MIN}$ to $T_{MAX}$     | 16      |     | 24        | NS2    |

| ADC LEVEL CONTROL             |            |                                    |                                  |         |     |           |        |

| ADC Level Adjust Range        | AVADCLVL   | AVL/AVR = 0xF  to  0x0  0          | (Note 5)                         | -12     |     | +3        | dB     |

| ADC Level Step Size           |            |                                    |                                  |         | 1   |           | dB     |

| ADC Gain Adjust Range         | AVADCGAIN  | AVLG/AVRG = 00 to 11               | (Note 5)                         | 0       |     | 18        | dB     |

| ADC Gain Adjust Step Size     |            |                                    |                                  |         | 6   |           | dB     |

| ADC DIGITAL FILTERS           |            |                                    |                                  |         |     |           |        |

| VOICE MODE IIR LOWPASS        | FILTER (MO | DE1 = 0)                           |                                  |         |     |           |        |

| Passband Cutoff               | fPLP       | Ripple limit cutoff                |                                  | 0.441 x | fs  |           | <br>Hz |

| i assuaria Cutori             |            | -3dB cutoff                        |                                  | 0.449 x | fs  |           | 1 12   |

| Passband Ripple               |            | f < fplp                           |                                  | -0.1    |     | +0.1      | dB     |

| Stopband Cutoff               | fSLP       |                                    |                                  |         |     | 0.47 x fs | Hz     |

| Stopband Attenuation (Note 6) |            | f > fSLP                           |                                  | 74      |     |           | dB     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(VAVDD = VPVDD = VDVDD = VDVDDS1 = VDVDDS2 = 1.8V, VSPKLVDD = VSPKRVDD = 3.7V. Speaker loads (ZSPK) connected between SPK_P and SPK_N. Receiver load (RREC) connected between RECP and RECN. Headphone loads (RHP) connected from HPL or HPR to HPGND. Line out loads (RLOUT) connected from LOUTL or LOUTR to SPKLGND. RLOAD = RHP = <math>\infty$ , RREC =  $\infty$ , ZSPK =  $\infty$ , CREF =  $2.2\mu$ F, CMICBIAS = CREG =  $1\mu$ F, CC1N-C1P =  $1\mu$ F, CHPVDD = CHPVSS =  $1\mu$ F. AVMICPRE\_ = +20dB, AVMICPGA\_ = 0dB, AVDACATTN = 0dB, AVDACGAIN = 0dB, AVADCLVL = 0dB, AVADCGAIN = 0dB, AVPGAIN\_ = 0

| PARAMETER                            | SYMBOL        | CONDITIONS                                                  | MIN            | TYP MAX                    | UNITS |

|--------------------------------------|---------------|-------------------------------------------------------------|----------------|----------------------------|-------|

| VOICE MODE IIR HIGHPAS               | SS FILTER (MC | DDE1 = 0)                                                   |                |                            |       |

|                                      |               | AVFLT = 0x1 (Elliptical tuned for fs = 16kHz + 217Hz notch) |                | 0.0161<br>x f <sub>S</sub> |       |

|                                      |               | AVFLT = 0x2 (500Hz Butterworth tuned for fs = 16kHz)        |                | 0.0319<br>x fs             |       |

| Passband Cutoff<br>(-3dB from Peak)  | fahppb        | AVFLT = 0x3 (Elliptical tuned for fs = 8kHz + 217Hz notch)  |                | 0.0321<br>x fs             | Hz    |

|                                      |               | AVFLT = 0x4 (500Hz Butterworth tuned for fs = 8kHz)         |                | 0.0632<br>x f <sub>S</sub> |       |

|                                      |               | AVFLT = 0x5 (fs/240 Butterworth)                            |                | 0.0043<br>x fs             |       |

|                                      |               | AVFLT = 0x1 (Elliptical tuned for fs = 16kHz + 217Hz notch) | 0.0139<br>x fs |                            |       |

|                                      |               | AVFLT = 0x2 (500Hz Butterworth tuned for fs = 16kHz)        | 0.0156<br>x fs |                            |       |

| Stopband Cutoff<br>(-30dB from Peak) | fAHPSB        | AVFLT = 0x3 (Elliptical tuned for fs = 8kHz + 217Hz notch)  | 0.0279<br>x fs |                            | Hz    |

|                                      |               | AVFLT = 0x4 (500Hz Butterworth tuned for fs = 8kHz)         | 0.0312<br>x fs |                            |       |

|                                      |               | AVFLT = 0x5 (fs/240 Butterworth)                            | 0.0018<br>x fs |                            |       |

| DC Attenuation                       | DCATTEN       | AVFLT ≠ 000                                                 |                | 90                         | dB    |

| STEREO AUDIO MODE FII                | R LOWPASS F   | LTER (MODE1 = 1, DHF1 = 0, LRCLK < 50kHz)                   |                |                            |       |

|                                      |               | Ripple limit cutoff                                         | 0.43 x fs      |                            |       |

| Passband Cutoff                      | fPLP          | -3dB cutoff                                                 | 0.48 x fs      |                            | Hz    |

|                                      |               | -6.02dB cutoff                                              | 0.5 x fs       |                            |       |

| Passband Ripple                      |               | f < fPLP                                                    | -0.1           | +0.1                       | dB    |

| Stopband Cutoff                      | fSLP          |                                                             |                | 0.58 x fs                  | Hz    |

| Stopband Attenuation (Note 6)        |               | f < fSLP                                                    | 60             |                            | dB    |

| ADC STEREO AUDIO MOD                 | DE FIR LOWPA  | SS FILTER (MODE1 = 1, DHF1 = 1, LRCLK > 50kHz               | )              |                            |       |

| Doophand Cutoff                      | for o         | Ripple limit cutoff                                         | 0.208 x fs     |                            | Шэ    |

| Passband Cutoff                      | fPLP          | -3dB cutoff                                                 | 0.28 x fs      |                            | Hz    |

| Passband Ripple                      |               | f < fplp                                                    | -0.1           | +0.1                       | dB    |

| Stopband Cutoff                      | fSLP          |                                                             |                | 0.417 x fs                 | Hz    |

| Stopband Attenuation                 |               | f < fSLP                                                    | 60             |                            | dB    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(VAVDD = VPVDD = VDVDDS1 = VDVDDS2 = 1.8V, VSPKLVDD = VSPKRVDD = 3.7V. Speaker loads (ZSPK) connected between SPK_P and SPK_N. Receiver load (RREC) connected between RECP and RECN. Headphone loads (RHP) connected from HPL or HPR to HPGND. Line out loads (RLOUT) connected from LOUTL or LOUTR to SPKLGND. RLOAD = RHP = <math>\infty$ , RREC =  $\infty$ , ZSPK =  $\infty$ , CREF =  $2.2\mu$ F, CMICBIAS = CREG =  $1\mu$ F, CC1N-C1P =  $1\mu$ F, CHPVDD = CHPVSS =  $1\mu$ F. AVMICPRE\_ = +20dB, AVMICPGA\_ = 0dB, AVDACATTN = 0dB, AVDACGAIN = 0dB, AVADCLVL = 0dB, AVADCGAIN = 0dB, AVPGAIN\_ = 0dB, AVHP\_ = 0dB, AVREC = 0dB, AVSPK\_ = 0dB, MCLK = +12.288MHz, LRCLK = +12.288MHz, MAS = +12.288MHz, URCLK = +12.288MHz, UR

| PARAMETER                           | SYMBOL     | CONDITIONS                                                         | 3                | MIN | TYP   | MAX             | UNITS |

|-------------------------------------|------------|--------------------------------------------------------------------|------------------|-----|-------|-----------------|-------|

| STEREO AUDIO MODE DC E              | LOCKING H  | IGHPASS FILTER (MODE1 = 1)                                         |                  |     |       |                 |       |

| Passband Cutoff<br>(-3dB from Peak) | fAHPPB     | AVFLT ≠ 000                                                        |                  |     | 0     | .000125<br>x fs | Hz    |

| DC Attenuation                      | DCAtten    | AVFLT ≠ 000                                                        |                  |     | 90    |                 | dB    |

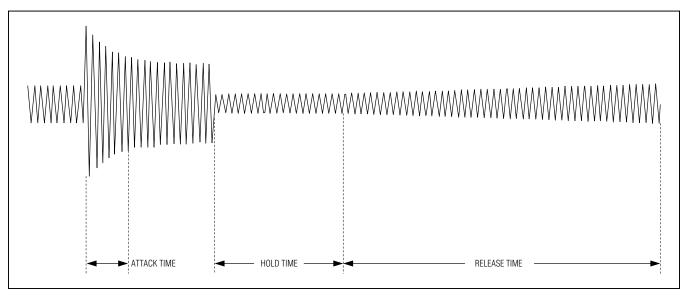

| MICROPHONE AUTOMATIC                | GAIN CONTI | ROL                                                                |                  |     |       |                 |       |

| ACCIDED Demotion                    |            | AGCHLD = 01                                                        |                  |     | 50    |                 |       |

| AGC Hold Duration                   |            | AGCHLD = 11                                                        |                  |     | 400   |                 | ms    |

| ACC Attack Times                    |            | AGCATK = 00                                                        |                  |     | 2     |                 |       |

| AGC Attack Time                     |            | AGCATK = 11                                                        |                  |     | 123   |                 | ms    |

| ACC Pologo Timo                     |            | AGCRLS = 000                                                       |                  |     | 0.078 |                 |       |

| AGC Release Time                    |            | AGCRLS = 111                                                       |                  |     | 10    |                 | S     |

| AGC Threshold Level                 |            | AGCTH = 0x0 to 0xF                                                 |                  | -3  |       | +18             | dB    |

| AGC Threshold Step Size             |            |                                                                    |                  |     | 1     |                 | dB    |

| AGC Gain                            |            | (Note 5)                                                           |                  | 0   |       | 20              | dB    |

| ADC NOISE GATE                      |            |                                                                    |                  |     |       |                 |       |

| NG Threshold Level                  |            | ANTH = 0x3 to 0xF, referred to 0                                   | dBFS             | -64 |       | -16             | dB    |

| NG Attenuation                      |            | (Note 5)                                                           |                  | 0   |       | 12              | dB    |

| ADC-TO-DAC DIGITAL SIDE             | TONE (MODE | ≣ = 0)                                                             |                  |     |       |                 |       |

| Cidatana Cain Adiust Danga          | Λ\/οτο ι   | DVST = 0x01                                                        |                  |     | -0.5  |                 | dB    |

| Sidetone Gain Adjust Range          | AVSTGA     | DVST = 0x1F                                                        |                  |     | -60.5 |                 | иь    |

| Sidetone Gain Adjust Step<br>Size   |            |                                                                    |                  |     | 2     |                 | dB    |

| Cidatana Dath Dhaga Dalay           |            | 1kHz, 0dB input, highpass filter                                   | 8kHz             |     | 2.2   |                 |       |

| Sidetone Path Phase Delay           |            | disabled                                                           | 16kHz            |     | 1.1   |                 | ms    |

| ADC-TO-DAC DIGITAL LOO              | P-THROUGH  | PATH                                                               |                  |     |       |                 | •     |

| Dynamic Range (Note 4)              | DR         | fs = 48kHz, MCLK = 12.288MHz,<br>(FIR audio), MIC to HP output, TA |                  | 83  | 93    |                 | dB    |

| Total Harmonic Distortion + Noise   | THD+N      | f = 1kHz, fs = 48kHz, MCLK = 12<br>1 (FIR audio), MIC to HP output | 2.288MHz, MODE = |     | 81    |                 | dB    |

| DAC LEVEL CONTROL                   |            |                                                                    |                  |     |       |                 |       |

| DAC Attenuation Range               | AVDACATTN  | DV_ = 0xF to 0x0 (Note 5)                                          |                  | -15 |       | 0               | dB    |

| DAC Attenuation Step Size           |            |                                                                    |                  |     | 1     |                 | dB    |

| DAC Gain Adjust Range               | AVDACGAIN  | DV1G = 00 to 11 (Note 5)                                           |                  | 0   |       | 18              | dB    |

| DAC Gain Adjust Step Size           | 2,100,111  | (,                                                                 |                  |     | 6     |                 | dB    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(VAVDD = VPVDD = VDVDD = VDVDDS1 = VDVDDS2 = 1.8V, VSPKLVDD = VSPKRVDD = 3.7V. Speaker loads (ZSPK) connected between SPK_P and SPK_N. Receiver load (RREC) connected between RECP and RECN. Headphone loads (RHP) connected from HPL or HPR to HPGND. Line out loads (RLOUT) connected from LOUTL or LOUTR to SPKLGND. RLOAD = RHP = <math>\infty$ , RREC =  $\infty$ , ZSPK =  $\infty$ , CREF =  $2.2\mu$ F, CMICBIAS = CREG =  $1\mu$ F, CC1N-C1P =  $1\mu$ F, CHPVDD = CHPVSS =  $1\mu$ F. AVMICPRE\_ = +20dB, AVMICPGA\_ = 0dB, AVDACATTN = 0dB, AVDACGAIN = 0dB, AVADCLVL = 0dB, AVADCGAIN = 0dB, AVPGAIN\_ = 0

| PARAMETER                            | SYMBOL       | CONDITIONS                                                  | MIN         | TYP | MAX            | UNITS |

|--------------------------------------|--------------|-------------------------------------------------------------|-------------|-----|----------------|-------|

| DAC DIGITAL FILTERS                  |              |                                                             |             |     |                |       |

| VOICE MODE IIR LOWPASS               | FILTER (MO   | DE1 = 0)                                                    |             |     |                |       |

| Passband Cutoff                      | four         | Ripple limit cutoff                                         | 0.448 x fs  |     |                | Hz    |

| rasspand Culon                       | fpLp         | -3dB cutoff                                                 | 0.451 x fs  |     |                | 112   |

| Passband Ripple                      |              | f < fplp                                                    | -0.1        |     | +0.1           | dB    |

| Stopband Cutoff                      | fSLP         |                                                             |             | 0.4 | 76 x fs        | Hz    |

| Stopband Attenuation (Note 6)        |              | f > fSLP                                                    | 75          |     |                | dB    |

| VOICE MODE IIR HIGHPAS               | S FILTER (MC | DDE1 = 0)                                                   |             |     |                |       |

|                                      |              | DVFLT = 0x1 (Elliptical tuned for fs = 16kHz + 217Hz notch) |             |     | 0.0161<br>x fs |       |

|                                      |              | DVFLT = 0x2 (500Hz Butterworth tuned for fs = 16kHz)        |             |     | 0.0312<br>x fs |       |

| Passband Cutoff<br>(-3dB from Peak)  | fDHPPB       | DVFLT = 0x3 (Elliptical tuned for fs = 8kHz + 217Hz notch)  |             |     | 0.0321<br>x fs | Hz    |

|                                      |              | DVFLT = 0x4 (500Hz Butterworth tuned for fs = 8kHz)         |             |     | 0.0625<br>x fs |       |

|                                      |              | DVFLT = 0x5 (fs/240 Butterworth)                            |             |     | 0.0042<br>x fs |       |

|                                      |              | DVFLT = 0x1 (Elliptical tuned for fs = 16kHz + 217Hz notch) | 0.0139 x fs | 6   |                |       |

| 0                                    |              | DVFLT = 0x2 (500Hz Butterworth tuned for fs = 16kHz)        | 0.0156 x fs | 6   |                |       |

| Stopband Cutoff<br>(-30dB from Peak) | fDHPSB       | DVFLT = 0x3 (Elliptical tuned for fs = 8kHz + 217Hz notch)  | 0.0279 x fs | 6   |                | Hz    |

|                                      |              | DVFLT = 0x4 (500Hz Butterworth tuned for fs = 8kHz)         | 0.0312 x fs | 6   |                |       |

|                                      |              | DVFLT = 0x5 (fs/240 Butterworth)                            | 0.0021 x fs | 3   |                |       |

| DC Attenuation                       | DCATTEN      | DVFLT ≠ 000                                                 |             | 85  |                | dB    |

| STEREO AUDIO MODE FIR                | LOWPASS FI   | LTER (MODE1 = 1, DHF1/DHF2 = 0, LRCLK < 50kHz               | z)          |     |                |       |

|                                      |              | Ripple limit cutoff                                         | 0.43 x fs   |     |                |       |

| Passband Cutoff                      | fPLP         | -3dB cutoff                                                 | 0.47 x fs   |     |                | Hz    |

|                                      |              | -6.02dB cutoff                                              | 0.5 x fs    |     |                |       |

| Passband Ripple                      |              | f < fPLP                                                    | -0.1        |     | +0.1           | dB    |

| Stopband Cutoff                      | fSLP         |                                                             |             | 0   | .58 x fs       | Hz    |

| Stopband Attenuation (Note 6)        |              | f > fSLP                                                    | 60          |     |                | dB    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(VAVDD = VPVDD = VDVDD = VDVDDS1 = VDVDDS2 = 1.8V, VSPKLVDD = VSPKRVDD = 3.7V. Speaker loads (ZSPK) connected between SPK_P and SPK_N. Receiver load (RREC) connected between RECP and RECN. Headphone loads (RHP) connected from HPL or HPR to HPGND. Line out loads (RLOUT) connected from LOUTL or LOUTR to SPKLGND. RLOAD = RHP = <math>\infty$ , RREC =  $\infty$ , ZSPK =  $\infty$ , CREF =  $2.2\mu$ F, CMICBIAS = CREG =  $1\mu$ F, CC1N-C1P =  $1\mu$ F, CHPVDD = CHPVSS =  $1\mu$ F. AVMICPRE\_ = +20dB, AVMICPGA\_ = 0dB, AVDACATTN = 0dB, AVDACGAIN = 0dB, AVADCGAIN = 0dB, AVPGAIN\_ = 0

| PARAMETER                             | SYMBOL    | CONDITIONS                                                          | MIN       | TYP  | MAX              | UNITS |

|---------------------------------------|-----------|---------------------------------------------------------------------|-----------|------|------------------|-------|

| STEREO AUDIO MODE FIR L               | OWPASS FI | LTER (MODE1 = 1, DHF1/DHF2 = 1 for LRCLK > 50                       | kHz)      |      |                  |       |

| Passband Cutoff                       | fplp      | Ripple limit cutoff                                                 |           |      |                  | Hz    |

| rasspand Culon                        | IPLP      | -3dB cutoff                                                         | 0.31 x fs |      |                  | 1 12  |

| Passband Ripple                       |           | f < fPLP                                                            | -0.1      |      | +0.1             | dB    |

| Stopband Cutoff                       | fSLP      |                                                                     |           |      | 0.477 x fs       | Hz    |

| Stopband Attenuation (Note 6)         |           | f < fSLP                                                            | 60        |      |                  | dB    |

| STEREO AUDIO MODE DC B                | LOCKING H | IGHPASS FILTER                                                      |           |      |                  |       |

| Passband Cutoff<br>(-3dB from Peak)   | fDHPPB    | DVFLT ≠ 000 (DAI1), DCB2 = 1 (DAI2)                                 |           |      | 0.000104<br>x fs | Hz    |

| DC Attenuation                        | DCATTEN   | DVFLT ≠ 000 (DAI1), DCB2 = 1 (DAI2)                                 |           | 90   |                  | dB    |

| AUTOMATIC LEVEL CONTRO                |           |                                                                     | ·         |      |                  |       |

| Dual Band Lowpass Corner<br>Frequency |           | ALCMB = 1                                                           |           | 5    |                  | kHz   |

| Dual Band Highpass Corner Frequency   |           | ALCMB = 1                                                           |           | 5    |                  | kHz   |

| Gain Range                            |           |                                                                     | 0         |      | 12               | dB    |

| Low-Signal Threshold                  |           | ALCTH = 111 to 001                                                  | -48       |      | -12              | dBFS  |

| Release Time                          |           | ALCRLS = 101                                                        |           | 0.25 |                  |       |

| helease Time                          |           | ALCRLS = 000                                                        |           | 8    |                  | s     |

| PARAMETRIC EQUALIZER                  |           |                                                                     |           |      |                  |       |

| Number of Bands                       |           |                                                                     |           | 5    |                  | Bands |

| Per Band Gain Range                   |           |                                                                     | -12       |      | +12              | dB    |

| Preattenuator Gain Range              |           | (Note 5)                                                            | -15       |      | 0                | dB    |

| Preattenuator Step Size               |           |                                                                     |           | 1    |                  | dB    |

| DAC TO RECEIVER AMPLIFI               | ER PATH   |                                                                     |           |      |                  |       |

| Dynamic Range                         | DR        | $f_S = 48kHz$ , $f = 1kHz$ (Note 4)                                 |           | 96   |                  | dB    |

| Output Offset Voltage                 | Vos       | AV <sub>REC</sub> = -62dB, T <sub>A</sub> = +25°C, WLP package only |           | ±0.5 | ±4               | mV    |

| Total Harmonic Distortion + Noise     | THD+N     | $f = 1kHz$ , $P_{OUT} = 15mW$ , $R_{REC} = 32\Omega$                |           | -70  | -63              | dB    |

|                                       |           | VSPKLVDD = 2.8V to 5.5V, T <sub>A</sub> = +25°C                     | 64        | 75   |                  |       |

| Davida Comarko Daia atia - Daii       | DODD      | f = 217Hz, VRIPPLE = 200mVp-p                                       |           | 80   |                  |       |

| Power-Supply Rejection Ratio          | PSRR      | f = 1kHz, VRIPPLE = 200mVp-p                                        | 80        |      |                  | dB    |

|                                       |           | f = 10kHz, VRIPPLE = 200mVp-p                                       |           | 77   |                  |       |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(VAVDD = VPVDD = VDVDD = VDVDDS1 = VDVDDS2 = 1.8V, VSPKLVDD = VSPKRVDD = 3.7V. Speaker loads (ZSPK) connected between SPK_P and SPK_N. Receiver load (RREC) connected between RECP and RECN. Headphone loads (RHP) connected from HPL or HPR to HPGND. Line out loads (RLOUT) connected from LOUTL or LOUTR to SPKLGND. RLOAD = RHP = <math>\infty$ , RREC =  $\infty$ , ZSPK =  $\infty$ , CREF =  $2.2\mu$ F, CMICBIAS = CREG =  $1\mu$ F, CC1N-C1P =  $1\mu$ F, CHPVDD = CHPVSS =  $1\mu$ F. AVMICPRE\_ = +20dB, AVMICPGA\_ = 0dB, AVDACATTN = 0dB, AVDACGAIN = 0dB, AVADCUL = 0dB, AVADCGAIN = 0dB, AVPGAIN\_ = 0dB, AVHP\_ = 0dB, AVREC = 0dB, AVSPK\_ = 0dB, MCLK = 12.288MHz, LRCLK = 48kHz, MAS = 0.74 = 1.80MHz to 1.80MHz, unless otherwise noted. Typical values are at 1.80MHz = 1.80MHz = 1.80MHz.

| PARAMETER                         | SYMBOL      | CONDIT                                                | IONS                                         | <b>3</b>        | MIN | TYP  | MAX | UNITS            |

|-----------------------------------|-------------|-------------------------------------------------------|----------------------------------------------|-----------------|-----|------|-----|------------------|

| Click-and-Pop Level               | KCP         | Peak voltage, A-weighted, 3 samples per second, AVREC |                                              | Into shutdown   |     | -68  |     | dBV              |

| '                                 |             | 0dB                                                   |                                              | Out of shutdown |     | -72  |     |                  |

| LINE INPUT TO RECEIVER A          | MPLIFIER P  | ATH                                                   |                                              |                 |     |      |     |                  |

| Dynamic Range (Note 4)            | DR          | Referenced to full-scale outp                         | out le                                       | evel            |     | 94   |     | dB               |

| Total Harmonic Distortion + Noise | THD+N       |                                                       |                                              |                 |     | -64  |     | dB               |

|                                   |             |                                                       | Peak voltage, A-weighted, 32 Int             |                 |     | -51  |     |                  |

| Click-and-Pop Level               | KCP         | samples per second, AVREC = Out of shutdown -         |                                              | -49             |     | dBV  |     |                  |

| RECEIVER AMPLIFIER                | •           |                                                       |                                              |                 |     |      |     | •                |

| Output Power                      | Pout        | RREC = $32\Omega$ , f = 1kHz, THD                     | = 19                                         | 6               |     | 92   |     | mW               |

| Full-Scale Output                 |             | (Note 7)                                              | Note 7)                                      |                 |     |      |     | V <sub>RMS</sub> |

| Volume Control (Note 5)           | AVREC       | RECVOL = 0x00                                         | ECVOL = 0x00                                 |                 |     |      |     | dB               |

| Volume Control (Note 5)           | AVREC       | RECVOL = 0x1F                                         | RECVOL = 0x1F                                |                 |     |      |     | UB               |

|                                   |             | +8dB to +6dB                                          |                                              |                 |     | 0.5  |     |                  |

|                                   |             | +6dB to +0dB                                          |                                              |                 |     | 1    |     |                  |

| Volume Control Step Size          |             | 0dB to -14dB                                          |                                              |                 | 2   |      |     | dB               |

|                                   |             | -14dB to -38dB                                        |                                              |                 |     | 3    |     |                  |

|                                   |             | -38dB to -62dB                                        |                                              |                 |     | 4    |     |                  |

| Mute Attenuation                  |             | f = 1kHz                                              |                                              |                 |     | 88   |     | dB               |

| Capacitive Drive Capability       |             | No sustained oscillations                             | RRE                                          | $C = 32\Omega$  |     | 500  |     | - pF             |

| Capacitive Drive Capability       |             | TWO SUSTAINED OSCINATIONS                             | RRE                                          | C = ∞           |     | 100  |     | Рі               |

| DAC TO LINE OUT AMPLIFI           | ER PATH     |                                                       |                                              |                 |     |      |     |                  |

| Dynamic Range (Note 4)            | DR          | $f_S = 48kHz$ , $f = 1kHz$                            |                                              |                 | 83  | 96   |     | dB               |

| Total Harmonic Distortion + Noise | THD+N       | $f = 1kHz, R_L = 1k\Omega$                            |                                              |                 |     | -78  | -72 | dB               |

| LINE INPUT TO LINE OUT A          | MPLIFIER PA | ATH                                                   |                                              |                 |     |      |     |                  |

| Dynamic Range (Note 4)            | DR          | Referenced to full-scale outp                         | out le                                       | evel            |     | 92   |     | dB               |

| Total Harmonic Distortion + Noise | THD+N       | $f = 1kHz, R_L = 10k\Omega$                           |                                              |                 | 76  |      | dB  |                  |

| Full-Scale Output                 |             | (Note 7)                                              | (Note 7)                                     |                 |     | 2    |     | V <sub>P-P</sub> |

| Mute Attenuation                  |             | f = 1kHz                                              |                                              |                 |     | 85   |     | dB               |

| Output Offset Voltage             | Vos         | AV <sub>REC</sub> = -62dB, TQFN pac                   | AV <sub>REC</sub> = -62dB, TQFN package only |                 |     | ±0.5 | ±4  | mV               |

| Capacitive Drive Capability       |             | No sustained oscillations, R                          |                                              |                 |     | 500  |     | рF               |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(VAVDD = VPVDD = VDVDD = VDVDDS1 = VDVDDS2 = 1.8V, VSPKLVDD = VSPKRVDD = 3.7V. Speaker loads (ZSPK) connected between SPK_P and SPK_N. Receiver load (RREC) connected between RECP and RECN. Headphone loads (RHP) connected from HPL or HPR to HPGND. Line out loads (RLOUT) connected from LOUTL or LOUTR to SPKLGND. RLOAD = RHP = <math>\infty$ , RREC =  $\infty$ , ZSPK =  $\infty$ , CREF =  $2.2\mu$ F, CMICBIAS = CREG =  $1\mu$ F, CC1N-C1P =  $1\mu$ F, CHPVDD = CHPVSS =  $1\mu$ F. AVMICPRE\_ = +20dB, AVMICPGA\_ = 0dB, AVDACATTN = 0dB, AVDACGAIN = 0dB, AVADCLVL = 0dB, AVADCGAIN = 0dB, AVPGAIN\_ = 0dB, AVHP\_ = 0dB, AVREC = 0dB, AVSPK\_ = 0dB, MCLK = 12.288MHz, LRCLK = 48kHz, MAS = 0.74 = 1.80MHz to 1.80MHz, unless otherwise noted. Typical values are at 1.80MHz = 1.80MHz

| PARAMETER                         | SYMBOL  |                                            | CONDITIONS                                    | 3                             | MIN TYP  | MAX | UNITS   |

|-----------------------------------|---------|--------------------------------------------|-----------------------------------------------|-------------------------------|----------|-----|---------|

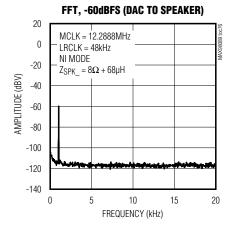

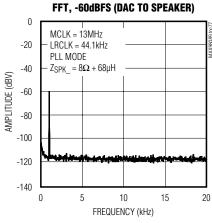

| DAC TO SPEAKER AMPLIFI            | ER PATH | •                                          |                                               |                               |          |     |         |

| Total Harmonic Distortion + Noise | THD+N   | f = 1kHz, Pout                             | = 200mW, Z <sub>SPK</sub>                     | = 8Ω + 68μH                   | -68      |     | dB      |

| Crosstalk                         |         | SPKL to SPKR a                             | and SPKR to SPK<br>/, f = 1kHz                | L,                            | -88      |     | dB      |

| Output Noise                      |         |                                            |                                               |                               | 53       |     | μVRMS   |

| Click-and-Pop Level               | KCP     | Peak voltage, A 32 samples per             |                                               | Into shutdown Out of shutdown | 65<br>66 |     | dBV     |

|                                   |         | AVSPK_ = 0dB                               |                                               | Out of shutdown               | 00       |     |         |

| MIC INPUT TO SPEAKER AN           | 1       |                                            |                                               | 1 A) / 0 ID                   | 1 00     |     | 1 15    |

| Dynamic Range (Note 4)            | DR      | Referenced to fu                           | scale output level, AV <sub>SPK</sub> _ = 0dB |                               | 82       |     | dB      |

| Total Harmonic Distortion + Noise | THD+N   | f = 1kHz, Pout                             | = 200mW, R <sub>L</sub> = 8                   | 8Ω + 68μΗ                     | 71       |     | dB      |

| Click-and-Pop Level               | KCP     | Peak voltage, A                            | -weighted, 32<br>cond, AV <sub>SPK</sub> _ =  | Into shutdown                 | 55       |     | dBV     |

| Olick-aria-r op Level             | NOP     | 0dB                                        |                                               | Out of shutdown               | 52       |     | ubv     |

| SPEAKER AMPLIFIER                 |         |                                            |                                               |                               |          |     |         |

|                                   |         | f = 1kHz                                   | VSPKLVDD = V                                  | SPKRVDD = 5.0V                | 2950     |     |         |

|                                   |         | THD = 10%,<br>ZSPK = $4\Omega$ + $33\mu$ H | VSPKLVDD = V                                  | SPKRVDD = 4.2V                | 2060     | 1   |         |

|                                   |         |                                            | VSPKLVDD = V                                  | SPKRVDD = 3.7V                | 1570     | 1   |         |

|                                   |         |                                            | VSPKLVDD = VSPKRVDD = 3.0V                    |                               | 1000     |     |         |

|                                   |         | f = 1kHz                                   | VSPKLVDD = V                                  | SPKRVDD = 5.0V                | 2320     |     |         |

|                                   |         | THD = 1%,                                  | VSPKLVDD = VSPKRVDD = 4.2V                    |                               | 1620     |     |         |

|                                   |         | $Z_{SPK} = 4\Omega +$                      | VSPKLVDD = VSPKRVDD = 3.7V                    |                               | 1240     |     | 7       |

| 0                                 |         | 33µH                                       | VSPKLVDD = V                                  | SPKRVDD = 3.0V                | 785      |     | Ī .,,,, |

| Output Power                      | Pout    | f = 1kHz.                                  | VSPKLVDD = V                                  | SPKRVDD = 5.0V                | 1730     |     | mW      |

|                                   |         | THD = 10%.                                 | VSPKLVDD = V                                  | SPKRVDD = 4.2V                | 1210     |     | 1       |

|                                   |         | $Z_{SPK} = 8\Omega +$                      | VSPKLVDD = V                                  | SPKRVDD = 3.7V                | 930      |     | 1       |

|                                   |         | 68µH                                       | VSPKLVDD = V                                  | SPKRVDD = 3.0V                | 600      |     | 1       |

|                                   |         | f = 1kHz                                   | _                                             | SPKRVDD = 5.0V                | 1365     | 1   | 1       |

|                                   |         | THD = 1%,                                  |                                               | SPKRVDD = 4.2V                | 955      |     | 1       |

|                                   |         | $Z_{SPK} = 8\Omega +$                      |                                               | SPKRVDD = 3.7V                | 735      |     | 1       |

|                                   |         | 68µH                                       | VSPKLVDD = V                                  | VSPKLVDD = VSPKRVDD = 3.0V    |          |     |         |

| Full-Scale Output                 |         | (Note 7)                                   | 1 0                                           |                               | 2        |     | VRMS    |

| -                                 |         | SPVOLL/SPVOLR                              |                                               | DLR = 0x00                    | -62      |     | dB      |

| Volume Control                    | AVSPK_  | (Note 5)                                   |                                               | SPVOLL/SPVOLR = 0x1F          |          | +8  |         |

|                                   |         | 1                                          |                                               |                               |          |     | 1       |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(VAVDD = VPVDD = VDVDD = VDVDDS1 = VDVDDS2 = 1.8V, VSPKLVDD = VSPKRVDD = 3.7V. Speaker loads (ZSPK) connected between SPK_P and SPK_N. Receiver load (RREC) connected between RECP and RECN. Headphone loads (RHP) connected from HPL or HPR to HPGND. Line out loads (RLOUT) connected from LOUTL or LOUTR to SPKLGND. RLOAD = RHP = <math>\infty$ , RREC =  $\infty$ , ZSPK =  $\infty$ , CREF =  $2.2\mu$ F, CMICBIAS = CREG =  $1\mu$ F, CC1N-C1P =  $1\mu$ F, CHPVDD = CHPVSS =  $1\mu$ F. AVMICPRE\_ = +20dB, AVMICPGA\_ = 0dB, AVDACATTN = 0dB, AVDACGAIN = 0dB, AVADCLVL = 0dB, AVADCGAIN = 0dB, AVPGAIN\_ = 0

| PARAMETER                       | SYMBOL               | CONDITIO                                                                    | ONS         | MIN  | TYP  | MAX  | UNITS |  |

|---------------------------------|----------------------|-----------------------------------------------------------------------------|-------------|------|------|------|-------|--|

|                                 |                      | +8dB to +6dB                                                                |             |      | 0.5  |      |       |  |

|                                 |                      | +6dB to +0dB                                                                |             |      | 1    |      | 1     |  |

| Volume Control Step Size        |                      | 0dB to -14dB                                                                |             |      | 2    |      | dB    |  |

|                                 |                      | -14dB to -38dB                                                              |             |      | 3    |      | 1     |  |

|                                 |                      | -38dB to -64dB                                                              |             |      | 4    |      | 1     |  |

| Mute Attenuation                |                      | f = 1kHz                                                                    |             |      | 86   |      | dB    |  |

| Output Offset Voltage           | Vos                  | AVSPK_ = -61dB, TA = +25°C                                                  | ;           |      | ±0.5 | ±3   | mV    |  |

| EXCURSION LIMITER               | •                    |                                                                             |             |      |      |      |       |  |

| Upper Corner Frequency<br>Range |                      | DHPUCF = 001 to 100                                                         |             | 400  |      | 1000 | Hz    |  |

| Lower Corner Frequency          |                      | DHPLCF = 01 to 10                                                           |             |      | 400  |      | Hz    |  |

|                                 |                      | DHPUCF = 000 (fixed mode)                                                   |             |      | 100  |      |       |  |

|                                 |                      | DHPUCF = 001                                                                |             |      | 200  |      |       |  |

| Biquad Minimum Corner           |                      | DHPUCF = 010                                                                | PUCF = 010  |      |      |      | Hz    |  |

| Frequency                       |                      | DHPUCF = 011                                                                |             |      | 400  |      |       |  |

|                                 |                      | DHPUCF = 100                                                                |             |      |      |      | 1     |  |

| Threshold Voltage               |                      | $Z$ SPK = 8 $\Omega$ + 68μH, $V$ SP-<br>KLVDD = $V$ SPKR $V$ DD = 5.5 $V$ , | DHPTH = 000 |      | 0.34 |      | VP    |  |

| Trii conord Vollago             |                      | $AV_{SPK} = 8dB$                                                            | DHPTH = 111 |      | 0.95 |      | "     |  |

| Release Time                    |                      | ALCRLS = 101                                                                |             |      | 0.25 |      |       |  |

| nelease Time                    |                      | ALCRLS = 000                                                                |             |      | 4    |      | S     |  |

| POWER LIMITER                   |                      |                                                                             |             |      |      |      |       |  |

| Attenuation                     |                      |                                                                             |             |      | -64  |      | dB    |  |

| Threshold                       |                      | ZSPK = $8\Omega$ + $68\mu$ H, VSP-<br>KLVDD = VSPKRVDD = $5.5$ V,           | PWRTH = 0x1 |      | 0.08 |      | W     |  |

| modificial                      |                      | $AV_{SPK} = 8dB$                                                            | PWRTH = 0xF |      | 1.23 |      | ''    |  |

| Time Constant 1                 | town.                | PWRT1 = 0x1                                                                 | •           |      | 0.5  |      |       |  |

| Time Constant 1                 | tPWR1                | PWRT1 = 0xF                                                                 |             |      | 8.7  |      | S     |  |

| Time Constant 0                 |                      | PWRT2 = 0x1 to 0xF                                                          |             |      | 0.5  |      | main  |  |

| Time Constant 2                 | tPWR2                | PWRT2 = 0xF                                                                 |             |      | 8.7  |      | min   |  |

| Weighting Factor                | kpwr                 | PWRK = 000 to 111                                                           |             | 12.5 |      | 100  | %     |  |

| DISTORTION LIMITER              |                      |                                                                             |             |      |      |      |       |  |

| Distortion Limit                |                      | THDCLP = 0x1                                                                |             |      | < 1  |      | 0/    |  |